エンコーダ搭載機器およびエンコーダ装置

【課題】簡素な回路構成で、複数のエンコーダの検出結果を伝送することのできるエンコーダ搭載機器、およびエンコーダ装置を提供すること。

【解決手段】エンコーダ装置100およびエンコーダ搭載機器1000では、エンコーダ装置100側および制御部210側に同期式の半2重シリアル通信用のインターフェース機器150、250を設け、制御部210は、複数の演算処理部11での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信する一方、エンコーダ装置100は、指令信号に対応するタイミングで複数の演算処理部11での演算結果、および複数の演算処理部11での演算結果が出力されるタイミングに対応する同期信号CLKの各々をシリアル信号として出力する。

【解決手段】エンコーダ装置100およびエンコーダ搭載機器1000では、エンコーダ装置100側および制御部210側に同期式の半2重シリアル通信用のインターフェース機器150、250を設け、制御部210は、複数の演算処理部11での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信する一方、エンコーダ装置100は、指令信号に対応するタイミングで複数の演算処理部11での演算結果、および複数の演算処理部11での演算結果が出力されるタイミングに対応する同期信号CLKの各々をシリアル信号として出力する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、複数のエンコーダを備えたエンコーダ搭載機器、および複数のエンコーダを備えたエンコーダ装置に関するものである。

【背景技術】

【0002】

エンコーダ装置は、固定体に対する移動体の移動を検出する装置であり、概ね、エンコーダと、エンコーダからの出力に演算処理を行う演算処理部とによって構成されている。かかるエンコーダは、電子フィーダ部品装置やプリンタ等の機器において複数設けられて、複数の移動体の動作を各々監視するために用いられることもある(特許文献1、2参照)。

【0003】

このような場合、複数のエンコーダに対して一対一の関係をもって複数の演算処理部が設けられることになる。また、エンコーダ装置は、機器本体と別体に構成される場合が多く、この場合、複数の演算処理部での演算結果は、伝送路を介して機器本体の制御部に伝送されることになる。その際、複数の演算処理部での演算結果を機器本体の制御部にパラレル伝送する方式を採用すると、回路規模が増大しコストが増大する。

【0004】

そこで、エンコーダ装置側において、制御部側から出力された共通のリクエスト信号に応じて各演算処理部での演算結果を送信する開始時間を相違させて、演算結果をシリアル出力する構成が提案されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−60809号公報

【特許文献2】特開平09−258513号公報

【特許文献3】特開平8−233607号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献3に記載の構成では、共通のリクエスト信号をデコード化して自己認識番号に応じてエンコーダ信号を読み出す必要がある等、シリアル通信を用いた割には回路規模が増大しコストが増大するという問題点がある。

【0007】

以上の問題点に鑑みて、本発明の課題は、簡素な回路構成で、複数のエンコーダの検出結果を伝送することのできるエンコーダ搭載機器、およびエンコーダ装置を提供することにある。

【課題を解決するための手段】

【0008】

上記の課題を解決するために、本発明は、複数のエンコーダ、および該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部を備えたエンコーダ装置と、該エンコーダ装置に対する制御部と、前記エンコーダ装置と前記制御部とを接続する伝送路と、を有するエンコーダ搭載機器において、前記制御部は、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として受信する同期式の半2重シリアル通信用の制御部側インターフェース機器を有し、前記エンコーダ装置は、前記指令信号を受信するとともに、当該指令信号に基づいて前記複数の演算処理部での演算結果および前記同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のエンコーダ装置側インターフェース機器を有していることを特徴とする。

【0009】

本発明では、エンコーダ装置側および制御部側に同期式の半2重シリアル通信用のインターフェース機器を設け、制御部は、複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信する一方、エンコーダ装置は、指令信号に基づいて複数の演算処理部での演算結果、および複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号の各々をシリアル信号として出力する。このため、制御部は、同期信号に基づいてエンコーダ毎の検出結果を取得することができる。また、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができる。

【0010】

本発明において、前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、前記制御部側インターフェース機器は、制御部側第1トランシーバと制御部側第2トランシーバと、を備え、前記エンコーダ装置側インターフェース機器は、前記制御部側第1トランシーバと対をなすエンコーダ装置側第1トランシーバと、前記制御部側第2トランシーバと対をなすエンコーダ装置側第2トランシーバと、を備え、前記制御部側第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する前記同期信号を受信するシリアルレシーバと、を備え、前記制御部側第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を前記第1指令信号と異なるタイミングで送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を受信するシリアルレシーバと、を備え、前記エンコーダ装置側第1トランシーバは、前記第1指令信号を受信するシリアルレシーバと、前記同期信号を送信するシリアルドライバと、を備え、前記エンコーダ装置側第2トランシーバは、前記第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果をシリアル信号として送信するシリアルドライバと、を備えていることが好ましい。かかる構成によれば、エンコーダ装置側および制御部側の同期式の半2重シリアル通信用のインターフェース機器として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダの検出結果を伝送することができる。

【0011】

また、本発明に係るエンコーダ装置は、複数のエンコーダと、該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部と、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号をシリアル信号として受信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のインターフェース機器と、を有していることを特徴とする。

【0012】

本発明において、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができる。

【0013】

本発明において、前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、前記インターフェース機器は、第1トランシーバと第2トランシーバとを備え、前記第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する同期信号を送信するシリアルドライバと、を備え、前記第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を送信するシリアルドライバと、を備えていることが好ましい。かかる構成によれば、同期式の半2重シリアル通信用のインターフェース機器として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダの検出結果を伝送することができる。

【0014】

本発明において、前記複数のエンコーダは、例えば、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えている。

【発明の効果】

【0015】

本発明において、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができるので、コストを低減することができる。

【図面の簡単な説明】

【0016】

【図1】本発明を適用したエンコーダ搭載機器の説明図である。

【図2】本発明に係るエンコーダ装置の基本構成等を示す説明図である。

【図3】本発明に係るエンコーダ装置に用いた感磁素子の磁気抵抗パターンの電気的な接続構造の説明図である。

【図4】本発明を適用したエンコーダ装置のエンコーダの具体的構成例を示す説明図である。

【図5】本発明に係るエンコーダ装置に用いた感磁素子の説明図である。

【図6】本発明に係るエンコーダ搭載機器に用いたインターフェース機器等の説明図である。

【図7】本発明に係るエンコーダ搭載機器で送信される演算結果の説明図である。

【発明を実施するための形態】

【0017】

以下に、図面を参照して、本発明を適用したエンコーダ搭載機器およびエンコーダ装置を説明する。なお、本発明では、エンコーダとしてロータリエンコーダおよびリニアエンコーダを用いることができるが、以下の説明では、エンコーダとしてロータリエンコーダを用いた場合を説明する。また、ロータリエンコーダにおいて、固定体に対する回転体の回転を検出するにあたっては、固定体に磁気スケールを設け、回転体に感磁素子(センサユニット)を設けた構成、および固定体に感磁素子(センサユニット)を設け、回転体に磁気スケールを設けた構成のいずれの構成を採用してもよいが、以下の説明では、固定体に感磁素子(センサユニット)を設け、回転体に磁気スケールを設けた構成を中心に説明する。また、以下に参照する図面において、マグネットおよび感磁素子等の構成について模式的に示してある。

【0018】

(エンコーダ搭載機器の全体構成)

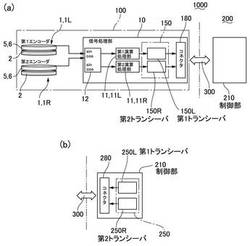

図1は、本発明を適用したエンコーダ搭載機器の説明図であり、図1(a)、(b)は、エンコーダ搭載機器の主要部の構成を示す説明図、制御部側のインターフェース機器の説明図である。

【0019】

図1に示すエンコーダ搭載機器1000は、電子フィーダ部品装置やプリンタ等の機器であり、図示を省略するが、エンコーダ搭載機器1000は、複数のアクチュエータと、これらのアクチュエータの各々によって駆動される複数の回転軸とを有している。かかるエンコーダ搭載機器1000では、複数の回転軸が同期して回転するように、複数の回転軸の各々の回転を複数のエンコーダ1で検出し、かかる複数のエンコーダ1での検出結果に基づいて、機器本体200は、複数のアクチュエータを制御する。

【0020】

ここで、複数のエンコーダ1は、エンコーダ1に対する信号処理部10とともにエンコーダ装置100を構成しており、信号処理部10は、複数のエンコーダ1に対して一対一で対応する複数の演算処理部11を有している。ここで、エンコーダ装置100は、制御部210を備えた機器本体200とは別体に構成されている。このため、エンコーダ装置100と機器本体200の制御部210とは伝送路300を介して接続されており、エンコーダ装置100は、制御部210から伝送路300を介して送信される指令に基づいて、複数の演算処理部11での演算結果を、伝送路300を介して制御部210に出力する。

【0021】

本形態において、エンコーダ装置100は、複数のエンコーダ1として、第1エンコーダ1Lと第2エンコーダ1Rとを有しており、それ故、信号処理部10は、複数の演算処理部11として、第1エンコーダ1Lでの検出結果に演算処理を行う第1演算処理部11Lと、第2エンコーダ1Rでの検出結果に演算処理を行う第2演算処理部11Rとを有している。また、エンコーダ装置100および制御部210は各々、伝送路300を介して通信を行うためのインターフェース機器150、250およびコネクタ180、280を有している。かかるインターフェース機器150、250を用いての通信の内容は、図6等を参照して後述する。

【0022】

(エンコーダ装置100の構成)

図2は、本発明に係るエンコーダ装置100の基本構成等を示す説明図であり、図2(a)、(b)、(c)は、磁気スケールと感磁素子との位置関係等を模式的に示す説明図、感磁素子からの出力信号の説明図、および感磁素子からの出力信号と回転体の角度位置θ(電気角)との関係を示す説明図である。図3(a)、(b)は、本発明に係るエンコーダ装置100に用いた感磁素子の磁気抵抗パターンの電気的な接続構造の説明図である。なお、本形態において、2つのエンコーダ1(第1エンコーダ1Lと第2エンコーダ1R)の構成は同一であるため、第1を意味する「L」や第2意味する「R」等を付さずに説明する。

【0023】

図2に示すように、本形態のエンコーダ装置100において、複数のエンコーダ1は各々、磁気スケール2およびセンサユニット5を有している。本形態において、磁気スケール2は回転体側に設けられ、センサユニット5は固定体側に設けられている。磁気スケール2は、N極とS極とが周方向において交互に着磁された磁気トラック31を回転軸線方向Lの一方側L1に向けており、センサユニット5は、磁気トラック31に対して回転軸線方向Lの一方側L1で対向する感磁素子6(センサ素子)を備えている。磁気トラック31には、トラック311、312が2列、同心状に並列して形成されている。かかる磁気トラック31において、2つのトラック311、312の間ではN極およびS極の位置が周方向でずれており、本形態では、2つのトラック311、312の間においてN極およびS極が周方向に1極分ずれている。

【0024】

感磁素子6は、磁気抵抗素子であり、磁気トラック31の位相に対して、互いに90°の位相差を有するA相(SIN)の磁気抵抗パターンとB相(COS)の磁気抵抗パターンとを備えている。かかる感磁素子(磁気抵抗素子)において、A相の磁気抵抗パターンは、180°の位相差をもって回転体の移動検出を行う+a相(SIN+)の磁気抵抗パターン64および−a相(SIN-)の磁気抵抗パターン62を備えており、B相の磁気抵抗パターンは、180°の位相差をもって回転体の移動検出を行う+b相(COS+)の磁気抵抗パターン63および−b相(COS-)の磁気抵抗パターン61を備えている。

【0025】

図3(a)に示すように、+a相の磁気抵抗パターン64および−a相の磁気抵抗パターン62はブリッジ回路を構成しており、一方端が電源端子(Vcc)に接続され、他方端がグランド端子(GND)に接続されている。また、+a相の磁気抵抗パターン64の中点位置には、+a相が出力される端子(+a)が設けられ、−a相の磁気抵抗パターン62の中点位置には、−a相が出力される端子(−a)が設けられている。

【0026】

図3(b)に示すように、+b相の磁気抵抗パターン63および−b相の磁気抵抗パターン61も、+a相の磁気抵抗パターン64および−a相の磁気抵抗パターン62と同様、ブリッジ回路を構成しており、一方端が電源端子(Vcc)に接続され、他方端がグランド端子(GND)に接続されている。また、+b相の磁気抵抗パターン63の中点位置には、+b相が出力される端子(+b)が設けられ、−b相の磁気抵抗パターン61の中点位置には、−b相が出力される端子(−b)が設けられている。

【0027】

再び図2において、感磁素子6は、磁気トラック31において隣接するトラック311、312の境界部分313に回転軸線方向Lで重なる位置に配置されている。このため、感磁素子6の磁気抵抗パターン61〜64は、各磁気抵抗パターン61〜64の抵抗値の飽和感度領域以上の磁界強度で磁気トラック31の面内方向で向きが変化する回転磁界を検出することができる。すなわち、隣接するトラック311、312の境界部分313においては、各磁気抵抗パターン61〜64の抵抗値の飽和感度領域以上の磁界強度でトラック311、312の面内方向の向きが周方向で漸次に変化する回転磁界が発生する。飽和感度領域とは、一般的に、抵抗値変化量kが、磁界強度Hと近似的に「k∝H2」の式で表すことができる領域以外の領域をいう。また、飽和感度領域以上の磁界強度で回転磁界(磁気ベクトルの回転)の方向を検出する際の原理は、強磁性金属からなる磁気抵抗パターン61〜64に通電した状態で、抵抗値が飽和する磁界強度を印加したとき、磁界と電流方向がなす角度θと、磁気抵抗パターン61〜64の抵抗値Rとの間には、下式

R=R0−k×sin2θ

R0:無磁界中での抵抗値

k:抵抗値変化量(飽和感度領域以上のときは定数)

で示す関係があることを利用するものである。このような原理に基づいて回転磁界を検出すれば、角度θが変化すると抵抗値Rが正弦波に沿って変化するので、波形品質の高いA相およびB相を得ることができる。

【0028】

かかる構成のエンコーダ装置100において、エンコーダ1の感磁素子6に対しては信号処理部10が接続されており、信号処理部10は、増幅回路13、14を備えた増幅回路部12や、これらの増幅回路13、14から出力される正弦波信号sin、cosに補間処理や各種演算処理を行う演算処理部11等が設けられており、感磁素子6からの出力に基づいて、固定体に対する回転体の回転速度、回転方向、角度位置が検出される。より具体的には、エンコーダ装置100において、回転体が磁極の1周期分回転すると、感磁素子6からは、図2(b)に示す正弦波信号sin、cosが2周期分、出力される。従って、正弦波信号sin、cosを増幅回路13、14により増幅した後、演算処理部11において、図2(c)に示すように、正弦波信号sin、cosからθ=tan-1(sin/cos)を求めれば、回転体の角度位置θが分かる。

【0029】

(エンコーダ1の具体的構成)

図4は、本発明を適用したエンコーダ装置100のエンコーダ1の具体的構成例を示す説明図であり、図4(a)、(b)、(c)、(d)は、エンコーダ1の側面図、磁気スケール2をセンサユニット5の側から見た斜視図、磁気スケール2の磁気トラック31の説明図、およびセンサユニット5の斜視図である。なお、図4(d)には感磁素子6の表面からシールドテープを剥がした様子を示してある。

【0030】

図4(a)、(b)、(d)に示すように、エンコーダ1において、磁気スケール2およびセンサユニット5はいずれも円環状であり、回転体の回転軸線方向Lで対向し、かつ、磁気スケール2の中心O2、およびセンサユニット5の中心O5が回転体の回転軸線方向L上に位置するように配置されている。

【0031】

図4(b)に示すように、磁気スケール2は、SPPC(冷間圧延鋼板)等の金属製の円環状のヨーク板20と、このヨーク板20の表面(センサユニット5が位置する側)に固定された円環状のセンサマグネット30とを備えており、図4(c)に示すように、センサマグネット30の表面(着磁されている面33)には周方向に延びる円環状の磁気トラック31が設けられている。磁気トラック31は半径方向に並列して周方向に延びる内側のトラック311と外側のトラック312とからなる。これらトラック311、312は着磁ヘッドによってセンサマグネット30に対する着磁を行うことにより設けられる。

【0032】

図4(b)に点線で示すように、センサマグネット30の着磁表面には、ステンレス等の非磁性材料からなる円環状の保護シート40が取り付けられている。本例では、磁気トラック31は周方向に90分割されてN極とS極が交互に着磁されており、各磁極が着磁されている角度範囲は4°である。また、各S極および各N極の平面形状は外周から内周側に向けて幅が狭くなる扇形となっている。なお、磁気スケール2から保護シート40を省略することも可能である。

【0033】

図4(a)、(d)に示すように、センサユニット5は、亜鉛ダイカスト品やアルミニウムダイカスト品からなる円環状のホルダ8と、このホルダ8の裏面側(磁気スケール2が位置する側とは反対側)に取り付けられた剛性の回路基板7と、回路基板7に電気的に接続された可撓性基板9と、可撓性基板9に電気的に接続された感磁素子6とを備えており、感磁素子6において磁気スケール2が位置する側の面がセンサ面6aである。回路基板7には、回路基板7からの出力を、図2(a)に示す信号処理部10に出力するコネクタ15が実装されている。感磁素子6のセンサ面6aには、電気ノイズ対策として金属製のシールドテープが貼り付けられており、センサ面6aはシールドテープによって覆われている。

【0034】

(感磁素子6の具体的構成例)

図5は、本発明に係るエンコーダ装置100に用いた感磁素子6の説明図であり、図5(a)、(b)は、感磁素子6の平面図、および感磁素子6における磁気抵抗パターンの積層状態を模式的に示す説明図である。なお、図5(a)では、各磁気抵抗パターンと重ねて各磁気抵抗パターンと対向配置されるトラック311、312を表してある。

【0035】

図5において、本形態で用いた感磁素子6は、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は、層間絶縁膜を介して積層された第1積層磁気抵抗パターン601として素子基板60の主面60a上に形成されており、素子基板60の主面60a側がセンサ面6aである。+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は各々、磁気トラック31の半径方向においては、その中心がトラック311、312の境界部分313に対向して配置されており、磁気トラック31の周方向においては、+a相の磁気抵抗パターン64(SIN+)が検出する+a相と+b相の磁気抵抗パターン63(COS+)が検出する+b相が最小位相差となる最小機械角度ずれた位置に配置されている。すなわち、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は、磁気スケール2から得られる同一の波長を90°の位相差で検出可能な角度位置に配置されている。本例では、+a相の磁気抵抗パターン64(SIN+)と+b相の磁気抵抗パターン63(COS+)は周方向で1°ずれた位置に配置されている。なお、本形態では、図5(b)に示すように、素子基板60の主面60a上に+b相の磁気抵抗パターン63(COS+)が形成され、+a相の磁気抵抗パターン64(SIN+)がその上に積層されている。なお、最小位相差とは90°の位相差であり、+a相の磁気抵抗パターン64(SIN+)と+b相の磁気抵抗パターン63(COS+)の上下関係は逆でもよい。

【0036】

−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)も、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)と同様、層間絶縁膜を介して積層された第2積層磁気抵抗パターン602として素子基板60の主面60a上に形成されている。−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)は各々、磁気トラック31の半径方向においては、その中心がトラック311、312の境界部分313に対向して配置されており、磁気トラック31の周方向においては、−a相の磁気抵抗パターン62(SIN-)が検出する−a相と−b相の磁気抵抗パターン61(COS-)が検出する−b相とが最小位相差となる最小機械角度ずれた位置に配置されている。すなわち、−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)は、磁気スケール2から得られる同一の波長を90°の位相差で検出可能な角度位置に配置されている。本例では、−a相の磁気抵抗パターン62(SIN-)と−b相の磁気抵抗パターン61(COS-)は周方向で1°ずれた位置に配置されている。なお、本形態では、図5(b)に示すように、素子基板60の主面60a上に−a相の磁気抵抗パターン62(SIN-)が形成され、−b相の磁気抵抗パターン61(COS-)がその上に積層されている。なお、最小位相差とは90°の位相差であり、−a相の磁気抵抗パターン62(SIN-)と−b相の磁気抵抗パターン61(COS-)の積層関係は逆でもよい。

【0037】

次に、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602は、周方向で重ならない位置に配置されている。より詳細には、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602は、第1積層磁気抵抗パターン601の+a相の磁気抵抗パターン64(SIN+)から検出される+a相と、第2積層磁気抵抗パターン602の−a相の磁気抵抗パターン62(SIN-)から検出される−a相が180°の位相差となる位置であり、第1積層磁気抵抗パターン601の+b相の磁気抵抗パターン63(COS+)から検出される+b相と、第2積層磁気抵抗パターン602の−b相の磁気抵抗パターン61(COS-)から検出される−b相とが180°の位相差となる位置に配置されている。さらに、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602が電気的或いは磁気的に干渉しない最小距離だけ離れた角度位置に配置されている。本例では、第1積層磁気抵抗パターン601の+a相の磁気抵抗パターン64(SIN+)と、第2積層磁気抵抗パターン602の−a相の磁気抵抗パターン62(SIN-)は周方向に22°ずれた位置に配置されている。第1積層磁気抵抗パターン601の+b相の磁気抵抗パターン63(COS+)と、第2積層磁気抵抗パターン602の−b相の磁気抵抗パターン61(COS-)も、同様に、周方向に22°ずれた位置に配置されている。

【0038】

ここで、各磁気抵抗パターン61〜64は互いに平行ではなく、図4等に示すホルダ8の中心O8(センサユニット5の中心O5)から径方向に延在する複数の仮想線上に位置しており、ホルダ8およびセンサユニット5の半径方向に延在している。かかる磁気抵抗パターン61〜64は、ガラスあるいはシリコンからなる素子基板60上に、半導体プロセスによって強磁性体NiFe等の磁性体膜を積層することによって形成されている。素子基板60は長方形をしており、各磁気抵抗パターン61〜64は素子基板60の中央領域に形成されている。素子基板60の端部には、一方の長辺に沿って複数の端子68が形成されており、かかる端子68は、図4等に示す可撓性基板9との電気的な接続に用いられている。また、各磁気抵抗パターン61〜64は、端子68を避けるように形成されたエポキシ樹脂等の保護層(図示せず)によって覆われており、かかる保護層は、例えば、スクリーン印刷によって形成されている。

【0039】

(磁気スケール2の詳細構成)

図4(b)において、磁気スケール2は、円環状のヨーク板20と、このヨーク板20の表面(センサユニット5が位置する側)に固定した円環状のセンサマグネット30とを備えている。ヨーク板20は、センサマグネット30より幅寸法が大であり、ヨーク板20の内周部分21は、センサマグネット30の内周縁35より内側に位置し、ヨーク板20の外周部分22は、センサマグネット30の外周縁32より外側に位置している。従って、磁気スケール2の円形の外周縁および円形の内周縁は、ヨーク板20の内周部分21および外周部分22に相当する。

【0040】

かかる構成の磁気スケール2において、センサマグネット30は、ヨーク板20の円形状を基準に着磁されている。より具体的には、センサマグネット30は、円環状に成形した磁性体をヨーク板20に接着剤により固定した後、磁性体の表面を研磨し、しかる後に着磁を行って、磁気トラック31を形成することにより、形成されている。かかる着磁の際、本形態では、センサマグネット30(磁性体)の円形状ではなく、ヨーク板20の内周部分21や外周部分22等、ヨーク板20の円形状を基準に着磁されている。このため、磁気スケール2では、磁気トラック31と、ヨーク板20の内周部分21および外周部分22とは、同心状である。

【0041】

ここで、センサマグネット30は、フェライト等の磁性粉(マグネット原料)とPPS(polyphenylene sulfide)等の熱可塑性樹脂材料(プラスチック材料)とを混合して成形したプラスチックマグネットである。本形態において、センサマグネット30は、各種のプラスチックマグネットのうち、フィルムゲート(フラッシュゲート)により成形されたプラスチックマグネットである。かかるフィルムゲートによる成形では、フィルム状(膜状)のゲートを使用し、かつ、このフィルム状のゲートを円環状のセンサマグネット30の内周面となる部分の全周に設けて成形する。

【0042】

(インターフェース機器150、250等の構成)

図6は、本発明に係るエンコーダ搭載機器1000に用いたインターフェース機器150、250等の説明図であり、図6(a)、(b)は、インターフェース機器150、250の具体的構成例を示す説明図、および通信プロトコルの説明図である。

【0043】

図1に示すように、本形態のエンコーダ搭載機器1000では、機器本体200側の制御部210にはインターフェース機器250(制御部側インターフェース機器)が設けられ、エンコーダ装置100側にはインターフェース機器150(エンコーダ装置側インターフェース機器)が設けられている。インターフェース機器150、250はいずれも、同期式の半2重シリアル通信用のインターフェース機器であり、各々、RS485機器等からなるトランシーバを2つずつ有している。

【0044】

より具体的には、図1および図6に示すように、インターフェース機器250は、第1トランシーバ250Lおよび第2トランシーバ250Rを有しており、第1トランシーバ250Lは制御部側第1トランシーバであり、第2トランシーバ250Rは制御部側第2トランシーバである。また、インターフェース機器150は、第1トランシーバ150Lおよび第2トランシーバ150Rを有しており、第1トランシーバ150Lは、第1トランシーバ250L(制御部側第1トランシーバ)と対をなすエンコーダ装置側第1トランシーバであり、第2トランシーバ150Rは、第2トランシーバ250R(制御部側第2トランシーバ)と対をなすエンコーダ装置側第2トランシーバである。伝送路300には、第1トランシーバ150L、250Lを接続する第1伝送路300Lと、第2トランシーバ150R、250Rを接続する第2伝送路300Rとが構成されている。なお、インターフェース機器150、250に用いたRS485機器は、電源電位Vddとグランド電位GNDを抵抗分割した2つの電位を用いた差動式であるため、第1伝送路300Lおよび第2伝送路300Rは各々、2本の配線により構成されている。従って、図6では、第1伝送路300Lおよび第2伝送路300Rの各々を構成する2本の配線のうち、一方側の配線で伝送される信号(第1指令信号MR−QL/同期信号CLK、第2指令信号MR−QR/演算結果DATA)の末尾には「+」を付し、他方側の配線で伝送される信号の末尾には、反転信号を意味する「−」を付してある。

【0045】

このように構成したエンコーダ搭載機器1000において、制御部210側の第1トランシーバ250Lは、指令信号として第1演算処理部11Lでの演算結果DATA−Lが送信されるタイミングを規定する第1指令信号MR−QLを送信するシリアルドライバ251Lと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)が送信されるタイミングに同期する同期信号CLKを受信するシリアルレシーバ252Lとを備えている。

【0046】

制御部210側の第2トランシーバ250Rは、指令信号として第2演算処理部11Rでの演算結果DATA−Rが送信されるタイミングを規定する第2指令信号MR−QRを第1指令信号MR−QLと異なるタイミングで送信するシリアルドライバ251Rと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)を受信するシリアルレシーバ252Rとを備えている。

【0047】

エンコーダ装置100側の第1トランシーバ150Lは、第1指令信号MR−QLを受信するシリアルレシーバ152Lと、同期信号CLKを送信するシリアルドライバ151Lとを備えている。

【0048】

エンコーダ装置100側の第2トランシーバ150Rは、第2指令信号MR−QRを受信するシリアルレシーバ152Rと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)をシリアル信号として送信するシリアルドライバ151Rとを備えている。

【0049】

図6(b)を参照しながらインターフェース機器150、250の動作を説明して、インターフェース機器150、250の構成を詳述する。なお、以下に説明において、制御部210側の信号には「CTRL」を付し、エンコーダ装置100側の信号には「ENC」を付してある。

【0050】

図1および図6に示すように、時間t1〜t4の期間T1では、機器本体200側において、上位の制御部(図示せず)から制御部210の第1トランシーバ250Lのシリアルドライバ251Lに制御信号D/R−1(CTRL)が供給される。その結果、第1トランシーバ250Lがドライブ状態となる。その間、他のトランシーバ(第2トランシーバ250R、第1トランシーバ150Lおよび第2トランシーバ150R)はレシーブ状態にある。

【0051】

この状態で、時間t1〜t4の期間T1のうち、時間t2〜t3の期間T2では、機器本体200側において、上位の制御部(図示せず)から制御部210の第1トランシーバ250Lのシリアルドライバ151Lに第1指令信号MR−QL(CTRL)が供給される。その結果、第1トランシーバ250Lから第1指令信号MR−QLが第1伝送路300Lを介してエンコーダ装置100側の第1トランシーバ150Lのシリアルレシーバ152Lに送信される。

【0052】

次に、時間t5〜t8の期間T3では、エンコーダ装置100側において、第1指令信号MR−QLに基づき、第1トランシーバ150Lのシリアルドライバ151Lおよび第2トランシーバ150Rのシリアルドライバ151Rに制御信号D/R−1(ENC)、D/R−2(ENC)が供給される。その結果、第1トランシーバ150Lおよび第2トランシーバ150Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250Lおよび第2トランシーバ250R)はレシーブ状態にある。

【0053】

この状態で、時間t5〜t8の期間T3のうち、時間t6〜t7の期間T4では、エンコーダ装置100側において、第1指令信号MR−QLに基づき、第1トランシーバ150Lのシリアルドライバ151Lに同期信号CLK(ENC)が供給され、第2トランシーバ150Rのシリアルドライバ151Rに第1演算処理部11Lでの演算結果DATA−L(演算結果DATA(ENC))が供給される。その結果、第1トランシーバ150Lのシリアルドライバ151Lは、第1伝送路300Lを介して第1トランシーバ250Lのシリアルレシーバ252Lに同期信号CLKを送信し、第2トランシーバ150Rのシリアルドライバ151Rは、第2伝送路300Rを介して第2トランシーバ250Rのシリアルレシーバ252Rに第1演算処理部11Lでの演算結果DATA−Lを送信する。

【0054】

従って、機器本体200の側において、上位の制御部は、第1トランシーバ250Lのシリアルレシーバ252Lから出力された同期信号CLK(CTRL)、および第2トランシーバ250Rのシリアルレシーバ252Rから出力された演算結果DATA(CTRL)に基づいて、第1演算処理部11Lでの演算結果DATA−Lを取得することになる。

【0055】

次に、時間t9〜t12の期間T5において、機器本体200側において、上位の制御部(図示せず)から制御部210の第2トランシーバ250Rのシリアルドライバ251Rに制御信号D/R−2(CTRL)が供給される。その結果、第2トランシーバ250Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250L、第1トランシーバ150Lおよび第2トランシーバ150R)はレシーブ状態にある。

【0056】

この状態で、時間t9〜t12の期間T5のうち、時間t10〜t11の期間T6では、機器本体200側において、上位の制御部(図示せず)から制御部210の第2トランシーバ250Rのシリアルドライバ151Rに第2指令信号MR−QR(CTRL)が供給される。その結果、第2トランシーバ250Rから第2指令信号MR−QRが第2伝送路300Rを介してエンコーダ装置100側の第2トランシーバ150Rのシリアルレシーバ152Rに送信される。

【0057】

次に、時間t13〜t16の期間T7では、エンコーダ装置100側において、第2指令信号MR−QRに基づき、第1トランシーバ150Lのシリアルドライバ151Lおよび第2トランシーバ150Rのシリアルドライバ151Rに制御信号D/R−1(ENC)、D/R−2(ENC)が供給され、第1トランシーバ150Lおよび第2トランシーバ150Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250Lおよび第2トランシーバ250R)はレシーブ状態にある。

【0058】

この状態で、時間t13〜t16の期間T7のうち、時間t14〜t15の期間T8では、エンコーダ装置100側において、第2指令信号MR−QRに基づき、第1トランシーバ150Lのシリアルドライバ151Lに同期信号CLK(ENC)が供給され、第2トランシーバ150Rのシリアルドライバ151Rに第2演算処理部11Rでの演算結果DATA−R(演算結果DATA(ENC))が供給される。その結果、第1トランシーバ150Lのシリアルドライバ151Lは、第1伝送路300Lを介して第1トランシーバ250Lのシリアルレシーバ252Lに同期信号CLKを送信し、第2トランシーバ150Rのシリアルドライバ151Rは、第2伝送路300Rを介して第2トランシーバ250Rのシリアルレシーバ252Rに第2演算処理部11Rでの演算結果DATA−Rを送信する。

【0059】

従って、機器本体200の側において、上位の制御部は、第1トランシーバ250Lのシリアルレシーバ252Lから出力された同期信号CLK、および第2トランシーバ250Rのシリアルレシーバ252Rから出力された演算結果DATA(CTRL)に基づいて、第2演算処理部11Rでの演算結果DATA−Rを取得することになる。

【0060】

(演算結果DATAの送信フレームフォーマット)

図7は、本発明に係るエンコーダ搭載機器1000で送信される演算結果DATAの説明図であり、図7(a)、(b)は、演算結果DATAの送信フレームの説明図、および異常検出の内容を示す説明図である。

【0061】

図6等に示す演算結果DATAの送信フレームフォーマットは、例えば、図7(a)に示す16ビットのデータD0〜D15からなり、かかるデータD0〜D15のうち、例えば、8ビットのデータD0〜D8によって、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)が送信される。従って、データD0〜D15のうち、例えば、3ビットのデータD12〜D14を用いれば、エンコーダ1での異常検出結果を送信することもできる。かかる異常検出結果とは、例えば、図7(b)に示すように、図2(c)に示す感磁素子6からの出力信号を円として表したとき、かかる円(実線Gで示す円)が3つの斜線領域E1、E2、E3の何れかに重なったときである。すなわち、円が斜線領域E1に重なったときには、磁気スケール2とセンサユニット5とが離間し過ぎた状態に相当し、円が斜線領域E2、E3に重なったときには、磁気スケール2の中心とセンサユニット5の中心とが大きくずれた場合に相当する。

【0062】

(本形態の主な効果)

以上説明したように、本形態のエンコーダ装置100およびエンコーダ搭載機器1000では、エンコーダ装置100側および制御部210側に同期式の半2重シリアル通信用のインターフェース機器150、250を設けてある。このため、制御部210は、複数の演算処理部11での演算結果が各々送信されるタイミングを規定する指令信号(第1指令信号MR−QLおよび第2指令信号MR−QR)を異なるタイミングで送信する一方、エンコーダ装置100は、指令信号に対応するタイミングで複数の演算処理部11での演算結果DATA、および複数の演算処理部11での演算結果が出力されるタイミングに対応する同期信号CLKを各々、シリアル信号として出力する、従って、制御部210は、同期信号CLKに基づいてエンコーダ1毎の検出結果を取得することができる。また、エンコーダ装置100では、指令信号に基づいて同期信号CLKおよびエンコーダ1毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダ1の検出結果を伝送することができる。

【0063】

また、本形態においては、エンコーダ装置100側および制御部210側の同期式の半2重シリアル通信用のインターフェース機器150、250として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダ1の検出結果を伝送することができる。

【0064】

[他の実施の形態]

上記実施の形態のエンコーダ1に対して、磁気スケール2の中心からみて90°ずれた位置に第1ホール素子および第2ホール素子を配置すれば、現在位置が正弦波信号sin、cosのいずれの区間に位置するかが分かるので、回転体の絶対角度位置情報を生成することができる。かかるアブソリュート動作を行うエンコーダ装置100を用いた場合に本発明を適用してもよい。

【0065】

上記実施の形態では、エンコーダ1として磁気式エンコーダを用いた例を説明したが、エンコーダとして光学式エンコーダを用いた場合に本発明を適用してもよい。

【0066】

また、上記実施の形態では、エンコーダ1が2つの場合を説明したが、トランシーバの数を増やして、エンコーダ1が3つ以上の場合に本発明を適用してもよい。

【符号の説明】

【0067】

1 エンコーダ

2 磁気スケール

5 センサユニット

6 感磁素子(磁気抵抗素子)

100 エンコーダ装置

150 インターフェース機器(エンコーダ装置側インターフェース機器)

150L 第1トランシーバ(エンコーダ装置側第1トランシーバ)

150R 第2トランシーバ(エンコーダ装置側第2トランシーバ)

151L、151R、251L、251R シリアルドライバ

152L、152R、252L、252R シリアルレシーバ

210 制御部

250 インターフェース機器(制御部側インターフェース機器)

250L 第1トランシーバ(制御部側第1トランシーバ)

250R 第2トランシーバ(制御部側第2トランシーバ)

300 伝送路

1000 エンコーダ搭載機器

CLK 同期信号

DATA 演算結果

DATA−L 第1演算処理部での演算結果

DATA−R 第2演算処理部での演算結果

MR−QL 第1指令信号

MR−QR 第2指令信号

【技術分野】

【0001】

本発明は、複数のエンコーダを備えたエンコーダ搭載機器、および複数のエンコーダを備えたエンコーダ装置に関するものである。

【背景技術】

【0002】

エンコーダ装置は、固定体に対する移動体の移動を検出する装置であり、概ね、エンコーダと、エンコーダからの出力に演算処理を行う演算処理部とによって構成されている。かかるエンコーダは、電子フィーダ部品装置やプリンタ等の機器において複数設けられて、複数の移動体の動作を各々監視するために用いられることもある(特許文献1、2参照)。

【0003】

このような場合、複数のエンコーダに対して一対一の関係をもって複数の演算処理部が設けられることになる。また、エンコーダ装置は、機器本体と別体に構成される場合が多く、この場合、複数の演算処理部での演算結果は、伝送路を介して機器本体の制御部に伝送されることになる。その際、複数の演算処理部での演算結果を機器本体の制御部にパラレル伝送する方式を採用すると、回路規模が増大しコストが増大する。

【0004】

そこで、エンコーダ装置側において、制御部側から出力された共通のリクエスト信号に応じて各演算処理部での演算結果を送信する開始時間を相違させて、演算結果をシリアル出力する構成が提案されている(特許文献3参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2011−60809号公報

【特許文献2】特開平09−258513号公報

【特許文献3】特開平8−233607号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、特許文献3に記載の構成では、共通のリクエスト信号をデコード化して自己認識番号に応じてエンコーダ信号を読み出す必要がある等、シリアル通信を用いた割には回路規模が増大しコストが増大するという問題点がある。

【0007】

以上の問題点に鑑みて、本発明の課題は、簡素な回路構成で、複数のエンコーダの検出結果を伝送することのできるエンコーダ搭載機器、およびエンコーダ装置を提供することにある。

【課題を解決するための手段】

【0008】

上記の課題を解決するために、本発明は、複数のエンコーダ、および該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部を備えたエンコーダ装置と、該エンコーダ装置に対する制御部と、前記エンコーダ装置と前記制御部とを接続する伝送路と、を有するエンコーダ搭載機器において、前記制御部は、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として受信する同期式の半2重シリアル通信用の制御部側インターフェース機器を有し、前記エンコーダ装置は、前記指令信号を受信するとともに、当該指令信号に基づいて前記複数の演算処理部での演算結果および前記同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のエンコーダ装置側インターフェース機器を有していることを特徴とする。

【0009】

本発明では、エンコーダ装置側および制御部側に同期式の半2重シリアル通信用のインターフェース機器を設け、制御部は、複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信する一方、エンコーダ装置は、指令信号に基づいて複数の演算処理部での演算結果、および複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号の各々をシリアル信号として出力する。このため、制御部は、同期信号に基づいてエンコーダ毎の検出結果を取得することができる。また、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができる。

【0010】

本発明において、前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、前記制御部側インターフェース機器は、制御部側第1トランシーバと制御部側第2トランシーバと、を備え、前記エンコーダ装置側インターフェース機器は、前記制御部側第1トランシーバと対をなすエンコーダ装置側第1トランシーバと、前記制御部側第2トランシーバと対をなすエンコーダ装置側第2トランシーバと、を備え、前記制御部側第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する前記同期信号を受信するシリアルレシーバと、を備え、前記制御部側第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を前記第1指令信号と異なるタイミングで送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を受信するシリアルレシーバと、を備え、前記エンコーダ装置側第1トランシーバは、前記第1指令信号を受信するシリアルレシーバと、前記同期信号を送信するシリアルドライバと、を備え、前記エンコーダ装置側第2トランシーバは、前記第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果をシリアル信号として送信するシリアルドライバと、を備えていることが好ましい。かかる構成によれば、エンコーダ装置側および制御部側の同期式の半2重シリアル通信用のインターフェース機器として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダの検出結果を伝送することができる。

【0011】

また、本発明に係るエンコーダ装置は、複数のエンコーダと、該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部と、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号をシリアル信号として受信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のインターフェース機器と、を有していることを特徴とする。

【0012】

本発明において、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができる。

【0013】

本発明において、前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、前記インターフェース機器は、第1トランシーバと第2トランシーバとを備え、前記第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する同期信号を送信するシリアルドライバと、を備え、前記第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を送信するシリアルドライバと、を備えていることが好ましい。かかる構成によれば、同期式の半2重シリアル通信用のインターフェース機器として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダの検出結果を伝送することができる。

【0014】

本発明において、前記複数のエンコーダは、例えば、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えている。

【発明の効果】

【0015】

本発明において、エンコーダ装置では、指令信号に基づいて同期信号およびエンコーダ毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダの検出結果を伝送することができるので、コストを低減することができる。

【図面の簡単な説明】

【0016】

【図1】本発明を適用したエンコーダ搭載機器の説明図である。

【図2】本発明に係るエンコーダ装置の基本構成等を示す説明図である。

【図3】本発明に係るエンコーダ装置に用いた感磁素子の磁気抵抗パターンの電気的な接続構造の説明図である。

【図4】本発明を適用したエンコーダ装置のエンコーダの具体的構成例を示す説明図である。

【図5】本発明に係るエンコーダ装置に用いた感磁素子の説明図である。

【図6】本発明に係るエンコーダ搭載機器に用いたインターフェース機器等の説明図である。

【図7】本発明に係るエンコーダ搭載機器で送信される演算結果の説明図である。

【発明を実施するための形態】

【0017】

以下に、図面を参照して、本発明を適用したエンコーダ搭載機器およびエンコーダ装置を説明する。なお、本発明では、エンコーダとしてロータリエンコーダおよびリニアエンコーダを用いることができるが、以下の説明では、エンコーダとしてロータリエンコーダを用いた場合を説明する。また、ロータリエンコーダにおいて、固定体に対する回転体の回転を検出するにあたっては、固定体に磁気スケールを設け、回転体に感磁素子(センサユニット)を設けた構成、および固定体に感磁素子(センサユニット)を設け、回転体に磁気スケールを設けた構成のいずれの構成を採用してもよいが、以下の説明では、固定体に感磁素子(センサユニット)を設け、回転体に磁気スケールを設けた構成を中心に説明する。また、以下に参照する図面において、マグネットおよび感磁素子等の構成について模式的に示してある。

【0018】

(エンコーダ搭載機器の全体構成)

図1は、本発明を適用したエンコーダ搭載機器の説明図であり、図1(a)、(b)は、エンコーダ搭載機器の主要部の構成を示す説明図、制御部側のインターフェース機器の説明図である。

【0019】

図1に示すエンコーダ搭載機器1000は、電子フィーダ部品装置やプリンタ等の機器であり、図示を省略するが、エンコーダ搭載機器1000は、複数のアクチュエータと、これらのアクチュエータの各々によって駆動される複数の回転軸とを有している。かかるエンコーダ搭載機器1000では、複数の回転軸が同期して回転するように、複数の回転軸の各々の回転を複数のエンコーダ1で検出し、かかる複数のエンコーダ1での検出結果に基づいて、機器本体200は、複数のアクチュエータを制御する。

【0020】

ここで、複数のエンコーダ1は、エンコーダ1に対する信号処理部10とともにエンコーダ装置100を構成しており、信号処理部10は、複数のエンコーダ1に対して一対一で対応する複数の演算処理部11を有している。ここで、エンコーダ装置100は、制御部210を備えた機器本体200とは別体に構成されている。このため、エンコーダ装置100と機器本体200の制御部210とは伝送路300を介して接続されており、エンコーダ装置100は、制御部210から伝送路300を介して送信される指令に基づいて、複数の演算処理部11での演算結果を、伝送路300を介して制御部210に出力する。

【0021】

本形態において、エンコーダ装置100は、複数のエンコーダ1として、第1エンコーダ1Lと第2エンコーダ1Rとを有しており、それ故、信号処理部10は、複数の演算処理部11として、第1エンコーダ1Lでの検出結果に演算処理を行う第1演算処理部11Lと、第2エンコーダ1Rでの検出結果に演算処理を行う第2演算処理部11Rとを有している。また、エンコーダ装置100および制御部210は各々、伝送路300を介して通信を行うためのインターフェース機器150、250およびコネクタ180、280を有している。かかるインターフェース機器150、250を用いての通信の内容は、図6等を参照して後述する。

【0022】

(エンコーダ装置100の構成)

図2は、本発明に係るエンコーダ装置100の基本構成等を示す説明図であり、図2(a)、(b)、(c)は、磁気スケールと感磁素子との位置関係等を模式的に示す説明図、感磁素子からの出力信号の説明図、および感磁素子からの出力信号と回転体の角度位置θ(電気角)との関係を示す説明図である。図3(a)、(b)は、本発明に係るエンコーダ装置100に用いた感磁素子の磁気抵抗パターンの電気的な接続構造の説明図である。なお、本形態において、2つのエンコーダ1(第1エンコーダ1Lと第2エンコーダ1R)の構成は同一であるため、第1を意味する「L」や第2意味する「R」等を付さずに説明する。

【0023】

図2に示すように、本形態のエンコーダ装置100において、複数のエンコーダ1は各々、磁気スケール2およびセンサユニット5を有している。本形態において、磁気スケール2は回転体側に設けられ、センサユニット5は固定体側に設けられている。磁気スケール2は、N極とS極とが周方向において交互に着磁された磁気トラック31を回転軸線方向Lの一方側L1に向けており、センサユニット5は、磁気トラック31に対して回転軸線方向Lの一方側L1で対向する感磁素子6(センサ素子)を備えている。磁気トラック31には、トラック311、312が2列、同心状に並列して形成されている。かかる磁気トラック31において、2つのトラック311、312の間ではN極およびS極の位置が周方向でずれており、本形態では、2つのトラック311、312の間においてN極およびS極が周方向に1極分ずれている。

【0024】

感磁素子6は、磁気抵抗素子であり、磁気トラック31の位相に対して、互いに90°の位相差を有するA相(SIN)の磁気抵抗パターンとB相(COS)の磁気抵抗パターンとを備えている。かかる感磁素子(磁気抵抗素子)において、A相の磁気抵抗パターンは、180°の位相差をもって回転体の移動検出を行う+a相(SIN+)の磁気抵抗パターン64および−a相(SIN-)の磁気抵抗パターン62を備えており、B相の磁気抵抗パターンは、180°の位相差をもって回転体の移動検出を行う+b相(COS+)の磁気抵抗パターン63および−b相(COS-)の磁気抵抗パターン61を備えている。

【0025】

図3(a)に示すように、+a相の磁気抵抗パターン64および−a相の磁気抵抗パターン62はブリッジ回路を構成しており、一方端が電源端子(Vcc)に接続され、他方端がグランド端子(GND)に接続されている。また、+a相の磁気抵抗パターン64の中点位置には、+a相が出力される端子(+a)が設けられ、−a相の磁気抵抗パターン62の中点位置には、−a相が出力される端子(−a)が設けられている。

【0026】

図3(b)に示すように、+b相の磁気抵抗パターン63および−b相の磁気抵抗パターン61も、+a相の磁気抵抗パターン64および−a相の磁気抵抗パターン62と同様、ブリッジ回路を構成しており、一方端が電源端子(Vcc)に接続され、他方端がグランド端子(GND)に接続されている。また、+b相の磁気抵抗パターン63の中点位置には、+b相が出力される端子(+b)が設けられ、−b相の磁気抵抗パターン61の中点位置には、−b相が出力される端子(−b)が設けられている。

【0027】

再び図2において、感磁素子6は、磁気トラック31において隣接するトラック311、312の境界部分313に回転軸線方向Lで重なる位置に配置されている。このため、感磁素子6の磁気抵抗パターン61〜64は、各磁気抵抗パターン61〜64の抵抗値の飽和感度領域以上の磁界強度で磁気トラック31の面内方向で向きが変化する回転磁界を検出することができる。すなわち、隣接するトラック311、312の境界部分313においては、各磁気抵抗パターン61〜64の抵抗値の飽和感度領域以上の磁界強度でトラック311、312の面内方向の向きが周方向で漸次に変化する回転磁界が発生する。飽和感度領域とは、一般的に、抵抗値変化量kが、磁界強度Hと近似的に「k∝H2」の式で表すことができる領域以外の領域をいう。また、飽和感度領域以上の磁界強度で回転磁界(磁気ベクトルの回転)の方向を検出する際の原理は、強磁性金属からなる磁気抵抗パターン61〜64に通電した状態で、抵抗値が飽和する磁界強度を印加したとき、磁界と電流方向がなす角度θと、磁気抵抗パターン61〜64の抵抗値Rとの間には、下式

R=R0−k×sin2θ

R0:無磁界中での抵抗値

k:抵抗値変化量(飽和感度領域以上のときは定数)

で示す関係があることを利用するものである。このような原理に基づいて回転磁界を検出すれば、角度θが変化すると抵抗値Rが正弦波に沿って変化するので、波形品質の高いA相およびB相を得ることができる。

【0028】

かかる構成のエンコーダ装置100において、エンコーダ1の感磁素子6に対しては信号処理部10が接続されており、信号処理部10は、増幅回路13、14を備えた増幅回路部12や、これらの増幅回路13、14から出力される正弦波信号sin、cosに補間処理や各種演算処理を行う演算処理部11等が設けられており、感磁素子6からの出力に基づいて、固定体に対する回転体の回転速度、回転方向、角度位置が検出される。より具体的には、エンコーダ装置100において、回転体が磁極の1周期分回転すると、感磁素子6からは、図2(b)に示す正弦波信号sin、cosが2周期分、出力される。従って、正弦波信号sin、cosを増幅回路13、14により増幅した後、演算処理部11において、図2(c)に示すように、正弦波信号sin、cosからθ=tan-1(sin/cos)を求めれば、回転体の角度位置θが分かる。

【0029】

(エンコーダ1の具体的構成)

図4は、本発明を適用したエンコーダ装置100のエンコーダ1の具体的構成例を示す説明図であり、図4(a)、(b)、(c)、(d)は、エンコーダ1の側面図、磁気スケール2をセンサユニット5の側から見た斜視図、磁気スケール2の磁気トラック31の説明図、およびセンサユニット5の斜視図である。なお、図4(d)には感磁素子6の表面からシールドテープを剥がした様子を示してある。

【0030】

図4(a)、(b)、(d)に示すように、エンコーダ1において、磁気スケール2およびセンサユニット5はいずれも円環状であり、回転体の回転軸線方向Lで対向し、かつ、磁気スケール2の中心O2、およびセンサユニット5の中心O5が回転体の回転軸線方向L上に位置するように配置されている。

【0031】

図4(b)に示すように、磁気スケール2は、SPPC(冷間圧延鋼板)等の金属製の円環状のヨーク板20と、このヨーク板20の表面(センサユニット5が位置する側)に固定された円環状のセンサマグネット30とを備えており、図4(c)に示すように、センサマグネット30の表面(着磁されている面33)には周方向に延びる円環状の磁気トラック31が設けられている。磁気トラック31は半径方向に並列して周方向に延びる内側のトラック311と外側のトラック312とからなる。これらトラック311、312は着磁ヘッドによってセンサマグネット30に対する着磁を行うことにより設けられる。

【0032】

図4(b)に点線で示すように、センサマグネット30の着磁表面には、ステンレス等の非磁性材料からなる円環状の保護シート40が取り付けられている。本例では、磁気トラック31は周方向に90分割されてN極とS極が交互に着磁されており、各磁極が着磁されている角度範囲は4°である。また、各S極および各N極の平面形状は外周から内周側に向けて幅が狭くなる扇形となっている。なお、磁気スケール2から保護シート40を省略することも可能である。

【0033】

図4(a)、(d)に示すように、センサユニット5は、亜鉛ダイカスト品やアルミニウムダイカスト品からなる円環状のホルダ8と、このホルダ8の裏面側(磁気スケール2が位置する側とは反対側)に取り付けられた剛性の回路基板7と、回路基板7に電気的に接続された可撓性基板9と、可撓性基板9に電気的に接続された感磁素子6とを備えており、感磁素子6において磁気スケール2が位置する側の面がセンサ面6aである。回路基板7には、回路基板7からの出力を、図2(a)に示す信号処理部10に出力するコネクタ15が実装されている。感磁素子6のセンサ面6aには、電気ノイズ対策として金属製のシールドテープが貼り付けられており、センサ面6aはシールドテープによって覆われている。

【0034】

(感磁素子6の具体的構成例)

図5は、本発明に係るエンコーダ装置100に用いた感磁素子6の説明図であり、図5(a)、(b)は、感磁素子6の平面図、および感磁素子6における磁気抵抗パターンの積層状態を模式的に示す説明図である。なお、図5(a)では、各磁気抵抗パターンと重ねて各磁気抵抗パターンと対向配置されるトラック311、312を表してある。

【0035】

図5において、本形態で用いた感磁素子6は、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は、層間絶縁膜を介して積層された第1積層磁気抵抗パターン601として素子基板60の主面60a上に形成されており、素子基板60の主面60a側がセンサ面6aである。+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は各々、磁気トラック31の半径方向においては、その中心がトラック311、312の境界部分313に対向して配置されており、磁気トラック31の周方向においては、+a相の磁気抵抗パターン64(SIN+)が検出する+a相と+b相の磁気抵抗パターン63(COS+)が検出する+b相が最小位相差となる最小機械角度ずれた位置に配置されている。すなわち、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)は、磁気スケール2から得られる同一の波長を90°の位相差で検出可能な角度位置に配置されている。本例では、+a相の磁気抵抗パターン64(SIN+)と+b相の磁気抵抗パターン63(COS+)は周方向で1°ずれた位置に配置されている。なお、本形態では、図5(b)に示すように、素子基板60の主面60a上に+b相の磁気抵抗パターン63(COS+)が形成され、+a相の磁気抵抗パターン64(SIN+)がその上に積層されている。なお、最小位相差とは90°の位相差であり、+a相の磁気抵抗パターン64(SIN+)と+b相の磁気抵抗パターン63(COS+)の上下関係は逆でもよい。

【0036】

−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)も、+a相の磁気抵抗パターン64(SIN+)、および+b相の磁気抵抗パターン63(COS+)と同様、層間絶縁膜を介して積層された第2積層磁気抵抗パターン602として素子基板60の主面60a上に形成されている。−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)は各々、磁気トラック31の半径方向においては、その中心がトラック311、312の境界部分313に対向して配置されており、磁気トラック31の周方向においては、−a相の磁気抵抗パターン62(SIN-)が検出する−a相と−b相の磁気抵抗パターン61(COS-)が検出する−b相とが最小位相差となる最小機械角度ずれた位置に配置されている。すなわち、−a相の磁気抵抗パターン62(SIN-)、および−b相の磁気抵抗パターン61(COS-)は、磁気スケール2から得られる同一の波長を90°の位相差で検出可能な角度位置に配置されている。本例では、−a相の磁気抵抗パターン62(SIN-)と−b相の磁気抵抗パターン61(COS-)は周方向で1°ずれた位置に配置されている。なお、本形態では、図5(b)に示すように、素子基板60の主面60a上に−a相の磁気抵抗パターン62(SIN-)が形成され、−b相の磁気抵抗パターン61(COS-)がその上に積層されている。なお、最小位相差とは90°の位相差であり、−a相の磁気抵抗パターン62(SIN-)と−b相の磁気抵抗パターン61(COS-)の積層関係は逆でもよい。

【0037】

次に、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602は、周方向で重ならない位置に配置されている。より詳細には、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602は、第1積層磁気抵抗パターン601の+a相の磁気抵抗パターン64(SIN+)から検出される+a相と、第2積層磁気抵抗パターン602の−a相の磁気抵抗パターン62(SIN-)から検出される−a相が180°の位相差となる位置であり、第1積層磁気抵抗パターン601の+b相の磁気抵抗パターン63(COS+)から検出される+b相と、第2積層磁気抵抗パターン602の−b相の磁気抵抗パターン61(COS-)から検出される−b相とが180°の位相差となる位置に配置されている。さらに、第1積層磁気抵抗パターン601と第2積層磁気抵抗パターン602が電気的或いは磁気的に干渉しない最小距離だけ離れた角度位置に配置されている。本例では、第1積層磁気抵抗パターン601の+a相の磁気抵抗パターン64(SIN+)と、第2積層磁気抵抗パターン602の−a相の磁気抵抗パターン62(SIN-)は周方向に22°ずれた位置に配置されている。第1積層磁気抵抗パターン601の+b相の磁気抵抗パターン63(COS+)と、第2積層磁気抵抗パターン602の−b相の磁気抵抗パターン61(COS-)も、同様に、周方向に22°ずれた位置に配置されている。

【0038】

ここで、各磁気抵抗パターン61〜64は互いに平行ではなく、図4等に示すホルダ8の中心O8(センサユニット5の中心O5)から径方向に延在する複数の仮想線上に位置しており、ホルダ8およびセンサユニット5の半径方向に延在している。かかる磁気抵抗パターン61〜64は、ガラスあるいはシリコンからなる素子基板60上に、半導体プロセスによって強磁性体NiFe等の磁性体膜を積層することによって形成されている。素子基板60は長方形をしており、各磁気抵抗パターン61〜64は素子基板60の中央領域に形成されている。素子基板60の端部には、一方の長辺に沿って複数の端子68が形成されており、かかる端子68は、図4等に示す可撓性基板9との電気的な接続に用いられている。また、各磁気抵抗パターン61〜64は、端子68を避けるように形成されたエポキシ樹脂等の保護層(図示せず)によって覆われており、かかる保護層は、例えば、スクリーン印刷によって形成されている。

【0039】

(磁気スケール2の詳細構成)

図4(b)において、磁気スケール2は、円環状のヨーク板20と、このヨーク板20の表面(センサユニット5が位置する側)に固定した円環状のセンサマグネット30とを備えている。ヨーク板20は、センサマグネット30より幅寸法が大であり、ヨーク板20の内周部分21は、センサマグネット30の内周縁35より内側に位置し、ヨーク板20の外周部分22は、センサマグネット30の外周縁32より外側に位置している。従って、磁気スケール2の円形の外周縁および円形の内周縁は、ヨーク板20の内周部分21および外周部分22に相当する。

【0040】

かかる構成の磁気スケール2において、センサマグネット30は、ヨーク板20の円形状を基準に着磁されている。より具体的には、センサマグネット30は、円環状に成形した磁性体をヨーク板20に接着剤により固定した後、磁性体の表面を研磨し、しかる後に着磁を行って、磁気トラック31を形成することにより、形成されている。かかる着磁の際、本形態では、センサマグネット30(磁性体)の円形状ではなく、ヨーク板20の内周部分21や外周部分22等、ヨーク板20の円形状を基準に着磁されている。このため、磁気スケール2では、磁気トラック31と、ヨーク板20の内周部分21および外周部分22とは、同心状である。

【0041】

ここで、センサマグネット30は、フェライト等の磁性粉(マグネット原料)とPPS(polyphenylene sulfide)等の熱可塑性樹脂材料(プラスチック材料)とを混合して成形したプラスチックマグネットである。本形態において、センサマグネット30は、各種のプラスチックマグネットのうち、フィルムゲート(フラッシュゲート)により成形されたプラスチックマグネットである。かかるフィルムゲートによる成形では、フィルム状(膜状)のゲートを使用し、かつ、このフィルム状のゲートを円環状のセンサマグネット30の内周面となる部分の全周に設けて成形する。

【0042】

(インターフェース機器150、250等の構成)

図6は、本発明に係るエンコーダ搭載機器1000に用いたインターフェース機器150、250等の説明図であり、図6(a)、(b)は、インターフェース機器150、250の具体的構成例を示す説明図、および通信プロトコルの説明図である。

【0043】

図1に示すように、本形態のエンコーダ搭載機器1000では、機器本体200側の制御部210にはインターフェース機器250(制御部側インターフェース機器)が設けられ、エンコーダ装置100側にはインターフェース機器150(エンコーダ装置側インターフェース機器)が設けられている。インターフェース機器150、250はいずれも、同期式の半2重シリアル通信用のインターフェース機器であり、各々、RS485機器等からなるトランシーバを2つずつ有している。

【0044】

より具体的には、図1および図6に示すように、インターフェース機器250は、第1トランシーバ250Lおよび第2トランシーバ250Rを有しており、第1トランシーバ250Lは制御部側第1トランシーバであり、第2トランシーバ250Rは制御部側第2トランシーバである。また、インターフェース機器150は、第1トランシーバ150Lおよび第2トランシーバ150Rを有しており、第1トランシーバ150Lは、第1トランシーバ250L(制御部側第1トランシーバ)と対をなすエンコーダ装置側第1トランシーバであり、第2トランシーバ150Rは、第2トランシーバ250R(制御部側第2トランシーバ)と対をなすエンコーダ装置側第2トランシーバである。伝送路300には、第1トランシーバ150L、250Lを接続する第1伝送路300Lと、第2トランシーバ150R、250Rを接続する第2伝送路300Rとが構成されている。なお、インターフェース機器150、250に用いたRS485機器は、電源電位Vddとグランド電位GNDを抵抗分割した2つの電位を用いた差動式であるため、第1伝送路300Lおよび第2伝送路300Rは各々、2本の配線により構成されている。従って、図6では、第1伝送路300Lおよび第2伝送路300Rの各々を構成する2本の配線のうち、一方側の配線で伝送される信号(第1指令信号MR−QL/同期信号CLK、第2指令信号MR−QR/演算結果DATA)の末尾には「+」を付し、他方側の配線で伝送される信号の末尾には、反転信号を意味する「−」を付してある。

【0045】

このように構成したエンコーダ搭載機器1000において、制御部210側の第1トランシーバ250Lは、指令信号として第1演算処理部11Lでの演算結果DATA−Lが送信されるタイミングを規定する第1指令信号MR−QLを送信するシリアルドライバ251Lと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)が送信されるタイミングに同期する同期信号CLKを受信するシリアルレシーバ252Lとを備えている。

【0046】

制御部210側の第2トランシーバ250Rは、指令信号として第2演算処理部11Rでの演算結果DATA−Rが送信されるタイミングを規定する第2指令信号MR−QRを第1指令信号MR−QLと異なるタイミングで送信するシリアルドライバ251Rと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)を受信するシリアルレシーバ252Rとを備えている。

【0047】

エンコーダ装置100側の第1トランシーバ150Lは、第1指令信号MR−QLを受信するシリアルレシーバ152Lと、同期信号CLKを送信するシリアルドライバ151Lとを備えている。

【0048】

エンコーダ装置100側の第2トランシーバ150Rは、第2指令信号MR−QRを受信するシリアルレシーバ152Rと、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)をシリアル信号として送信するシリアルドライバ151Rとを備えている。

【0049】

図6(b)を参照しながらインターフェース機器150、250の動作を説明して、インターフェース機器150、250の構成を詳述する。なお、以下に説明において、制御部210側の信号には「CTRL」を付し、エンコーダ装置100側の信号には「ENC」を付してある。

【0050】

図1および図6に示すように、時間t1〜t4の期間T1では、機器本体200側において、上位の制御部(図示せず)から制御部210の第1トランシーバ250Lのシリアルドライバ251Lに制御信号D/R−1(CTRL)が供給される。その結果、第1トランシーバ250Lがドライブ状態となる。その間、他のトランシーバ(第2トランシーバ250R、第1トランシーバ150Lおよび第2トランシーバ150R)はレシーブ状態にある。

【0051】

この状態で、時間t1〜t4の期間T1のうち、時間t2〜t3の期間T2では、機器本体200側において、上位の制御部(図示せず)から制御部210の第1トランシーバ250Lのシリアルドライバ151Lに第1指令信号MR−QL(CTRL)が供給される。その結果、第1トランシーバ250Lから第1指令信号MR−QLが第1伝送路300Lを介してエンコーダ装置100側の第1トランシーバ150Lのシリアルレシーバ152Lに送信される。

【0052】

次に、時間t5〜t8の期間T3では、エンコーダ装置100側において、第1指令信号MR−QLに基づき、第1トランシーバ150Lのシリアルドライバ151Lおよび第2トランシーバ150Rのシリアルドライバ151Rに制御信号D/R−1(ENC)、D/R−2(ENC)が供給される。その結果、第1トランシーバ150Lおよび第2トランシーバ150Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250Lおよび第2トランシーバ250R)はレシーブ状態にある。

【0053】

この状態で、時間t5〜t8の期間T3のうち、時間t6〜t7の期間T4では、エンコーダ装置100側において、第1指令信号MR−QLに基づき、第1トランシーバ150Lのシリアルドライバ151Lに同期信号CLK(ENC)が供給され、第2トランシーバ150Rのシリアルドライバ151Rに第1演算処理部11Lでの演算結果DATA−L(演算結果DATA(ENC))が供給される。その結果、第1トランシーバ150Lのシリアルドライバ151Lは、第1伝送路300Lを介して第1トランシーバ250Lのシリアルレシーバ252Lに同期信号CLKを送信し、第2トランシーバ150Rのシリアルドライバ151Rは、第2伝送路300Rを介して第2トランシーバ250Rのシリアルレシーバ252Rに第1演算処理部11Lでの演算結果DATA−Lを送信する。

【0054】

従って、機器本体200の側において、上位の制御部は、第1トランシーバ250Lのシリアルレシーバ252Lから出力された同期信号CLK(CTRL)、および第2トランシーバ250Rのシリアルレシーバ252Rから出力された演算結果DATA(CTRL)に基づいて、第1演算処理部11Lでの演算結果DATA−Lを取得することになる。

【0055】

次に、時間t9〜t12の期間T5において、機器本体200側において、上位の制御部(図示せず)から制御部210の第2トランシーバ250Rのシリアルドライバ251Rに制御信号D/R−2(CTRL)が供給される。その結果、第2トランシーバ250Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250L、第1トランシーバ150Lおよび第2トランシーバ150R)はレシーブ状態にある。

【0056】

この状態で、時間t9〜t12の期間T5のうち、時間t10〜t11の期間T6では、機器本体200側において、上位の制御部(図示せず)から制御部210の第2トランシーバ250Rのシリアルドライバ151Rに第2指令信号MR−QR(CTRL)が供給される。その結果、第2トランシーバ250Rから第2指令信号MR−QRが第2伝送路300Rを介してエンコーダ装置100側の第2トランシーバ150Rのシリアルレシーバ152Rに送信される。

【0057】

次に、時間t13〜t16の期間T7では、エンコーダ装置100側において、第2指令信号MR−QRに基づき、第1トランシーバ150Lのシリアルドライバ151Lおよび第2トランシーバ150Rのシリアルドライバ151Rに制御信号D/R−1(ENC)、D/R−2(ENC)が供給され、第1トランシーバ150Lおよび第2トランシーバ150Rがドライブ状態となる。その間、他のトランシーバ(第1トランシーバ250Lおよび第2トランシーバ250R)はレシーブ状態にある。

【0058】

この状態で、時間t13〜t16の期間T7のうち、時間t14〜t15の期間T8では、エンコーダ装置100側において、第2指令信号MR−QRに基づき、第1トランシーバ150Lのシリアルドライバ151Lに同期信号CLK(ENC)が供給され、第2トランシーバ150Rのシリアルドライバ151Rに第2演算処理部11Rでの演算結果DATA−R(演算結果DATA(ENC))が供給される。その結果、第1トランシーバ150Lのシリアルドライバ151Lは、第1伝送路300Lを介して第1トランシーバ250Lのシリアルレシーバ252Lに同期信号CLKを送信し、第2トランシーバ150Rのシリアルドライバ151Rは、第2伝送路300Rを介して第2トランシーバ250Rのシリアルレシーバ252Rに第2演算処理部11Rでの演算結果DATA−Rを送信する。

【0059】

従って、機器本体200の側において、上位の制御部は、第1トランシーバ250Lのシリアルレシーバ252Lから出力された同期信号CLK、および第2トランシーバ250Rのシリアルレシーバ252Rから出力された演算結果DATA(CTRL)に基づいて、第2演算処理部11Rでの演算結果DATA−Rを取得することになる。

【0060】

(演算結果DATAの送信フレームフォーマット)

図7は、本発明に係るエンコーダ搭載機器1000で送信される演算結果DATAの説明図であり、図7(a)、(b)は、演算結果DATAの送信フレームの説明図、および異常検出の内容を示す説明図である。

【0061】

図6等に示す演算結果DATAの送信フレームフォーマットは、例えば、図7(a)に示す16ビットのデータD0〜D15からなり、かかるデータD0〜D15のうち、例えば、8ビットのデータD0〜D8によって、演算処理部11での演算結果DATA(第1演算処理部11Lでの演算結果DATA−Lおよび第2演算処理部11Rでの演算結果DATA−R)が送信される。従って、データD0〜D15のうち、例えば、3ビットのデータD12〜D14を用いれば、エンコーダ1での異常検出結果を送信することもできる。かかる異常検出結果とは、例えば、図7(b)に示すように、図2(c)に示す感磁素子6からの出力信号を円として表したとき、かかる円(実線Gで示す円)が3つの斜線領域E1、E2、E3の何れかに重なったときである。すなわち、円が斜線領域E1に重なったときには、磁気スケール2とセンサユニット5とが離間し過ぎた状態に相当し、円が斜線領域E2、E3に重なったときには、磁気スケール2の中心とセンサユニット5の中心とが大きくずれた場合に相当する。

【0062】

(本形態の主な効果)

以上説明したように、本形態のエンコーダ装置100およびエンコーダ搭載機器1000では、エンコーダ装置100側および制御部210側に同期式の半2重シリアル通信用のインターフェース機器150、250を設けてある。このため、制御部210は、複数の演算処理部11での演算結果が各々送信されるタイミングを規定する指令信号(第1指令信号MR−QLおよび第2指令信号MR−QR)を異なるタイミングで送信する一方、エンコーダ装置100は、指令信号に対応するタイミングで複数の演算処理部11での演算結果DATA、および複数の演算処理部11での演算結果が出力されるタイミングに対応する同期信号CLKを各々、シリアル信号として出力する、従って、制御部210は、同期信号CLKに基づいてエンコーダ1毎の検出結果を取得することができる。また、エンコーダ装置100では、指令信号に基づいて同期信号CLKおよびエンコーダ1毎の検出結果を出力すればよく、指令信号をデコード化する等の処理が不要である。このため、簡素な回路構成で複数のエンコーダ1の検出結果を伝送することができる。

【0063】

また、本形態においては、エンコーダ装置100側および制御部210側の同期式の半2重シリアル通信用のインターフェース機器150、250として、2つのトランシーバを備えた機器を設ければよいので、簡素な回路構成で2つのエンコーダ1の検出結果を伝送することができる。

【0064】

[他の実施の形態]

上記実施の形態のエンコーダ1に対して、磁気スケール2の中心からみて90°ずれた位置に第1ホール素子および第2ホール素子を配置すれば、現在位置が正弦波信号sin、cosのいずれの区間に位置するかが分かるので、回転体の絶対角度位置情報を生成することができる。かかるアブソリュート動作を行うエンコーダ装置100を用いた場合に本発明を適用してもよい。

【0065】

上記実施の形態では、エンコーダ1として磁気式エンコーダを用いた例を説明したが、エンコーダとして光学式エンコーダを用いた場合に本発明を適用してもよい。

【0066】

また、上記実施の形態では、エンコーダ1が2つの場合を説明したが、トランシーバの数を増やして、エンコーダ1が3つ以上の場合に本発明を適用してもよい。

【符号の説明】

【0067】

1 エンコーダ

2 磁気スケール

5 センサユニット

6 感磁素子(磁気抵抗素子)

100 エンコーダ装置

150 インターフェース機器(エンコーダ装置側インターフェース機器)

150L 第1トランシーバ(エンコーダ装置側第1トランシーバ)

150R 第2トランシーバ(エンコーダ装置側第2トランシーバ)

151L、151R、251L、251R シリアルドライバ

152L、152R、252L、252R シリアルレシーバ

210 制御部

250 インターフェース機器(制御部側インターフェース機器)

250L 第1トランシーバ(制御部側第1トランシーバ)

250R 第2トランシーバ(制御部側第2トランシーバ)

300 伝送路

1000 エンコーダ搭載機器

CLK 同期信号

DATA 演算結果

DATA−L 第1演算処理部での演算結果

DATA−R 第2演算処理部での演算結果

MR−QL 第1指令信号

MR−QR 第2指令信号

【特許請求の範囲】

【請求項1】

複数のエンコーダ、および該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部を備えたエンコーダ装置と、該エンコーダ装置に対する制御部と、前記エンコーダ装置と前記制御部とを接続する伝送路と、を有するエンコーダ搭載機器において、

前記制御部は、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として受信する同期式の半2重シリアル通信用の制御部側インターフェース機器を有し、

前記エンコーダ装置は、前記指令信号を受信するとともに、当該指令信号に対応するタイミングで前記複数の演算処理部での演算結果および前記同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のエンコーダ装置側インターフェース機器を有していることを特徴とするエンコーダ搭載機器。

【請求項2】

前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、

前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、

前記制御部側インターフェース機器は、制御部側第1トランシーバと制御部側第2トランシーバと、を備え、

前記エンコーダ装置側インターフェース機器は、前記制御部側第1トランシーバと対をなすエンコーダ装置側第1トランシーバと、前記制御部側第2トランシーバと対をなすエンコーダ装置側第2トランシーバと、を備え、

前記制御部側第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する前記同期信号を受信するシリアルレシーバと、を備え、

前記制御部側第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を前記第1指令信号と異なるタイミングで送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を受信するシリアルレシーバと、を備え、

前記エンコーダ装置側第1トランシーバは、前記第1指令信号を受信するシリアルレシーバと、前記同期信号を送信するシリアルドライバと、を備え、

前記エンコーダ装置側第2トランシーバは、前記第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果をシリアル信号として送信するシリアルドライバと、を備えていることを特徴とする請求項1に記載のエンコーダ搭載機器。

【請求項3】

前記複数のエンコーダは、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えていることを特徴とする請求項1または2に記載のエンコーダ搭載機器。

【請求項4】

複数のエンコーダと、

該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部と、

前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号をシリアル信号として受信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のインターフェース機器と、

を有していることを特徴とするエンコーダ装置。

【請求項5】

前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、

前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、

前記インターフェース機器は、第1トランシーバと第2トランシーバとを備え、

前記第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する同期信号を送信するシリアルドライバと、を備え、

前記第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を送信するシリアルドライバと、を備えていることを特徴とする請求項4に記載のエンコーダ装置。

【請求項6】

前記複数のエンコーダは、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えていることを特徴とする請求項4または5に記載のエンコーダ装置。

【請求項1】

複数のエンコーダ、および該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部を備えたエンコーダ装置と、該エンコーダ装置に対する制御部と、前記エンコーダ装置と前記制御部とを接続する伝送路と、を有するエンコーダ搭載機器において、

前記制御部は、前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号を異なるタイミングで送信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として受信する同期式の半2重シリアル通信用の制御部側インターフェース機器を有し、

前記エンコーダ装置は、前記指令信号を受信するとともに、当該指令信号に対応するタイミングで前記複数の演算処理部での演算結果および前記同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のエンコーダ装置側インターフェース機器を有していることを特徴とするエンコーダ搭載機器。

【請求項2】

前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、

前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、

前記制御部側インターフェース機器は、制御部側第1トランシーバと制御部側第2トランシーバと、を備え、

前記エンコーダ装置側インターフェース機器は、前記制御部側第1トランシーバと対をなすエンコーダ装置側第1トランシーバと、前記制御部側第2トランシーバと対をなすエンコーダ装置側第2トランシーバと、を備え、

前記制御部側第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する前記同期信号を受信するシリアルレシーバと、を備え、

前記制御部側第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を前記第1指令信号と異なるタイミングで送信するシリアルドライバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を受信するシリアルレシーバと、を備え、

前記エンコーダ装置側第1トランシーバは、前記第1指令信号を受信するシリアルレシーバと、前記同期信号を送信するシリアルドライバと、を備え、

前記エンコーダ装置側第2トランシーバは、前記第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果をシリアル信号として送信するシリアルドライバと、を備えていることを特徴とする請求項1に記載のエンコーダ搭載機器。

【請求項3】

前記複数のエンコーダは、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えていることを特徴とする請求項1または2に記載のエンコーダ搭載機器。

【請求項4】

複数のエンコーダと、

該複数のエンコーダに対して一対一の関係をもって設けられ、前記複数のエンコーダからの出力に演算処理を行う複数の演算処理部と、

前記複数の演算処理部での演算結果が各々送信されるタイミングを規定する指令信号をシリアル信号として受信するとともに、前記複数の演算処理部での演算結果、および前記複数の演算処理部での演算結果が出力されるタイミングに対応する同期信号を各々、シリアル信号として送信する同期式の半2重シリアル通信用のインターフェース機器と、

を有していることを特徴とするエンコーダ装置。

【請求項5】

前記複数のエンコーダには、第1エンコーダと第2エンコーダとが含まれ、

前記複数の演算処理部には、前記第1エンコーダからの出力に演算処理を行う第1演算処理部と、前記第2エンコーダからの出力に演算処理を行う第2演算処理部とが含まれ、

前記インターフェース機器は、第1トランシーバと第2トランシーバとを備え、

前記第1トランシーバは、前記指令信号として前記第1演算処理部での演算結果が送信されるタイミングを規定する第1指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果が送信されるタイミングに同期する同期信号を送信するシリアルドライバと、を備え、

前記第2トランシーバは、前記指令信号として前記第2演算処理部での演算結果が送信されるタイミングを規定する第2指令信号を受信するシリアルレシーバと、前記第1演算処理部での演算結果および前記第2演算処理部での演算結果を送信するシリアルドライバと、を備えていることを特徴とする請求項4に記載のエンコーダ装置。

【請求項6】

前記複数のエンコーダは、固定体に対する回転体の回転を検出するロータリエンコーダであって、周方向にN極およびS極が配置された磁気トラックを備えた磁気スケールと、該磁気スケールに対して前記回転体の回転中心軸線方向で対向する位置に配置された感磁素子と、を備えていることを特徴とする請求項4または5に記載のエンコーダ装置。

【図2】

【図3】

【図4】

【図5】

【図7】

【図1】

【図6】

【図3】

【図4】

【図5】

【図7】

【図1】

【図6】

【公開番号】特開2013−108838(P2013−108838A)

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願番号】特願2011−253893(P2011−253893)

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000002233)日本電産サンキョー株式会社 (1,337)

【Fターム(参考)】

【公開日】平成25年6月6日(2013.6.6)

【国際特許分類】

【出願日】平成23年11月21日(2011.11.21)

【出願人】(000002233)日本電産サンキョー株式会社 (1,337)

【Fターム(参考)】

[ Back to top ]