オーディオ信号処理装置

【課題】差動回路に入力される2つの信号が同じDA変換回路から出力されるオーディオ信号処理装置を提供する。

【解決手段】オーディオ信号処理装置のDA変換回路の前段にデータ組替回路を設けた。データ組替回路は、第1のデータと第2のデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第3のデータと第4のデータとをワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、第1のデータと第3のデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成する。DA変換回路は、生成された第3のオーディオデータを第1のデータと第3のデータとに分離し、それぞれ第1のアナログ信号および第2のアナログ信号に変換する。差動回路は、第1のアナログ信号と第2のアナログ信号とから第3のアナログ信号を合成する。

【解決手段】オーディオ信号処理装置のDA変換回路の前段にデータ組替回路を設けた。データ組替回路は、第1のデータと第2のデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第3のデータと第4のデータとをワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、第1のデータと第3のデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成する。DA変換回路は、生成された第3のオーディオデータを第1のデータと第3のデータとに分離し、それぞれ第1のアナログ信号および第2のアナログ信号に変換する。差動回路は、第1のアナログ信号と第2のアナログ信号とから第3のアナログ信号を合成する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、入力されるデジタルオーディオ信号をアナログオーディオ信号に変換するオーディオ信号処理装置に関し、特に、複数のオーディオ信号を同時に処理するマルチチャンネルのオーディオ信号処理装置に関する。

【背景技術】

【0002】

デジタルオーディオ機器において、入力されるデジタルオーディオ信号をアナログオーディオ信号に変換するオーディオ信号処理装置が用いられている。入力されるデジタルオーディオ信号のフォーマットとして、例えば、I2Sフォーマットが知られている。

【0003】

図6は、I2Sフォーマットで伝送されるデジタルオーディオ信号(以下、「I2S信号」とする。)の信号波形を示す図である。I2S信号は、LチャンネルのオーディオデータとRチャンネルのオーディオデータとを1ワードデータ毎に交互に配置したDATA信号と、このDATA信号のワードデータを識別するためのワードクロック信号(以下、「LRCK信号」とする。)と、ワードデータを構成する各ビットデータを識別するためのビットクロック信号(以下、「BCLK信号」とする。)とで構成されている。

【0004】

DATA信号は、同一のサンプリング位置iのLチャンネルのデータDLi(nビットデータで1ワードデータに相当)とRチャンネルのデータDRi(nビットデータで1ワードデータに相当)とをペアにし、各ペアをサンプリング順に配列したシリアルのデータ(DL1/DR1,DL2/DR2,…DLm/DRm)である。LRCK信号は、DATA信号の1ワードデータDLi/DRiを1周期とするクロックで、図6では、LRCK信号のローレベル(以下、「Lレベル」という。)の期間がDATA信号のLチャンネルのワードデータDLiに同期し、LRCK信号のハイレベル(以下、「Hレベル」とする。)の期間がDATA信号のRチャンネルのワードデータDRiに同期している。BCLK信号は、DATA信号のビットデータに同期したクロックである。

【0005】

DATA信号は、LRCK信号を用いてLチャンネルのワードデータDLiとRチャンネルのワードデータDRiとに分離され、BCLK信号を用いてビットデータ毎にアナログ信号に変換される。これにより、I2S信号は、Lチャンネルのデータに基づくアナログオーディオ信号とRチャンネルのデータに基づくアナログオーディオ信号とに変換される。

【0006】

ところで、マルチチャンネルのデジタルオーディオ信号の場合、DATA信号は複数の信号からなる場合があり、デジタルオーディオ機器によっては、以下に説明するように、DATA信号に含まれる各チャンネルのデジタルオーディオ信号をアナログオーディオ信号に変換するだけでなく、DATA信号に含まれる2つのオーディオ信号の組み合わせとは異なる組み合わせの2つのオーディオ信号を混合したアナログオーディオ信号を生成して出力する場合がある。

【0007】

図6は、5.1chサラウンドスピーカシステムに対するI2S信号を示したものである。なお、5.1chサラウンドスピーカシステムでは、リスナーの周りに、Lチャンネルフロントスピーカ(リスナーの前方左側のスピーカ。FLスピーカ)、Rチャンネルフロントスピーカ(リスナーの前方右側のスピーカ。FRスピーカ)、Lチャンネルリヤースピーカ(リスナーの後方左側のスピーカ。SLスピーカ)、Rチャンネルリヤースピーカ(リスナーの後方右側のスピーカ。SRスピーカ)、センタースピーカ(リスナーの前方中央のスピーカ。Cスピーカ)およびサブウーファー用スピーカ(低音専用のスピーカ。SWスピーカ)の6本のスピーカが配置されるので(図5(a)参照)、5.1chサラウンドに対するI2S信号のDATA信号には、各スピーカに対する6種類のデジタルオーディオ信号が含まれる。しかし、図6では、説明の便宜上、DATA信号に含まれるCスピーカとSWスピーカに対するデジタルオーディオ信号は省略している。また、以下の説明では、場合により「チャンネル」を「ch」と表記する。

【0008】

5.1chサラウンドに対するI2S信号のDATA信号では、FLスピーカから出力される音声に変換されるオーディオデータ(FLデータ)とFRスピーカから出力される音声に変換されるオーディオデータ(FRデータ)とが組み合わされたFL_FR信号と、SLスピーカから出力される音声に変換されるオーディオデータ(SLデータ)とSRスピーカから出力される音声に変換されるオーディオデータ(SRデータ)とが組み合わされたSL_SR信号とが含まれている。

【0009】

図6に示すI2S信号のDATA信号に含まれるFL_FR信号はFLデータとFRデータとに分離され、SL_SR信号はSLデータとSRデータとに分離され、それぞれアナログオーディオ信号であるfl信号、fr信号、sl信号およびsr信号に変換される。変換されたfl信号、fr信号、sl信号およびsr信号は、それぞれ対応するFLスピーカ、FRスピーカ、SLスピーカおよびSRスピーカに出力される。なお、Cスピーカに対するデジタルオーディオ信号は、アナログオーディオ信号であるc信号に変換されてCスピーカに出力され、SWスピーカに対するデジタルオーディオ信号は、アナログオーディオ信号であるsw信号に変換されてSWスピーカに出力される。

【0010】

5.1chサラウンドスピーカシステムに適用されるデジタルオーディオ機器(オーディオアンプ)には、上記のように、6本のスピーカに対して6個のアナログオーディオ信号(fl信号、fr信号、sl信号、sr信号、c信号、sw信号)の出力端子が設けられているが、ユーザが5.1chサラウンドスピーカシステムを有していない場合には、スピーカのない出力端子は接続されず、その出力端子のアナログオーディオ信号は使用されないことになる。

【0011】

例えば、ユーザの所有するスピーカシステムがFLスピーカ、FRスピーカおよびCスピーカからなるスピーカシステムの場合、そのスピーカシステムでは、sl信号、sr信号、sw信号は使用できない。このような不都合を解消するため、5.1chサラウンドスピーカシステムに適用可能なオーディオアンプには、fl信号とsl信号とを混合した信号(fl_sl信号)をfl信号の出力端子から出力し、fr信号とsr信号とを混合した信号(fr_sr信号)をfr信号の出力端子から出力するようにしているものがある。このようなオーディオアンプでは、FLスピーカ、FRスピーカおよびCスピーカからなるスピーカシステムと組み合わせる場合、FLスピーカとFRスピーカから出力させるオーディオ信号をそれぞれfl_sl信号とfr_sr信号とすることにより、sl信号およびsr信号も有効に利用できる。

【0012】

図7は、FL_FR信号およびSL_SR信号のデジタルオーディオ信号からfl信号、fr信号、sl信号、sr信号、fl_sl信号およびfr_sr信号のアナログオーディオ信号を生成し、異なる2種類の組み合わせで切換出力することのできるオーディオ信号処理装置を説明するための図である。オーディオ信号処理装置A100は、DA変換回路310,320、差動回路410,420、切替回路510,520、および出力端子610a,610b,620a,620bを備えている。

【0013】

DA変換回路310,320は、DATA信号、LRCK信号、およびBCLK信号が入力されて、変換されたアナログオーディオ信号を出力する。DA変換回路310は、ワンビットDAC310a、ローパスフィルタ310b,310cを備えている。ワンビットDAC310aは、FL_FR信号をFLデータおよびFRデータに分離し、DA変換を行って、fl信号およびfr信号を出力する。ローパスフィルタ310b,310cは、それぞれワンビットDC310aより入力されるfl信号およびfr信号から高域周波数成分を除去するものである。DA変換回路320は、ワンビットDAC320a、ローパスフィルタ320b,320cを備えており、SL_SR信号をsl信号およびsr信号に変換し、高域周波数成分を除去して出力する。

【0014】

差動回路410は、DA変換回路310より入力されるfl信号とDA変換回路320より入力されるsl信号とを合成してfl_sl信号を出力する。差動回路420は、DA変換回路310より入力されるfr信号とDA変換回路320より入力されるsr信号とを合成してfr_sr信号を出力する。

【0015】

切替回路510は、DA変換回路310から出力されたfl信号と差動回路410から出力されるfl_sl信号とを切り換えて出力端子610aに出力させる。また、切替回路520は、DA変換回路310から出力されるfr信号と差動回路420から出力されるfr_sr信号とを切り換えて出力端子620aに出力させる。切替回路510と切替回路520は連動して切り替えられ、4つの出力端子610a,610b,620a,620bからは(fl信号,sl信号,fr信号,sr信号)の組み合わせと(fl_sl信号,sl信号,fr_sr信号,sr信号)の組み合わせのいずれかが出力される。

【0016】

【特許文献1】特開2003−116200号公報

【特許文献2】特許3770219号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

オーディオ信号処理装置A100は、基板にDA変換回路310,320、差動回路410,420、および切替回路510,520を搭載して、各回路間をパターン配線することにより実現される。このとき、DA変換回路310のローパスフィルタ310bから出力されるfl信号を差動回路410に入力するために、ローパスフィルタ310bの出力と差動回路410の入力とをパターン配線し、ローパスフィルタ310cから出力されるfr信号を差動回路420に入力するために、ローパスフィルタ310cの出力と差動回路420の入力とをパターン配線する必要がある。また、ローパスフィルタ320bの出力と差動回路410の入力、および、ローパスフィルタ320cの出力と差動回路420の入力をパターン配線する必要がある。

【0018】

しかし、図7に示すように、DA変換回路310と差動回路420との間のfr信号のパターン配線とDA変換回路320と差動回路410との間のsl信号のパターン配線とは交差するので、これらのパターン配線は基板の同一平面上にパターン形成によって配線することはできない。従って、例えば、一方のパターン配線をジャンパー線によって迂回させるとか、スルーホールと裏面側に形成したパターン配線とによって迂回させるとか、などの対策を採らなければならず、基板上の配線が複雑になるとともに、迂回させたパターン配線は他のパターン配線に比べて線路長が長くなるので、その配線を流れるアナログオーディオ信号にノイズが重畳し易くなり、音質に悪影響を与えるという問題がある。

【0019】

本発明は上記した事情のもとで考え出されたものであって、差動回路に入力される2つの信号が同じDA変換回路から出力されるオーディオ信号処理装置を提供することをその目的としている。

【課題を解決するための手段】

【0020】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0021】

本発明の第1の側面によって提供されるオーディオ信号処理装置は、第1のLチャンネルのデータと第1のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第2のLチャンネルのデータと第2のRチャンネルのデータとを前記ワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成するオーディオデータ生成手段と、前記第3のオーディオデータを前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとに分離し、前記第1のLチャンネルのデータおよび前記第2のLチャンネルのデータをそれぞれ第1のアナログ信号および第2のアナログ信号に変換するDA変換手段と、前記第1のアナログ信号と前記第2のアナログ信号とから第3のアナログ信号を合成する合成手段と、を備えることを特徴とする。

【0022】

この構成によると、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとが互いに異なるオーディオデータに含まれて入力されるが、オーディオデータ生成手段により前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとを含む前記第3のオーディオデータが生成される。また、当該第3のオーディオデータは前記DA変換手段により前記第1のアナログ信号および前記第2のアナログ信号に変換される。したがって、前記合成装置で合成されるために入力されるべき前記第1のアナログ信号および前記第2のアナログ信号が、同じ前記DA変換装置から出力されることになる。

【0023】

本発明の好ましい実施の形態においては、前記第1のアナログ信号および前記第2のアナログ信号のみを出力する第1の出力状態と、少なくとも前記第3のアナログ信号を出力する第2の出力状態とを切り替える切替手段をさらに備えている。

【0024】

この構成によると、前記第1のアナログ信号および前記第2のアナログ信号を別々に出力する第1の出力状態と、前記第1のアナログ信号および前記第2のアナログ信号を合成して出力する第2の出力状態とを切り替えることができる。したがって、オーディオシステムのスピーカの接続状態に応じて、出力されるアナログ信号を変更することができる。

【0025】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段には前記ワード単位で反転するワードクロックと、前記ワードクロックのローレベルと前記第1のLチャンネルのデータとが同期している前記第1のオーディオデータと、前記ワードクロックのハイレベルと前記第2のLチャンネルのデータが同期している前記第2のオーディオデータと、が入力されており、前記オーディオデータ生成手段は、前記第1のオーディオデータと前記ワードクロックを反転させた反転クロックとの論理積を演算することにより前記第1のLチャンネルのデータを抽出した第1の抽出オーディオデータを生成する第1のAND回路と、前記第2のオーディオデータと前記ワードクロックとの論理積を演算することにより前記第2のLチャンネルのデータを抽出した第2の抽出オーディオデータを生成する第2のAND回路と、前記第1の抽出オーディオデータと前記第2の抽出オーディオデータとの論理和を演算することにより前記第3のオーディオデータを生成するOR回路と、を備えている。

【0026】

この構成によると、前記オーディオデータ生成手段は、前記第1のオーディオデータおよび前記第2のオーディオデータから前記第3のオーディオデータを生成することができる。

【0027】

本発明の好ましい実施の形態においては、前記第1のオーディオデータはI2Sフォーマットのデジタルオーディオデータであり、前記第2のオーディオデータはI2SフォーマットのデジタルオーディオデータのLチャンネルのデータとRチャンネルのデータとを入れ替えたデータである。

【0028】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段は、前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第4のオーディオデータをさらに生成し、生成された前記第4のオーディオデータを前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとに分離し、前記第1のRチャンネルのデータおよび前記第2のRチャンネルのデータをそれぞれ第4のアナログ信号および第5のアナログ信号に変換する第2のDA変換手段と、前記第4のアナログ信号と前記第5のアナログ信号とから第6のアナログ信号を合成する第2の合成手段と、をさらに備え、前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号のみが出力され、前記第2の出力状態に切り替えられている場合、少なくとも前記第3のアナログ信号および前記第6のアナログ信号が出力される。

【0029】

この構成によると、前記第2の合成手段に入力される前記第4のアナログ信号および前記第5のアナログ信号が、同じ前記第2のDA変換手段から出力される。したがって、基板上に実現する場合、前記合成手段は前記DA変換手段とのみパターン配線で接続され、前記第2の合成手段は前記第2のDA変換手段とのみパターン配線で接続される。したがって、前記合成手段および前記第2の合成手段がそれぞれ前記DA変換手段および前記第2のDA変換手段の両方と接続されることがなく、一部のパターン配線が迂回のために長くなることを、防止することができる。

【0030】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段、前記DA変換手段、前記第2のDA変換手段、前記合成手段、および前記第2の合成手段を少なくともそれぞれ2つずつ備え、9.2ch用の6つのオーディオデータが入力され、前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号を9.2ch用のアナログ信号として出力し、前記切替手段により前記第2の出力状態に切り替えられている場合、前記第3のアナログ信号および前記第6のアナログ信号を5.1ch用のアナログ信号として出力する。

【0031】

この構成によると、各オーディオデータを分離して変換した各アナログ信号を、9.2ch用のアナログ信号として、それぞれ別々に出力する前記第1の出力状態と、前記各アナログ信号を合成したものを、5.1ch用のアナログ信号として出力する前記第2の出力状態とを切り替えることができる。したがって、オーディオシステムのスピーカの接続状態に応じて、出力されるアナログ信号を9.2ch用と5.1ch用との間で変更することができる。

【0032】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【発明を実施するための最良の形態】

【0033】

以下、本発明の好ましい実施の形態を、図面を参照して具体的に説明する。

【0034】

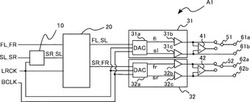

図1は、本発明に係るオーディオ信号処理装置の第1実施形態を説明するための図である。オーディオ信号処理装置A1は、FL_FR信号およびSL_SR信号のデジタルオーディオ信号からfl信号、fr信号、sl信号、sr信号、fl_sl信号およびfr_sr信号のアナログオーディオ信号を生成し、異なる2種類の組み合わせで切換出力することのできるものである。オーディオ信号処理装置A1は、データ反転回路10、データ組替回路20、DA変換回路31,32、差動回路41,42、切替回路51,52、および出力端子61a,61b,62a,62bを備えている。

【0035】

DATA信号には、LチャンネルのオーディオデータとRチャンネルのオーディオデータの2つのチャンネルのオーディオデータが含まれるが、データ反転回路10およびデータ組替回路20は、入力される2つのDATA信号の間で各DATA信号に含まれる2つのチャンネルのオーディオデータの組み合わせを組み替えて出力するものである。すなわち、データ反転回路10およびデータ組替回路20は、例えば、図6に示すI2S信号が入力された場合、FL_FR信号に含まれるFRデータとSL_SR信号に含まれるSLデータとを入れ替え、FL_FR信号をFLデータとSLデータを組み合わせたFL_SL信号に変換し、SL_SR信号をSRデータとFRデータを組み合わせたSR_FR信号に変換して出力する。

【0036】

データ反転回路10は、入力されるDATA信号の各ワードにおけるLチャンネルのオーディオデータとRチャンネルのオーディオデータの順番を入れ替える(すなわち、図6に示すI2S信号において、LRCK信号のローレベルにRチャンネルのデータDRiを対応させ、LRCK信号のハイレベルにLチャンネルのデータDLiを対応させるように、DATA信号のDLiとDRiの順番を入れ替える)ものである。データ反転回路10には、図6に示すI2S信号の2つのDATA信号のうちの一方であるSL_SR信号とLRCK信号とが入力され、データ反転回路10から各ワードにおけるSLデータDLiとSRデータDRiの順番が入れ替えられたSR_SL信号がデータ組替回路20に出力される。

【0037】

データ組替回路20は、入力される2つの信号の各ワードにおけるRチャンネルのオーディオデータを入れ替えるものである。データ組替回路20には、データ反転回路10から出力されるSR_SL信号と、I2S信号のDATA信号の他方であるFL_FR信号と、LRCK信号とが入力されるので、データ組替回路20は、FL_FR信号のFRデータとSR_SL信号のSLデータとを組み替えたFL_SL信号およびSR_FR信号を出力する。

【0038】

図2は、データ組替回路20の論理回路を示す図である。

【0039】

データ組替回路20は、FL_FR信号に含まれるFRデータをSR_SL信号に含まれるSLデータに入れ替え、FLデータとSLデータを組み合わせたFL_SL信号を生成する第1の論理回路と、SR_SL信号に含まれるSLデータをFL_FR信号に含まれるFRデータに入れ替え、SRデータとFRデータを組み合わせたSR_FR信号を生成する第2の論理回路とを備えている。

【0040】

第1の論理回路は1つのNOT回路201と、2つのAND回路203,204と、1つのOR回路207とで構成され、第2の論理回路は1つのNOT回路202と、2つのAND回路205,206と、1つのOR回路208とで構成されている。図2に示すように、第2の論理回路の回路構成は第1の論理回路の回路構成と同一である。

【0041】

AND回路204とAND回路205の一方の入力には、LRCK信号が入力され、AND回路203とAND回路206の一方の入力には、それぞれNOT回路201とNOT回路202を介してLRCK信号が入力される。また、AND回路203とAND回路205の他方の入力には、FL_FR信号が入力され、AND回路204とAND回路206の他方の入力には、SR_SL信号が入力される。AND回路203とAND回路204の各出力はOR回路207に入力され、AND回路205とAND回路206の各出力はOR回路208に入力され、OR回路207とOR回路208からそれぞれFL_SL信号とSR_FR信号とが出力される。

【0042】

図3は、データ組替回路20の論理演算により、FL_FR信号とSR_SL信号とが組み替えられてFL_SL信号が生成されることを説明するための図である。

【0043】

同図(a)は、AND回路203における2つの入力信号と1つの出力信号の波形を示している。上段と中段はそれぞれ入力信号であるLRCK信号の反転信号とFL_FR信号の波形であり、下段は2つの入力信号の論理積であるAND203信号の波形である。LRCK信号のLレベル期間がFL_FR信号のLチャンネルのFLデータと同期しているので、LRCK信号の反転信号のHレベル期間はFL_FR信号のLチャンネルのFLデータと同期している。したがって、AND203信号はFL_FR信号からFLデータのみを取り出した信号となる。

【0044】

同図(b)は、AND回路204における2つの入力信号と1つの出力信号の波形を示している。上段と中段はそれぞれ入力信号であるLRCK信号とSR_SL信号の波形であり、下段は2つの入力信号の論理積であるAND204信号の波形である。LRCK信号のHレベル期間がSR_SL信号のRチャンネルのSLデータと同期しているので、AND204信号はSR_SL信号からSLデータのみを取り出した信号となる。

【0045】

同図(c)は、AND203信号とAND204信号の論理和としてOR回路207から出力されるOR207信号を示している。OR207信号は、LチャンネルがFLデータで、RチャンネルがSLデータであるFL_SL信号となっている。

【0046】

同様に、AND回路205から出力されるAND205信号はFL_FR信号からFRデータのみを取り出した信号となり、AND回路206から出力されるAND206信号はSR_SL信号からSRデータのみを取り出した信号となる。したがって、OR回路208から出力されるOR208信号は、LチャンネルがSRデータで、RチャンネルがFRデータであるSR_FR信号となっている。

【0047】

図1に戻って、DA変換回路31は、データ組替回路20から出力されるFL_SL信号と、I2S信号のLRCK信号およびBCLK信号が入力されて、アナログオーディオ信号であるfl信号とsl信号に変換して出力する。DA変換回路31は、ワンビットDAC31a、ローパスフィルタ31b,31cを備えている。ワンビットDAC31aは、FL_SL信号をFLデータおよびSLデータに分離する図示しないデジタルフィルタと、FLデータおよびSLデータをそれぞれビット毎にシリアルにアナログ信号に変換する図示しない2つのDAコンバータとで構成されている。したがって、ワンビットDAC31aからは、FLデータをDA変換したfl信号と、SLデータをDA変換したsl信号とが出力される。ローパスフィルタ31b,31cは、それぞれワンビットDC31aより入力されるfl信号およびsl信号から高域周波数成分を除去するものである。

【0048】

DA変換回路32は、データ組替回路20から出力されるSR_FR信号と、I2S信号のLRCK信号およびBCLK信号が入力されて、アナログオーディオ信号であるfr信号とsr信号に変換して出力する。DA変換回路32は、DA変換回路31のワンビットDAC31a、ローパスフィルタ31b,31cにそれぞれ対応するワンビットDAC32a、ローパスフィルタ32b,32cを備えており、SR_FR信号をfr信号およびsr信号に変換し、高域周波数成分を除去して出力する。

【0049】

差動回路41,42は、例えばオペアンプなどからなり、入力される2つのアナログ信号の差動増幅を行うことにより、2つのアナログ信号が合成されたアナログ信号を出力する。差動回路41は、DA変換回路31より入力されるfl信号とsl信号とを合成してfl_sl信号を出力する。差動回路42は、DA変換回路32より入力されるfr信号とsr信号とを合成してfr_sr信号を出力する。

【0050】

切替回路51は、DA変換回路31から出力されたfl信号と差動回路41から出力されるfl_sl信号とを切り換えて出力端子61aに出力させる。また、切替回路52は、DA変換回路32から出力されるfr信号と差動回路42から出力されるfr_sr信号とを切り換えて出力端子62aに出力させる。切替回路51と切替回路52は連動して切り替えられ、4つの出力端子61a,61b,62a,62bからは(fl信号,sl信号,fr信号,sr信号)の組み合わせと(fl_sl信号,sl信号,fr_sr信号,sr信号)の組み合わせのいずれかが出力される。なお、DA変換回路31と出力端子61bとの間、および、DA変換回路32と出力端子62bとの間に、切替回路51,52と連動するスイッチを設けて、出力端子61a,62aがそれぞれfl_sl信号とfr_sr信号を出力するときに、出力端子61b,62bがそれぞれsl信号とsr信号を出力しないようにしてもよい。

【0051】

次に、オーディオ信号処理装置A1の作用について説明する。

【0052】

オーディオ信号処理装置A1は、基板にDA変換回路31,32、差動回路41,42、および切替回路51,52を搭載して、各回路間をパターン配線することにより実現される。このとき、DA変換回路31のローパスフィルタ31bから出力されるfl信号を差動回路41に入力するために、ローパスフィルタ31bの出力と差動回路41の入力とがパターン配線され、ローパスフィルタ31cから出力されるsl信号を差動回路41に入力するために、ローパスフィルタ31cの出力と差動回路41の入力とがパターン配線される。また、ローパスフィルタ32bの出力と差動回路42の入力、および、ローパスフィルタ32cの出力と差動回路42の入力がそれぞれパターン配線される。

【0053】

図1と図7を比較すると、図7のDA変換回路310と差動回路410がそれぞれ図1のDA変換回路31と差動回路41に対応し、図7のDA変換回路320と差動回路420がそれぞれ図1のDA変換回路32と差動回路42に対応するが、本実施形態においては、DA変換回路31から出力されるsl信号の信号線とDA変換回路32から出力されるfr信号の信号線とが交差することがない。従って、DA変換回路31と差動回路41の部分の回路ブロックとDA変換回路32と差動回路42の部分の回路ブロックとをそれぞれ独立してパターン配線すればよく、DA変換回路31と差動回路42の間およびDA変換回路32と差動回路41の間でパターン配線を交差させる必要がない。

【0054】

したがって、一方のパターン配線をジャンパー線によって迂回させたり、スルーホールと裏面側に形成したパターン配線とによって迂回させたりする必要がないので、各DA変換回路から後段のアナログオーディオ信号に対するパターン配線をほぼ同じにすることができる。これにより、複数のアナログオーディオ信号のパターン配線うち、一部のアナログオーディオ信号のパターン配線が他のアナログオーディオ信号のパターン配線より長くなることによる、当該一部のパターン配線を流れるアナログオーディオ信号へのノイズの重畳を抑制することができ、音質の劣化を防止することができる。

【0055】

上記第1実施形態では、入力されるDATA信号がFL_FR信号とSL_SR信号である場合について説明したが、これに限られず、他の信号でも構わない。要するに、I2Sフォーマットでは、左右に配置される一対のスピーカ(FchとRchのスピーカ)に対応する一対のデジタルオーディオ信号が混合されたDATA信号が1以上含まれるが、4ch以上のスピーカシステムに対応するオーディオディジタル機器では、各チャンネルのアナログオーディオ信号だけでなく、2つのアナログオーディオ信号(通常は左側の前後または右側の前後に配置されるスピーカに対応したアナログオーディオ信号)を混合した信号を生成して出力させる場合があるので、このような場合には、FL_FR信号とSL_SR信号に限られず、任意の組み合わせの2つのDATA信号の場合に適用することができるということである。

【0056】

図4は、本発明に係るオーディオ信号処理装置の第2実施形態を説明するための図である。

【0057】

第2実施形態は、本願発明を9.2chサラウンドスピーカシステムに適用されるオーディオアンプの、デジタルオーディオ信号からアナログオーディオ信号に変換して出力する回路構成に適用したもので、特に5.1chサラウンドスピーカシステムしか所有していないユーザを考慮し、5.1chサラウンドスピーカシステムに適用可能な6種類のオーディオ信号も切替出力できるようにしたものである。

【0058】

オーディオ信号処理装置A2は、入力される9.2chのI2S信号を9.2chのアナログオーディオ信号または5.1chのアナログオーディオ信号に変換して出力するものであり、9.2chサラウンド出力と5.1chサラウンド出力とを切り替えることができる。

【0059】

図5は、サラウンドオーディオシステムにおけるスピーカの配置を説明するための図であり、同図(a)は5.1chサラウンドの場合を示したものであり、同図(b)は9.2chサラウンドシステムの場合を示したものである。

【0060】

リスナーLが同図の上側を向いているとして、5.1chサラウンドの場合、同図(a)に示すように、リスナーLの前方左側にFLスピーカ、前方右側にFRスピーカ、前方中央にCスピーカ、後方左側にSLスピーカ、後方右側にSRスピーカの5つのスピーカと、低音専用のSWスピーカが配置される。9.2chサラウンドの場合、同図(b)に示すように、SLスピーカのさらに後方にSBLスピーカ、SRスピーカのさらに後方にSBRスピーカ、FLスピーカの左にFLHWスピーカ、FRスピーカの右にFRHWスピーカの4つのスピーカが追加され、SWスピーカの代わりに左側の低音専用のSWLスピーカと右側の低音専用のSWRスピーカが配置される。

【0061】

オーディオ信号処理装置A2には、9.2chサラウンド用のデジタルオーディオ信号が、I2Sフォーマットで入力される。この場合、DATA信号として、FL_FR信号、FLHW_FRHW信号(FLHWスピーカから出力される音声に変換されるFLHWデータとFRHWスピーカから出力される音声に変換されるFRHWデータとからなる。)、SL_SR信号、SBL_SBR信号(SBLスピーカから出力される音声に変換されるSBLデータとSBRスピーカから出力される音声に変換されるSBRデータとからなる。)、C信号(Cスピーカから出力される音声に変換されるCデータからなる。)、SWL_SWR信号(SWLスピーカから出力される音声に変換されるSWLデータとSWRスピーカから出力される音声に変換されるSWRデータとからなる。)が入力される。

【0062】

図4に示すように、オーディオ信号処理装置A2は、データ反転回路11,12、データ組替回路21,22、DA変換回路33,34,35,36,37,38、差動回路43,44,45,46,48、切替回路53,54,55,56,58、および出力端子63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68bを備えている。

【0063】

データ反転回路11,12は、図1に示すデータ反転回路10と同様の構成である。したがって、データ反転回路11は、FLHW_FRHW信号が入力されて、FLHWデータとFRHWデータとが入れ替えられたFRHW_FLHW信号をデータ組替回路21に出力する。また、データ反転回路12は、SBL_SBR信号が入力されて、SBLデータとSBRデータとが入れ替えられたSBR_SBL信号をデータ組替回路22に出力する。

【0064】

データ組替回路21,22は、図1に示すデータ組替回路20と同様の構成であり、その論理構成を示す図は図2に示すものと同様になる。したがって、データ組替回路21は、入力されるFL_FR信号およびFRHW_FLHW信号を組み替えて、FL_FLHW信号およびFRHW_FR信号として出力し、データ組替回路22は、入力されるSL_SR信号およびSBR_SBL信号を組み替えて、SL_SBL信号およびSBR_SR信号として出力する。

【0065】

DA変換回路33,34,35,36,38は、図1に示すDA変換回路31,32と同様の構成である。したがって、DA変換回路33はFL_FLHW信号をfl信号およびflhw信号(FLHWデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路34はFRHW_FR信号をfr信号およびfrhw信号(FRHWデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路35はSL_SBL信号をsl信号およびsbl信号(SBLデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路36はSBR_SR信号をsr信号およびsbr信号(SBRデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路38はSWL_SWR信号をswl信号(SWLデータから変換されたアナログオーディオ信号)およびswr信号(SWRデータから変換されたアナログオーディオ信号)に変換して出力する。

【0066】

一方、C信号はLチャンネルがCデータでRチャンネルはローレベルのデータとなっており、Rチャンネルのデータを取り出す必要がないので、DA変換回路37はローパスフィルタを1つ備えるのみである。また、ワンビットDAC37aのDAコンバータは1つであってもよい。DA変換回路37は、C信号のCデータをアナログオーディオ信号に変換したc信号を出力する。

【0067】

差動回路43,44,45,46,48は、図1に示す差動回路41,42と同様の構成である。したがって、差動回路43はflhw信号とfl信号とを合成して出力し、差動回路44はfrhw信号とfr信号とを合成して出力し、差動回路45はsbl信号とsl信号とを合成して出力し、差動回路46はsbr信号とsr信号とを合成して出力し、差動回路48はswr信号とswl信号とを合成して出力する。

【0068】

出力端子63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68bは、各信号を出力する端子であり、それぞれ対応するスピーカが接続される。出力端子63b,64b,65b,66b,67b,68bにはそれぞれFLスピーカ、FRスピーカ、SLスピーカ、SRスピーカ、Cスピーカ、SWスピーカ(SWLスピーカ)が接続される(図5参照)。また、出力端子63a,64a,65a,66a,68aにはそれぞれFLHWスピーカ、FRHWスピーカ、SBLスピーカ、SBRスピーカ、SWRスピーカが接続される(図5(b)参照)。

【0069】

切替回路53,54,55,56,58は、9.2chサラウンド出力である第1の出力状態と5.1chサラウンド出力である第2の出力状態とを切り替えるものであり、連動して切り替えられる。

【0070】

9.2chに対応できるスピーカ(すなわち、図5(b)に示すスピーカシステム)が接続されている場合、切替回路53,54,55,56,58は、第1の出力状態(図4における下側の端子に接続されている状態)となる。この場合、DA変換回路33から出力されるfl信号が出力端子63bから出力され、DA変換回路34から出力されるfr信号が出力端子64bから出力され、DA変換回路35から出力されるsl信号が出力端子65bから出力され、DA変換回路36から出力されるsr信号が出力端子66bから出力され、DA変換回路38から出力されるswl信号が出力端子68bから出力される。DA変換回路37から出力されるc信号は、出力状態の切り替えに関係なく、出力端子67bから出力される。また、DA変換回路33から出力されるflhw信号が出力端子63aから出力され、DA変換回路34から出力されるfrhw信号が出力端子64aから出力され、DA変換回路35から出力されるsbl信号が出力端子65aから出力され、DA変換回路36から出力されるsbr信号が出力端子66aから出力され、DA変換回路38から出力されるswr信号が出力端子68aから出力される。

【0071】

5.1chに対応するスピーカ(すなわち、図5(a)に示すスピーカシステム)が接続されている場合、すなわち、出力端子63a,64a,65a,66a,68aにFLHWスピーカ、FRHWスピーカ、SBLスピーカ、SBRスピーカ、SWRスピーカが接続されていない場合、切替回路53,54,55,56,58は、第2の出力状態(図4における上側の端子に接続されている状態)となる。この場合、差動回路43から出力されるfl信号およびflhw信号の合成信号が出力端子63bから出力され、差動回路44から出力されるfr信号およびfrhw信号の合成信号が出力端子64bから出力され、差動回路45から出力されるsl信号およびsbl信号の合成信号が出力端子65bから出力され、差動回路46から出力されるsr信号およびsbr信号の合成信号が出力端子66bから出力され、差動回路48から出力されるswr信号およびswl信号の合成信号が出力端子68bから出力される。また、DA変換回路37から出力されるc信号が、出力端子67bから出力される。なお、出力端子63a,64a,65a,66a,68aから、それぞれflhw信号、frhw信号、sbl信号、sbr信号、swr信号が出力されるが、これらの出力端子にはスピーカが接続されていない。第2の出力状態において、出力端子63a,64a,65a,66a,68aとDA変換回路33,34,35,36,38との接続を切り離すようにしてもよい。

【0072】

これにより、オーディオ信号処理装置A2は、接続されているスピーカシステムに応じて、入力される9.2chのI2S信号を9.2chのアナログオーディオ信号または5.1chのアナログオーディオ信号に変換して出力することができる。

【0073】

本実施形態においては、FL_FR信号およびFLHW_FRHW信号がFL_FLHW信号およびFRHW_FR信号に変換されるので、DA変換回路33から出力される信号線とDA変換回路34から出力される信号線とが交差することがない。また、SL_SR信号およびSBL_SBR信号がSL_SBL信号およびSBR_SR信号に変換されるので、DA変換回路35から出力される信号線とDA変換回路36から出力される信号線とが交差することがない。したがって、DA変換回路33と差動回路43の部分の回路ブロック、DA変換回路34と差動回路44の部分の回路ブロック、DA変換回路35と差動回路45の部分の回路ブロック、および、DA変換回路36と差動回路46の部分の回路ブロックをそれぞれ独立してパターン配線すればよく、一方のパターン配線をジャンパー線によって迂回させたり、スルーホールと裏面側に形成したパターン配線とによって迂回させたりする必要がないので、複数のアナログオーディオ信号のパターン配線うち、一部のアナログオーディオ信号のパターン配線が他のアナログオーディオ信号のパターン配線より長くなることによる、当該一部のパターン配線を流れるアナログオーディオ信号へのノイズの重畳を抑制することができ、音質の劣化を防止することができる。

【0074】

なお、オーディオ信号処理装置A2に5.1chのI2S信号が入力された場合、出力状態にかかわらず、5.1chのアナログオーディオ信号が出力される。すなわち、FLHW_FRHW信号が入力されないので、データ組替回路21から出力されるFL_FLHW信号のRチャンネルはローレベルデータとなり、FRHW_FR信号のLチャンネルはローレベルデータとなり、DA変換回路33からflhw信号が出力されず、DA変換回路34からfrhw信号が出力されない。したがって、出力端子63a,64aからは信号が出力されず、出力端子63b,64bからは出力状態にかかわらず、それぞれfl信号、fr信号が出力される。同様にSBL_SBR信号が入力されないので、出力端子65a,66aからは信号が出力されず、出力端子65b,66bからは出力状態にかかわらず、それぞれsl信号、sr信号が出力される。また、SWL_SWR信号の代わりに、LチャンネルがSWデータ(SWスピーカから出力される音声に変換されるオーディオデータ)でRチャンネルがローレベルのデータであるSW信号が入力されるので、出力端子68aからは信号が出力されず、出力端子68bからは出力状態にかかわらず、sw信号(SWデータから変換されたアナログオーディオ信号)が出力される。

【0075】

上記第1実施形態および第2実施形態では、I2Sフォーマットで伝送されるデジタルオーディオ信号が入力された場合について説明したが、これに限られない。本発明は、2種類のオーディオデータが1ワードデータ毎に交互に配置されているデジタルオーディオ信号の場合に適用することができる。例えば、Right−Justified(右詰め)フォーマット、Left−Justified(左詰め)フォーマット、Left−JustifiedDSPフォーマット、32×FsPackedフォーマットなどの各種のフォーマットにも適用することができる。

【0076】

なお、上記第1および第2実施形態では、データ反転回路により一方のDATA信号のLチャンネルのオーディオデータとRチャンネルのオーディオデータとを入れ替えているが、これは2つのDATA信号の同じチャンネルのデータ同士を組み合わせたいからである。したがって、一方のDATA信号のLチャンネルのデータと他方のDATA信号のRチャンネルのデータとを組み合わせる場合は、データ反転回路を必要としない。

【0077】

本発明に係るオーディオ信号処理装置は、上述した実施形態に限定されるものではない。本発明に係るオーディオ信号処理装置の各部の具体的な構成は、種々に設計変更自在である。

【図面の簡単な説明】

【0078】

【図1】本発明に係るオーディオ信号処理装置の第1実施形態を説明するための図である。

【図2】データ組替回路の論理回路を示す図である。

【図3】データ組替回路の論理演算を説明するための図である。

【図4】本発明に係るオーディオ信号処理装置の第2実施形態を説明するための図である。

【図5】サラウンドオーディオシステムにおけるスピーカの配置を説明するための図である。

【図6】I2Sフォーマットで伝送されるデジタルオーディオ信号の信号波形を示す図である。

【図7】従来のオーディオ信号処理装置を説明するための図である。

【符号の説明】

【0079】

A1,A2 オーディオ信号処理装置

10,11,12 データ反転回路

20,21,22 データ組替回路(オーディオデータ生成手段)

201,202 NOT回路

203,204,205,206 AND回路

207,208 OR回路

31,32,33,34,35,36,37,38 DA変換回路(DA変換手段、第2のDA変換手段)

31a,32a ワンビットDAC

31b,31c,32b,32c ローパスフィルタ

41,42,43,44,45,46,48 差動回路(合成手段、第2の合成手段)

51,52,53,54,55,56,58 切替回路(切替手段)

61a,61b,62a,62b,63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68b 出力端子

【技術分野】

【0001】

本発明は、入力されるデジタルオーディオ信号をアナログオーディオ信号に変換するオーディオ信号処理装置に関し、特に、複数のオーディオ信号を同時に処理するマルチチャンネルのオーディオ信号処理装置に関する。

【背景技術】

【0002】

デジタルオーディオ機器において、入力されるデジタルオーディオ信号をアナログオーディオ信号に変換するオーディオ信号処理装置が用いられている。入力されるデジタルオーディオ信号のフォーマットとして、例えば、I2Sフォーマットが知られている。

【0003】

図6は、I2Sフォーマットで伝送されるデジタルオーディオ信号(以下、「I2S信号」とする。)の信号波形を示す図である。I2S信号は、LチャンネルのオーディオデータとRチャンネルのオーディオデータとを1ワードデータ毎に交互に配置したDATA信号と、このDATA信号のワードデータを識別するためのワードクロック信号(以下、「LRCK信号」とする。)と、ワードデータを構成する各ビットデータを識別するためのビットクロック信号(以下、「BCLK信号」とする。)とで構成されている。

【0004】

DATA信号は、同一のサンプリング位置iのLチャンネルのデータDLi(nビットデータで1ワードデータに相当)とRチャンネルのデータDRi(nビットデータで1ワードデータに相当)とをペアにし、各ペアをサンプリング順に配列したシリアルのデータ(DL1/DR1,DL2/DR2,…DLm/DRm)である。LRCK信号は、DATA信号の1ワードデータDLi/DRiを1周期とするクロックで、図6では、LRCK信号のローレベル(以下、「Lレベル」という。)の期間がDATA信号のLチャンネルのワードデータDLiに同期し、LRCK信号のハイレベル(以下、「Hレベル」とする。)の期間がDATA信号のRチャンネルのワードデータDRiに同期している。BCLK信号は、DATA信号のビットデータに同期したクロックである。

【0005】

DATA信号は、LRCK信号を用いてLチャンネルのワードデータDLiとRチャンネルのワードデータDRiとに分離され、BCLK信号を用いてビットデータ毎にアナログ信号に変換される。これにより、I2S信号は、Lチャンネルのデータに基づくアナログオーディオ信号とRチャンネルのデータに基づくアナログオーディオ信号とに変換される。

【0006】

ところで、マルチチャンネルのデジタルオーディオ信号の場合、DATA信号は複数の信号からなる場合があり、デジタルオーディオ機器によっては、以下に説明するように、DATA信号に含まれる各チャンネルのデジタルオーディオ信号をアナログオーディオ信号に変換するだけでなく、DATA信号に含まれる2つのオーディオ信号の組み合わせとは異なる組み合わせの2つのオーディオ信号を混合したアナログオーディオ信号を生成して出力する場合がある。

【0007】

図6は、5.1chサラウンドスピーカシステムに対するI2S信号を示したものである。なお、5.1chサラウンドスピーカシステムでは、リスナーの周りに、Lチャンネルフロントスピーカ(リスナーの前方左側のスピーカ。FLスピーカ)、Rチャンネルフロントスピーカ(リスナーの前方右側のスピーカ。FRスピーカ)、Lチャンネルリヤースピーカ(リスナーの後方左側のスピーカ。SLスピーカ)、Rチャンネルリヤースピーカ(リスナーの後方右側のスピーカ。SRスピーカ)、センタースピーカ(リスナーの前方中央のスピーカ。Cスピーカ)およびサブウーファー用スピーカ(低音専用のスピーカ。SWスピーカ)の6本のスピーカが配置されるので(図5(a)参照)、5.1chサラウンドに対するI2S信号のDATA信号には、各スピーカに対する6種類のデジタルオーディオ信号が含まれる。しかし、図6では、説明の便宜上、DATA信号に含まれるCスピーカとSWスピーカに対するデジタルオーディオ信号は省略している。また、以下の説明では、場合により「チャンネル」を「ch」と表記する。

【0008】

5.1chサラウンドに対するI2S信号のDATA信号では、FLスピーカから出力される音声に変換されるオーディオデータ(FLデータ)とFRスピーカから出力される音声に変換されるオーディオデータ(FRデータ)とが組み合わされたFL_FR信号と、SLスピーカから出力される音声に変換されるオーディオデータ(SLデータ)とSRスピーカから出力される音声に変換されるオーディオデータ(SRデータ)とが組み合わされたSL_SR信号とが含まれている。

【0009】

図6に示すI2S信号のDATA信号に含まれるFL_FR信号はFLデータとFRデータとに分離され、SL_SR信号はSLデータとSRデータとに分離され、それぞれアナログオーディオ信号であるfl信号、fr信号、sl信号およびsr信号に変換される。変換されたfl信号、fr信号、sl信号およびsr信号は、それぞれ対応するFLスピーカ、FRスピーカ、SLスピーカおよびSRスピーカに出力される。なお、Cスピーカに対するデジタルオーディオ信号は、アナログオーディオ信号であるc信号に変換されてCスピーカに出力され、SWスピーカに対するデジタルオーディオ信号は、アナログオーディオ信号であるsw信号に変換されてSWスピーカに出力される。

【0010】

5.1chサラウンドスピーカシステムに適用されるデジタルオーディオ機器(オーディオアンプ)には、上記のように、6本のスピーカに対して6個のアナログオーディオ信号(fl信号、fr信号、sl信号、sr信号、c信号、sw信号)の出力端子が設けられているが、ユーザが5.1chサラウンドスピーカシステムを有していない場合には、スピーカのない出力端子は接続されず、その出力端子のアナログオーディオ信号は使用されないことになる。

【0011】

例えば、ユーザの所有するスピーカシステムがFLスピーカ、FRスピーカおよびCスピーカからなるスピーカシステムの場合、そのスピーカシステムでは、sl信号、sr信号、sw信号は使用できない。このような不都合を解消するため、5.1chサラウンドスピーカシステムに適用可能なオーディオアンプには、fl信号とsl信号とを混合した信号(fl_sl信号)をfl信号の出力端子から出力し、fr信号とsr信号とを混合した信号(fr_sr信号)をfr信号の出力端子から出力するようにしているものがある。このようなオーディオアンプでは、FLスピーカ、FRスピーカおよびCスピーカからなるスピーカシステムと組み合わせる場合、FLスピーカとFRスピーカから出力させるオーディオ信号をそれぞれfl_sl信号とfr_sr信号とすることにより、sl信号およびsr信号も有効に利用できる。

【0012】

図7は、FL_FR信号およびSL_SR信号のデジタルオーディオ信号からfl信号、fr信号、sl信号、sr信号、fl_sl信号およびfr_sr信号のアナログオーディオ信号を生成し、異なる2種類の組み合わせで切換出力することのできるオーディオ信号処理装置を説明するための図である。オーディオ信号処理装置A100は、DA変換回路310,320、差動回路410,420、切替回路510,520、および出力端子610a,610b,620a,620bを備えている。

【0013】

DA変換回路310,320は、DATA信号、LRCK信号、およびBCLK信号が入力されて、変換されたアナログオーディオ信号を出力する。DA変換回路310は、ワンビットDAC310a、ローパスフィルタ310b,310cを備えている。ワンビットDAC310aは、FL_FR信号をFLデータおよびFRデータに分離し、DA変換を行って、fl信号およびfr信号を出力する。ローパスフィルタ310b,310cは、それぞれワンビットDC310aより入力されるfl信号およびfr信号から高域周波数成分を除去するものである。DA変換回路320は、ワンビットDAC320a、ローパスフィルタ320b,320cを備えており、SL_SR信号をsl信号およびsr信号に変換し、高域周波数成分を除去して出力する。

【0014】

差動回路410は、DA変換回路310より入力されるfl信号とDA変換回路320より入力されるsl信号とを合成してfl_sl信号を出力する。差動回路420は、DA変換回路310より入力されるfr信号とDA変換回路320より入力されるsr信号とを合成してfr_sr信号を出力する。

【0015】

切替回路510は、DA変換回路310から出力されたfl信号と差動回路410から出力されるfl_sl信号とを切り換えて出力端子610aに出力させる。また、切替回路520は、DA変換回路310から出力されるfr信号と差動回路420から出力されるfr_sr信号とを切り換えて出力端子620aに出力させる。切替回路510と切替回路520は連動して切り替えられ、4つの出力端子610a,610b,620a,620bからは(fl信号,sl信号,fr信号,sr信号)の組み合わせと(fl_sl信号,sl信号,fr_sr信号,sr信号)の組み合わせのいずれかが出力される。

【0016】

【特許文献1】特開2003−116200号公報

【特許文献2】特許3770219号公報

【発明の開示】

【発明が解決しようとする課題】

【0017】

オーディオ信号処理装置A100は、基板にDA変換回路310,320、差動回路410,420、および切替回路510,520を搭載して、各回路間をパターン配線することにより実現される。このとき、DA変換回路310のローパスフィルタ310bから出力されるfl信号を差動回路410に入力するために、ローパスフィルタ310bの出力と差動回路410の入力とをパターン配線し、ローパスフィルタ310cから出力されるfr信号を差動回路420に入力するために、ローパスフィルタ310cの出力と差動回路420の入力とをパターン配線する必要がある。また、ローパスフィルタ320bの出力と差動回路410の入力、および、ローパスフィルタ320cの出力と差動回路420の入力をパターン配線する必要がある。

【0018】

しかし、図7に示すように、DA変換回路310と差動回路420との間のfr信号のパターン配線とDA変換回路320と差動回路410との間のsl信号のパターン配線とは交差するので、これらのパターン配線は基板の同一平面上にパターン形成によって配線することはできない。従って、例えば、一方のパターン配線をジャンパー線によって迂回させるとか、スルーホールと裏面側に形成したパターン配線とによって迂回させるとか、などの対策を採らなければならず、基板上の配線が複雑になるとともに、迂回させたパターン配線は他のパターン配線に比べて線路長が長くなるので、その配線を流れるアナログオーディオ信号にノイズが重畳し易くなり、音質に悪影響を与えるという問題がある。

【0019】

本発明は上記した事情のもとで考え出されたものであって、差動回路に入力される2つの信号が同じDA変換回路から出力されるオーディオ信号処理装置を提供することをその目的としている。

【課題を解決するための手段】

【0020】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0021】

本発明の第1の側面によって提供されるオーディオ信号処理装置は、第1のLチャンネルのデータと第1のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第2のLチャンネルのデータと第2のRチャンネルのデータとを前記ワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成するオーディオデータ生成手段と、前記第3のオーディオデータを前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとに分離し、前記第1のLチャンネルのデータおよび前記第2のLチャンネルのデータをそれぞれ第1のアナログ信号および第2のアナログ信号に変換するDA変換手段と、前記第1のアナログ信号と前記第2のアナログ信号とから第3のアナログ信号を合成する合成手段と、を備えることを特徴とする。

【0022】

この構成によると、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとが互いに異なるオーディオデータに含まれて入力されるが、オーディオデータ生成手段により前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとを含む前記第3のオーディオデータが生成される。また、当該第3のオーディオデータは前記DA変換手段により前記第1のアナログ信号および前記第2のアナログ信号に変換される。したがって、前記合成装置で合成されるために入力されるべき前記第1のアナログ信号および前記第2のアナログ信号が、同じ前記DA変換装置から出力されることになる。

【0023】

本発明の好ましい実施の形態においては、前記第1のアナログ信号および前記第2のアナログ信号のみを出力する第1の出力状態と、少なくとも前記第3のアナログ信号を出力する第2の出力状態とを切り替える切替手段をさらに備えている。

【0024】

この構成によると、前記第1のアナログ信号および前記第2のアナログ信号を別々に出力する第1の出力状態と、前記第1のアナログ信号および前記第2のアナログ信号を合成して出力する第2の出力状態とを切り替えることができる。したがって、オーディオシステムのスピーカの接続状態に応じて、出力されるアナログ信号を変更することができる。

【0025】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段には前記ワード単位で反転するワードクロックと、前記ワードクロックのローレベルと前記第1のLチャンネルのデータとが同期している前記第1のオーディオデータと、前記ワードクロックのハイレベルと前記第2のLチャンネルのデータが同期している前記第2のオーディオデータと、が入力されており、前記オーディオデータ生成手段は、前記第1のオーディオデータと前記ワードクロックを反転させた反転クロックとの論理積を演算することにより前記第1のLチャンネルのデータを抽出した第1の抽出オーディオデータを生成する第1のAND回路と、前記第2のオーディオデータと前記ワードクロックとの論理積を演算することにより前記第2のLチャンネルのデータを抽出した第2の抽出オーディオデータを生成する第2のAND回路と、前記第1の抽出オーディオデータと前記第2の抽出オーディオデータとの論理和を演算することにより前記第3のオーディオデータを生成するOR回路と、を備えている。

【0026】

この構成によると、前記オーディオデータ生成手段は、前記第1のオーディオデータおよび前記第2のオーディオデータから前記第3のオーディオデータを生成することができる。

【0027】

本発明の好ましい実施の形態においては、前記第1のオーディオデータはI2Sフォーマットのデジタルオーディオデータであり、前記第2のオーディオデータはI2SフォーマットのデジタルオーディオデータのLチャンネルのデータとRチャンネルのデータとを入れ替えたデータである。

【0028】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段は、前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第4のオーディオデータをさらに生成し、生成された前記第4のオーディオデータを前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとに分離し、前記第1のRチャンネルのデータおよび前記第2のRチャンネルのデータをそれぞれ第4のアナログ信号および第5のアナログ信号に変換する第2のDA変換手段と、前記第4のアナログ信号と前記第5のアナログ信号とから第6のアナログ信号を合成する第2の合成手段と、をさらに備え、前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号のみが出力され、前記第2の出力状態に切り替えられている場合、少なくとも前記第3のアナログ信号および前記第6のアナログ信号が出力される。

【0029】

この構成によると、前記第2の合成手段に入力される前記第4のアナログ信号および前記第5のアナログ信号が、同じ前記第2のDA変換手段から出力される。したがって、基板上に実現する場合、前記合成手段は前記DA変換手段とのみパターン配線で接続され、前記第2の合成手段は前記第2のDA変換手段とのみパターン配線で接続される。したがって、前記合成手段および前記第2の合成手段がそれぞれ前記DA変換手段および前記第2のDA変換手段の両方と接続されることがなく、一部のパターン配線が迂回のために長くなることを、防止することができる。

【0030】

本発明の好ましい実施の形態においては、前記オーディオデータ生成手段、前記DA変換手段、前記第2のDA変換手段、前記合成手段、および前記第2の合成手段を少なくともそれぞれ2つずつ備え、9.2ch用の6つのオーディオデータが入力され、前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号を9.2ch用のアナログ信号として出力し、前記切替手段により前記第2の出力状態に切り替えられている場合、前記第3のアナログ信号および前記第6のアナログ信号を5.1ch用のアナログ信号として出力する。

【0031】

この構成によると、各オーディオデータを分離して変換した各アナログ信号を、9.2ch用のアナログ信号として、それぞれ別々に出力する前記第1の出力状態と、前記各アナログ信号を合成したものを、5.1ch用のアナログ信号として出力する前記第2の出力状態とを切り替えることができる。したがって、オーディオシステムのスピーカの接続状態に応じて、出力されるアナログ信号を9.2ch用と5.1ch用との間で変更することができる。

【0032】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【発明を実施するための最良の形態】

【0033】

以下、本発明の好ましい実施の形態を、図面を参照して具体的に説明する。

【0034】

図1は、本発明に係るオーディオ信号処理装置の第1実施形態を説明するための図である。オーディオ信号処理装置A1は、FL_FR信号およびSL_SR信号のデジタルオーディオ信号からfl信号、fr信号、sl信号、sr信号、fl_sl信号およびfr_sr信号のアナログオーディオ信号を生成し、異なる2種類の組み合わせで切換出力することのできるものである。オーディオ信号処理装置A1は、データ反転回路10、データ組替回路20、DA変換回路31,32、差動回路41,42、切替回路51,52、および出力端子61a,61b,62a,62bを備えている。

【0035】

DATA信号には、LチャンネルのオーディオデータとRチャンネルのオーディオデータの2つのチャンネルのオーディオデータが含まれるが、データ反転回路10およびデータ組替回路20は、入力される2つのDATA信号の間で各DATA信号に含まれる2つのチャンネルのオーディオデータの組み合わせを組み替えて出力するものである。すなわち、データ反転回路10およびデータ組替回路20は、例えば、図6に示すI2S信号が入力された場合、FL_FR信号に含まれるFRデータとSL_SR信号に含まれるSLデータとを入れ替え、FL_FR信号をFLデータとSLデータを組み合わせたFL_SL信号に変換し、SL_SR信号をSRデータとFRデータを組み合わせたSR_FR信号に変換して出力する。

【0036】

データ反転回路10は、入力されるDATA信号の各ワードにおけるLチャンネルのオーディオデータとRチャンネルのオーディオデータの順番を入れ替える(すなわち、図6に示すI2S信号において、LRCK信号のローレベルにRチャンネルのデータDRiを対応させ、LRCK信号のハイレベルにLチャンネルのデータDLiを対応させるように、DATA信号のDLiとDRiの順番を入れ替える)ものである。データ反転回路10には、図6に示すI2S信号の2つのDATA信号のうちの一方であるSL_SR信号とLRCK信号とが入力され、データ反転回路10から各ワードにおけるSLデータDLiとSRデータDRiの順番が入れ替えられたSR_SL信号がデータ組替回路20に出力される。

【0037】

データ組替回路20は、入力される2つの信号の各ワードにおけるRチャンネルのオーディオデータを入れ替えるものである。データ組替回路20には、データ反転回路10から出力されるSR_SL信号と、I2S信号のDATA信号の他方であるFL_FR信号と、LRCK信号とが入力されるので、データ組替回路20は、FL_FR信号のFRデータとSR_SL信号のSLデータとを組み替えたFL_SL信号およびSR_FR信号を出力する。

【0038】

図2は、データ組替回路20の論理回路を示す図である。

【0039】

データ組替回路20は、FL_FR信号に含まれるFRデータをSR_SL信号に含まれるSLデータに入れ替え、FLデータとSLデータを組み合わせたFL_SL信号を生成する第1の論理回路と、SR_SL信号に含まれるSLデータをFL_FR信号に含まれるFRデータに入れ替え、SRデータとFRデータを組み合わせたSR_FR信号を生成する第2の論理回路とを備えている。

【0040】

第1の論理回路は1つのNOT回路201と、2つのAND回路203,204と、1つのOR回路207とで構成され、第2の論理回路は1つのNOT回路202と、2つのAND回路205,206と、1つのOR回路208とで構成されている。図2に示すように、第2の論理回路の回路構成は第1の論理回路の回路構成と同一である。

【0041】

AND回路204とAND回路205の一方の入力には、LRCK信号が入力され、AND回路203とAND回路206の一方の入力には、それぞれNOT回路201とNOT回路202を介してLRCK信号が入力される。また、AND回路203とAND回路205の他方の入力には、FL_FR信号が入力され、AND回路204とAND回路206の他方の入力には、SR_SL信号が入力される。AND回路203とAND回路204の各出力はOR回路207に入力され、AND回路205とAND回路206の各出力はOR回路208に入力され、OR回路207とOR回路208からそれぞれFL_SL信号とSR_FR信号とが出力される。

【0042】

図3は、データ組替回路20の論理演算により、FL_FR信号とSR_SL信号とが組み替えられてFL_SL信号が生成されることを説明するための図である。

【0043】

同図(a)は、AND回路203における2つの入力信号と1つの出力信号の波形を示している。上段と中段はそれぞれ入力信号であるLRCK信号の反転信号とFL_FR信号の波形であり、下段は2つの入力信号の論理積であるAND203信号の波形である。LRCK信号のLレベル期間がFL_FR信号のLチャンネルのFLデータと同期しているので、LRCK信号の反転信号のHレベル期間はFL_FR信号のLチャンネルのFLデータと同期している。したがって、AND203信号はFL_FR信号からFLデータのみを取り出した信号となる。

【0044】

同図(b)は、AND回路204における2つの入力信号と1つの出力信号の波形を示している。上段と中段はそれぞれ入力信号であるLRCK信号とSR_SL信号の波形であり、下段は2つの入力信号の論理積であるAND204信号の波形である。LRCK信号のHレベル期間がSR_SL信号のRチャンネルのSLデータと同期しているので、AND204信号はSR_SL信号からSLデータのみを取り出した信号となる。

【0045】

同図(c)は、AND203信号とAND204信号の論理和としてOR回路207から出力されるOR207信号を示している。OR207信号は、LチャンネルがFLデータで、RチャンネルがSLデータであるFL_SL信号となっている。

【0046】

同様に、AND回路205から出力されるAND205信号はFL_FR信号からFRデータのみを取り出した信号となり、AND回路206から出力されるAND206信号はSR_SL信号からSRデータのみを取り出した信号となる。したがって、OR回路208から出力されるOR208信号は、LチャンネルがSRデータで、RチャンネルがFRデータであるSR_FR信号となっている。

【0047】

図1に戻って、DA変換回路31は、データ組替回路20から出力されるFL_SL信号と、I2S信号のLRCK信号およびBCLK信号が入力されて、アナログオーディオ信号であるfl信号とsl信号に変換して出力する。DA変換回路31は、ワンビットDAC31a、ローパスフィルタ31b,31cを備えている。ワンビットDAC31aは、FL_SL信号をFLデータおよびSLデータに分離する図示しないデジタルフィルタと、FLデータおよびSLデータをそれぞれビット毎にシリアルにアナログ信号に変換する図示しない2つのDAコンバータとで構成されている。したがって、ワンビットDAC31aからは、FLデータをDA変換したfl信号と、SLデータをDA変換したsl信号とが出力される。ローパスフィルタ31b,31cは、それぞれワンビットDC31aより入力されるfl信号およびsl信号から高域周波数成分を除去するものである。

【0048】

DA変換回路32は、データ組替回路20から出力されるSR_FR信号と、I2S信号のLRCK信号およびBCLK信号が入力されて、アナログオーディオ信号であるfr信号とsr信号に変換して出力する。DA変換回路32は、DA変換回路31のワンビットDAC31a、ローパスフィルタ31b,31cにそれぞれ対応するワンビットDAC32a、ローパスフィルタ32b,32cを備えており、SR_FR信号をfr信号およびsr信号に変換し、高域周波数成分を除去して出力する。

【0049】

差動回路41,42は、例えばオペアンプなどからなり、入力される2つのアナログ信号の差動増幅を行うことにより、2つのアナログ信号が合成されたアナログ信号を出力する。差動回路41は、DA変換回路31より入力されるfl信号とsl信号とを合成してfl_sl信号を出力する。差動回路42は、DA変換回路32より入力されるfr信号とsr信号とを合成してfr_sr信号を出力する。

【0050】

切替回路51は、DA変換回路31から出力されたfl信号と差動回路41から出力されるfl_sl信号とを切り換えて出力端子61aに出力させる。また、切替回路52は、DA変換回路32から出力されるfr信号と差動回路42から出力されるfr_sr信号とを切り換えて出力端子62aに出力させる。切替回路51と切替回路52は連動して切り替えられ、4つの出力端子61a,61b,62a,62bからは(fl信号,sl信号,fr信号,sr信号)の組み合わせと(fl_sl信号,sl信号,fr_sr信号,sr信号)の組み合わせのいずれかが出力される。なお、DA変換回路31と出力端子61bとの間、および、DA変換回路32と出力端子62bとの間に、切替回路51,52と連動するスイッチを設けて、出力端子61a,62aがそれぞれfl_sl信号とfr_sr信号を出力するときに、出力端子61b,62bがそれぞれsl信号とsr信号を出力しないようにしてもよい。

【0051】

次に、オーディオ信号処理装置A1の作用について説明する。

【0052】

オーディオ信号処理装置A1は、基板にDA変換回路31,32、差動回路41,42、および切替回路51,52を搭載して、各回路間をパターン配線することにより実現される。このとき、DA変換回路31のローパスフィルタ31bから出力されるfl信号を差動回路41に入力するために、ローパスフィルタ31bの出力と差動回路41の入力とがパターン配線され、ローパスフィルタ31cから出力されるsl信号を差動回路41に入力するために、ローパスフィルタ31cの出力と差動回路41の入力とがパターン配線される。また、ローパスフィルタ32bの出力と差動回路42の入力、および、ローパスフィルタ32cの出力と差動回路42の入力がそれぞれパターン配線される。

【0053】

図1と図7を比較すると、図7のDA変換回路310と差動回路410がそれぞれ図1のDA変換回路31と差動回路41に対応し、図7のDA変換回路320と差動回路420がそれぞれ図1のDA変換回路32と差動回路42に対応するが、本実施形態においては、DA変換回路31から出力されるsl信号の信号線とDA変換回路32から出力されるfr信号の信号線とが交差することがない。従って、DA変換回路31と差動回路41の部分の回路ブロックとDA変換回路32と差動回路42の部分の回路ブロックとをそれぞれ独立してパターン配線すればよく、DA変換回路31と差動回路42の間およびDA変換回路32と差動回路41の間でパターン配線を交差させる必要がない。

【0054】

したがって、一方のパターン配線をジャンパー線によって迂回させたり、スルーホールと裏面側に形成したパターン配線とによって迂回させたりする必要がないので、各DA変換回路から後段のアナログオーディオ信号に対するパターン配線をほぼ同じにすることができる。これにより、複数のアナログオーディオ信号のパターン配線うち、一部のアナログオーディオ信号のパターン配線が他のアナログオーディオ信号のパターン配線より長くなることによる、当該一部のパターン配線を流れるアナログオーディオ信号へのノイズの重畳を抑制することができ、音質の劣化を防止することができる。

【0055】

上記第1実施形態では、入力されるDATA信号がFL_FR信号とSL_SR信号である場合について説明したが、これに限られず、他の信号でも構わない。要するに、I2Sフォーマットでは、左右に配置される一対のスピーカ(FchとRchのスピーカ)に対応する一対のデジタルオーディオ信号が混合されたDATA信号が1以上含まれるが、4ch以上のスピーカシステムに対応するオーディオディジタル機器では、各チャンネルのアナログオーディオ信号だけでなく、2つのアナログオーディオ信号(通常は左側の前後または右側の前後に配置されるスピーカに対応したアナログオーディオ信号)を混合した信号を生成して出力させる場合があるので、このような場合には、FL_FR信号とSL_SR信号に限られず、任意の組み合わせの2つのDATA信号の場合に適用することができるということである。

【0056】

図4は、本発明に係るオーディオ信号処理装置の第2実施形態を説明するための図である。

【0057】

第2実施形態は、本願発明を9.2chサラウンドスピーカシステムに適用されるオーディオアンプの、デジタルオーディオ信号からアナログオーディオ信号に変換して出力する回路構成に適用したもので、特に5.1chサラウンドスピーカシステムしか所有していないユーザを考慮し、5.1chサラウンドスピーカシステムに適用可能な6種類のオーディオ信号も切替出力できるようにしたものである。

【0058】

オーディオ信号処理装置A2は、入力される9.2chのI2S信号を9.2chのアナログオーディオ信号または5.1chのアナログオーディオ信号に変換して出力するものであり、9.2chサラウンド出力と5.1chサラウンド出力とを切り替えることができる。

【0059】

図5は、サラウンドオーディオシステムにおけるスピーカの配置を説明するための図であり、同図(a)は5.1chサラウンドの場合を示したものであり、同図(b)は9.2chサラウンドシステムの場合を示したものである。

【0060】

リスナーLが同図の上側を向いているとして、5.1chサラウンドの場合、同図(a)に示すように、リスナーLの前方左側にFLスピーカ、前方右側にFRスピーカ、前方中央にCスピーカ、後方左側にSLスピーカ、後方右側にSRスピーカの5つのスピーカと、低音専用のSWスピーカが配置される。9.2chサラウンドの場合、同図(b)に示すように、SLスピーカのさらに後方にSBLスピーカ、SRスピーカのさらに後方にSBRスピーカ、FLスピーカの左にFLHWスピーカ、FRスピーカの右にFRHWスピーカの4つのスピーカが追加され、SWスピーカの代わりに左側の低音専用のSWLスピーカと右側の低音専用のSWRスピーカが配置される。

【0061】

オーディオ信号処理装置A2には、9.2chサラウンド用のデジタルオーディオ信号が、I2Sフォーマットで入力される。この場合、DATA信号として、FL_FR信号、FLHW_FRHW信号(FLHWスピーカから出力される音声に変換されるFLHWデータとFRHWスピーカから出力される音声に変換されるFRHWデータとからなる。)、SL_SR信号、SBL_SBR信号(SBLスピーカから出力される音声に変換されるSBLデータとSBRスピーカから出力される音声に変換されるSBRデータとからなる。)、C信号(Cスピーカから出力される音声に変換されるCデータからなる。)、SWL_SWR信号(SWLスピーカから出力される音声に変換されるSWLデータとSWRスピーカから出力される音声に変換されるSWRデータとからなる。)が入力される。

【0062】

図4に示すように、オーディオ信号処理装置A2は、データ反転回路11,12、データ組替回路21,22、DA変換回路33,34,35,36,37,38、差動回路43,44,45,46,48、切替回路53,54,55,56,58、および出力端子63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68bを備えている。

【0063】

データ反転回路11,12は、図1に示すデータ反転回路10と同様の構成である。したがって、データ反転回路11は、FLHW_FRHW信号が入力されて、FLHWデータとFRHWデータとが入れ替えられたFRHW_FLHW信号をデータ組替回路21に出力する。また、データ反転回路12は、SBL_SBR信号が入力されて、SBLデータとSBRデータとが入れ替えられたSBR_SBL信号をデータ組替回路22に出力する。

【0064】

データ組替回路21,22は、図1に示すデータ組替回路20と同様の構成であり、その論理構成を示す図は図2に示すものと同様になる。したがって、データ組替回路21は、入力されるFL_FR信号およびFRHW_FLHW信号を組み替えて、FL_FLHW信号およびFRHW_FR信号として出力し、データ組替回路22は、入力されるSL_SR信号およびSBR_SBL信号を組み替えて、SL_SBL信号およびSBR_SR信号として出力する。

【0065】

DA変換回路33,34,35,36,38は、図1に示すDA変換回路31,32と同様の構成である。したがって、DA変換回路33はFL_FLHW信号をfl信号およびflhw信号(FLHWデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路34はFRHW_FR信号をfr信号およびfrhw信号(FRHWデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路35はSL_SBL信号をsl信号およびsbl信号(SBLデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路36はSBR_SR信号をsr信号およびsbr信号(SBRデータから変換されたアナログオーディオ信号)に変換して出力し、DA変換回路38はSWL_SWR信号をswl信号(SWLデータから変換されたアナログオーディオ信号)およびswr信号(SWRデータから変換されたアナログオーディオ信号)に変換して出力する。

【0066】

一方、C信号はLチャンネルがCデータでRチャンネルはローレベルのデータとなっており、Rチャンネルのデータを取り出す必要がないので、DA変換回路37はローパスフィルタを1つ備えるのみである。また、ワンビットDAC37aのDAコンバータは1つであってもよい。DA変換回路37は、C信号のCデータをアナログオーディオ信号に変換したc信号を出力する。

【0067】

差動回路43,44,45,46,48は、図1に示す差動回路41,42と同様の構成である。したがって、差動回路43はflhw信号とfl信号とを合成して出力し、差動回路44はfrhw信号とfr信号とを合成して出力し、差動回路45はsbl信号とsl信号とを合成して出力し、差動回路46はsbr信号とsr信号とを合成して出力し、差動回路48はswr信号とswl信号とを合成して出力する。

【0068】

出力端子63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68bは、各信号を出力する端子であり、それぞれ対応するスピーカが接続される。出力端子63b,64b,65b,66b,67b,68bにはそれぞれFLスピーカ、FRスピーカ、SLスピーカ、SRスピーカ、Cスピーカ、SWスピーカ(SWLスピーカ)が接続される(図5参照)。また、出力端子63a,64a,65a,66a,68aにはそれぞれFLHWスピーカ、FRHWスピーカ、SBLスピーカ、SBRスピーカ、SWRスピーカが接続される(図5(b)参照)。

【0069】

切替回路53,54,55,56,58は、9.2chサラウンド出力である第1の出力状態と5.1chサラウンド出力である第2の出力状態とを切り替えるものであり、連動して切り替えられる。

【0070】

9.2chに対応できるスピーカ(すなわち、図5(b)に示すスピーカシステム)が接続されている場合、切替回路53,54,55,56,58は、第1の出力状態(図4における下側の端子に接続されている状態)となる。この場合、DA変換回路33から出力されるfl信号が出力端子63bから出力され、DA変換回路34から出力されるfr信号が出力端子64bから出力され、DA変換回路35から出力されるsl信号が出力端子65bから出力され、DA変換回路36から出力されるsr信号が出力端子66bから出力され、DA変換回路38から出力されるswl信号が出力端子68bから出力される。DA変換回路37から出力されるc信号は、出力状態の切り替えに関係なく、出力端子67bから出力される。また、DA変換回路33から出力されるflhw信号が出力端子63aから出力され、DA変換回路34から出力されるfrhw信号が出力端子64aから出力され、DA変換回路35から出力されるsbl信号が出力端子65aから出力され、DA変換回路36から出力されるsbr信号が出力端子66aから出力され、DA変換回路38から出力されるswr信号が出力端子68aから出力される。

【0071】

5.1chに対応するスピーカ(すなわち、図5(a)に示すスピーカシステム)が接続されている場合、すなわち、出力端子63a,64a,65a,66a,68aにFLHWスピーカ、FRHWスピーカ、SBLスピーカ、SBRスピーカ、SWRスピーカが接続されていない場合、切替回路53,54,55,56,58は、第2の出力状態(図4における上側の端子に接続されている状態)となる。この場合、差動回路43から出力されるfl信号およびflhw信号の合成信号が出力端子63bから出力され、差動回路44から出力されるfr信号およびfrhw信号の合成信号が出力端子64bから出力され、差動回路45から出力されるsl信号およびsbl信号の合成信号が出力端子65bから出力され、差動回路46から出力されるsr信号およびsbr信号の合成信号が出力端子66bから出力され、差動回路48から出力されるswr信号およびswl信号の合成信号が出力端子68bから出力される。また、DA変換回路37から出力されるc信号が、出力端子67bから出力される。なお、出力端子63a,64a,65a,66a,68aから、それぞれflhw信号、frhw信号、sbl信号、sbr信号、swr信号が出力されるが、これらの出力端子にはスピーカが接続されていない。第2の出力状態において、出力端子63a,64a,65a,66a,68aとDA変換回路33,34,35,36,38との接続を切り離すようにしてもよい。

【0072】

これにより、オーディオ信号処理装置A2は、接続されているスピーカシステムに応じて、入力される9.2chのI2S信号を9.2chのアナログオーディオ信号または5.1chのアナログオーディオ信号に変換して出力することができる。

【0073】

本実施形態においては、FL_FR信号およびFLHW_FRHW信号がFL_FLHW信号およびFRHW_FR信号に変換されるので、DA変換回路33から出力される信号線とDA変換回路34から出力される信号線とが交差することがない。また、SL_SR信号およびSBL_SBR信号がSL_SBL信号およびSBR_SR信号に変換されるので、DA変換回路35から出力される信号線とDA変換回路36から出力される信号線とが交差することがない。したがって、DA変換回路33と差動回路43の部分の回路ブロック、DA変換回路34と差動回路44の部分の回路ブロック、DA変換回路35と差動回路45の部分の回路ブロック、および、DA変換回路36と差動回路46の部分の回路ブロックをそれぞれ独立してパターン配線すればよく、一方のパターン配線をジャンパー線によって迂回させたり、スルーホールと裏面側に形成したパターン配線とによって迂回させたりする必要がないので、複数のアナログオーディオ信号のパターン配線うち、一部のアナログオーディオ信号のパターン配線が他のアナログオーディオ信号のパターン配線より長くなることによる、当該一部のパターン配線を流れるアナログオーディオ信号へのノイズの重畳を抑制することができ、音質の劣化を防止することができる。

【0074】

なお、オーディオ信号処理装置A2に5.1chのI2S信号が入力された場合、出力状態にかかわらず、5.1chのアナログオーディオ信号が出力される。すなわち、FLHW_FRHW信号が入力されないので、データ組替回路21から出力されるFL_FLHW信号のRチャンネルはローレベルデータとなり、FRHW_FR信号のLチャンネルはローレベルデータとなり、DA変換回路33からflhw信号が出力されず、DA変換回路34からfrhw信号が出力されない。したがって、出力端子63a,64aからは信号が出力されず、出力端子63b,64bからは出力状態にかかわらず、それぞれfl信号、fr信号が出力される。同様にSBL_SBR信号が入力されないので、出力端子65a,66aからは信号が出力されず、出力端子65b,66bからは出力状態にかかわらず、それぞれsl信号、sr信号が出力される。また、SWL_SWR信号の代わりに、LチャンネルがSWデータ(SWスピーカから出力される音声に変換されるオーディオデータ)でRチャンネルがローレベルのデータであるSW信号が入力されるので、出力端子68aからは信号が出力されず、出力端子68bからは出力状態にかかわらず、sw信号(SWデータから変換されたアナログオーディオ信号)が出力される。

【0075】

上記第1実施形態および第2実施形態では、I2Sフォーマットで伝送されるデジタルオーディオ信号が入力された場合について説明したが、これに限られない。本発明は、2種類のオーディオデータが1ワードデータ毎に交互に配置されているデジタルオーディオ信号の場合に適用することができる。例えば、Right−Justified(右詰め)フォーマット、Left−Justified(左詰め)フォーマット、Left−JustifiedDSPフォーマット、32×FsPackedフォーマットなどの各種のフォーマットにも適用することができる。

【0076】

なお、上記第1および第2実施形態では、データ反転回路により一方のDATA信号のLチャンネルのオーディオデータとRチャンネルのオーディオデータとを入れ替えているが、これは2つのDATA信号の同じチャンネルのデータ同士を組み合わせたいからである。したがって、一方のDATA信号のLチャンネルのデータと他方のDATA信号のRチャンネルのデータとを組み合わせる場合は、データ反転回路を必要としない。

【0077】

本発明に係るオーディオ信号処理装置は、上述した実施形態に限定されるものではない。本発明に係るオーディオ信号処理装置の各部の具体的な構成は、種々に設計変更自在である。

【図面の簡単な説明】

【0078】

【図1】本発明に係るオーディオ信号処理装置の第1実施形態を説明するための図である。

【図2】データ組替回路の論理回路を示す図である。

【図3】データ組替回路の論理演算を説明するための図である。

【図4】本発明に係るオーディオ信号処理装置の第2実施形態を説明するための図である。

【図5】サラウンドオーディオシステムにおけるスピーカの配置を説明するための図である。

【図6】I2Sフォーマットで伝送されるデジタルオーディオ信号の信号波形を示す図である。

【図7】従来のオーディオ信号処理装置を説明するための図である。

【符号の説明】

【0079】

A1,A2 オーディオ信号処理装置

10,11,12 データ反転回路

20,21,22 データ組替回路(オーディオデータ生成手段)

201,202 NOT回路

203,204,205,206 AND回路

207,208 OR回路

31,32,33,34,35,36,37,38 DA変換回路(DA変換手段、第2のDA変換手段)

31a,32a ワンビットDAC

31b,31c,32b,32c ローパスフィルタ

41,42,43,44,45,46,48 差動回路(合成手段、第2の合成手段)

51,52,53,54,55,56,58 切替回路(切替手段)

61a,61b,62a,62b,63a,63b,64a,64b,65a,65b,66a,66b,67b,68a,68b 出力端子

【特許請求の範囲】

【請求項1】

第1のLチャンネルのデータと第1のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第2のLチャンネルのデータと第2のRチャンネルのデータとを前記ワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成するオーディオデータ生成手段と、

前記第3のオーディオデータを前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとに分離し、前記第1のLチャンネルのデータおよび前記第2のLチャンネルのデータをそれぞれ第1のアナログ信号および第2のアナログ信号に変換するDA変換手段と、

前記第1のアナログ信号と前記第2のアナログ信号とから第3のアナログ信号を合成する合成手段と、

を備えることを特徴とするオーディオ信号処理装置。

【請求項2】

前記第1のアナログ信号および前記第2のアナログ信号のみを出力する第1の出力状態と、少なくとも前記第3のアナログ信号を出力する第2の出力状態とを切り替える切替手段をさらに備えている、請求項1に記載のオーディオ信号処理装置。

【請求項3】

前記オーディオデータ生成手段には前記ワード単位で反転するワードクロックと、前記ワードクロックのローレベルと前記第1のLチャンネルのデータとが同期している前記第1のオーディオデータと、前記ワードクロックのハイレベルと前記第2のLチャンネルのデータが同期している前記第2のオーディオデータと、が入力されており、

前記オーディオデータ生成手段は、

前記第1のオーディオデータと前記ワードクロックを反転させた反転クロックとの論理積を演算することにより前記第1のLチャンネルのデータを抽出した第1の抽出オーディオデータを生成する第1のAND回路と、

前記第2のオーディオデータと前記ワードクロックとの論理積を演算することにより前記第2のLチャンネルのデータを抽出した第2の抽出オーディオデータを生成する第2のAND回路と、

前記第1の抽出オーディオデータと前記第2の抽出オーディオデータとの論理和を演算することにより前記第3のオーディオデータを生成するOR回路と、

を備えている、

請求項1または2に記載のオーディオ信号処理装置。

【請求項4】

前記第1のオーディオデータはI2Sフォーマットのデジタルオーディオデータであり、前記第2のオーディオデータはI2SフォーマットのデジタルオーディオデータのLチャンネルのデータとRチャンネルのデータとを入れ替えたデータである、請求項1ないし3のいずれかに記載のオーディオ信号処理装置。

【請求項5】

前記オーディオデータ生成手段は、前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第4のオーディオデータをさらに生成し、

生成された前記第4のオーディオデータを前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとに分離し、前記第1のRチャンネルのデータおよび前記第2のRチャンネルのデータをそれぞれ第4のアナログ信号および第5のアナログ信号に変換する第2のDA変換手段と、

前記第4のアナログ信号と前記第5のアナログ信号とから第6のアナログ信号を合成する第2の合成手段と、をさらに備え、

前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号のみが出力され、前記第2の出力状態に切り替えられている場合、少なくとも前記第3のアナログ信号および前記第6のアナログ信号が出力される、

請求項2ないし4のいずれかに記載のオーディオ信号処理装置。

【請求項6】

前記オーディオデータ生成手段、前記DA変換手段、前記第2のDA変換手段、前記合成手段、および前記第2の合成手段を少なくともそれぞれ2つずつ備え、

9.2ch用の6つのオーディオデータが入力され、

前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号を9.2ch用のアナログ信号として出力し、前記切替手段により前記第2の出力状態に切り替えられている場合、前記第3のアナログ信号および前記第6のアナログ信号を5.1ch用のアナログ信号として出力する、

請求項5に記載のオーディオ信号処理装置。

【請求項1】

第1のLチャンネルのデータと第1のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第1のオーディオデータと、第2のLチャンネルのデータと第2のRチャンネルのデータとを前記ワード単位で交互にシリアルに配列してなる第2のオーディオデータとから、前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとをワード単位で交互にシリアルに配列してなる第3のオーディオデータを生成するオーディオデータ生成手段と、

前記第3のオーディオデータを前記第1のLチャンネルのデータと前記第2のLチャンネルのデータとに分離し、前記第1のLチャンネルのデータおよび前記第2のLチャンネルのデータをそれぞれ第1のアナログ信号および第2のアナログ信号に変換するDA変換手段と、

前記第1のアナログ信号と前記第2のアナログ信号とから第3のアナログ信号を合成する合成手段と、

を備えることを特徴とするオーディオ信号処理装置。

【請求項2】

前記第1のアナログ信号および前記第2のアナログ信号のみを出力する第1の出力状態と、少なくとも前記第3のアナログ信号を出力する第2の出力状態とを切り替える切替手段をさらに備えている、請求項1に記載のオーディオ信号処理装置。

【請求項3】

前記オーディオデータ生成手段には前記ワード単位で反転するワードクロックと、前記ワードクロックのローレベルと前記第1のLチャンネルのデータとが同期している前記第1のオーディオデータと、前記ワードクロックのハイレベルと前記第2のLチャンネルのデータが同期している前記第2のオーディオデータと、が入力されており、

前記オーディオデータ生成手段は、

前記第1のオーディオデータと前記ワードクロックを反転させた反転クロックとの論理積を演算することにより前記第1のLチャンネルのデータを抽出した第1の抽出オーディオデータを生成する第1のAND回路と、

前記第2のオーディオデータと前記ワードクロックとの論理積を演算することにより前記第2のLチャンネルのデータを抽出した第2の抽出オーディオデータを生成する第2のAND回路と、

前記第1の抽出オーディオデータと前記第2の抽出オーディオデータとの論理和を演算することにより前記第3のオーディオデータを生成するOR回路と、

を備えている、

請求項1または2に記載のオーディオ信号処理装置。

【請求項4】

前記第1のオーディオデータはI2Sフォーマットのデジタルオーディオデータであり、前記第2のオーディオデータはI2SフォーマットのデジタルオーディオデータのLチャンネルのデータとRチャンネルのデータとを入れ替えたデータである、請求項1ないし3のいずれかに記載のオーディオ信号処理装置。

【請求項5】

前記オーディオデータ生成手段は、前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとをワード単位で交互にシリアルに配列してなる第4のオーディオデータをさらに生成し、

生成された前記第4のオーディオデータを前記第1のRチャンネルのデータと前記第2のRチャンネルのデータとに分離し、前記第1のRチャンネルのデータおよび前記第2のRチャンネルのデータをそれぞれ第4のアナログ信号および第5のアナログ信号に変換する第2のDA変換手段と、

前記第4のアナログ信号と前記第5のアナログ信号とから第6のアナログ信号を合成する第2の合成手段と、をさらに備え、

前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号のみが出力され、前記第2の出力状態に切り替えられている場合、少なくとも前記第3のアナログ信号および前記第6のアナログ信号が出力される、

請求項2ないし4のいずれかに記載のオーディオ信号処理装置。

【請求項6】

前記オーディオデータ生成手段、前記DA変換手段、前記第2のDA変換手段、前記合成手段、および前記第2の合成手段を少なくともそれぞれ2つずつ備え、

9.2ch用の6つのオーディオデータが入力され、

前記切替手段により前記第1の出力状態に切り替えられている場合、前記第1のアナログ信号、前記第2のアナログ信号、前記第4のアナログ信号、および前記第5のアナログ信号を9.2ch用のアナログ信号として出力し、前記切替手段により前記第2の出力状態に切り替えられている場合、前記第3のアナログ信号および前記第6のアナログ信号を5.1ch用のアナログ信号として出力する、

請求項5に記載のオーディオ信号処理装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【公開番号】特開2010−114640(P2010−114640A)

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願番号】特願2008−285316(P2008−285316)

【出願日】平成20年11月6日(2008.11.6)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

【公開日】平成22年5月20日(2010.5.20)

【国際特許分類】

【出願日】平成20年11月6日(2008.11.6)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

[ Back to top ]