スイッチングアンプ

【課題】 オペアンプを設けることなく、スイッチ素子に流れる過電流を検出することができるスイッチングアンプを提供すること。

【解決手段】 スイッチングアンプは、MOSFET15,16と、アノードがMOSFET15のソースに接続されたダイオードD1と、ダイオードD1のカソードと接地電位との間に接続された抵抗1と、ダイオードD1のカソードの電圧を分圧して、トランジスタQ1のベースに供給する抵抗2および抵抗3と、抵抗R2およびR3によって分圧された電圧がベースに供給されることにより、MOSFET15の両端電圧が所定電圧以上であるか否かを検出するトランジスタQ1と、ダイオードD1のカソードと電源+VCCとの間に接続されたコンデンサC1とを備える。

【解決手段】 スイッチングアンプは、MOSFET15,16と、アノードがMOSFET15のソースに接続されたダイオードD1と、ダイオードD1のカソードと接地電位との間に接続された抵抗1と、ダイオードD1のカソードの電圧を分圧して、トランジスタQ1のベースに供給する抵抗2および抵抗3と、抵抗R2およびR3によって分圧された電圧がベースに供給されることにより、MOSFET15の両端電圧が所定電圧以上であるか否かを検出するトランジスタQ1と、ダイオードD1のカソードと電源+VCCとの間に接続されたコンデンサC1とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、出力段のスイッチ素子に流れる過電流を検出するスイッチングアンプに関する。

【背景技術】

【0002】

図8は、従来のスイッチングアンプにおける、正側のMOSFET51、負側のMOSFET52及び過電流検出回路(図8では負側のみを記載)を示す概略回路図である。MOSFET51,52は、図示しないドライバから出力される駆動信号(PWM信号)がハイレベルのときにオン状態となり、駆動信号がローレベルのときにオフ状態になる。MOSFET51がオン状態の時に、出力端子OUTには電源電圧+VCCが出力される。MOSFET52がオン状態の時に、出力端子OUTには電源電圧−VCCが出力される。

【0003】

過電流検出回路は、スイッチ53と比較回路(オペアンプ)54とを備える。スイッチ53は、MOSFET52に供給される駆動信号がハイレベル(すなわち、MOSFET52がオン状態)のときにオン状態になり、ローレベル(すなわち、MOSFET52がオフ状態)のときにオフ状態になる。比較回路54は、正側入力端子に基準電圧Vrefが入力され、負側入力端子には、スイッチ53がオン状態のときに、MSOFET52の両端電圧(ドレイン−ソース間電圧)が入力される。MOSFET52は内部にオン抵抗を有しているので、MOSFET52のドレイン−ソース間に流れる電流にオン抵抗を乗算した値の電圧が、比較回路54の負側入力端子に入力される。MOSFET52のドレイン−ソース間に過電流が流れる場合に、ドレイン−ソース間電圧が高くなり、比較回路54の負側入力端子に入力される電圧が高くなり、比較回路54は、MOSFET52に過電流が流れたことを示す信号を出力する。

【0004】

従来の過電流検出回路においては、比較回路(オペアンプ)54を備えているので、コストが高くなるという問題がある。また、比較回路(オペアンプ)54に電圧を供給する電源回路を別途設ける必要があり、さらにコストが高くなるという問題がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−205662号

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来の課題を解決するためになされたものであり、その目的は、オペアンプを設けることなく、スイッチ素子に流れる過電流を検出することができるスイッチングアンプを提供することである。

【課題を解決するための手段】

【0007】

本発明の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、前記第1ダイオードのカソードと前記第1電源との間に接続された第1コンデンサとを備える。

【0008】

本実施形態によると、第1スイッチ素子に流れる過電流を検出することができる。また、第1ダイオードを備えることにより、第1スイッチ素子がオフ状態の時に、第1トランジスタの制御電極から第2スイッチ素子へと電流が流れることが防止され、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。また、第1スイッチ素子がオフ状態の時に、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に流れる電流により、第1ダイオードのカソード電圧が減少するが、第1コンデンサを備えることによって、第1抵抗と第1コンデンサとの時定数により、第1ダイオードのカソード電圧の減少速度が緩やかになり、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0009】

好ましい実施形態においては、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとをさらに備える。

【0010】

本実施形態によると、第2スイッチ素子に流れる過電流を検出することができる。また、第2ダイオードを備えることにより、第2スイッチ素子がオフ状態の時に、第1スイッチ素子から第2トランジスタの制御電極に電流が流れることが防止され、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。また、第2スイッチ素子がオフ状態の時に、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に流れる電流により、第2ダイオードのアノード電圧が増加するが、第2コンデンサを備えることによって、第4抵抗と第2コンデンサとの時定数により、第2ダイオードのアノード電圧の増加速度が緩やかになり、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧以上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0011】

好ましい実施形態においては、前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタをさらに備える。

【0012】

第3トランジスタを備えることによって、第1スイッチ素子がオフ状態の期間が長い場合でも、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に電流が流れることを阻止し、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0013】

好ましい実施形態においては、前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタをさらに備える。

【0014】

第4トランジスタを備えることによって、第2スイッチ素子がオフ状態の期間が長い場合でも、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に電流が流れることを阻止し、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0015】

本発明の別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとを備える。

【0016】

本発明のさらに別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタとを備える。

【0017】

本実施形態によると、第1スイッチ素子に流れる過電流を検出することができる。また、第3トランジスタを備えることによって、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に電流が流れることを阻止し、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0018】

本発明のさらに別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタとを備える。

【0019】

本実施形態によると、第2スイッチ素子に流れる過電流を検出することができる。第4トランジスタを備えることによって、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に電流が流れることを阻止し、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧以上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【発明の効果】

【0020】

本発明によると、オペアンプを設けることなく、スイッチ素子に流れる過電流を検出することができる。従って、コストを安価にすることができ、オペアンプ用の電源を別途設ける必要がない。

【発明を実施するための形態】

【0021】

以下、本発明の好ましい実施形態について、図面を参照して具体的に説明するが、本発明はこれらの実施形態には限定されない。図1は、本実施形態のスイッチングアンプ10を示す概略回路図である。スイッチングアンプ10は、パルス幅変調回路20、ドライバ11、スイッチング出力回路12、LPF(Low Pass Filter)13および検出回路19(図2のみに記載)を備える。

【0022】

パルス幅変調回路20は、入力信号(例えば、オーディオ信号)をパルス幅変調して第1のPWM信号OUT1および第2のPWM信号OUT2を生成する。第1のPWM信号OUT1および第2のPWM信号OUT2は、一方がハイレベルの信号である場合に他方がローレベルの信号である。

【0023】

ドライバ11は、第1のPWM信号OUT1および第2のPWM信号OUT2が入力され、電源電圧に基づいて、後述のスイッチ素子を駆動するための駆動信号DRV1およびDRV2を出力する。

【0024】

スイッチング出力回路12は、第1の電源(例えば正の電源+VCC)と第2の電源(例えば負の電源−VCC)との間に接続され、駆動信号に応答して正の電源+VCCまたは負の電源−VCCを出力する。スイッチング出力回路12は、スイッチ素子(本例ではMOSFET15、16)を有する。

【0025】

MOSFET15は、ソースがLPF17(つまり、スイッチングアンプの出力)に接続され、ゲートがドライバ11に接続され、ドレインが電源電圧+VCCの正側に接続されている。MOSFET16は、ドレインがLPF17(つまり、スイッチングアンプの出力)に接続され、ゲートがドライバ11に接続され、ソースが電源電圧−VCCの負側に接続されている。

【0026】

LPF13は、スイッチング出力回路12の出力端とスイッチングアンプ10の出力端との間に接続され、高周波成分を除去して、スピーカー等の負荷に出力する。LPF13は、コイル17およびコンデンサ18を有する。

【0027】

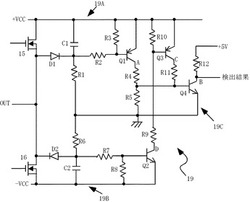

図2は、MOSFET15,16、及び、検出回路19を示す回路図である。検出回路19は、MOSFET15,16に過電流が流れていることを検出し、その旨を示す信号を出力する。過電流が流れていることを示す信号は、例えば、ドライバ11に供給され、ドライバ11からの駆動信号DRV1,DRV2の出力が停止される。または、過電流が流れていることを示す信号は、マイコンに供給され、マイコンからの指示によってパルス幅変調回路20からのPWM信号の出力を停止する。

【0028】

検出回路19は、正側検出部19Aと、負側検出部19Bと、出力部19Cとを含む。

【0029】

正側検出部19Aは、MOSFET15に流れる電流が過電流であることを検出する。MOSFET15はドレイン−ソース間にオン抵抗を有しており、ドレイン−ソース間に流れる電流の電流値にオン抵抗の値を乗算することによって、ドレイン−ソース間電圧が得られる。従って、ドレイン−ソース間に流れる電流が変化することにより、ドレイン−ソース間電圧が変化する。従って、MOSFET15のドレイン−ソース間電圧が所定電圧(第1所定電圧)以上であることを検出することによって、MOSFET15に流れる電流が過電流であることを検出することができる。

【0030】

正側検出部19Aは、ダイオード(第1ダイオード)D1、トランジスタ(第1トランジスタ)Q1、コンデンサ(第1コンデンサ)C1、及び、抵抗R1〜R5を含む。トランジスタQ1は、MOSFET15の両端電圧が所定電圧以上であることを検出する。ダイオードD1は、MOSFET15がオン状態(MOSFET16がオフ状態)のときに、MOSFET15の両端電圧が所定電圧未満であれば、トランジスタQ1のベースに導通開始電圧より大きい電圧を供給することにより、トランジスタQ1をオフ状態にさせ、トランジスタQ1にMOSFET15の両端電圧が所定電圧未満であることを検出させる。一方、MOSFET15の両端電圧が所定電圧以上であれば、トランジスタQ1のベースに導通開始電圧以下の電圧を供給することにより、トランジスタQ1をオン状態にさせ、トラジスタQ1にMOSFET15の両端電圧が所定電圧以上であることを検出させる。

【0031】

ダイオードD1は、アノードがMOSFET15のソースに接続され、カソードがコンデンサC1を介して電源+VCCに接続され、抵抗R1を介して接地電位(基準電位)に接続され、かつ、抵抗R2を介してトランジスタQ1のベースに接続されている。トランジスタQ1は、ベースが抵抗R3を介して電源+VCCに接続され、エミッタが電源+VCCに接続され、コレクタが抵抗R4、R5を介して接地電位に接続されている。

【0032】

ダイオードD1は、MOSFET15がオン状態のときにオン状態になり、MOSFET15がオフ状態のときオフ状態になる。MOSFET15のオン抵抗が53mΩ、過電流が11.3A以上の電流である場合、所定電圧は0.6Vに設定される。従って、MOSFET15のドレイン−ソース間電圧が0.6V以上である場合に、MOSFET15のソース電位が(+VCC−0.6)V以下に、ダイオードD1のカソード電位が(+VCC−1.2)V以下となり、トランジスタQ1に過電流であることを検出させる。一方、MOSFET15のドレイン−ソース間電圧が0.6V未満である場合に、MOSFET15のソース電位が(+VCC−0.6)Vより大きく、ダイオードD1のカソード電位が(+VCC−1.2)Vよりも大きくなり、トランジスタQ1に過電流でないことを検出させる。

【0033】

トランジスタQ1は、ダイオードD1のカソード電位が(+VCC−1.2)Vよりも大きい場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)よりも大きくなり、オフ状態になる。詳細には、ダイオードD1のカソード電圧が、抵抗R2及びR3によって分圧され、トランジスタQ1のベースに供給されるが、当該分圧された電圧がトランジスタQ1の導通開始電圧よりも大きくなっている。

【0034】

一方、トランジスタQ1は、ダイオードD1のカソード電位が(+VCC−1.2)V以下である場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)以下となり、オン状態になる。詳細には、ダイオードD1のカソード電圧が、抵抗R2及びR3によって分圧されて、トランジスタQ1のベースに供給されるが、当該分圧された電圧がトランジスタQ1の導通開始電圧以下になっている。

【0035】

抵抗R2,R3は、上記の通り、ダイオードD1のカソード電圧を分圧してトランジスタQ1のベース電圧を供給する。従って、抵抗R2,R3の各抵抗値は、MOSFET15のドレイン−ソース間電圧が0.6V以上になり、ダイオードD1のカソード電圧が(+VCC−1.2)V以下であるときに、トランジスタQ1のベース−エミッタ間電圧がトランジスタQ1の導通開始電圧(0.6V)以下になるように適切な値に設定されている。

【0036】

ダイオードD1は、MOSFET15がオフ状態(MOSFET16がオン状態)のときに、オフ状態なることにより、正側検出部19A(トランジスタQ1)をMOSFET15,16から電気的に切り離すために設けられる。ダイオードD1がオフになることにより、トランジスタQ1から抵抗R2を介してMOSFET16に電流が流れて、トランジスタQ1がオン状態になることを防止する。

【0037】

コンデンサC1は、MOSFET15がオン状態のときに、電源+VCCからMOSFET15、ダイオードD1を介して電流が流れ、充電されることによって、ダイオードD1のカソード電圧を定める。また、コンデンサC1は、一瞬だけMOSFET15のドレイン−ソース間電圧が非常に大きくなった場合には、ダイオードD1のカソード電圧を一瞬だけ減少させず、ダイオードD1のカソード電圧を安定化させることにより、トランジスタQ1が誤ってオン状態になることを防止する。

【0038】

コンデンサC1は、MOSFET15がオフ状態(MOSFET16がオン状態)のときに、ダイオードD1がオフ状態になるためにトランジスタQ1がオン状態になることを阻止する。つまり、MOSFET15がオフ状態のとき、電源+VCCから抵抗R3、R2、R1を介して接地電位に電流が流れ、その結果、ダイオードD1のカソード電圧が減少する。仮に、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少してしまうと、トランジスタQ1がオン状態になってしまい、MOSFET15に過電流が流れていると誤検出される。しかし、コンデンサC1を設けることによって、コンデンサC1と抵抗R1との時定数によって、ダイオードD1のカソード電圧の減少速度を緩やかにできる。従って、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少しないようにすることができる。

【0039】

負側検出部19Bは、MOSFET16に流れる電流が過電流であることを検出する。MOSFET16はドレイン−ソース間にオン抵抗を有しており、ドレイン−ソース間に流れる電流の電流値にオン抵抗の値を乗算することによって、ドレイン−ソース間電圧が得られる。従って、ドレイン−ソース間に流れる電流が変化することにより、ドレイン−ソース間電圧が変化し、MOSFET16のドレイン−ソース間電圧が所定電圧(第2所定電圧、本例では、第1所定電圧と同じ電圧である)以上であることを検出することによって、MOSFET16に流れる電流が過電流であることを検出することができる。

【0040】

負側検出部19Bは、ダイオード(第2ダイオード)D2、トランジスタ(第2トランジスタ)Q2,トランジスタQ3、コンデンサ(第2コンデンサ)C2、及び、抵抗R6〜R11を含む。トランジスタQ2は、MOSFET16の両端電圧が所定電圧以上であることを検出する。ダイオードD2は、MOSFET16がオン状態(MOSFET15がオフ状態)のときに、MOSFET16の両端電圧が所定電圧未満であれば、トランジスタQ2のベースに導通開始電圧未満の電圧を供給し、トランジスタQ2をオフ状態にさせ、トランジスタQ2にMOSFET16の両端電圧が所定電圧未満であることを検出させる。一方、MOSFET16の両端電圧が所定電圧以上であれば、トランジスタQ2のベースに導通開始電圧以上の電圧を供給し、トランジスタQ2をオン状態にさせ、トラジスタQ2にMOSFET16の両端電圧が所定電圧以上であることを検出させる。

【0041】

ダイオードD2は、カソードがMOSFET16のドレインに接続され、アノードがコンデンサC2を介して電源−VCCに接続され、抵抗R6を介して接地電位に接続され、かつ、抵抗R7を介してトランジスタQ2のベースに接続されている。トランジスタQ2は、ベースが抵抗R8を介して電源−VCCに接続され、エミッタが電源−VCCに接続され、コレクタが抵抗R9,R10を介して電源+VCCに接続されている。トランジスタQ3は、ベースが抵抗R9とR10との接続点に接続され、コレクタが抵抗R11を介してトランジスタQ4のベースに接続され、エミッタが電源+VCCに接続されている。

【0042】

ダイオードD2は、MOSFET16がオン状態のときにオン状態になり、MOSFET16がオフ状態のときにオフ状態になる。MOSFET16のオン抵抗が53mΩ、過電流が11.3A以上の電流である場合、所定電圧は0.6Vに設定される。従って、MOSFET16のドレイン−ソース間電圧が0.6V以上である場合に、MOSFET16のドレイン電位が(−VCC+0.6)V以上に、ダイオードD2のアノード電位が(−VCC+1.2)V以上になり、トランジスタQ1に過電流であることを検出させる。一方、MOSFET16のドレイン−ソース間電圧が0.6V未満である場合に、MOSFET16のドレイン電位が(−VCC+0.6)V未満に、ダイオードD2のアノード電位が(−VCC+1.2)V未満になり、トランジスタQ2に過電流電でないことを検出させる。

【0043】

トランジスタQ2は、ダイオードD2のアノード電位が(−VCC+0.6)Vよりも小さい場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)未満となり、オフ状態になる。つまり、ダイオードD2のアノード電圧が、抵抗R7及びR8によって分圧されて、トランジスタQ2のベースに供給されるが、当該分圧された電圧がトランジスタQ2の導通開始電圧未満になっている。

【0044】

一方、トランジスタQ2は、ダイオードD2のアノード電位が(−VCC+0.6)V以上の場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)以上となり、オン状態になる。つまり、ダイオードD2のアノード電圧が、抵抗R7及びR8によって分圧されて、トランジスタQ2のベースに供給されるが、当該分圧された電圧が、トランジスタQ2の導通開始電圧以上になっている。

【0045】

抵抗R7,R8は、上記の通り、ダイオードD2のアノード電圧を分圧してトランジスタQ2のベース電圧を供給する。従って、抵抗R7,R8の各抵抗値は、MOSFET16のドレイン−ソース間電圧が0.6V以上になり、ダイオードD2のアノード電圧が(−VCC+1.2)V以上であるときに、トランジスタQ2のベース−エミッタ間電圧がトランジスタQ2の導通開始電圧(0.6V)以上になるように適切な値に設定されている。

【0046】

ダイオードD2は、MOSFET16がオフ状態(MOSFET15がオン状態)のときに、オフ状態なることにより、負側検出部19B(トランジスタQ2)をMOSFET15,16から電気的に切り離す。ダイオードD2がオフ状態になることにより、MOSFET15から抵抗R7を介してトランジスタQ2のベースに電流が流れて、トランジスタQ2がオン状態になることを防止することができる。

【0047】

コンデンサC2は、MOSFET16がオン状態の時に、ダイオードD2との接続点がダイオードD2、MOSFET16を介して電源−VCCに接続された状態になり、当該点の電圧が減少することにより、ダイオードD2のアノード電圧を定める。また、コンデンサC2は、一瞬だけMOSFET16のドレイン−ソース間電圧が非常に大きくなった場合には、ダイオードD2のアノード電圧を増加させず、当該電圧を安定化させることによって、トランジスタQ2を一瞬だけオン状態にすることを防止する。

【0048】

コンデンサC2は、MOSFET16がオフ状態(MOSFET15がオン状態)のときに、ダイオードD2がオフ状態になるためにトランジスタQ2がオン状態になることを阻止する。つまり、MOSFET16がオフ状態のとき、接地電位から抵抗R6、R7、R8を介して電源−VCCに電流が流れ、その結果、ダイオードD2のアノード電圧が増加する。仮に、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加してしまうと、トランジスタQ2がオン状態になってしまい、MOSFET16に過電流が流れていると誤検出される。しかし、コンデンサC2を設けることによって、コンデンサC2と抵抗R6の時定数によって、ダイオードD2のアノード電圧の増加速度を緩やかにできる。従って、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加しないようにすることができる。

【0049】

トランジスタQ3は、トランジスタQ2の出力信号を反転させる。トランジスタQ3は、トランジスタQ2がオフ状態のときに、ベースが電源+VCCに接続された状態になるのでオフ状態になる。一方、トランジスタQ3は、トランジスタQ2がオン状態のときに、ベースが電源−VCCに接続された状態になるのでオン状態になる。

【0050】

出力部19Cは、MOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号を出力する。出力部19Cは、トランジスタQ4及び抵抗R12を含む。トランジスタQ4は、ベースが抵抗R4とR5との接続点に接続され、抵抗R11を介してトランジスタQ3のコレクタに接続され、エミッタが接地電位に接続され、コレクタが抵抗R12を介して+5V電源に接続され、MOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号を出力する出力端になっている。

【0051】

トランジスタQ4は、トランジスタQ1がオン状態であるとき、ベースが電源電圧+VCCに接続された状態になるので、オン状態になる。トランジスタQ4は、トランジスタQ3がオン状態であるとき、ベースが電源電圧+VCCに接続された状態になるので、オン状態になる。トランジスタQ4がオン状態になると、トランジスタQ4のコレクタは、接地電位に接続された状態になり、ローレベルになり、このローレベルの信号がMOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号となる。トランジスタQ4は、トランジスタQ1,Q3がオフ状態である場合、ベースが接地電位に接続された状態になり、オフ状態になる。トランジスタQ4がオフ状態になると、トランジスタQ4のコレクタは、+5V電源に接続された状態になり、ハイレベルになり、このハイレベルの信号がMOSFET15及び16のドレイン−ソース間電圧が所定電圧未満であることを示す信号となる。

【0052】

以上の構成を有する検出回路19についてその動作を説明する。図3は、図2の検出回路19の各点における電圧波形を示している。なお、上記所定電圧を0.6Vとして説明する。

【0053】

[MOSFET15がオン状態、MOSFET16がオフ状態、MOSFET15に過電流が流れていない場合]

MOSFET15のドレイン−ソース間電圧が所定電圧0.6V未満であるので、MOSFET15のソース電位は(+VCC−0.6)Vより大きくなっている。ダイオードD1は、MOSFET15がオン状態であるので、オン状態になっている。ダイオードD1のカソード電位が(+VCC−1.2)Vより大きく、トランジスタQ1のベース電位も高くなり、トランジスタQ1のベース−エミッタ間電圧が導通開始電圧より大きいので、トランジスタQ1はオフ状態である。従って、トランジスタQ1のコレクタは接地電位に接続された状態になり、コレクタ電圧(A点電圧)はローレベルになっている。

【0054】

ダイオードD2のカソード電位はMOSFET15のソース電位((+VCC−0.6V)以上)になっているので、アノード電位よりも大きく、ダイオードD2はオフ状態になっている。従って、接地電位から抵抗R6を介して流れる電流は、MOSFET16には流れず、抵抗R7、R8を介して電源−VCCへと流れる。その結果、抵抗R6とコンデンサC2との時定数に応じて、ダイオードD2のアノード電圧が緩やかな速度で増加する。ダイオードD2のアノード電圧が、トランジスタQ2をオン状態にする電圧以上に増加する前に、MOSFET16がオン状態になるので、コンデンサC2のダイオードD2のアノードとの接続点が電源−VCCに接続された状態になり、当該点の電圧が低下し、ダイオードD2のアノード電圧が減少する。従って、MOSFET16がオフ状態の間には、ダイオードD2のアノード電圧はトランジスタQ2をオン状態にする電圧以上に増加しないので、トランジスタQ2はオフ状態を継続する。

【0055】

トランジスタQ2がオフ状態であるので、トランジスタQ3は、ベースが電源電圧+VCCに接続された状態であり、オフ状態になっている。トランジスタQ3のコレクタ電圧(C点電圧)はローレベルになっている。

【0056】

従って、トランジスタQ4は、トランジスタQ1,Q3が共にオフ状態であるので、ベースが接地電位に接続された状態になり、オフ状態になっている。トランジスタQ4のコレクタ電圧(B点電圧)は、ハイレベルになっており、このハイレベルの信号がMOSFET15に過電流が流れていないことを示す信号として出力される。

【0057】

[MOSFET15がオン状態、MOSFET16がオフ状態、MOSFET15に過電流が流れている場合]

MOSFET15のドレイン−ソース間電圧が所定電圧0.6V以上であるので、MOSFET15のソース電位は(+VCC−0.6)V以下になっている。ダイオードD1は、MOSFET15がオン状態であるので、オン状態になっている。ダイオードD1のカソード電圧が(+VCC−1.2)V以下になり、トランジスタQ1のベース電圧が低くなるので、トランジスタQ1のベース−エミッタ間電圧が導通開始電圧以下になり、トランジスタQ1がオン状態になる。トランジスタQ1のコレクタは電源電圧+VCCに接続された状態になり、コレクタ電圧(A点電圧)はハイレベルになっている(時刻t1〜t2)。

【0058】

その結果、トランジスタQ4のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ4がオン状態になる。トランジスタQ4は、コレクタが接地電位に接続された状態になり、コレクタ電圧(B点電圧)がローレベルになり(時刻t1〜t2)、このローレベルの信号がMOSFET15に過電流が流れていることを示す信号として出力される。

【0059】

[MOSFET16がオン状態、MOSFET15がオフ状態、MOSFET16に過電流が流れていない場合]

MOSFET16のドレイン−ソース間電圧が所定電圧0.6V未満であるので、MOSFET16のドレイン電位は(−VCC+0.6)V未満になっている。ダイオードD2は、MOSFET16がオン状態であるので、オン状態になっている。ダイオードD2のアノード電位が(−VCC+1.2)V未満であり、トランジスタQ2のベース電位も低くなり、トランジスタQ2のベース−エミッタ間電圧が導通開始電圧より小さいので、トランジスタQ2はオフ状態である。従って、トランジスタQ2のコレクタは電源電圧+VCCに接続された状態になり、コレクタ電圧(D点電圧)はハイレベルになっている。

【0060】

トランジスタQ3は、ベースが電源電圧+VCCに接続された状態であり、オフ状態になっている。トランジスタQ3のコレクタ電圧(C点電圧)は、ローレベルになっている。

【0061】

ダイオードD1のアノード電位はMOSFET16のドレイン電位((−VCC+0.6V)未満)になっているので、カソード電位よりも小さく、ダイオードD1はオフ状態になっている。従って、抵抗R1を介して接地電位に流れる電流は、MOSFET15からは流れず、電源+VCCから抵抗R3、R2を介して流れる。その結果、抵抗R1とコンデンサC1との時定数に応じて、ダイオードD1のカソード電圧が緩やかな速度で減少する。ダイオードD1のカソード電圧が、トランジスタQ1をオン状態にする電圧以下に減少する前に、MOSFET15がオン状態になるので、コンデンサC1が電源+VCCからMOSFET15、ダイオードD1を介して流れる電流によって再度充電され、ダイオードD1のカソード電圧が増加する。従って、MOSFET15がオフ状態の間には、ダイオードD1のカソード電圧はトランジスタQ1をオン状態にする電圧以下に減少しないので、トランジスタQ1はオフ状態を継続する。

【0062】

トランジスタQ1のコレクタは接地電位に接続された状態であり、トランジスタQ1のコレクタ電圧(A点電圧)は、ローレベルになっている。

【0063】

従って、トランジスタQ4は、トランジスタQ1,Q3が共にオフ状態であるので、ベースが接地電位に接続された状態になり、オフ状態になっている。トランジスタQ4のコレクタ電圧(B点電圧)は、ハイレベルになっており、このハイレベルの信号がMOSFET16に過電流が流れていないことを示す信号として出力される。

【0064】

[MOSFET16がオン状態、MOSFET15がオフ状態、MOSFET16に過電流が流れている場合]

MOSFET16のドレイン−ソース間電圧が所定電圧0.6V以上であるので、MOSFET16のドレイン電位は(−VCC+0.6)V以上になっている。ダイオードD2は、MOSFET16がオン状態であるので、オン状態になっている。ダイオードD2のアノード電位が(−VCC+1.2V)以上になり、トランジスタQ2のベース電位が高くなるので、トランジスタQ2のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ2がオン状態になる。トランジスタQ2のコレクタは電源電圧−VCCに接続された状態になり、コレクタ電圧(D点電圧)はローレベルになっている(時刻t3〜t4)。

【0065】

トランジスタQ2がオン状態になると、トランジスタQ3のベースが接地電位に接続された状態になり、オン状態になる。トランジスタQ3のコレクタは、電源電圧+VCCに接続された状態になり、コレクタ電圧(C点電圧)がハイレベルになる(時刻t3〜t4)。

【0066】

その結果、トランジスタQ4のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ4がオン状態になる。トランジスタQ4は、コレクタが接地電位に接続された状態になり、コレクタ電圧(B点電圧)がローレベルになり(時刻t3〜t4)、このローレベルの信号がMOSFET16に過電流が流れていることを示す信号として出力される。

【0067】

以上のように、本実施形態によると、ダイオードD1,D2、トランジスタQ1,Q2、コンデンサC1,C2等を備えることによって、MOSFET15,16の過電流を検出することができる。

【0068】

また、検出回路19は、MOSFET15,16の温度が所定温度以上であることを検出し、その旨を示す検出結果を出力してもよい。MOSFET15,16のオン抵抗の抵抗値は、温度によって変化し、温度が高くなるにつれて略一次関数的に抵抗値が高くなる。従って、温度が変化することにより、MOSFETのドレイン−ソース間電圧が変化する。従って、上記の実施例のように、MOSFET15,16のドレイン−ソース間電圧を検出することによって、MOSFET15,16に流れる過電流に加えて、MOSFET15,16の温度が所定温度以上であることを検出することができる。

【0069】

図4は本発明の別の好ましい実施形態による検出回路29を示す概略回路図である。検出回路29は、図2の検出回路19の各構成のうち、正側検出部19Aのみを有し、MOSFET15に流れる過電流のみを検出できる。図5は本発明の別の好ましい実施形態による検出回路39を示す概略回路図である。検出回路39は、図2の検出回路19の各構成のうち、負側検出部19Bのみを有し、MOSFET16に流れる過電流のみを検出できる。

【0070】

図6は本発明の別の好ましい実施形態による検出回路49を示す回路図である。検出回路49は、図2の検出回路19の構成に加えて、トランジスタQ31、Q32、抵抗R31〜R34、ダイオードD31,D32をさらに有する。

【0071】

図2の検出回路19では、MOSFET15がオフ状態の間に、コンデンサC1と抵抗R1との時定数により、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少することを防止している。しかし、図1のパルス幅変調回路20に、例えば、本出願人が特開2004−320182の特に背景技術に記載するパルス幅変調回路を使用すると、入力信号の振幅値が大きくなると、PWM信号の周期が大きくなり(周波数が小さくなり)、その結果、MOSFET15のオフ期間が長くなる。その結果、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少してしまい、MOSFET15に過電流が流れていると誤検出されてしまうという問題がある。

【0072】

同様に、図2の検出回路19では、MOSFET16がオフ状態の間に、コンデンサC2と抵抗R6との時定数により、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加することを防止している。しかし、図1のパルス幅変調回路20に、例えば、本出願人が特開2004−320182の特に背景技術に記載するパルス幅変調回路を使用すると、入力信号の振幅値が大きくなると、PWM信号の周期が大きくなり(周波数が小さくなり)、その結果、MOSFET16のオフ期間が長くなる。その結果、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加してしまい、MOSFET16に過電流が流れていると誤検出されてしまうという問題がある。

【0073】

上記問題を解決するために、トランジスタQ31、Q32が設けられている。トランジスタQ31は、MOSFET15がオン状態のときに、ベースが電源+VCCに接続されオン状態になり、MOSFET15がオフ状態のときに、ベースが電源−VCCに接続されオフ状態になる。トランジスタQ31は、MOSFET15がオン状態のときに、オン状態になることにより、抵抗R1を接地電位に接続する。トランジスタQ31は、MOSFET15がオフ状態のときに、オフ状態になることにより、抵抗R1を接地電位から切り離し、電源+VCCから抵抗3,R2,R1を介して接地電位に電流が流れることを阻止し、ダイオードD1のカソード電圧の減少を阻止する。その結果、MOSFET15のオフ期間が長い場合であっても、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少することが防止される。従って、MOSFET15に過電流が流れていると誤検出されることが防止される。トランジスタQ31は、ベースが抵抗R31を介してMOSFET15のソースに接続され、かつ、抵抗R32を介してトランジスタQ31のエミッタに接続され、コレクタが抵抗R1に接続され、エミッタが接地電位に接続されている。

【0074】

トランジスタQ32は、MOSFET16がオン状態のときに、ベースが電源−VCCに接続されオン状態になり、MOSFET16がオフ状態のときに、ベースが電源+VCCに接続されオフ状態になる。トランジスタQ32は、MOSFET16がオン状態のときに、オン状態になることにより、抵抗R6を接地電位に接続する。トランジスタQ32は、MOSFET16がオフ状態のときに、オフ状態になることにより、抵抗R6を接地電位から切り離し、接地電位から抵抗6,R7,R8を介して電源−VCCに電流が流れることを阻止し、ダイオードD2のアノード電圧の増加を阻止する。その結果、MOSFET16のオフ期間が長い場合であっても、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加することが防止される。従って、MOSFET16に過電流が流れていると誤検出されることが防止される。トランジスタQ32は、ベースが抵抗R33を介してMOSFET16のドレインに接続され、かつ、抵抗R34を介してトランジスタQ32のエミッタに接続され、コレクタが抵抗R6に接続され、エミッタが接地電位に接続されている。

【0075】

ダイオードD31は、ダイオードD1のカソード電位が電源+VCC+0.6V以上になった際に、電源+VCCからMOSFET15、ダイオードD1を介して流れる電流をコンデンサC1に充電するのではなく、ダイオードD31を介して電源+VCCに流すものである。これにより、ダイオードD1のカソード電圧が高くなりすぎて、MOSFET15のドレイン−ソース間電圧の変動をダイオードD1のカソード電圧に反映できなくなることを防止できる。

【0076】

同様に、ダイオードD32は、ダイオードD2のアノード電位が電源−VCC−0.6V以下になった際に、ダイオードD32からダイオードD2、MOSFET15を介して電源−VCCと電流を流すものである。これにより、ダイオードD2のアノード電圧が低くなりすぎて、MOSFET16のドレイン−ソース間電圧の変動をダイオードD2のアノード電圧に反映できなくなることを防止できる。

【0077】

図7は本発明の別の好ましい実施形態による検出回路59を示す概略回路図である。検出回路59は、図6の検出回路49からコンデンサC1、C2を省略したものである。コンデンサC1を省略したのは、MOSFET15がオフ状態の間にはトランジスタQ31がオフ状態になり、ダイオードD1のカソード電圧の減少を防止しているので、コンデンサC1の時定数による作用が不要だからである。しかし、図2における説明のように、コンデンサC1を備える方が、一瞬のみMOSFET15のドレイン−ソース間電圧が大きく変動した際にも、その影響を打ち消して、ダイオードD1のカソード電圧を安定化させることができるという点で好ましい。

【0078】

同様に、コンデンサC2を省略したのは、MOSFET16がオフ状態の間にはトランジスタQ32がオフ状態になり、ダイオードD2のアノード電圧の増加を防止しているので、コンデンサC2の時定数による作用が不要だからである。しかし、図2における説明のように、コンデンサC2を備える方が、一瞬のみMOSFET16のドレイン−ソース間電圧が大きく変動した際にも、その影響を打ち消して、ダイオードD2のカソード電圧を安定化させることができるという点で好ましい。

【0079】

なお、図6又は図7の検出回路においても、図4又は図5のように、正側検出部のみを備える回路構成、又は、負側検出部のみを備える回路構成であってもよい。

【0080】

以上、本発明の好ましい実施形態を説明したが、本発明はこれらの実施形態には限定されない。例えば、パルス幅変調回路の代わりにパルス密度変調回路等のパルス変調回路を使用してもよい。また、スイッチング出力回路のスイッチ素子はMOSFETに限定されない。検出回路19の各スイッチ素子もバイポーラトランジスタに限定されない。検出回路19において、ハイレベル/ローレベルの極性を逆にしてもよく、この場合、各トランジスタの極性を逆にする等周知の技術を用いて適用することができる。また、A点電圧をMOSFET15のドレイン−ソース間電圧が所定電圧以上であることを示す信号として出力し、D点電圧をMOSFET16のドレイン−ソース間電圧が所定電圧以上であることを示す信号として出力する場合には、抵抗R5,R10〜R12、トランジスタQ3,Q4等が不要である。

【産業上の利用可能性】

【0081】

本発明はオーディオ用のスイッチングアンプに好適に適用され得る。

【図面の簡単な説明】

【0082】

【図1】本発明の好ましい実施形態によるスイッチングアンプを示す概略回路図である。

【図2】本発明の実施形態の要部であるMOSFET15,16及び検出回路19を示す概略回路図である。

【図3】図2の回路における検出回路19の各点における電圧波形を示すタイムチャートである。

【図4】本発明の別の実施形態の検出回路29を示す概略回路図である。

【図5】本発明の別の実施形態の検出回路39を示す概略回路図である。

【図6】本発明の別の実施形態の検出回路49を示す概略回路図である。

【図7】本発明の別の実施形態の検出回路59を示す概略回路図である。

【図8】従来の過電流検出回路を示す概略回路図である。

【符号の説明】

【0083】

10 スイッチングアンプ

11 ドライバ

12 スイッチング出力回路

13 LPF

15 MOSFET

16 MOSFET

19 検出回路

19A 正側検出部

19B 負側検出部

19C 出力部

【技術分野】

【0001】

本発明は、出力段のスイッチ素子に流れる過電流を検出するスイッチングアンプに関する。

【背景技術】

【0002】

図8は、従来のスイッチングアンプにおける、正側のMOSFET51、負側のMOSFET52及び過電流検出回路(図8では負側のみを記載)を示す概略回路図である。MOSFET51,52は、図示しないドライバから出力される駆動信号(PWM信号)がハイレベルのときにオン状態となり、駆動信号がローレベルのときにオフ状態になる。MOSFET51がオン状態の時に、出力端子OUTには電源電圧+VCCが出力される。MOSFET52がオン状態の時に、出力端子OUTには電源電圧−VCCが出力される。

【0003】

過電流検出回路は、スイッチ53と比較回路(オペアンプ)54とを備える。スイッチ53は、MOSFET52に供給される駆動信号がハイレベル(すなわち、MOSFET52がオン状態)のときにオン状態になり、ローレベル(すなわち、MOSFET52がオフ状態)のときにオフ状態になる。比較回路54は、正側入力端子に基準電圧Vrefが入力され、負側入力端子には、スイッチ53がオン状態のときに、MSOFET52の両端電圧(ドレイン−ソース間電圧)が入力される。MOSFET52は内部にオン抵抗を有しているので、MOSFET52のドレイン−ソース間に流れる電流にオン抵抗を乗算した値の電圧が、比較回路54の負側入力端子に入力される。MOSFET52のドレイン−ソース間に過電流が流れる場合に、ドレイン−ソース間電圧が高くなり、比較回路54の負側入力端子に入力される電圧が高くなり、比較回路54は、MOSFET52に過電流が流れたことを示す信号を出力する。

【0004】

従来の過電流検出回路においては、比較回路(オペアンプ)54を備えているので、コストが高くなるという問題がある。また、比較回路(オペアンプ)54に電圧を供給する電源回路を別途設ける必要があり、さらにコストが高くなるという問題がある。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−205662号

【発明の概要】

【発明が解決しようとする課題】

【0006】

本発明は上記従来の課題を解決するためになされたものであり、その目的は、オペアンプを設けることなく、スイッチ素子に流れる過電流を検出することができるスイッチングアンプを提供することである。

【課題を解決するための手段】

【0007】

本発明の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、前記第1ダイオードのカソードと前記第1電源との間に接続された第1コンデンサとを備える。

【0008】

本実施形態によると、第1スイッチ素子に流れる過電流を検出することができる。また、第1ダイオードを備えることにより、第1スイッチ素子がオフ状態の時に、第1トランジスタの制御電極から第2スイッチ素子へと電流が流れることが防止され、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。また、第1スイッチ素子がオフ状態の時に、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に流れる電流により、第1ダイオードのカソード電圧が減少するが、第1コンデンサを備えることによって、第1抵抗と第1コンデンサとの時定数により、第1ダイオードのカソード電圧の減少速度が緩やかになり、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0009】

好ましい実施形態においては、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとをさらに備える。

【0010】

本実施形態によると、第2スイッチ素子に流れる過電流を検出することができる。また、第2ダイオードを備えることにより、第2スイッチ素子がオフ状態の時に、第1スイッチ素子から第2トランジスタの制御電極に電流が流れることが防止され、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。また、第2スイッチ素子がオフ状態の時に、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に流れる電流により、第2ダイオードのアノード電圧が増加するが、第2コンデンサを備えることによって、第4抵抗と第2コンデンサとの時定数により、第2ダイオードのアノード電圧の増加速度が緩やかになり、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧以上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0011】

好ましい実施形態においては、前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタをさらに備える。

【0012】

第3トランジスタを備えることによって、第1スイッチ素子がオフ状態の期間が長い場合でも、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に電流が流れることを阻止し、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0013】

好ましい実施形態においては、前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタをさらに備える。

【0014】

第4トランジスタを備えることによって、第2スイッチ素子がオフ状態の期間が長い場合でも、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に電流が流れることを阻止し、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0015】

本発明の別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとを備える。

【0016】

本発明のさらに別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタとを備える。

【0017】

本実施形態によると、第1スイッチ素子に流れる過電流を検出することができる。また、第3トランジスタを備えることによって、第1電源から第3抵抗、第2抵抗、第1抵抗を介して基準電位に電流が流れることを阻止し、第1ダイオードのカソード電圧が第1トランジスタをオン状態にする電圧以下に減少しないので、第1スイッチ素子に過電流が流れていると誤検出することを防止できる。

【0018】

本発明のさらに別の好ましい実施形態によるスイッチングアンプは、制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタとを備える。

【0019】

本実施形態によると、第2スイッチ素子に流れる過電流を検出することができる。第4トランジスタを備えることによって、基準電位から第4抵抗、第5抵抗、第6抵抗を介して第2電源に電流が流れることを阻止し、第2ダイオードのアノード電圧が第2トランジスタをオン状態にする電圧以上に増加しないので、第2スイッチ素子に過電流が流れていると誤検出することを防止できる。

【発明の効果】

【0020】

本発明によると、オペアンプを設けることなく、スイッチ素子に流れる過電流を検出することができる。従って、コストを安価にすることができ、オペアンプ用の電源を別途設ける必要がない。

【発明を実施するための形態】

【0021】

以下、本発明の好ましい実施形態について、図面を参照して具体的に説明するが、本発明はこれらの実施形態には限定されない。図1は、本実施形態のスイッチングアンプ10を示す概略回路図である。スイッチングアンプ10は、パルス幅変調回路20、ドライバ11、スイッチング出力回路12、LPF(Low Pass Filter)13および検出回路19(図2のみに記載)を備える。

【0022】

パルス幅変調回路20は、入力信号(例えば、オーディオ信号)をパルス幅変調して第1のPWM信号OUT1および第2のPWM信号OUT2を生成する。第1のPWM信号OUT1および第2のPWM信号OUT2は、一方がハイレベルの信号である場合に他方がローレベルの信号である。

【0023】

ドライバ11は、第1のPWM信号OUT1および第2のPWM信号OUT2が入力され、電源電圧に基づいて、後述のスイッチ素子を駆動するための駆動信号DRV1およびDRV2を出力する。

【0024】

スイッチング出力回路12は、第1の電源(例えば正の電源+VCC)と第2の電源(例えば負の電源−VCC)との間に接続され、駆動信号に応答して正の電源+VCCまたは負の電源−VCCを出力する。スイッチング出力回路12は、スイッチ素子(本例ではMOSFET15、16)を有する。

【0025】

MOSFET15は、ソースがLPF17(つまり、スイッチングアンプの出力)に接続され、ゲートがドライバ11に接続され、ドレインが電源電圧+VCCの正側に接続されている。MOSFET16は、ドレインがLPF17(つまり、スイッチングアンプの出力)に接続され、ゲートがドライバ11に接続され、ソースが電源電圧−VCCの負側に接続されている。

【0026】

LPF13は、スイッチング出力回路12の出力端とスイッチングアンプ10の出力端との間に接続され、高周波成分を除去して、スピーカー等の負荷に出力する。LPF13は、コイル17およびコンデンサ18を有する。

【0027】

図2は、MOSFET15,16、及び、検出回路19を示す回路図である。検出回路19は、MOSFET15,16に過電流が流れていることを検出し、その旨を示す信号を出力する。過電流が流れていることを示す信号は、例えば、ドライバ11に供給され、ドライバ11からの駆動信号DRV1,DRV2の出力が停止される。または、過電流が流れていることを示す信号は、マイコンに供給され、マイコンからの指示によってパルス幅変調回路20からのPWM信号の出力を停止する。

【0028】

検出回路19は、正側検出部19Aと、負側検出部19Bと、出力部19Cとを含む。

【0029】

正側検出部19Aは、MOSFET15に流れる電流が過電流であることを検出する。MOSFET15はドレイン−ソース間にオン抵抗を有しており、ドレイン−ソース間に流れる電流の電流値にオン抵抗の値を乗算することによって、ドレイン−ソース間電圧が得られる。従って、ドレイン−ソース間に流れる電流が変化することにより、ドレイン−ソース間電圧が変化する。従って、MOSFET15のドレイン−ソース間電圧が所定電圧(第1所定電圧)以上であることを検出することによって、MOSFET15に流れる電流が過電流であることを検出することができる。

【0030】

正側検出部19Aは、ダイオード(第1ダイオード)D1、トランジスタ(第1トランジスタ)Q1、コンデンサ(第1コンデンサ)C1、及び、抵抗R1〜R5を含む。トランジスタQ1は、MOSFET15の両端電圧が所定電圧以上であることを検出する。ダイオードD1は、MOSFET15がオン状態(MOSFET16がオフ状態)のときに、MOSFET15の両端電圧が所定電圧未満であれば、トランジスタQ1のベースに導通開始電圧より大きい電圧を供給することにより、トランジスタQ1をオフ状態にさせ、トランジスタQ1にMOSFET15の両端電圧が所定電圧未満であることを検出させる。一方、MOSFET15の両端電圧が所定電圧以上であれば、トランジスタQ1のベースに導通開始電圧以下の電圧を供給することにより、トランジスタQ1をオン状態にさせ、トラジスタQ1にMOSFET15の両端電圧が所定電圧以上であることを検出させる。

【0031】

ダイオードD1は、アノードがMOSFET15のソースに接続され、カソードがコンデンサC1を介して電源+VCCに接続され、抵抗R1を介して接地電位(基準電位)に接続され、かつ、抵抗R2を介してトランジスタQ1のベースに接続されている。トランジスタQ1は、ベースが抵抗R3を介して電源+VCCに接続され、エミッタが電源+VCCに接続され、コレクタが抵抗R4、R5を介して接地電位に接続されている。

【0032】

ダイオードD1は、MOSFET15がオン状態のときにオン状態になり、MOSFET15がオフ状態のときオフ状態になる。MOSFET15のオン抵抗が53mΩ、過電流が11.3A以上の電流である場合、所定電圧は0.6Vに設定される。従って、MOSFET15のドレイン−ソース間電圧が0.6V以上である場合に、MOSFET15のソース電位が(+VCC−0.6)V以下に、ダイオードD1のカソード電位が(+VCC−1.2)V以下となり、トランジスタQ1に過電流であることを検出させる。一方、MOSFET15のドレイン−ソース間電圧が0.6V未満である場合に、MOSFET15のソース電位が(+VCC−0.6)Vより大きく、ダイオードD1のカソード電位が(+VCC−1.2)Vよりも大きくなり、トランジスタQ1に過電流でないことを検出させる。

【0033】

トランジスタQ1は、ダイオードD1のカソード電位が(+VCC−1.2)Vよりも大きい場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)よりも大きくなり、オフ状態になる。詳細には、ダイオードD1のカソード電圧が、抵抗R2及びR3によって分圧され、トランジスタQ1のベースに供給されるが、当該分圧された電圧がトランジスタQ1の導通開始電圧よりも大きくなっている。

【0034】

一方、トランジスタQ1は、ダイオードD1のカソード電位が(+VCC−1.2)V以下である場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)以下となり、オン状態になる。詳細には、ダイオードD1のカソード電圧が、抵抗R2及びR3によって分圧されて、トランジスタQ1のベースに供給されるが、当該分圧された電圧がトランジスタQ1の導通開始電圧以下になっている。

【0035】

抵抗R2,R3は、上記の通り、ダイオードD1のカソード電圧を分圧してトランジスタQ1のベース電圧を供給する。従って、抵抗R2,R3の各抵抗値は、MOSFET15のドレイン−ソース間電圧が0.6V以上になり、ダイオードD1のカソード電圧が(+VCC−1.2)V以下であるときに、トランジスタQ1のベース−エミッタ間電圧がトランジスタQ1の導通開始電圧(0.6V)以下になるように適切な値に設定されている。

【0036】

ダイオードD1は、MOSFET15がオフ状態(MOSFET16がオン状態)のときに、オフ状態なることにより、正側検出部19A(トランジスタQ1)をMOSFET15,16から電気的に切り離すために設けられる。ダイオードD1がオフになることにより、トランジスタQ1から抵抗R2を介してMOSFET16に電流が流れて、トランジスタQ1がオン状態になることを防止する。

【0037】

コンデンサC1は、MOSFET15がオン状態のときに、電源+VCCからMOSFET15、ダイオードD1を介して電流が流れ、充電されることによって、ダイオードD1のカソード電圧を定める。また、コンデンサC1は、一瞬だけMOSFET15のドレイン−ソース間電圧が非常に大きくなった場合には、ダイオードD1のカソード電圧を一瞬だけ減少させず、ダイオードD1のカソード電圧を安定化させることにより、トランジスタQ1が誤ってオン状態になることを防止する。

【0038】

コンデンサC1は、MOSFET15がオフ状態(MOSFET16がオン状態)のときに、ダイオードD1がオフ状態になるためにトランジスタQ1がオン状態になることを阻止する。つまり、MOSFET15がオフ状態のとき、電源+VCCから抵抗R3、R2、R1を介して接地電位に電流が流れ、その結果、ダイオードD1のカソード電圧が減少する。仮に、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少してしまうと、トランジスタQ1がオン状態になってしまい、MOSFET15に過電流が流れていると誤検出される。しかし、コンデンサC1を設けることによって、コンデンサC1と抵抗R1との時定数によって、ダイオードD1のカソード電圧の減少速度を緩やかにできる。従って、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少しないようにすることができる。

【0039】

負側検出部19Bは、MOSFET16に流れる電流が過電流であることを検出する。MOSFET16はドレイン−ソース間にオン抵抗を有しており、ドレイン−ソース間に流れる電流の電流値にオン抵抗の値を乗算することによって、ドレイン−ソース間電圧が得られる。従って、ドレイン−ソース間に流れる電流が変化することにより、ドレイン−ソース間電圧が変化し、MOSFET16のドレイン−ソース間電圧が所定電圧(第2所定電圧、本例では、第1所定電圧と同じ電圧である)以上であることを検出することによって、MOSFET16に流れる電流が過電流であることを検出することができる。

【0040】

負側検出部19Bは、ダイオード(第2ダイオード)D2、トランジスタ(第2トランジスタ)Q2,トランジスタQ3、コンデンサ(第2コンデンサ)C2、及び、抵抗R6〜R11を含む。トランジスタQ2は、MOSFET16の両端電圧が所定電圧以上であることを検出する。ダイオードD2は、MOSFET16がオン状態(MOSFET15がオフ状態)のときに、MOSFET16の両端電圧が所定電圧未満であれば、トランジスタQ2のベースに導通開始電圧未満の電圧を供給し、トランジスタQ2をオフ状態にさせ、トランジスタQ2にMOSFET16の両端電圧が所定電圧未満であることを検出させる。一方、MOSFET16の両端電圧が所定電圧以上であれば、トランジスタQ2のベースに導通開始電圧以上の電圧を供給し、トランジスタQ2をオン状態にさせ、トラジスタQ2にMOSFET16の両端電圧が所定電圧以上であることを検出させる。

【0041】

ダイオードD2は、カソードがMOSFET16のドレインに接続され、アノードがコンデンサC2を介して電源−VCCに接続され、抵抗R6を介して接地電位に接続され、かつ、抵抗R7を介してトランジスタQ2のベースに接続されている。トランジスタQ2は、ベースが抵抗R8を介して電源−VCCに接続され、エミッタが電源−VCCに接続され、コレクタが抵抗R9,R10を介して電源+VCCに接続されている。トランジスタQ3は、ベースが抵抗R9とR10との接続点に接続され、コレクタが抵抗R11を介してトランジスタQ4のベースに接続され、エミッタが電源+VCCに接続されている。

【0042】

ダイオードD2は、MOSFET16がオン状態のときにオン状態になり、MOSFET16がオフ状態のときにオフ状態になる。MOSFET16のオン抵抗が53mΩ、過電流が11.3A以上の電流である場合、所定電圧は0.6Vに設定される。従って、MOSFET16のドレイン−ソース間電圧が0.6V以上である場合に、MOSFET16のドレイン電位が(−VCC+0.6)V以上に、ダイオードD2のアノード電位が(−VCC+1.2)V以上になり、トランジスタQ1に過電流であることを検出させる。一方、MOSFET16のドレイン−ソース間電圧が0.6V未満である場合に、MOSFET16のドレイン電位が(−VCC+0.6)V未満に、ダイオードD2のアノード電位が(−VCC+1.2)V未満になり、トランジスタQ2に過電流電でないことを検出させる。

【0043】

トランジスタQ2は、ダイオードD2のアノード電位が(−VCC+0.6)Vよりも小さい場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)未満となり、オフ状態になる。つまり、ダイオードD2のアノード電圧が、抵抗R7及びR8によって分圧されて、トランジスタQ2のベースに供給されるが、当該分圧された電圧がトランジスタQ2の導通開始電圧未満になっている。

【0044】

一方、トランジスタQ2は、ダイオードD2のアノード電位が(−VCC+0.6)V以上の場合に、ベース−エミッタ間電圧が導通開始電圧(0.6V)以上となり、オン状態になる。つまり、ダイオードD2のアノード電圧が、抵抗R7及びR8によって分圧されて、トランジスタQ2のベースに供給されるが、当該分圧された電圧が、トランジスタQ2の導通開始電圧以上になっている。

【0045】

抵抗R7,R8は、上記の通り、ダイオードD2のアノード電圧を分圧してトランジスタQ2のベース電圧を供給する。従って、抵抗R7,R8の各抵抗値は、MOSFET16のドレイン−ソース間電圧が0.6V以上になり、ダイオードD2のアノード電圧が(−VCC+1.2)V以上であるときに、トランジスタQ2のベース−エミッタ間電圧がトランジスタQ2の導通開始電圧(0.6V)以上になるように適切な値に設定されている。

【0046】

ダイオードD2は、MOSFET16がオフ状態(MOSFET15がオン状態)のときに、オフ状態なることにより、負側検出部19B(トランジスタQ2)をMOSFET15,16から電気的に切り離す。ダイオードD2がオフ状態になることにより、MOSFET15から抵抗R7を介してトランジスタQ2のベースに電流が流れて、トランジスタQ2がオン状態になることを防止することができる。

【0047】

コンデンサC2は、MOSFET16がオン状態の時に、ダイオードD2との接続点がダイオードD2、MOSFET16を介して電源−VCCに接続された状態になり、当該点の電圧が減少することにより、ダイオードD2のアノード電圧を定める。また、コンデンサC2は、一瞬だけMOSFET16のドレイン−ソース間電圧が非常に大きくなった場合には、ダイオードD2のアノード電圧を増加させず、当該電圧を安定化させることによって、トランジスタQ2を一瞬だけオン状態にすることを防止する。

【0048】

コンデンサC2は、MOSFET16がオフ状態(MOSFET15がオン状態)のときに、ダイオードD2がオフ状態になるためにトランジスタQ2がオン状態になることを阻止する。つまり、MOSFET16がオフ状態のとき、接地電位から抵抗R6、R7、R8を介して電源−VCCに電流が流れ、その結果、ダイオードD2のアノード電圧が増加する。仮に、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加してしまうと、トランジスタQ2がオン状態になってしまい、MOSFET16に過電流が流れていると誤検出される。しかし、コンデンサC2を設けることによって、コンデンサC2と抵抗R6の時定数によって、ダイオードD2のアノード電圧の増加速度を緩やかにできる。従って、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加しないようにすることができる。

【0049】

トランジスタQ3は、トランジスタQ2の出力信号を反転させる。トランジスタQ3は、トランジスタQ2がオフ状態のときに、ベースが電源+VCCに接続された状態になるのでオフ状態になる。一方、トランジスタQ3は、トランジスタQ2がオン状態のときに、ベースが電源−VCCに接続された状態になるのでオン状態になる。

【0050】

出力部19Cは、MOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号を出力する。出力部19Cは、トランジスタQ4及び抵抗R12を含む。トランジスタQ4は、ベースが抵抗R4とR5との接続点に接続され、抵抗R11を介してトランジスタQ3のコレクタに接続され、エミッタが接地電位に接続され、コレクタが抵抗R12を介して+5V電源に接続され、MOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号を出力する出力端になっている。

【0051】

トランジスタQ4は、トランジスタQ1がオン状態であるとき、ベースが電源電圧+VCCに接続された状態になるので、オン状態になる。トランジスタQ4は、トランジスタQ3がオン状態であるとき、ベースが電源電圧+VCCに接続された状態になるので、オン状態になる。トランジスタQ4がオン状態になると、トランジスタQ4のコレクタは、接地電位に接続された状態になり、ローレベルになり、このローレベルの信号がMOSFET15又は16のドレイン−ソース間電圧が所定電圧以上であることを示す信号となる。トランジスタQ4は、トランジスタQ1,Q3がオフ状態である場合、ベースが接地電位に接続された状態になり、オフ状態になる。トランジスタQ4がオフ状態になると、トランジスタQ4のコレクタは、+5V電源に接続された状態になり、ハイレベルになり、このハイレベルの信号がMOSFET15及び16のドレイン−ソース間電圧が所定電圧未満であることを示す信号となる。

【0052】

以上の構成を有する検出回路19についてその動作を説明する。図3は、図2の検出回路19の各点における電圧波形を示している。なお、上記所定電圧を0.6Vとして説明する。

【0053】

[MOSFET15がオン状態、MOSFET16がオフ状態、MOSFET15に過電流が流れていない場合]

MOSFET15のドレイン−ソース間電圧が所定電圧0.6V未満であるので、MOSFET15のソース電位は(+VCC−0.6)Vより大きくなっている。ダイオードD1は、MOSFET15がオン状態であるので、オン状態になっている。ダイオードD1のカソード電位が(+VCC−1.2)Vより大きく、トランジスタQ1のベース電位も高くなり、トランジスタQ1のベース−エミッタ間電圧が導通開始電圧より大きいので、トランジスタQ1はオフ状態である。従って、トランジスタQ1のコレクタは接地電位に接続された状態になり、コレクタ電圧(A点電圧)はローレベルになっている。

【0054】

ダイオードD2のカソード電位はMOSFET15のソース電位((+VCC−0.6V)以上)になっているので、アノード電位よりも大きく、ダイオードD2はオフ状態になっている。従って、接地電位から抵抗R6を介して流れる電流は、MOSFET16には流れず、抵抗R7、R8を介して電源−VCCへと流れる。その結果、抵抗R6とコンデンサC2との時定数に応じて、ダイオードD2のアノード電圧が緩やかな速度で増加する。ダイオードD2のアノード電圧が、トランジスタQ2をオン状態にする電圧以上に増加する前に、MOSFET16がオン状態になるので、コンデンサC2のダイオードD2のアノードとの接続点が電源−VCCに接続された状態になり、当該点の電圧が低下し、ダイオードD2のアノード電圧が減少する。従って、MOSFET16がオフ状態の間には、ダイオードD2のアノード電圧はトランジスタQ2をオン状態にする電圧以上に増加しないので、トランジスタQ2はオフ状態を継続する。

【0055】

トランジスタQ2がオフ状態であるので、トランジスタQ3は、ベースが電源電圧+VCCに接続された状態であり、オフ状態になっている。トランジスタQ3のコレクタ電圧(C点電圧)はローレベルになっている。

【0056】

従って、トランジスタQ4は、トランジスタQ1,Q3が共にオフ状態であるので、ベースが接地電位に接続された状態になり、オフ状態になっている。トランジスタQ4のコレクタ電圧(B点電圧)は、ハイレベルになっており、このハイレベルの信号がMOSFET15に過電流が流れていないことを示す信号として出力される。

【0057】

[MOSFET15がオン状態、MOSFET16がオフ状態、MOSFET15に過電流が流れている場合]

MOSFET15のドレイン−ソース間電圧が所定電圧0.6V以上であるので、MOSFET15のソース電位は(+VCC−0.6)V以下になっている。ダイオードD1は、MOSFET15がオン状態であるので、オン状態になっている。ダイオードD1のカソード電圧が(+VCC−1.2)V以下になり、トランジスタQ1のベース電圧が低くなるので、トランジスタQ1のベース−エミッタ間電圧が導通開始電圧以下になり、トランジスタQ1がオン状態になる。トランジスタQ1のコレクタは電源電圧+VCCに接続された状態になり、コレクタ電圧(A点電圧)はハイレベルになっている(時刻t1〜t2)。

【0058】

その結果、トランジスタQ4のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ4がオン状態になる。トランジスタQ4は、コレクタが接地電位に接続された状態になり、コレクタ電圧(B点電圧)がローレベルになり(時刻t1〜t2)、このローレベルの信号がMOSFET15に過電流が流れていることを示す信号として出力される。

【0059】

[MOSFET16がオン状態、MOSFET15がオフ状態、MOSFET16に過電流が流れていない場合]

MOSFET16のドレイン−ソース間電圧が所定電圧0.6V未満であるので、MOSFET16のドレイン電位は(−VCC+0.6)V未満になっている。ダイオードD2は、MOSFET16がオン状態であるので、オン状態になっている。ダイオードD2のアノード電位が(−VCC+1.2)V未満であり、トランジスタQ2のベース電位も低くなり、トランジスタQ2のベース−エミッタ間電圧が導通開始電圧より小さいので、トランジスタQ2はオフ状態である。従って、トランジスタQ2のコレクタは電源電圧+VCCに接続された状態になり、コレクタ電圧(D点電圧)はハイレベルになっている。

【0060】

トランジスタQ3は、ベースが電源電圧+VCCに接続された状態であり、オフ状態になっている。トランジスタQ3のコレクタ電圧(C点電圧)は、ローレベルになっている。

【0061】

ダイオードD1のアノード電位はMOSFET16のドレイン電位((−VCC+0.6V)未満)になっているので、カソード電位よりも小さく、ダイオードD1はオフ状態になっている。従って、抵抗R1を介して接地電位に流れる電流は、MOSFET15からは流れず、電源+VCCから抵抗R3、R2を介して流れる。その結果、抵抗R1とコンデンサC1との時定数に応じて、ダイオードD1のカソード電圧が緩やかな速度で減少する。ダイオードD1のカソード電圧が、トランジスタQ1をオン状態にする電圧以下に減少する前に、MOSFET15がオン状態になるので、コンデンサC1が電源+VCCからMOSFET15、ダイオードD1を介して流れる電流によって再度充電され、ダイオードD1のカソード電圧が増加する。従って、MOSFET15がオフ状態の間には、ダイオードD1のカソード電圧はトランジスタQ1をオン状態にする電圧以下に減少しないので、トランジスタQ1はオフ状態を継続する。

【0062】

トランジスタQ1のコレクタは接地電位に接続された状態であり、トランジスタQ1のコレクタ電圧(A点電圧)は、ローレベルになっている。

【0063】

従って、トランジスタQ4は、トランジスタQ1,Q3が共にオフ状態であるので、ベースが接地電位に接続された状態になり、オフ状態になっている。トランジスタQ4のコレクタ電圧(B点電圧)は、ハイレベルになっており、このハイレベルの信号がMOSFET16に過電流が流れていないことを示す信号として出力される。

【0064】

[MOSFET16がオン状態、MOSFET15がオフ状態、MOSFET16に過電流が流れている場合]

MOSFET16のドレイン−ソース間電圧が所定電圧0.6V以上であるので、MOSFET16のドレイン電位は(−VCC+0.6)V以上になっている。ダイオードD2は、MOSFET16がオン状態であるので、オン状態になっている。ダイオードD2のアノード電位が(−VCC+1.2V)以上になり、トランジスタQ2のベース電位が高くなるので、トランジスタQ2のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ2がオン状態になる。トランジスタQ2のコレクタは電源電圧−VCCに接続された状態になり、コレクタ電圧(D点電圧)はローレベルになっている(時刻t3〜t4)。

【0065】

トランジスタQ2がオン状態になると、トランジスタQ3のベースが接地電位に接続された状態になり、オン状態になる。トランジスタQ3のコレクタは、電源電圧+VCCに接続された状態になり、コレクタ電圧(C点電圧)がハイレベルになる(時刻t3〜t4)。

【0066】

その結果、トランジスタQ4のベース−エミッタ間電圧が導通開始電圧以上になり、トランジスタQ4がオン状態になる。トランジスタQ4は、コレクタが接地電位に接続された状態になり、コレクタ電圧(B点電圧)がローレベルになり(時刻t3〜t4)、このローレベルの信号がMOSFET16に過電流が流れていることを示す信号として出力される。

【0067】

以上のように、本実施形態によると、ダイオードD1,D2、トランジスタQ1,Q2、コンデンサC1,C2等を備えることによって、MOSFET15,16の過電流を検出することができる。

【0068】

また、検出回路19は、MOSFET15,16の温度が所定温度以上であることを検出し、その旨を示す検出結果を出力してもよい。MOSFET15,16のオン抵抗の抵抗値は、温度によって変化し、温度が高くなるにつれて略一次関数的に抵抗値が高くなる。従って、温度が変化することにより、MOSFETのドレイン−ソース間電圧が変化する。従って、上記の実施例のように、MOSFET15,16のドレイン−ソース間電圧を検出することによって、MOSFET15,16に流れる過電流に加えて、MOSFET15,16の温度が所定温度以上であることを検出することができる。

【0069】

図4は本発明の別の好ましい実施形態による検出回路29を示す概略回路図である。検出回路29は、図2の検出回路19の各構成のうち、正側検出部19Aのみを有し、MOSFET15に流れる過電流のみを検出できる。図5は本発明の別の好ましい実施形態による検出回路39を示す概略回路図である。検出回路39は、図2の検出回路19の各構成のうち、負側検出部19Bのみを有し、MOSFET16に流れる過電流のみを検出できる。

【0070】

図6は本発明の別の好ましい実施形態による検出回路49を示す回路図である。検出回路49は、図2の検出回路19の構成に加えて、トランジスタQ31、Q32、抵抗R31〜R34、ダイオードD31,D32をさらに有する。

【0071】

図2の検出回路19では、MOSFET15がオフ状態の間に、コンデンサC1と抵抗R1との時定数により、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少することを防止している。しかし、図1のパルス幅変調回路20に、例えば、本出願人が特開2004−320182の特に背景技術に記載するパルス幅変調回路を使用すると、入力信号の振幅値が大きくなると、PWM信号の周期が大きくなり(周波数が小さくなり)、その結果、MOSFET15のオフ期間が長くなる。その結果、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少してしまい、MOSFET15に過電流が流れていると誤検出されてしまうという問題がある。

【0072】

同様に、図2の検出回路19では、MOSFET16がオフ状態の間に、コンデンサC2と抵抗R6との時定数により、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加することを防止している。しかし、図1のパルス幅変調回路20に、例えば、本出願人が特開2004−320182の特に背景技術に記載するパルス幅変調回路を使用すると、入力信号の振幅値が大きくなると、PWM信号の周期が大きくなり(周波数が小さくなり)、その結果、MOSFET16のオフ期間が長くなる。その結果、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加してしまい、MOSFET16に過電流が流れていると誤検出されてしまうという問題がある。

【0073】

上記問題を解決するために、トランジスタQ31、Q32が設けられている。トランジスタQ31は、MOSFET15がオン状態のときに、ベースが電源+VCCに接続されオン状態になり、MOSFET15がオフ状態のときに、ベースが電源−VCCに接続されオフ状態になる。トランジスタQ31は、MOSFET15がオン状態のときに、オン状態になることにより、抵抗R1を接地電位に接続する。トランジスタQ31は、MOSFET15がオフ状態のときに、オフ状態になることにより、抵抗R1を接地電位から切り離し、電源+VCCから抵抗3,R2,R1を介して接地電位に電流が流れることを阻止し、ダイオードD1のカソード電圧の減少を阻止する。その結果、MOSFET15のオフ期間が長い場合であっても、MOSFET15がオフ状態の間に、ダイオードD1のカソード電圧がトランジスタQ1をオン状態にする電圧以下に減少することが防止される。従って、MOSFET15に過電流が流れていると誤検出されることが防止される。トランジスタQ31は、ベースが抵抗R31を介してMOSFET15のソースに接続され、かつ、抵抗R32を介してトランジスタQ31のエミッタに接続され、コレクタが抵抗R1に接続され、エミッタが接地電位に接続されている。

【0074】

トランジスタQ32は、MOSFET16がオン状態のときに、ベースが電源−VCCに接続されオン状態になり、MOSFET16がオフ状態のときに、ベースが電源+VCCに接続されオフ状態になる。トランジスタQ32は、MOSFET16がオン状態のときに、オン状態になることにより、抵抗R6を接地電位に接続する。トランジスタQ32は、MOSFET16がオフ状態のときに、オフ状態になることにより、抵抗R6を接地電位から切り離し、接地電位から抵抗6,R7,R8を介して電源−VCCに電流が流れることを阻止し、ダイオードD2のアノード電圧の増加を阻止する。その結果、MOSFET16のオフ期間が長い場合であっても、MOSFET16がオフ状態の間に、ダイオードD2のアノード電圧がトランジスタQ2をオン状態にする電圧以上に増加することが防止される。従って、MOSFET16に過電流が流れていると誤検出されることが防止される。トランジスタQ32は、ベースが抵抗R33を介してMOSFET16のドレインに接続され、かつ、抵抗R34を介してトランジスタQ32のエミッタに接続され、コレクタが抵抗R6に接続され、エミッタが接地電位に接続されている。

【0075】

ダイオードD31は、ダイオードD1のカソード電位が電源+VCC+0.6V以上になった際に、電源+VCCからMOSFET15、ダイオードD1を介して流れる電流をコンデンサC1に充電するのではなく、ダイオードD31を介して電源+VCCに流すものである。これにより、ダイオードD1のカソード電圧が高くなりすぎて、MOSFET15のドレイン−ソース間電圧の変動をダイオードD1のカソード電圧に反映できなくなることを防止できる。

【0076】

同様に、ダイオードD32は、ダイオードD2のアノード電位が電源−VCC−0.6V以下になった際に、ダイオードD32からダイオードD2、MOSFET15を介して電源−VCCと電流を流すものである。これにより、ダイオードD2のアノード電圧が低くなりすぎて、MOSFET16のドレイン−ソース間電圧の変動をダイオードD2のアノード電圧に反映できなくなることを防止できる。

【0077】

図7は本発明の別の好ましい実施形態による検出回路59を示す概略回路図である。検出回路59は、図6の検出回路49からコンデンサC1、C2を省略したものである。コンデンサC1を省略したのは、MOSFET15がオフ状態の間にはトランジスタQ31がオフ状態になり、ダイオードD1のカソード電圧の減少を防止しているので、コンデンサC1の時定数による作用が不要だからである。しかし、図2における説明のように、コンデンサC1を備える方が、一瞬のみMOSFET15のドレイン−ソース間電圧が大きく変動した際にも、その影響を打ち消して、ダイオードD1のカソード電圧を安定化させることができるという点で好ましい。

【0078】

同様に、コンデンサC2を省略したのは、MOSFET16がオフ状態の間にはトランジスタQ32がオフ状態になり、ダイオードD2のアノード電圧の増加を防止しているので、コンデンサC2の時定数による作用が不要だからである。しかし、図2における説明のように、コンデンサC2を備える方が、一瞬のみMOSFET16のドレイン−ソース間電圧が大きく変動した際にも、その影響を打ち消して、ダイオードD2のカソード電圧を安定化させることができるという点で好ましい。

【0079】

なお、図6又は図7の検出回路においても、図4又は図5のように、正側検出部のみを備える回路構成、又は、負側検出部のみを備える回路構成であってもよい。

【0080】

以上、本発明の好ましい実施形態を説明したが、本発明はこれらの実施形態には限定されない。例えば、パルス幅変調回路の代わりにパルス密度変調回路等のパルス変調回路を使用してもよい。また、スイッチング出力回路のスイッチ素子はMOSFETに限定されない。検出回路19の各スイッチ素子もバイポーラトランジスタに限定されない。検出回路19において、ハイレベル/ローレベルの極性を逆にしてもよく、この場合、各トランジスタの極性を逆にする等周知の技術を用いて適用することができる。また、A点電圧をMOSFET15のドレイン−ソース間電圧が所定電圧以上であることを示す信号として出力し、D点電圧をMOSFET16のドレイン−ソース間電圧が所定電圧以上であることを示す信号として出力する場合には、抵抗R5,R10〜R12、トランジスタQ3,Q4等が不要である。

【産業上の利用可能性】

【0081】

本発明はオーディオ用のスイッチングアンプに好適に適用され得る。

【図面の簡単な説明】

【0082】

【図1】本発明の好ましい実施形態によるスイッチングアンプを示す概略回路図である。

【図2】本発明の実施形態の要部であるMOSFET15,16及び検出回路19を示す概略回路図である。

【図3】図2の回路における検出回路19の各点における電圧波形を示すタイムチャートである。

【図4】本発明の別の実施形態の検出回路29を示す概略回路図である。

【図5】本発明の別の実施形態の検出回路39を示す概略回路図である。

【図6】本発明の別の実施形態の検出回路49を示す概略回路図である。

【図7】本発明の別の実施形態の検出回路59を示す概略回路図である。

【図8】従来の過電流検出回路を示す概略回路図である。

【符号の説明】

【0083】

10 スイッチングアンプ

11 ドライバ

12 スイッチング出力回路

13 LPF

15 MOSFET

16 MOSFET

19 検出回路

19A 正側検出部

19B 負側検出部

19C 出力部

【特許請求の範囲】

【請求項1】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、

前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、

前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、

前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、

前記第1ダイオードのカソードと前記第1電源との間に接続された第1コンデンサとを備える、スイッチングアンプ。

【請求項2】

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとをさらに備える、スイッチングアンプ。

【請求項3】

前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタをさらに備える、請求項1または2に記載のスイッチングアンプ。

【請求項4】

前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタをさらに備える、請求項2に記載のスイッチングアンプ。

【請求項5】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとを備える、スイッチングアンプ。

【請求項6】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、

前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、

前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、

前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、

前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタとを備える、スイッチングアンプ。

【請求項7】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタとを備える、スイッチングアンプ。

【請求項1】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、

前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、

前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、

前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、

前記第1ダイオードのカソードと前記第1電源との間に接続された第1コンデンサとを備える、スイッチングアンプ。

【請求項2】

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとをさらに備える、スイッチングアンプ。

【請求項3】

前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタをさらに備える、請求項1または2に記載のスイッチングアンプ。

【請求項4】

前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタをさらに備える、請求項2に記載のスイッチングアンプ。

【請求項5】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第2ダイオードのアノードと前記第2電源との間に接続された第2コンデンサとを備える、スイッチングアンプ。

【請求項6】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

アノードが前記第1スイッチ素子の第2端子に接続された第1ダイオードと、

前記第1ダイオードのカソードと基準電位との間に接続された第1抵抗と、

前記第1ダイオードのカソードの電圧を分圧して、第1トランジスタの制御電極に供給する第2抵抗および第3抵抗と、

前記第2抵抗および第3抵抗によって分圧された電圧が制御電極に供給されることにより、前記第1スイッチ素子の両端電圧が第1所定電圧以上であるか否かを検出する第1トランジスタと、

前記第1抵抗と前記基準電位との間に接続され、前記第1スイッチ素子がオン状態の時にオン状態とされ、前記第1抵抗を前記基準電位に接続し、前記第1スイッチ素子がオフ状態の時にオフ状態とされ、前記第1抵抗を前記基準電位から切り離す第3トランジスタとを備える、スイッチングアンプ。

【請求項7】

制御電極に供給される第1駆動信号によってオン状態又はオフ状態に制御され、第1端子が第1電源に接続され、第2端子がスイッチングアンプの出力に接続された第1スイッチ素子と、

制御電極に供給される第2駆動信号によってオン状態又はオフ状態に制御され、第1端子が前記第1電源よりも低電圧である第2電源に接続され、第2端子が前記出力に接続された第2スイッチ素子と、

カソードが前記第2スイッチ素子の第2端子に接続された第2ダイオードと、

前記第2ダイオードのアノードと前記基準電位との間に接続された第4抵抗と、

前記第2ダイオードのアノードの電圧を分圧して、第2トランジスタの制御電極に供給する第5抵抗および第6抵抗と、

前記第5抵抗および第6抵抗によって分圧された電圧が制御電極に供給されることにより、前記第2スイッチ素子の両端電圧が第2所定電圧以上であるか否かを検出する第2トランジスタと、

前記第4抵抗と前記基準電位との間に接続され、前記第2スイッチ素子がオン状態の時にオン状態とされ、前記第4抵抗を前記基準電位に接続し、前記第2スイッチ素子がオフ状態の時にオフ状態とされ、前記第4抵抗を前記基準電位から切り離す第4トランジスタとを備える、スイッチングアンプ。

【図1】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図3】

【図2】

【図4】

【図5】

【図6】

【図7】

【図8】

【図3】

【公開番号】特開2010−233196(P2010−233196A)

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願番号】特願2009−130123(P2009−130123)

【出願日】平成21年5月29日(2009.5.29)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

【公開日】平成22年10月14日(2010.10.14)

【国際特許分類】

【出願日】平成21年5月29日(2009.5.29)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

[ Back to top ]