スイッチング電源装置

【課題】同期整流回路を有し、出力短絡時等に負荷や内部の回路素子を確実に保護するシングルエンディッド・フォワード型のスイッチング電源装置を提供する。

【解決手段】MOS型FETの主スイッチング素子14及び転流側スイッチング素子24を備える。主スイッチング素子14のオン時間が短くなると、転流側スイッチング素子24をオフ状態に保持する同期整流駆動回路32を備える。出力電圧Voの誤差信号ΔVoに基づいてパルス幅変調すると共に、電流検出回路38のスイッチング電流信号が第1基準電圧Vr1に達すると駆動パルスV16をローレベルにするPWM制御回路16を備える。主スイッチング素子14のゲート・ソース端子間に可変抵抗素子46を備える。スイッチング電流信号が第2基準電圧Vr2に達すると、可変抵抗素子46の抵抗値を低下させ、主スイッチング素子14のゲート・ソース端子間電圧Vg14を抑える可変制御回路48を備える。

【解決手段】MOS型FETの主スイッチング素子14及び転流側スイッチング素子24を備える。主スイッチング素子14のオン時間が短くなると、転流側スイッチング素子24をオフ状態に保持する同期整流駆動回路32を備える。出力電圧Voの誤差信号ΔVoに基づいてパルス幅変調すると共に、電流検出回路38のスイッチング電流信号が第1基準電圧Vr1に達すると駆動パルスV16をローレベルにするPWM制御回路16を備える。主スイッチング素子14のゲート・ソース端子間に可変抵抗素子46を備える。スイッチング電流信号が第2基準電圧Vr2に達すると、可変抵抗素子46の抵抗値を低下させ、主スイッチング素子14のゲート・ソース端子間電圧Vg14を抑える可変制御回路48を備える。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、過電流保護機能を有し、同期整流回路を備えたシングルエンディッド・フォワード型のスイッチング電源装置に関する。

【背景技術】

【0002】

一般的なスイッチング電源装置は、通電中に故障した負荷を保護する(例えば、焼損事故等の防止)ため、負荷に向けて出力可能な出力電流を一定以下に制限する過電流保護機能を備えている。従来から、過電流保護には様々な方式があり、中でも、主スイッチング素子に流れるパルス状のスイッチング電流をスイッチング周期ごとに観測しそのピーク値を制限するパルス・バイ・パルス方式が使用される場合が多い。

【0003】

パルス・バイ・パルス方式の過電流保護は、スイッチング電流のピーク値を1パルスごとに制限するため、スイッチング電源装置の内部素子(例えば、主スイッチング素子、整流素子などの半導体素子)に過大な電気的ストレスが加わるのを防ぐことができる。従って、出力電流が大きくなったときだけでなく、例えばスイッチング電源装置に入力電圧を投入し、出力の平滑コンデンサを急速充電して出力電圧を上昇させる動作においても内部素子が保護されるという利点がある。また、シングルエンディッド・フォワード型のスイッチング電源装置の場合、主スイッチング素子に流れるスイッチング電流のピーク値が出力電流と略比例の関係にあることから、出力電流の上限値を精度よく規定することができるという利点もある。

【0004】

例えば、特許文献1に開示されているスイッチング電源装置は、パルス・バイ・パルス方式の過電流保護回路を備えたシングルエンディッド・フォワード型のスイッチング電源装置である。このスイッチング電源装置は、主スイッチング素子に流れるスイッチング電流を電圧に変換する電流検出抵抗と、その検出電圧に重畳したスパイク成分を除去する積分回路と、積分回路の出力が基準値に達すると主スイッチング素子のゲート・ソース端子間に設けたトランジスタがオンして主スイッチング素子を強制的にオフさせ、主スイッチング素子のオン時間を短くするPWM回路とを備えている。さらに、積分回路の出力が高くなるとスイッチング周波数を低下させる発振周波数制御回路が設けられている。このスイッチング電源装置は、積分回路やPWM回路の動作遅延によりスイッチング電流のピーク値を基準値以下に制限することができず過電流垂下特性が裾を引くという問題を、出力電流が一定以上に大きくなるとスイッチング周波数を低下させることによって解消するものである。

【0005】

近年、トランスの2次側の整流ダイオードの損失を低減するため、導通抵抗の小さいMOS型FETを使用して同期整流を行うスイッチング電源装置が提案されている。例えば、特許文献2に開示されているように、シングルエンディッド・フォワード型のコンバータ回路を有し、N−ch(チャネル)のMOS型FETである整流側及び転流側スイッチング素子と、それらを駆動する所定の駆動回路を備えたスイッチング電源装置がある。駆動回路は、主トランスの3次巻線に発生する電圧を利用した巻線駆動方式であり、転流側スイッチング素子をオフさせるタイミングについては信号伝達用トランスからのタイミング信号によって決定する。このスイッチング電源装置は、整流側及び転流側スイッチング素子の駆動回路がシンプルな構成でありながら、主スイッチング素子、整流側及び転流側スイッチング素子のオン・オフのタイミング制御を適正化することができる。なお、特許文献2では、過電流保護回路について説明がされていない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭63−35171号公報

【特許文献2】特開2005−12919号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献1のスイッチング電源装置の場合、スイッチング電流が急増して発振周波数制御回路が動作を開始しスイッチング周波数が実際に低下するまで、ある程度の時間がかかるので、その期間に流れるスイッチング電流のピーク値が大きくなってしまうという問題がある。例えば、正常運転しているときに負荷である装置が故障し、スイッチング電源装置の出力端が急峻に短絡されると、発振周波数制御回路が発振回路の時定数を可変する動作を行うが、スイッチング周波数の変化は緩慢なため、少なくともスイッチング電流の1〜3パルス程度はピーク値が大きくなり、それに起因して装置内部の回路素子に大きな電気的ストレスが加わってしまう。特に、主スイッチング素子等の半導体は、電流ストレス、電圧ストレスまたは損失による熱ストレスに弱く、短時間でも過大なストレスが加わると破壊するおそれがある。従って、このスイッチング電源装置の過電流保護回路は、スイッチング電源装置内部の回路素子を確実に保護することができないものであった。また、主スイッチング素子等の半導体の安全性を確保するため、大型で電流定格や電圧定格の高い高価な素子を選択しなければならなかった。

【0008】

特許文献2のスイッチング電源装置に特許文献1の過電流保護回路を付加したとしても、上記と同様の問題が生じ得る。

【0009】

この発明は、上記背景技術に鑑みて成されたものであり、低損失の同期整流回路を有し、出力短絡時などに負荷や内部の回路素子を確実に保護することができるシングルエンディッド・フォワード型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

この発明は、入力電源と直列に接続されたN−chのMOS型FETであって、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、前記交流電圧が印加される1次巻線及びそれに磁気結合した2次巻線を有する主トランスと、一端が前記2次巻線の一端に接続され、前記主スイッチング素子がオンの期間中に前記2次巻線に発生した電圧を整流する整流側スイッチング素子と、前記2次巻線の他の一端と前記整流側スイッチング素子の他の一端にドレイン端子とソース端子が各々接続され、前記主スイッチング素子がオフの期間中にオンして前記ソース端子から前記ドレイン端子の向きに電流を流すN−chのMOS型FETである転流側スイッチング素子と、前記転流側スイッチング素子の内部のドレイン・ソース端子間に形成された寄生ダイオードと、前記転流側スイッチング素子をオン・オフ駆動する回路であって、前記主スイッチング素子のオン時間が一定以下に短くなると、前記転流側スイッチング素子をオフ状態に保持する同期整流駆動回路と、平滑チョーク及び平滑コンデンサで成るローパスフィルタであって、前記転流側スイッチング素子のドレイン・ソース端子間にその入力側が接続され、前記平滑コンデンサ両端に直流の出力電圧を生成して負荷に電力を供給する平滑回路と、前記主スイッチング素子に流れるスイッチング電流を検出する電流検出回路と、前記出力電圧の誤差信号に基づいてパルス幅変調した矩形の駆動パルスを出力して前記主スイッチング素子のオン・オフを制御すると共に、前記電流検出回路の出力信号を受け前記スイッチング電流のピーク値が第1基準値に達すると前記主スイッチング素子をオフさせるため前記駆動パルスをローレベルにするパルス・バイ・パルス式の過電流保護動作を行うPWM制御回路と、を備えたシングルエンディッド・フォワード型のスイッチング電源装置である。

【0011】

さらに、前記主スイッチング素子のゲート・ソース端子間に接続された可変抵抗素子と、前記電流検出回路の出力信号に基づいて前記可変抵抗素子の抵抗値を変化させる可変制御回路とを備え、前記可変制御回路は、前記電流検出回路の出力信号を受けスイッチング周期ごとに前記スイッチング電流のピーク値と前記第1基準値よりも高い第2基準値とを比較し、前記スイッチング電流が前記第2基準値に達すると前記可変抵抗素子の抵抗値を低下させ、前記主スイッチング素子のゲート・ソース端子間電圧を上げないように制御することによって前記スイッチング電流のピーク値の上昇を抑制し、前記転流側スイッチング素子の寄生ダイオードのリカバリ電流のピーク値を制限するスイッチング電源装置である。

【0012】

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記可変抵抗素子の抵抗値を低下させる動作を継続する。

【0013】

前記抵抗値可変素子は、コレクタ端子が前記主スイッチング素子のゲート端子側に接続され、エミッタ端子が前記主スイッチング素子のソース端子に接続されたNPNトランジスタであり、前記可変制御回路は、前記NPNトランジスタのベース電流を制御することによって前記NPNトランジスタのコレクタ・エミッタ端子間の導通抵抗を変化させるものである。

【0014】

また、前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、カソード端子が前記電流検出回路の出力端に接続され、アノード端子が前記NPNトランジスタのベース端子に接続されたツェナーダイオードとで構成されている。

【0015】

また、前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、両端が前記電流検出回路の出力端と前記NPNトランジスタのベース端子の間に接続された第2抵抗とで構成されている。

【0016】

また、前記第1抵抗と並列に電圧保持コンデンサが接続され、前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記NPNトランジスタのベース電流を前記電圧保持コンデンサから供給することによって、前記可変抵抗素子の抵抗値を低下させる動作を継続する。

【発明の効果】

【0017】

この発明のスイッチング電源装置によれば、負荷が故障して出力が短絡し、転流側スイッチング素子の同期整流動作が停止し、転流側スイッチング素子の寄生ダイオードにリカバリ電流が流れた時、スイッチング電流及びリカバリ電流を小さく抑え、転流側スイッチング素子のドレイン・ソース端子間に過大な電圧が発生するのを防止することができる。従って、転流側スイッチング素子として導通抵抗の小さい低耐圧のMOS型FETを選択することができ、低損失化を図ることができる。

【0018】

また、可変抵抗素子及び可変制御回路は、例えばNPNトランジスタ、ツェナーダイオード、第1及び第2抵抗、保持コンデンサなど組み合わせてシンプルに構成することができ、さらに転流側スイッチング素子や主スイッチング素子等の回路素子も過剰に大きな外形のものを選択する必要がなくなるので、装置の小型化、低コスト化を図ることができる。

【図面の簡単な説明】

【0019】

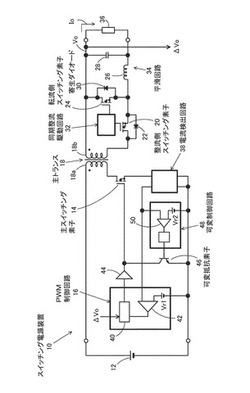

【図1】この発明のスイッチング電源装置の一実施形態を示すブロック図である。

【図2】この実施形態の具体的な回路構成を示す回路図である。

【図3】図2の回路における通常動作を説明するタイムチャートである。

【図4】図2の回路における過電流時の動作を説明するタイムチャートである。

【図5】図2の回路における出力短絡時の動作を説明するタイムチャートである。

【図6】図2の回路に可変抵抗素子及び可変制御回路が設けられていない場合の出力短絡時の動作を説明するタイムチャートである。

【図7】この実施形態の第1変形例を示す回路図である。

【図8】この実施形態の第2変形例を示す回路図である。

【発明を実施するための形態】

【0020】

以下、この発明のスイッチング電源装置の一実施形態について、図面に基づいて説明する。この実施形態のスイッチング電源装置10は、図1に示すように、入力電源12に直列接続され、入力電圧Viを断続する主スイッチング素子14を備えている。主スイッチング素子14は、N−chのMOS型FETが使用されており、後述するPWM制御回路16が出力する一定周期の駆動パルスで駆動され、所定の時比率でオン・オフする。主スイッチング素子14のドレイン端子と入力電源12との間には、主トランス18の1次巻線18aが接続され、主スイッチング素子14のオン・オフによって発生する断続電圧が印加される。また、主トランス18には、1次巻線18aに印加された断続電圧を変圧した交流電圧が発生する2次巻線18bが設けられている。各巻線18a,18bに付したドットは磁気結合の極性を表わしている。

【0021】

2次巻線18bのドットが付されていない端子には、N−chのMOS型FETである整流側スイッチング素子20のドレイン端子が接続されている。整流側スイッチング素子20は、主スイッチング素子14がオンの期間中に2次巻線18bに発生する電圧を整流する。また、整流側スイッチング素子20のソース端子からドレイン端子の向きに、整流側スイッチング素子20のチップ内に存在する寄生ダイオード22が並列に接続されている。なお、MOS型FETである整流側スイッチング素子20及び寄生ダイオード22は、ファストリカバリ・ダイオード等に置き換えてもよい。

【0022】

2次巻線18bのドットが付された端子には、N−chのMOS型FETである転流側スイッチング素子24のドレイン端子が接続されている。転流側スイッチング素子24のソース端子は、整流側スイッチング素子20のソース端子に接続されている。転流側スイッチング素子24は、整流側スイッチング素子20がオフのときに相補的にオンし、後述する平滑インダクタ26が平滑コンデンサ28に向けて蓄積エネルギーを放出するときの電流経路として働く。また、転流側スイッチング素子24のソース端子からドレイン端子の向きに、転流側スイッチング素子24のチップ内に存在するPN接合型の寄生ダイオード30が並列に接続されている。

【0023】

PN接合型の寄生ダイオード30は、理想的には順バイアスの印加によって順方向電流を流し、逆バイアスが印加されても逆方向には電流を流さないという、いわゆる順方向に整流作用を有する素子であるが、順方向電流が流れているときに印加電圧の向きが急激に反転すると、一時的に逆方向にリカバリ電流が流れるという性質がある。MOS型FETに存在する通常の寄生ダイオードは、高速整流用のファストリカバリ・ダイオード等と違ってリカバリ電流が流れる時間(逆回復時間)が長いという性質がある。特に、出力電圧Voが12〜15Vを超えるスイッチング電源装置10の場合、転流側スイッチング素子24として耐圧150〜250V以上のMOS型FETが使用され、その寄生ダイオード30の逆回復時間が無視できないほど長いので、回路動作上の不具合が生じやすい。詳しくは後で説明する。

【0024】

整流側スイッチング素子20と転流側スイッチング素子24は、同期整流駆動回路32が発生する駆動パルスがゲート端子に入力されることによってオン・オフ駆動される。同期整流駆動回路32は、主スイッチング素子14がオン・オフするタイミングに基づいて整流側スイッチング素子20と転流側スイッチング素子24のオン・オフのタイミングを決定すると共に、主スイッチング素子14のオン時間が一定以下に短くなると、転流側スイッチング素子24をオフ状態に保持する動作を行う。

【0025】

転流側スイッチング素子24のドレイン・ソース端子間には、平滑インダクタ26と平滑コンデンサ28とで成るローパスフィルタである平滑回路34の入力側が接続され、平滑コンデンサ28の両端に接続された負荷36に出力電圧Vo及び電流Ioを供給する。

【0026】

電流検出回路38は、主スイッチング素子14に流れるパルス状のスイッチング電流を比例変換した電圧を発生させ、スイッチング電流信号として出力する。

【0027】

主スイッチング素子14を駆動するPWM制御回路16は、駆動パルス発生回路40、比較器42を有している。駆動パルス発生回路40は、出力電圧Voの誤差信号であるΔVoを受け、誤差信号ΔVoが小さくなる方向にパルス幅変調した矩形の駆動パルスを発生させ、バッファ回路44を介して主スイッチング素子14のゲート端子に向けて出力する。比較器42は、電流検出回路38が出力したスイッチング電流信号と第1基準電圧Vr1とを比較し、スイッチング電流信号が第1基準電圧Vr1に達すると駆動パルス発生回路40が出力する駆動パルスを強制的にローレベルに反転させ、駆動パルス発生回路40は、次のスイッチング周期が始まるまで、そのローレベルを維持する動作を行う。第1基準電圧Vr1は、出力電流Ioがスイッチング電源装置10の定格電流を超えたとき(過電流時)に、スイッチング電流信号が第1基準電圧Vr1に達するように設定されており、正常に安定動作しているとき(通常動作時)は、スイッチング電流信号が第1基準電圧Vr1に達しないので比較器42は動作しない。このように、PWM制御回路16は、駆動パルス発生回路40と比較器42により、後述するパルス・バイ・パルス式の過電流保護動作を行うことができる。

【0028】

主スイッチング素子14のゲート・ソース端子間にはNPNトランジスタである可変抵抗素子46が設けられ、さらに、電流検出回路38が出力するスイッチング電流信号に基づいて可変抵抗素子46の抵抗値を変化させる可変制御回路48が設けられている。可変制御回路48は、スイッチング周期ごとに、スイッチング電流信号のピーク値と第2基準電圧Vr2とを比較器50を用いて比較し、スイッチング電流信号が第2基準電圧Vr2未満のときは可変抵抗素子46の抵抗値を非常に大きい値に保持し、第2基準電圧Vr2を超えると可変抵抗素子の抵抗値を低下させる制御信号を瞬時に出力する。これにより、主スイッチング素子14のゲート・ソース端子間電圧が低下し、主スイッチング素子14の導通抵抗が大きくなってスイッチング電流の増加が抑制される動作が行われる。ここで、第2基準電圧Vr2は第1基準電圧Vr1よりも大きな値に設定されており、負荷36が非常に低インピーダンスに故障したとき(出力短絡時)、すなわち、上記の過電流時よりもスイッチング電流が増加したとき等に可変制御回路48が動作し、後述する短絡保護動作を行うことができる。

【0029】

次に、スイッチング電源装置10の具体的な回路構成を、図2に基づいて説明する。同期整流駆動回路32は、主トランス18の3次巻線18c及び電圧保持用のツェナーダイオード52等を含む第1駆動回路54と、主スイッチング素子14のオン・オフのタイミング情報を伝達する信号伝達用トランス56等を含む第2駆動回路58とで構成されている。この第1、第2駆動回路54、58は、特許文献2に開示されている第二実施形態のスイッチング電源装置が有する同期整流素子駆動回路及びゲート放電回路に相当し、ほぼ同様の動作を行う。

【0030】

また、バッファ回路44は、PWM制御回路16に電源供給する直流電源44a、NPNトランジスタ及びPNPトランジスタをいわゆるトーテムポール型に組み合わせて構成されており、PWM制御回路16が出力する駆動パルスを2つのトランジスタのベース端子に受け、複数の抵抗によって所定時間だけ遅延した駆動パルスを主スイッチング素子14のゲート端子に向けて出力する。

【0031】

電流検出回路38は、1次巻線60a、2次巻線60bを有する電流トランス60を有しており、各巻線60a,60bに付したドットは磁気結合の極性を表わしている。この1次巻線60aは、主トランス18の1次巻線18aと入力電源12の接続点に挿入され、そこに流れる主スイッチング素子14のスイッチング電流Id14を検出し、2次巻線60bのドットを付した端子から電流Id14に比例した小さな電流を整流ダイオード62を介して出力する。整流ダイオードの出力と2次巻線60bのドットが付されていない側の一端に電流検出抵抗64が接続され、電流検出抵抗64の両端にスイッチング電流Id14に略比例した電圧であるスイッチング電流信号を発生させる。

【0032】

PMW制御回路16の駆動パルス発生回路40は、上述した比較器42が、カレントモード方式のパルス幅制御を行うための比較器として兼用されており、比較器42の反転入力端子に電流検出抵抗64に発生したスイッチング電流信号が入力され、非反転入力端子に出力電圧Voの誤差分を増幅器65で反転増幅した誤差信号ΔVoを抵抗分圧した信号が入力されている。そして、駆動パルス発生回路40は、比較器42によって主スイッチング素子14のオンの開始後、スイッチング電流信号が上昇して誤差信号ΔVoの分圧値に達したタイミングを検出し、そのタイミングに基づいてパルス幅変調された駆動パルスを生成する。

【0033】

また、比較器42の非反転入力端子には、第1基準電圧Vr1を発生させるツェナーダイオード66が接続されている。通常動作中は誤差信号ΔVoの分圧値がツェナー電圧Vr1よりも低いのでツェナーダイオード66は動作しないが、出力電流Ioが定格を超えて過電流状態になると誤差信号ΔVoの分圧値が上昇してツェナーダイオード66が導通し、非反転入力端子電圧を第1基準電圧Vr1に固定する。

【0034】

可変抵抗素子46は、コレクタ端子が主スイッチング素子14のゲート端子に接続され、エミッタ端子が主スイッチング素子14のソース端子に接続されたNPNトランジスタである。可変制御回路48は、可変抵抗素子46のベース・エミッタ端子間に接続された第1抵抗68と、カソード端子が電流検出回路38の出力端に接続され、アノード端子が可変抵抗素子46のベース端子に接続されたツェナーダイオード70とで構成されている。上述した第2基準電圧Vr2は、ツェナーダイオード70の電圧Vaと可変抵抗素子46のベース・エミッタ間順方向電圧Vbとの合計値である。従って、電流検出抵抗64に発生するスイッチング電流信号が小さいときは、可変抵抗素子46にベース電流が供給されないので可変抵抗素子46が大きな抵抗値の状態になり、スイッチング電流信号が第2基準電圧Vr2に達すると、ツェナーダイオード70が導通して可変抵抗素子46にベース電流が流れるので、コレクタ電流を流すことが可能な小さな抵抗値の状態になる。このように、可変制御回路48は、スイッチング電流信号が第2基準電圧Vr2に達すると、ベース電流を発生させることによって可変抵抗素子46の抵抗値を低下させる動作を行う。

【0035】

また、第1抵抗68は、可変制御回路48が出力するベース電流を適度な値に調節するための抵抗である。第1抵抗68の抵抗値は、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、そのピーク値が低下しても所定の期間は可変抵抗素子46が小さな抵抗値の状態を維持できる程度に大きな抵抗値であり、かつ、その所定の期間が経過した後、速やかに可変抵抗素子46の抵抗値が大きい状態に変化できる程度に小さな抵抗値に設定されている。

【0036】

次に、スイッチング電源装置10の動作を、図3〜図6に基づいて説明する。まず、出力電流Ioが定格以下で動作している通常動作について説明する。通常動作時の各部の動作波形は、図3のタイムチャートのように表わされる。

【0037】

主スイッチング素子14は、PWM制御回路16が出力する一定周期の駆動パルスV16によって駆動され、期間t11〜t12を1周期Tとするスイッチング動作を繰り返す。ここで、説明の便宜のため、転流側スイッチング素子24がオフして主スイッチング素子14がオンするまでの遅延時間は十分に短いものとして無視し、主トランス18の励磁インダクタンスに流れる励磁電流も小さいものとして無視している。

【0038】

期間t11に入る直前は、主スイッチング素子14がオフ、整流側スイッチング素子20がオフ、転流側スイッチング素子24がオンしている。期間t11に入ると、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。また、駆動パルスがハイレベルに転じたことを示すタイミング信号が信号伝達トランス56を介して伝達され、第2駆動回路58の動作により転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24がゲート閾値Vth24未満まで急峻に低下し、転流側スイッチング素子24がオフに転じる。また、主スイッチング素子14がオンすると、主トランス18の1次巻線18aの電圧V18aが急峻に上昇して入力電圧Viになり、それによって3次巻線18cに相似形の電圧が発生し、第1駆動回路54の動作により整流側スイッチング素子20のゲート・ソース端子間電圧がゲート閾値を超えて急峻に上昇し、整流側スイッチング素子20がオンに転じる。また、転流側スイッチング素子24と並列の寄生ダイオード30は、逆方向電圧(Vd24)が印加されるのでオフとなる。

【0039】

主スイッチング素子14がオンすると、スイッチング電流Id14が流れ始め、図3に示すように、期間t11の間、時間の経過とともに電流値が所定の傾きで徐々に増加する略台形状の波形となる。この電流Id14は、入力電源12、主トランス18、負荷36及び平滑コンデンサ28、平滑インダクタ26、整流側スイッチング素子20、主トランス18、主スイッチング素子14の経路に流れ、そのピーク値が出力電流Ioに略比例した値になる。

【0040】

ここで、スイッチング電源装置10は出力電流Ioが定格以下で動作しているので、電流Id14が小さく、過電流保護の第1及び第2基準値Ir1,Ir2に達していない。第1基準値Ir1は、PWM制御回路16の第1基準電圧Vr1に対応するものであり、比較器42に入力されるスイッチング電流信号(電圧信号)がVr1になるときの電流Id14がIr1である。同様に、第2基準値Ir2は、可変制御回路48の第2基準電圧Vr2に対応するものであり、可変制御回路48に入力されるスイッチング電流信号がVr2になるときの電流Id14がIr2である。よって、通常動作中は、PWM制御回路16のツェナーダイオード66は動作せず、可変制御回路48の後段の可変抵抗素子46も状態が変化することなく高い抵抗値を保持する。

【0041】

期間t11の終わりは、PWM制御回路16が出力電圧Voの誤差信号ΔVoを小さくなる方向にパルス幅変調する動作によって決定され、主スイッチング素子14をオンさせるべき期間が経過し、駆動パルスV16がローレベルに転じたところで期間t11が終了する。

【0042】

期間t12に入ると、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。また、主スイッチング素子14がオフすると、主トランス18の1次巻線18aの電圧V18aは急峻に低下してほぼゼロボルトになり、その後、主トランス18に蓄積された励磁エネルギーを放出するリセット動作により正弦波状の緩やかな負方向の電圧が発生する。それによって3次巻線18cに相似形の電圧が発生し、第1駆動回路54の動作により、転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24がゲート閾値Vth24を超えて上昇し、転流側スイッチング素子24がオンに転じる。同様に、3次巻線18cの電圧を受けた第1駆動回路54の動作により、整流側スイッチング素子20のゲート・ソース端子間電圧が低下してゲート閾値未満になり、整流側スイッチング素子20がオフに転じる。

【0043】

主スイッチング素子14がオフするとスイッチング電流Id14が遮断され入力電源12からの出力電流Ioの供給が停止する。そして、オンしている転流側スイッチング素子24に、平滑インダクタ26の励磁エネルギーが出力電流Ioとして放出される電流が流れる。この電流は、転流側スイッチング素子24及び寄生ダイオード30に流れる電流を示す電流Id24の波形のように、時間の経過とともに電流値が所定の傾きで徐々に減少する略台形状の波形となる。この電流Id24は、平滑インダクタ26、転流側スイッチング素子24、負荷36及び平滑コンデンサ28の経路に流れ、概ねそのピーク値が出力電流Ioとなる。

【0044】

1次巻線18aの電圧V18aが負方向のピーク値を示した後、ゼロボルトに向けて上昇し、3次巻線18cのドットと反対方向の電圧も同様に正電圧からゼロボルトに向けて低下する。そして、転流側スイッチング素子24のゲート電圧Vg24が電圧保持用のツェナーダイオード52のツェナー電圧Vzまで低下した時点で、ツェナーダイオード52の動作が停止し、電圧Vg24がVzに保持される。ツェナー電圧Vzはゲート閾値Vth24よりも高い値に設定されているので、期間t12が終了するまで転流側スイッチング素子24がオンを継続することができる。従って、期間t12の間、寄生ダイオード30には順方向電流がほとんど流れず、期間t12が終了して転流側スイッチング素子24がオフに転じる時も、逆方向電流(リカバリ電流)がほとんど流れない。

【0045】

期間t12の終わりは、PWM制御回路16が主スイッチング素子14のオンタイミングを一定の時間間隔にしようとする動作によって決定され、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで期間t12が終了する。

【0046】

スイッチング電源装置10が通常動作をするときは、上記の期間t11〜t12を1周期Tとするスイッチング動作を繰り返し、第1及び第2基準値Ir1,Ir2によってスイッチング電流Id14が制限されることなく、出力電圧Voを所定の電圧に安定化する。

【0047】

次に、出力電流Ioが定格を超える過電流状態であり、第1基準値Ir1に基づくパルス・バイ・パルス式の過電流保護を行う動作について説明する。過電流保護動作時の各部の動作波形は図4のタイムチャートのように表わされ、主スイッチング素子14は、期間t21〜t23を1周期Tとするスイッチング動作を繰り返す。

【0048】

期間t21に入る直前は、主スイッチング素子14がオフ、整流側スイッチング素子20がオフ、転流側スイッチング素子24がオンしている。期間t21に入ると、図3の期間t11とほぼ同様の動作を行う。すなわち、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。転流側スイッチング素子24がオフに転じ、整流側スイッチング素子20がオンに転じる動作も同様である。

【0049】

主スイッチング素子14がオンすると、スイッチング電流Id14が流れ始め、図4に示すように、期間t21の間、時間の経過とともに電流値が所定の傾きで徐々に増加する略台形状の波形となり、そのピーク値が出力電流Ioに略比例した値になる。

【0050】

スイッチング電源装置10は出力電流Ioが定格以上の過電流状態で動作しているので、電流Id14が大きく、期間t21の開始からしばらく経過したときにピーク値が第1基準値Ir1に達することになる。電流Id14が所定の傾きで上昇して第1基準値Ir1になると、電流検出回路38が出力するスイッチング電流信号も上昇して第1基準電圧Vr1になる。期間t21は、PWM制御回路16の比較器42の反転入力端子が受けるスイッチング電流信号のピーク値が第1基準電圧Vr1に達したところで終了する。

【0051】

一方、スイッチング電流Id14が第2基準値Ir2まで上昇せずスイッチング電流信号が第2基準電圧Vr2未満の範囲にあるので、可変制御回路48の後段の可変抵抗素子46の状態も変化することなく高い抵抗値を保持する。

【0052】

期間t22に入っても、駆動パルスVgはハイレベルに維持され、期間t21と同様に主スイッチング素子14がオン、転流側スイッチング素子24がオフ、整流側スイッチング素子20がオンを継続する。本来は、比較器42の反転入力端子にVr1を超えようとするスイッチング電流信号が入力されると、ツェナーダイオード66が動作して非反転入力端子を第1基準電圧Vr1に保持し、比較器42の出力がローレベルに転じ、駆動パルス発生回路40が駆動パルスV16をローレベルに反転させて保持する、という動作が瞬時に行われるのが理想である。しかしながら、実際には、比較器42や駆動パルス発生回路40等の動作遅延により、期間t22の間は、駆動パルスV16が反転することなくハイレベルを維持する。例えば、市販されているICを使用してPWM制御回路16を構成した場合、比較器42の反転入力端子にVr1を超えようとするスイッチング電流信号が入力されてから、駆動パルスV16がローレベルに反転するまでの時間(遅延時間Tm)が、50n〜300nsecほど存在するのが一般的である。

【0053】

また、ここでは、スイッチング電流Id14が第1基準値Ir1に達するものの、第2基準値Ir2には達しないので、可変制御回路48の後段の可変抵抗素子46も変化することなく高い抵抗値を保持する。期間t22は、期間t22が開始して遅延時間Tmが経過し、駆動パルスV16がローレベルに反転したところで終了する。

【0054】

期間t23に入ると、図3の期間t12とほぼ同様の動作を行う。すなわち、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。転流側スイッチング素子24がオンに転じ、整流側スイッチング素子20がオフに転じる動作も同様である。従って、期間t23の間、寄生ダイオード30には順方向電流がほとんど流れず、期間t23が終了して転流側スイッチング素子24がオフに転じる時も、逆方向電流(リカバリ電流)がほとんど流れない。

【0055】

期間t23は、PWM制御回路16が主スイッチング素子14のオンのタイミングを一定間隔にしようとする動作により、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで終了する。

【0056】

スイッチング電源装置10が過電流保護動作をするときは、上記の期間t21〜t23を1周期Tとするスイッチング動作を繰り返す。このような動作により、スイッチング電流Id14のピーク値が第1基準値Ir1を超えないようにする高速制御を行い、出力電流Ioを制限し、かつ、主スイッチング素子14のオン時間を短くして出力電圧Voを低下させることによって、負荷36や装置内部の回路素子を保護することができる。

【0057】

次に、負荷36が非常に低インピーダンスの状態で故障などしたとき(出力短絡時)、第2基準値Ir2に基づく短絡保護を行う動作について説明する。短絡保護動作時の各部の動作波形は図5のタイムチャートのように表わされ、主スイッチング素子14は、期間t31〜t35を1周期Tとするスイッチング動作を繰り返す。

【0058】

なお、短絡保護動作中は、主スイッチング素子14のオン時間が非常に短くなるので、図5に示すように、転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24が、全期間にわたってゲート閾値Vth24に達しない。同様に、図示しない整流側スイッチング素子20のゲート・ソース端子間電圧もゲート閾値に達しない。従って、以下に説明する短絡保護動作中は、転流側スイッチング素子24と整流側スイッチング素子20が全期間にわたってオフしている。

【0059】

期間t31に入る直前は、主スイッチング素子14がオフ、整流側の寄生ダイオード22がオフしており、転流側の寄生ダイオード30は順方向の電流Id24を流してオンしている。期間t31に入ると、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。整流側の寄生ダイオード22も速やかにオンに転じ、順方向の電流を流すことができる状態になる。しかし、転流側の寄生ダイオード30は、上述したように逆回復時間が長いPN接合型のダイオードのため、速やかにオフすることができず、逆方向のリカバリ電流が流れる(リカバリ動作)。

【0060】

このリカバリ電流成分は、入力電源12、主トランス18、転流側の寄生ダイオード30、整流側の寄生ダイオード22、主トランス18、主スイッチング素子14の経路に流れ、図5の電流Id14,Id24の波形に示すように非常に急峻に増加する。リカバリ電流の経路は非常にインピーダンスが低く、主トランス18が有する小さな漏れインダクタンスや主スイッチング素子14のオン・スピード等の要因によって制限されるのみであり、電流増加の傾きが非常に急峻になる。

【0061】

主スイッチング素子14がオンすると、上記のリカバリ動作の影響で、スイッチング電流Id14が瞬時に第1基準値Ir1に達する。すると、PWM制御回路16が、図4で説明した過電流保護の動作を開始するが、駆動パルスV16のハイレベルの時間をPWM制御回路16が有する遅延時間Tmよりも短くすることはできない。従って、主スイッチング素子14のオン時間が短くならないので、スイッチング電流Id14が第1基準値Ir1を超えてさらに上昇し、遅延時間Tmが経過する前に第2基準値Ir2に達する。

【0062】

電流Id14が第2基準値Ir2になると、電流検出回路38が出力するスイッチング電流信号も上昇して第2基準電圧Vr2になる。期間t31は、可変制御回路48に入力されるスイッチング電流信号のピーク値が第2基準電圧Vr2に達したところで終了する。

【0063】

期間t32に入っても、PWM制御回路16の駆動パルスV16は、上記の遅延時間Tmの影響でハイレベルを継続し、バッファ回路44が主スイッチング素子14のゲート・ソース端子間の電圧Vg14をゲート閾値Vth14よりも十分高い電圧に保持しようとする。

【0064】

一方、可変制御回路48は、電流検出回路38が出力するスイッチング電流信号がツェナーダイオード70の電圧Vaと可変抵抗素子46のベース・エミッタ間順方向電圧Vbとの合計値である第2基準電圧Vr2を超えようとすると、ツェナーダイオード70が導通することによって可変抵抗素子46に所定のベース電流を供給し、可変抵抗素子46がコレクタ電流を流すようになって等価的にコレクタ・エミッタ間の抵抗値が小さくなり、主スイッチング素子14のゲート・ソース端子間の電圧Vg14が低下する。このとき、可変制御回路48は、可変抵抗素子46の抵抗値を低下させ、電圧Vg14がゲート閾値Vth14を下回らない範囲でゲート閾値Vth14に近い電圧になるように制御する。従って、MOS型FETである主スイッチング素子14は、所定の大きな導通抵抗をもってオンする状態になる。

【0065】

このように、期間t32では、主スイッチング素子14の導通抵抗を増加させることによって、電流Id14,Id24のピーク値を小さく抑える動作が行われる。このとき、第1抵抗68の調整により可変抵抗素子46に流れるベース電流が最適化されているので、電流Id14,Id24のピーク値が低下し、スイッチング電流信号が第2基準電圧Vr2よりも低くなり、可変制御回路48から可変抵抗素子46へのベース電流の供給が止まっても、遅延時間Tmが経過するまでの間は、可変抵抗素子46が抵抗値を低下させる動作を継続する。

【0066】

期間t32は、PWM制御回路16に第1基準電圧Vr1を超えるスイッチング電流信号が入力されてから遅延時間Tmが経過し、駆動パルスV16がローレベルに反転したところで終了する。

【0067】

期間t33に入ると、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。すると、電流Id14,Id24の経路が、主スイッチング素子14内部のドレイン・ソース端子間に存在する図示しない寄生コンデンサに切り替わる。整流側の寄生ダイオード22はオンを継続し、転流側の寄生ダイオード30もリカバリ動作を継続する。

【0068】

その後、転流側の寄生ダイオード30のリカバリ動作がある程度回復し、電流Id14,Id24がゼロアンペアに近くなって電圧Vd24が上昇し始めたところで期間t33が終了する。

【0069】

期間t34に入ると、主スイッチング素子14はオフを継続し、整流側の寄生ダイオード22はオンを継続し、転流側の寄生ダイオード30のリカバリ動作の回復が進んだことによって、寄生ダイオード30の両端にサージ状の電圧Vd24が発生する。このサージ状の電圧Vd24のピーク値は、期間t34が開始する時の電流Id24に大きく依存するが、上述した期間t32の動作によって電流Id24が小さく抑えられているので、電圧Vd24が危険電圧にまで上昇する心配はない。

【0070】

その後、転流側の寄生ダイオード30のリカバリ動作が回復し、平滑インダクタ26が放出する電流が順方向に流れ始めたところで期間t34が終了する。

【0071】

期間t35に入ると、主スイッチング素子14はオフを継続し、整流側の寄生ダイオードが逆方向にバイアスされてオフに転じる。そして、転流側の寄生ダイオード30に、平滑インダクタ26の励磁エネルギーが出力電流Ioとして放出される電流が順方向に流れ始め、電圧Vd24がほぼゼロボルトに低下する。この電流は、電流Id24の波形のように、時間の経過とともに電流値が所定の傾きで徐々に減少する略台形状の波形となる。この電流Id24は、平滑インダクタ26、寄生ダイオード30、負荷36及び平滑コンデンサ28の経路に流れ、概ねそのピーク値が出力電流Ioとなる。

【0072】

期間t35は、PWM制御回路16が主スイッチング素子14のオンのタイミングを一定間隔にしようとする動作により、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで終了する。

【0073】

スイッチング電源装置10が短絡保護動作をするときは、上記の期間t31〜t35を1周期Tとするスイッチング動作を繰り返す。このような動作により、スイッチング電流Id14のピーク値が第2基準値Ir2を超えないように制限する高速制御を行い、転流側の寄生ダイオード30に逆方向に流れるリカバリ電流を制限し、転流側スイッチング素子24のドレイン・ソース端子間の電圧Vd24が危険電圧まで上昇するのを防止する。また、他の回路素子に対しても過剰な電気的ストレスが加わらないように保護することができ、同時に出力電流Ioも制限され、故障した負荷36が焼損する事故を未然に防止することができる。

【0074】

例えば、上記実施形態のスイッチング電源装置10に可変抵抗素子46と可変制御回路48を設けていない不完全なスイッチング電源装置の場合、出力短絡時に適切な短絡保護が行われない。

【0075】

この不完全なスイッチング電源装置は、第2基準値Vr2に基づいてスイッチング電流Id14を制限する機能を有していないので、図6に示すように、期間t41に入ったときに流れ始める電流Id14,Id24が、遅延時間Tmが経過するまで増加し続ける。そして、期間t42に入って主スイッチング素子14がオフすることによって初めて電流Id14,Id24の増加が抑制され、期間t43に入る直前の電流Id14,Id24が、図5の期間t34に入る直前の電流Id14,Id24よりも大きくなってしまう。その結果、期間t43に入って寄生ダイオード30の両端に発生するサージ状の電圧Vd24が非常に高くなり、転流側スイッチング素子24に大きな電気的ストレスが加わることになる。

【0076】

この場合、転流側スイッチング素子24が故障しないように、定格電圧の高いMOS型FETを選択する必要がある。しかし、MOS型FETは定格電圧が高いものほど導通抵抗が大きくなるという傾向があるので、定格電圧の高いMOS型FETを選択することによって通常動作中の整流損失が大きくなり、外形が大きく高価なMOS型FETを選択しなければならなくなる。

【0077】

以上説明したように、スイッチング電源装置10は、主スイッチング素子14に流れるスイッチング電流Id14を第1基準値Ir1に基づいて制限する過電流保護機能と、第1基準値Ir1よりも大きい第2基準値Ir2に基づいて高速に制限する短絡保護機能とを備えている。従って、負荷36が故障して出力が短絡し、転流側スイッチング素子24の同期整流動作が停止し、転流側の寄生ダイオード30にリカバリ電流Id24が流れた時、スイッチング電流Id14及びリカバリ電流Id24を小さく抑え、転流側スイッチング素子24のドレイン・ソース端子間に過大な電圧Vd24が発生するのを防止することができる。従って、転流側スイッチング素子24として、定格電圧が低く導通抵抗の小さいMOS型FETを選択することができ、低損失化を図ることができる。

【0078】

また、可変抵抗素子46及び可変制御回路48は、NPNトランジスタ、ツェナーダイオード、抵抗という3点の部品を組み合わせてシンプルに構成することができ、狭いスペースにも容易に実装することができる。

【0079】

次に、上記のスイッチング電源装置10の第1変形例について、図7に基づいて説明する。ここで、上記実施形態と同様の構成は、同一の符号を付して説明を省略する。第1変形例では、上記のPWM制御回路16に代えて、スロープ補正回路80を有したPWM制御回路82が設けられ、上記の電流検出回路38に代えて、電流検出抵抗64を主スイッチング素子14のソース端子側に挿入することによって電流トランス60等を省略した電流検出回路84が設けられている。さらに、上記のバッファ回路44が省略され、上記の可変抵抗素子46のコレクタ端子側に抵抗46aが挿入され、上記の可変制御回路48の第1抵抗68と並列に電圧保持コンデンサ90が接続されている。その他の構成は、上記実施形態と同様である。

【0080】

例えば、出力電力の小さいスイッチング電源装置や高入力電圧仕様のスイッチング電源装置の場合、主スイッチング素子14に流れるスイッチング電流Id14が小さいので、電流検出抵抗64に直接スイッチング電流Id14を流しても大きな損失が発生しない。従って、電流検出回路84を使用して構成を簡単化することができる。また、主スイッチング素子14として、ゲート・ソース端子間の駆動が容易な定格電流の小さいMOS型FETを選択することができるので、バッファ回路44を省略することができる。

【0081】

PWM制御回路82のスロープ補正回路80は、誤差信号ΔVoに基づくカレントモード式のパルス幅変調を行うときに問題となる電流発振現象を防止するために設けられたもので、図7に示すように、スイッチング周期に同期してスイッチ86がオン・オフすることによって、比較器42の反転入力端子と電流検出回路84の出力との間に挿入した抵抗88の両端にノコギリ波状の補正電圧Vdを発生させる動作を行う。

【0082】

スロープ補正回路80を設けることで、過電流保護動作及び短絡保護動作に関して以下のような差異が生じる。上記実施形態の場合は、第1基準電圧Vr1が、ツェナーダイオード66が導通した時のツェナー電圧で定まる一定の電圧であったが、第1変形例の場合は、第1基準電圧Vr1が、ツェナーダイオード66が導通した時のツェナー電圧Vcから補正電圧Vdを差し引いた電圧(時間と共に補正電圧Vdの範囲で変化する電圧)になる。しかしながら、第1基準電圧Vr1を第2基準電圧Vr2を超えない範囲に設定することにより、図5、図6を用いて説明した上記実施形態の動作と同様の動作を行い、スイッチング電流Id14を制限することができる。

【0083】

上記実施形態では、出力短絡時、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、遅延時間Tmが経過するまでの間、可変抵抗素子46が小さな抵抗値の状態を維持し、かつ遅延時間Tmが経過した後、速やかに可変抵抗素子46の抵抗値を大きく変化させる、という動作を第1抵抗68の調整により実現していた。しかし、第1抵抗68だけでは調整が困難な場合は、図7の第1変形例のように、可変抵抗素子46のコレクタ端子側に所定の抵抗46aを挿入したり、第1抵抗68と並列に電圧保持コンデンサ90を接続したりすることにより、調整を容易にすることができる。

【0084】

次に、上記のスイッチング電源装置10の第2変形例について、図8に基づいて説明する。ここで、上記実施形態と同様の構成は、同一の符号を付して説明を省略する。第2変形例では、上記のPWM制御回路16に代えて、誤差信号ΔVoに基づくボルテージモード式のパルス幅変調を行う駆動パルス発生回路91と、反転入力端子に電流検出回路96のスイッチング電流信号が入力され、非反転入力端子に負の第1基準電圧Vr1が入力される比較器42とで成るPWM制御回路92とが設けられている。また、上記の可変制御回路48のツェナーダイオード70が第2抵抗94に置き換えられ、第1抵抗68と並列に電圧保持コンデンサ90が接続されている。また、上記実施形態の電流検出回路38に代えて第1変形例の電流検出回路84が設けられ、電流検出回路84と直列に、負のスイッチング電流信号を発生し比較器42の反転入力端子に向けて出力する電流検出回路96が新たに設けられている。その他の構成は、上記実施形態と同様である。

【0085】

第2変形例のPWM制御回路92は、比較器42の非反転入力端子に負の第1基準電圧Vr1が入力されているので、その反転入力端子に負のスイッチング電流信号を入力しなければならない。そこで、電流検出回路84とは別に、スイッチング電流Id14に比例した負のスイッチング電流信号を出力する電流検出回路96が設けられている。電流検出回路96は、スイッチング電流Id14が流れて負の電圧が発生する電流検出抵抗98と、その負電圧を分圧する分圧抵抗100a,100bと、分圧抵抗100bに発生する負のスイッチング電流信号からスパイク成分を除去するコンデンサ102で構成されている。このコンデンサ102は、可変抵抗素子46の抵抗値を高速に変化させる動作には影響しない。また、可変抵抗素子46の抵抗値制御の調整のしやすさを考慮し、可変制御回路48に第2抵抗94が設けられている。

【0086】

このように構成の一部が変更された第2変形例においても、過電流保護動作及び短絡保護動作に関しては、図5、図6を用いて説明した上記実施形態の動作と同様の動作を行い、スイッチング電流Id14を制限することができる。

【0087】

なお、この発明のスイッチング電源装置は、上記実施形態及び変形例に限定されるものではない。例えば、上記実施形態及び変形例では、出力短絡時、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、遅延時間Tmが経過するまでの間、可変抵抗素子46が小さな抵抗値の状態を維持し、かつ遅延時間Tmが経過した後、速やかに可変抵抗素子46の抵抗値を大きく変化させる、という動作を行う構成になっているが、遅延時間Tmが経過する前に可変抵抗素子46の抵抗値が大きく変化するよう設定してもよい。この場合、遅延時間Tmの間に主スイッチング素子が複数回オン・オフし、主スイッチンング素子14のクロス損失が増加する可能性がある。しかし、遅延時間Tmというごく短い期間だけの動作であり、主スイッチング素子14の損失増加はさほど大きくない。従って、主スイッチング素子14が故障する心配がなければ、このような動作を許容することができる。

【0088】

また、同期整流駆動回路は、上記実施形態のような主トランスの巻線に発生する電圧を利用した巻線駆動方式に限定するものではなく、出力短絡時など主スイッチング素子のオン時間が一定以下に短くなると、転流側スイッチング素子をオフ状態に保持する機能を備えたものであれば、例えば、転流側スイッチング素子を、主トランスの2次側に設けた専用ICを用いて駆動する方式や、PWM制御回路の駆動パルスを駆動トランスを介して転流側スイッチング素子に伝達して駆動する方式などであってもよい。

【符号の説明】

【0089】

10 スイッチング電源装置

14 主スイッチング素子

16,82,92 PWM制御回路

18 主トランス

20 整流側スイッチング素子

24 転流側スイッチング素子

22,30 寄生ダイオード

32 同期整流駆動回路

34 平滑回路

38,84,96 電流検出回路

46 可変抵抗素子

48 可変制御回路

68 第1抵抗

70 ツェナーダイオード

90 電圧保持コンデンサ

94 第2抵抗

Ir1 第1基準値

Ir2 第2基準値

Vr1 第1基準電圧

Vr2 第2基準電圧

【技術分野】

【0001】

この発明は、過電流保護機能を有し、同期整流回路を備えたシングルエンディッド・フォワード型のスイッチング電源装置に関する。

【背景技術】

【0002】

一般的なスイッチング電源装置は、通電中に故障した負荷を保護する(例えば、焼損事故等の防止)ため、負荷に向けて出力可能な出力電流を一定以下に制限する過電流保護機能を備えている。従来から、過電流保護には様々な方式があり、中でも、主スイッチング素子に流れるパルス状のスイッチング電流をスイッチング周期ごとに観測しそのピーク値を制限するパルス・バイ・パルス方式が使用される場合が多い。

【0003】

パルス・バイ・パルス方式の過電流保護は、スイッチング電流のピーク値を1パルスごとに制限するため、スイッチング電源装置の内部素子(例えば、主スイッチング素子、整流素子などの半導体素子)に過大な電気的ストレスが加わるのを防ぐことができる。従って、出力電流が大きくなったときだけでなく、例えばスイッチング電源装置に入力電圧を投入し、出力の平滑コンデンサを急速充電して出力電圧を上昇させる動作においても内部素子が保護されるという利点がある。また、シングルエンディッド・フォワード型のスイッチング電源装置の場合、主スイッチング素子に流れるスイッチング電流のピーク値が出力電流と略比例の関係にあることから、出力電流の上限値を精度よく規定することができるという利点もある。

【0004】

例えば、特許文献1に開示されているスイッチング電源装置は、パルス・バイ・パルス方式の過電流保護回路を備えたシングルエンディッド・フォワード型のスイッチング電源装置である。このスイッチング電源装置は、主スイッチング素子に流れるスイッチング電流を電圧に変換する電流検出抵抗と、その検出電圧に重畳したスパイク成分を除去する積分回路と、積分回路の出力が基準値に達すると主スイッチング素子のゲート・ソース端子間に設けたトランジスタがオンして主スイッチング素子を強制的にオフさせ、主スイッチング素子のオン時間を短くするPWM回路とを備えている。さらに、積分回路の出力が高くなるとスイッチング周波数を低下させる発振周波数制御回路が設けられている。このスイッチング電源装置は、積分回路やPWM回路の動作遅延によりスイッチング電流のピーク値を基準値以下に制限することができず過電流垂下特性が裾を引くという問題を、出力電流が一定以上に大きくなるとスイッチング周波数を低下させることによって解消するものである。

【0005】

近年、トランスの2次側の整流ダイオードの損失を低減するため、導通抵抗の小さいMOS型FETを使用して同期整流を行うスイッチング電源装置が提案されている。例えば、特許文献2に開示されているように、シングルエンディッド・フォワード型のコンバータ回路を有し、N−ch(チャネル)のMOS型FETである整流側及び転流側スイッチング素子と、それらを駆動する所定の駆動回路を備えたスイッチング電源装置がある。駆動回路は、主トランスの3次巻線に発生する電圧を利用した巻線駆動方式であり、転流側スイッチング素子をオフさせるタイミングについては信号伝達用トランスからのタイミング信号によって決定する。このスイッチング電源装置は、整流側及び転流側スイッチング素子の駆動回路がシンプルな構成でありながら、主スイッチング素子、整流側及び転流側スイッチング素子のオン・オフのタイミング制御を適正化することができる。なお、特許文献2では、過電流保護回路について説明がされていない。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開昭63−35171号公報

【特許文献2】特開2005−12919号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

特許文献1のスイッチング電源装置の場合、スイッチング電流が急増して発振周波数制御回路が動作を開始しスイッチング周波数が実際に低下するまで、ある程度の時間がかかるので、その期間に流れるスイッチング電流のピーク値が大きくなってしまうという問題がある。例えば、正常運転しているときに負荷である装置が故障し、スイッチング電源装置の出力端が急峻に短絡されると、発振周波数制御回路が発振回路の時定数を可変する動作を行うが、スイッチング周波数の変化は緩慢なため、少なくともスイッチング電流の1〜3パルス程度はピーク値が大きくなり、それに起因して装置内部の回路素子に大きな電気的ストレスが加わってしまう。特に、主スイッチング素子等の半導体は、電流ストレス、電圧ストレスまたは損失による熱ストレスに弱く、短時間でも過大なストレスが加わると破壊するおそれがある。従って、このスイッチング電源装置の過電流保護回路は、スイッチング電源装置内部の回路素子を確実に保護することができないものであった。また、主スイッチング素子等の半導体の安全性を確保するため、大型で電流定格や電圧定格の高い高価な素子を選択しなければならなかった。

【0008】

特許文献2のスイッチング電源装置に特許文献1の過電流保護回路を付加したとしても、上記と同様の問題が生じ得る。

【0009】

この発明は、上記背景技術に鑑みて成されたものであり、低損失の同期整流回路を有し、出力短絡時などに負荷や内部の回路素子を確実に保護することができるシングルエンディッド・フォワード型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0010】

この発明は、入力電源と直列に接続されたN−chのMOS型FETであって、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、前記交流電圧が印加される1次巻線及びそれに磁気結合した2次巻線を有する主トランスと、一端が前記2次巻線の一端に接続され、前記主スイッチング素子がオンの期間中に前記2次巻線に発生した電圧を整流する整流側スイッチング素子と、前記2次巻線の他の一端と前記整流側スイッチング素子の他の一端にドレイン端子とソース端子が各々接続され、前記主スイッチング素子がオフの期間中にオンして前記ソース端子から前記ドレイン端子の向きに電流を流すN−chのMOS型FETである転流側スイッチング素子と、前記転流側スイッチング素子の内部のドレイン・ソース端子間に形成された寄生ダイオードと、前記転流側スイッチング素子をオン・オフ駆動する回路であって、前記主スイッチング素子のオン時間が一定以下に短くなると、前記転流側スイッチング素子をオフ状態に保持する同期整流駆動回路と、平滑チョーク及び平滑コンデンサで成るローパスフィルタであって、前記転流側スイッチング素子のドレイン・ソース端子間にその入力側が接続され、前記平滑コンデンサ両端に直流の出力電圧を生成して負荷に電力を供給する平滑回路と、前記主スイッチング素子に流れるスイッチング電流を検出する電流検出回路と、前記出力電圧の誤差信号に基づいてパルス幅変調した矩形の駆動パルスを出力して前記主スイッチング素子のオン・オフを制御すると共に、前記電流検出回路の出力信号を受け前記スイッチング電流のピーク値が第1基準値に達すると前記主スイッチング素子をオフさせるため前記駆動パルスをローレベルにするパルス・バイ・パルス式の過電流保護動作を行うPWM制御回路と、を備えたシングルエンディッド・フォワード型のスイッチング電源装置である。

【0011】

さらに、前記主スイッチング素子のゲート・ソース端子間に接続された可変抵抗素子と、前記電流検出回路の出力信号に基づいて前記可変抵抗素子の抵抗値を変化させる可変制御回路とを備え、前記可変制御回路は、前記電流検出回路の出力信号を受けスイッチング周期ごとに前記スイッチング電流のピーク値と前記第1基準値よりも高い第2基準値とを比較し、前記スイッチング電流が前記第2基準値に達すると前記可変抵抗素子の抵抗値を低下させ、前記主スイッチング素子のゲート・ソース端子間電圧を上げないように制御することによって前記スイッチング電流のピーク値の上昇を抑制し、前記転流側スイッチング素子の寄生ダイオードのリカバリ電流のピーク値を制限するスイッチング電源装置である。

【0012】

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記可変抵抗素子の抵抗値を低下させる動作を継続する。

【0013】

前記抵抗値可変素子は、コレクタ端子が前記主スイッチング素子のゲート端子側に接続され、エミッタ端子が前記主スイッチング素子のソース端子に接続されたNPNトランジスタであり、前記可変制御回路は、前記NPNトランジスタのベース電流を制御することによって前記NPNトランジスタのコレクタ・エミッタ端子間の導通抵抗を変化させるものである。

【0014】

また、前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、カソード端子が前記電流検出回路の出力端に接続され、アノード端子が前記NPNトランジスタのベース端子に接続されたツェナーダイオードとで構成されている。

【0015】

また、前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、両端が前記電流検出回路の出力端と前記NPNトランジスタのベース端子の間に接続された第2抵抗とで構成されている。

【0016】

また、前記第1抵抗と並列に電圧保持コンデンサが接続され、前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記NPNトランジスタのベース電流を前記電圧保持コンデンサから供給することによって、前記可変抵抗素子の抵抗値を低下させる動作を継続する。

【発明の効果】

【0017】

この発明のスイッチング電源装置によれば、負荷が故障して出力が短絡し、転流側スイッチング素子の同期整流動作が停止し、転流側スイッチング素子の寄生ダイオードにリカバリ電流が流れた時、スイッチング電流及びリカバリ電流を小さく抑え、転流側スイッチング素子のドレイン・ソース端子間に過大な電圧が発生するのを防止することができる。従って、転流側スイッチング素子として導通抵抗の小さい低耐圧のMOS型FETを選択することができ、低損失化を図ることができる。

【0018】

また、可変抵抗素子及び可変制御回路は、例えばNPNトランジスタ、ツェナーダイオード、第1及び第2抵抗、保持コンデンサなど組み合わせてシンプルに構成することができ、さらに転流側スイッチング素子や主スイッチング素子等の回路素子も過剰に大きな外形のものを選択する必要がなくなるので、装置の小型化、低コスト化を図ることができる。

【図面の簡単な説明】

【0019】

【図1】この発明のスイッチング電源装置の一実施形態を示すブロック図である。

【図2】この実施形態の具体的な回路構成を示す回路図である。

【図3】図2の回路における通常動作を説明するタイムチャートである。

【図4】図2の回路における過電流時の動作を説明するタイムチャートである。

【図5】図2の回路における出力短絡時の動作を説明するタイムチャートである。

【図6】図2の回路に可変抵抗素子及び可変制御回路が設けられていない場合の出力短絡時の動作を説明するタイムチャートである。

【図7】この実施形態の第1変形例を示す回路図である。

【図8】この実施形態の第2変形例を示す回路図である。

【発明を実施するための形態】

【0020】

以下、この発明のスイッチング電源装置の一実施形態について、図面に基づいて説明する。この実施形態のスイッチング電源装置10は、図1に示すように、入力電源12に直列接続され、入力電圧Viを断続する主スイッチング素子14を備えている。主スイッチング素子14は、N−chのMOS型FETが使用されており、後述するPWM制御回路16が出力する一定周期の駆動パルスで駆動され、所定の時比率でオン・オフする。主スイッチング素子14のドレイン端子と入力電源12との間には、主トランス18の1次巻線18aが接続され、主スイッチング素子14のオン・オフによって発生する断続電圧が印加される。また、主トランス18には、1次巻線18aに印加された断続電圧を変圧した交流電圧が発生する2次巻線18bが設けられている。各巻線18a,18bに付したドットは磁気結合の極性を表わしている。

【0021】

2次巻線18bのドットが付されていない端子には、N−chのMOS型FETである整流側スイッチング素子20のドレイン端子が接続されている。整流側スイッチング素子20は、主スイッチング素子14がオンの期間中に2次巻線18bに発生する電圧を整流する。また、整流側スイッチング素子20のソース端子からドレイン端子の向きに、整流側スイッチング素子20のチップ内に存在する寄生ダイオード22が並列に接続されている。なお、MOS型FETである整流側スイッチング素子20及び寄生ダイオード22は、ファストリカバリ・ダイオード等に置き換えてもよい。

【0022】

2次巻線18bのドットが付された端子には、N−chのMOS型FETである転流側スイッチング素子24のドレイン端子が接続されている。転流側スイッチング素子24のソース端子は、整流側スイッチング素子20のソース端子に接続されている。転流側スイッチング素子24は、整流側スイッチング素子20がオフのときに相補的にオンし、後述する平滑インダクタ26が平滑コンデンサ28に向けて蓄積エネルギーを放出するときの電流経路として働く。また、転流側スイッチング素子24のソース端子からドレイン端子の向きに、転流側スイッチング素子24のチップ内に存在するPN接合型の寄生ダイオード30が並列に接続されている。

【0023】

PN接合型の寄生ダイオード30は、理想的には順バイアスの印加によって順方向電流を流し、逆バイアスが印加されても逆方向には電流を流さないという、いわゆる順方向に整流作用を有する素子であるが、順方向電流が流れているときに印加電圧の向きが急激に反転すると、一時的に逆方向にリカバリ電流が流れるという性質がある。MOS型FETに存在する通常の寄生ダイオードは、高速整流用のファストリカバリ・ダイオード等と違ってリカバリ電流が流れる時間(逆回復時間)が長いという性質がある。特に、出力電圧Voが12〜15Vを超えるスイッチング電源装置10の場合、転流側スイッチング素子24として耐圧150〜250V以上のMOS型FETが使用され、その寄生ダイオード30の逆回復時間が無視できないほど長いので、回路動作上の不具合が生じやすい。詳しくは後で説明する。

【0024】

整流側スイッチング素子20と転流側スイッチング素子24は、同期整流駆動回路32が発生する駆動パルスがゲート端子に入力されることによってオン・オフ駆動される。同期整流駆動回路32は、主スイッチング素子14がオン・オフするタイミングに基づいて整流側スイッチング素子20と転流側スイッチング素子24のオン・オフのタイミングを決定すると共に、主スイッチング素子14のオン時間が一定以下に短くなると、転流側スイッチング素子24をオフ状態に保持する動作を行う。

【0025】

転流側スイッチング素子24のドレイン・ソース端子間には、平滑インダクタ26と平滑コンデンサ28とで成るローパスフィルタである平滑回路34の入力側が接続され、平滑コンデンサ28の両端に接続された負荷36に出力電圧Vo及び電流Ioを供給する。

【0026】

電流検出回路38は、主スイッチング素子14に流れるパルス状のスイッチング電流を比例変換した電圧を発生させ、スイッチング電流信号として出力する。

【0027】

主スイッチング素子14を駆動するPWM制御回路16は、駆動パルス発生回路40、比較器42を有している。駆動パルス発生回路40は、出力電圧Voの誤差信号であるΔVoを受け、誤差信号ΔVoが小さくなる方向にパルス幅変調した矩形の駆動パルスを発生させ、バッファ回路44を介して主スイッチング素子14のゲート端子に向けて出力する。比較器42は、電流検出回路38が出力したスイッチング電流信号と第1基準電圧Vr1とを比較し、スイッチング電流信号が第1基準電圧Vr1に達すると駆動パルス発生回路40が出力する駆動パルスを強制的にローレベルに反転させ、駆動パルス発生回路40は、次のスイッチング周期が始まるまで、そのローレベルを維持する動作を行う。第1基準電圧Vr1は、出力電流Ioがスイッチング電源装置10の定格電流を超えたとき(過電流時)に、スイッチング電流信号が第1基準電圧Vr1に達するように設定されており、正常に安定動作しているとき(通常動作時)は、スイッチング電流信号が第1基準電圧Vr1に達しないので比較器42は動作しない。このように、PWM制御回路16は、駆動パルス発生回路40と比較器42により、後述するパルス・バイ・パルス式の過電流保護動作を行うことができる。

【0028】

主スイッチング素子14のゲート・ソース端子間にはNPNトランジスタである可変抵抗素子46が設けられ、さらに、電流検出回路38が出力するスイッチング電流信号に基づいて可変抵抗素子46の抵抗値を変化させる可変制御回路48が設けられている。可変制御回路48は、スイッチング周期ごとに、スイッチング電流信号のピーク値と第2基準電圧Vr2とを比較器50を用いて比較し、スイッチング電流信号が第2基準電圧Vr2未満のときは可変抵抗素子46の抵抗値を非常に大きい値に保持し、第2基準電圧Vr2を超えると可変抵抗素子の抵抗値を低下させる制御信号を瞬時に出力する。これにより、主スイッチング素子14のゲート・ソース端子間電圧が低下し、主スイッチング素子14の導通抵抗が大きくなってスイッチング電流の増加が抑制される動作が行われる。ここで、第2基準電圧Vr2は第1基準電圧Vr1よりも大きな値に設定されており、負荷36が非常に低インピーダンスに故障したとき(出力短絡時)、すなわち、上記の過電流時よりもスイッチング電流が増加したとき等に可変制御回路48が動作し、後述する短絡保護動作を行うことができる。

【0029】

次に、スイッチング電源装置10の具体的な回路構成を、図2に基づいて説明する。同期整流駆動回路32は、主トランス18の3次巻線18c及び電圧保持用のツェナーダイオード52等を含む第1駆動回路54と、主スイッチング素子14のオン・オフのタイミング情報を伝達する信号伝達用トランス56等を含む第2駆動回路58とで構成されている。この第1、第2駆動回路54、58は、特許文献2に開示されている第二実施形態のスイッチング電源装置が有する同期整流素子駆動回路及びゲート放電回路に相当し、ほぼ同様の動作を行う。

【0030】

また、バッファ回路44は、PWM制御回路16に電源供給する直流電源44a、NPNトランジスタ及びPNPトランジスタをいわゆるトーテムポール型に組み合わせて構成されており、PWM制御回路16が出力する駆動パルスを2つのトランジスタのベース端子に受け、複数の抵抗によって所定時間だけ遅延した駆動パルスを主スイッチング素子14のゲート端子に向けて出力する。

【0031】

電流検出回路38は、1次巻線60a、2次巻線60bを有する電流トランス60を有しており、各巻線60a,60bに付したドットは磁気結合の極性を表わしている。この1次巻線60aは、主トランス18の1次巻線18aと入力電源12の接続点に挿入され、そこに流れる主スイッチング素子14のスイッチング電流Id14を検出し、2次巻線60bのドットを付した端子から電流Id14に比例した小さな電流を整流ダイオード62を介して出力する。整流ダイオードの出力と2次巻線60bのドットが付されていない側の一端に電流検出抵抗64が接続され、電流検出抵抗64の両端にスイッチング電流Id14に略比例した電圧であるスイッチング電流信号を発生させる。

【0032】

PMW制御回路16の駆動パルス発生回路40は、上述した比較器42が、カレントモード方式のパルス幅制御を行うための比較器として兼用されており、比較器42の反転入力端子に電流検出抵抗64に発生したスイッチング電流信号が入力され、非反転入力端子に出力電圧Voの誤差分を増幅器65で反転増幅した誤差信号ΔVoを抵抗分圧した信号が入力されている。そして、駆動パルス発生回路40は、比較器42によって主スイッチング素子14のオンの開始後、スイッチング電流信号が上昇して誤差信号ΔVoの分圧値に達したタイミングを検出し、そのタイミングに基づいてパルス幅変調された駆動パルスを生成する。

【0033】

また、比較器42の非反転入力端子には、第1基準電圧Vr1を発生させるツェナーダイオード66が接続されている。通常動作中は誤差信号ΔVoの分圧値がツェナー電圧Vr1よりも低いのでツェナーダイオード66は動作しないが、出力電流Ioが定格を超えて過電流状態になると誤差信号ΔVoの分圧値が上昇してツェナーダイオード66が導通し、非反転入力端子電圧を第1基準電圧Vr1に固定する。

【0034】

可変抵抗素子46は、コレクタ端子が主スイッチング素子14のゲート端子に接続され、エミッタ端子が主スイッチング素子14のソース端子に接続されたNPNトランジスタである。可変制御回路48は、可変抵抗素子46のベース・エミッタ端子間に接続された第1抵抗68と、カソード端子が電流検出回路38の出力端に接続され、アノード端子が可変抵抗素子46のベース端子に接続されたツェナーダイオード70とで構成されている。上述した第2基準電圧Vr2は、ツェナーダイオード70の電圧Vaと可変抵抗素子46のベース・エミッタ間順方向電圧Vbとの合計値である。従って、電流検出抵抗64に発生するスイッチング電流信号が小さいときは、可変抵抗素子46にベース電流が供給されないので可変抵抗素子46が大きな抵抗値の状態になり、スイッチング電流信号が第2基準電圧Vr2に達すると、ツェナーダイオード70が導通して可変抵抗素子46にベース電流が流れるので、コレクタ電流を流すことが可能な小さな抵抗値の状態になる。このように、可変制御回路48は、スイッチング電流信号が第2基準電圧Vr2に達すると、ベース電流を発生させることによって可変抵抗素子46の抵抗値を低下させる動作を行う。

【0035】

また、第1抵抗68は、可変制御回路48が出力するベース電流を適度な値に調節するための抵抗である。第1抵抗68の抵抗値は、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、そのピーク値が低下しても所定の期間は可変抵抗素子46が小さな抵抗値の状態を維持できる程度に大きな抵抗値であり、かつ、その所定の期間が経過した後、速やかに可変抵抗素子46の抵抗値が大きい状態に変化できる程度に小さな抵抗値に設定されている。

【0036】

次に、スイッチング電源装置10の動作を、図3〜図6に基づいて説明する。まず、出力電流Ioが定格以下で動作している通常動作について説明する。通常動作時の各部の動作波形は、図3のタイムチャートのように表わされる。

【0037】

主スイッチング素子14は、PWM制御回路16が出力する一定周期の駆動パルスV16によって駆動され、期間t11〜t12を1周期Tとするスイッチング動作を繰り返す。ここで、説明の便宜のため、転流側スイッチング素子24がオフして主スイッチング素子14がオンするまでの遅延時間は十分に短いものとして無視し、主トランス18の励磁インダクタンスに流れる励磁電流も小さいものとして無視している。

【0038】

期間t11に入る直前は、主スイッチング素子14がオフ、整流側スイッチング素子20がオフ、転流側スイッチング素子24がオンしている。期間t11に入ると、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。また、駆動パルスがハイレベルに転じたことを示すタイミング信号が信号伝達トランス56を介して伝達され、第2駆動回路58の動作により転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24がゲート閾値Vth24未満まで急峻に低下し、転流側スイッチング素子24がオフに転じる。また、主スイッチング素子14がオンすると、主トランス18の1次巻線18aの電圧V18aが急峻に上昇して入力電圧Viになり、それによって3次巻線18cに相似形の電圧が発生し、第1駆動回路54の動作により整流側スイッチング素子20のゲート・ソース端子間電圧がゲート閾値を超えて急峻に上昇し、整流側スイッチング素子20がオンに転じる。また、転流側スイッチング素子24と並列の寄生ダイオード30は、逆方向電圧(Vd24)が印加されるのでオフとなる。

【0039】

主スイッチング素子14がオンすると、スイッチング電流Id14が流れ始め、図3に示すように、期間t11の間、時間の経過とともに電流値が所定の傾きで徐々に増加する略台形状の波形となる。この電流Id14は、入力電源12、主トランス18、負荷36及び平滑コンデンサ28、平滑インダクタ26、整流側スイッチング素子20、主トランス18、主スイッチング素子14の経路に流れ、そのピーク値が出力電流Ioに略比例した値になる。

【0040】

ここで、スイッチング電源装置10は出力電流Ioが定格以下で動作しているので、電流Id14が小さく、過電流保護の第1及び第2基準値Ir1,Ir2に達していない。第1基準値Ir1は、PWM制御回路16の第1基準電圧Vr1に対応するものであり、比較器42に入力されるスイッチング電流信号(電圧信号)がVr1になるときの電流Id14がIr1である。同様に、第2基準値Ir2は、可変制御回路48の第2基準電圧Vr2に対応するものであり、可変制御回路48に入力されるスイッチング電流信号がVr2になるときの電流Id14がIr2である。よって、通常動作中は、PWM制御回路16のツェナーダイオード66は動作せず、可変制御回路48の後段の可変抵抗素子46も状態が変化することなく高い抵抗値を保持する。

【0041】

期間t11の終わりは、PWM制御回路16が出力電圧Voの誤差信号ΔVoを小さくなる方向にパルス幅変調する動作によって決定され、主スイッチング素子14をオンさせるべき期間が経過し、駆動パルスV16がローレベルに転じたところで期間t11が終了する。

【0042】

期間t12に入ると、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。また、主スイッチング素子14がオフすると、主トランス18の1次巻線18aの電圧V18aは急峻に低下してほぼゼロボルトになり、その後、主トランス18に蓄積された励磁エネルギーを放出するリセット動作により正弦波状の緩やかな負方向の電圧が発生する。それによって3次巻線18cに相似形の電圧が発生し、第1駆動回路54の動作により、転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24がゲート閾値Vth24を超えて上昇し、転流側スイッチング素子24がオンに転じる。同様に、3次巻線18cの電圧を受けた第1駆動回路54の動作により、整流側スイッチング素子20のゲート・ソース端子間電圧が低下してゲート閾値未満になり、整流側スイッチング素子20がオフに転じる。

【0043】

主スイッチング素子14がオフするとスイッチング電流Id14が遮断され入力電源12からの出力電流Ioの供給が停止する。そして、オンしている転流側スイッチング素子24に、平滑インダクタ26の励磁エネルギーが出力電流Ioとして放出される電流が流れる。この電流は、転流側スイッチング素子24及び寄生ダイオード30に流れる電流を示す電流Id24の波形のように、時間の経過とともに電流値が所定の傾きで徐々に減少する略台形状の波形となる。この電流Id24は、平滑インダクタ26、転流側スイッチング素子24、負荷36及び平滑コンデンサ28の経路に流れ、概ねそのピーク値が出力電流Ioとなる。

【0044】

1次巻線18aの電圧V18aが負方向のピーク値を示した後、ゼロボルトに向けて上昇し、3次巻線18cのドットと反対方向の電圧も同様に正電圧からゼロボルトに向けて低下する。そして、転流側スイッチング素子24のゲート電圧Vg24が電圧保持用のツェナーダイオード52のツェナー電圧Vzまで低下した時点で、ツェナーダイオード52の動作が停止し、電圧Vg24がVzに保持される。ツェナー電圧Vzはゲート閾値Vth24よりも高い値に設定されているので、期間t12が終了するまで転流側スイッチング素子24がオンを継続することができる。従って、期間t12の間、寄生ダイオード30には順方向電流がほとんど流れず、期間t12が終了して転流側スイッチング素子24がオフに転じる時も、逆方向電流(リカバリ電流)がほとんど流れない。

【0045】

期間t12の終わりは、PWM制御回路16が主スイッチング素子14のオンタイミングを一定の時間間隔にしようとする動作によって決定され、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで期間t12が終了する。

【0046】

スイッチング電源装置10が通常動作をするときは、上記の期間t11〜t12を1周期Tとするスイッチング動作を繰り返し、第1及び第2基準値Ir1,Ir2によってスイッチング電流Id14が制限されることなく、出力電圧Voを所定の電圧に安定化する。

【0047】

次に、出力電流Ioが定格を超える過電流状態であり、第1基準値Ir1に基づくパルス・バイ・パルス式の過電流保護を行う動作について説明する。過電流保護動作時の各部の動作波形は図4のタイムチャートのように表わされ、主スイッチング素子14は、期間t21〜t23を1周期Tとするスイッチング動作を繰り返す。

【0048】

期間t21に入る直前は、主スイッチング素子14がオフ、整流側スイッチング素子20がオフ、転流側スイッチング素子24がオンしている。期間t21に入ると、図3の期間t11とほぼ同様の動作を行う。すなわち、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。転流側スイッチング素子24がオフに転じ、整流側スイッチング素子20がオンに転じる動作も同様である。

【0049】

主スイッチング素子14がオンすると、スイッチング電流Id14が流れ始め、図4に示すように、期間t21の間、時間の経過とともに電流値が所定の傾きで徐々に増加する略台形状の波形となり、そのピーク値が出力電流Ioに略比例した値になる。

【0050】

スイッチング電源装置10は出力電流Ioが定格以上の過電流状態で動作しているので、電流Id14が大きく、期間t21の開始からしばらく経過したときにピーク値が第1基準値Ir1に達することになる。電流Id14が所定の傾きで上昇して第1基準値Ir1になると、電流検出回路38が出力するスイッチング電流信号も上昇して第1基準電圧Vr1になる。期間t21は、PWM制御回路16の比較器42の反転入力端子が受けるスイッチング電流信号のピーク値が第1基準電圧Vr1に達したところで終了する。

【0051】

一方、スイッチング電流Id14が第2基準値Ir2まで上昇せずスイッチング電流信号が第2基準電圧Vr2未満の範囲にあるので、可変制御回路48の後段の可変抵抗素子46の状態も変化することなく高い抵抗値を保持する。

【0052】

期間t22に入っても、駆動パルスVgはハイレベルに維持され、期間t21と同様に主スイッチング素子14がオン、転流側スイッチング素子24がオフ、整流側スイッチング素子20がオンを継続する。本来は、比較器42の反転入力端子にVr1を超えようとするスイッチング電流信号が入力されると、ツェナーダイオード66が動作して非反転入力端子を第1基準電圧Vr1に保持し、比較器42の出力がローレベルに転じ、駆動パルス発生回路40が駆動パルスV16をローレベルに反転させて保持する、という動作が瞬時に行われるのが理想である。しかしながら、実際には、比較器42や駆動パルス発生回路40等の動作遅延により、期間t22の間は、駆動パルスV16が反転することなくハイレベルを維持する。例えば、市販されているICを使用してPWM制御回路16を構成した場合、比較器42の反転入力端子にVr1を超えようとするスイッチング電流信号が入力されてから、駆動パルスV16がローレベルに反転するまでの時間(遅延時間Tm)が、50n〜300nsecほど存在するのが一般的である。

【0053】

また、ここでは、スイッチング電流Id14が第1基準値Ir1に達するものの、第2基準値Ir2には達しないので、可変制御回路48の後段の可変抵抗素子46も変化することなく高い抵抗値を保持する。期間t22は、期間t22が開始して遅延時間Tmが経過し、駆動パルスV16がローレベルに反転したところで終了する。

【0054】

期間t23に入ると、図3の期間t12とほぼ同様の動作を行う。すなわち、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。転流側スイッチング素子24がオンに転じ、整流側スイッチング素子20がオフに転じる動作も同様である。従って、期間t23の間、寄生ダイオード30には順方向電流がほとんど流れず、期間t23が終了して転流側スイッチング素子24がオフに転じる時も、逆方向電流(リカバリ電流)がほとんど流れない。

【0055】

期間t23は、PWM制御回路16が主スイッチング素子14のオンのタイミングを一定間隔にしようとする動作により、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで終了する。

【0056】

スイッチング電源装置10が過電流保護動作をするときは、上記の期間t21〜t23を1周期Tとするスイッチング動作を繰り返す。このような動作により、スイッチング電流Id14のピーク値が第1基準値Ir1を超えないようにする高速制御を行い、出力電流Ioを制限し、かつ、主スイッチング素子14のオン時間を短くして出力電圧Voを低下させることによって、負荷36や装置内部の回路素子を保護することができる。

【0057】

次に、負荷36が非常に低インピーダンスの状態で故障などしたとき(出力短絡時)、第2基準値Ir2に基づく短絡保護を行う動作について説明する。短絡保護動作時の各部の動作波形は図5のタイムチャートのように表わされ、主スイッチング素子14は、期間t31〜t35を1周期Tとするスイッチング動作を繰り返す。

【0058】

なお、短絡保護動作中は、主スイッチング素子14のオン時間が非常に短くなるので、図5に示すように、転流側スイッチング素子24のゲート・ソース端子間の電圧Vg24が、全期間にわたってゲート閾値Vth24に達しない。同様に、図示しない整流側スイッチング素子20のゲート・ソース端子間電圧もゲート閾値に達しない。従って、以下に説明する短絡保護動作中は、転流側スイッチング素子24と整流側スイッチング素子20が全期間にわたってオフしている。

【0059】

期間t31に入る直前は、主スイッチング素子14がオフ、整流側の寄生ダイオード22がオフしており、転流側の寄生ダイオード30は順方向の電流Id24を流してオンしている。期間t31に入ると、駆動パルスV16がハイレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が急峻に上昇してゲート閾値Vth14を超え、主スイッチング素子14がオンに転じる。整流側の寄生ダイオード22も速やかにオンに転じ、順方向の電流を流すことができる状態になる。しかし、転流側の寄生ダイオード30は、上述したように逆回復時間が長いPN接合型のダイオードのため、速やかにオフすることができず、逆方向のリカバリ電流が流れる(リカバリ動作)。

【0060】

このリカバリ電流成分は、入力電源12、主トランス18、転流側の寄生ダイオード30、整流側の寄生ダイオード22、主トランス18、主スイッチング素子14の経路に流れ、図5の電流Id14,Id24の波形に示すように非常に急峻に増加する。リカバリ電流の経路は非常にインピーダンスが低く、主トランス18が有する小さな漏れインダクタンスや主スイッチング素子14のオン・スピード等の要因によって制限されるのみであり、電流増加の傾きが非常に急峻になる。

【0061】

主スイッチング素子14がオンすると、上記のリカバリ動作の影響で、スイッチング電流Id14が瞬時に第1基準値Ir1に達する。すると、PWM制御回路16が、図4で説明した過電流保護の動作を開始するが、駆動パルスV16のハイレベルの時間をPWM制御回路16が有する遅延時間Tmよりも短くすることはできない。従って、主スイッチング素子14のオン時間が短くならないので、スイッチング電流Id14が第1基準値Ir1を超えてさらに上昇し、遅延時間Tmが経過する前に第2基準値Ir2に達する。

【0062】

電流Id14が第2基準値Ir2になると、電流検出回路38が出力するスイッチング電流信号も上昇して第2基準電圧Vr2になる。期間t31は、可変制御回路48に入力されるスイッチング電流信号のピーク値が第2基準電圧Vr2に達したところで終了する。

【0063】

期間t32に入っても、PWM制御回路16の駆動パルスV16は、上記の遅延時間Tmの影響でハイレベルを継続し、バッファ回路44が主スイッチング素子14のゲート・ソース端子間の電圧Vg14をゲート閾値Vth14よりも十分高い電圧に保持しようとする。

【0064】

一方、可変制御回路48は、電流検出回路38が出力するスイッチング電流信号がツェナーダイオード70の電圧Vaと可変抵抗素子46のベース・エミッタ間順方向電圧Vbとの合計値である第2基準電圧Vr2を超えようとすると、ツェナーダイオード70が導通することによって可変抵抗素子46に所定のベース電流を供給し、可変抵抗素子46がコレクタ電流を流すようになって等価的にコレクタ・エミッタ間の抵抗値が小さくなり、主スイッチング素子14のゲート・ソース端子間の電圧Vg14が低下する。このとき、可変制御回路48は、可変抵抗素子46の抵抗値を低下させ、電圧Vg14がゲート閾値Vth14を下回らない範囲でゲート閾値Vth14に近い電圧になるように制御する。従って、MOS型FETである主スイッチング素子14は、所定の大きな導通抵抗をもってオンする状態になる。

【0065】

このように、期間t32では、主スイッチング素子14の導通抵抗を増加させることによって、電流Id14,Id24のピーク値を小さく抑える動作が行われる。このとき、第1抵抗68の調整により可変抵抗素子46に流れるベース電流が最適化されているので、電流Id14,Id24のピーク値が低下し、スイッチング電流信号が第2基準電圧Vr2よりも低くなり、可変制御回路48から可変抵抗素子46へのベース電流の供給が止まっても、遅延時間Tmが経過するまでの間は、可変抵抗素子46が抵抗値を低下させる動作を継続する。

【0066】

期間t32は、PWM制御回路16に第1基準電圧Vr1を超えるスイッチング電流信号が入力されてから遅延時間Tmが経過し、駆動パルスV16がローレベルに反転したところで終了する。

【0067】

期間t33に入ると、駆動パルスV16がローレベルに転じ、バッファ回路44を介して主スイッチング素子14のゲート・ソース端子間の電圧Vg14が低下してゲート閾値Vth14未満になり、主スイッチング素子14がオフに転じる。すると、電流Id14,Id24の経路が、主スイッチング素子14内部のドレイン・ソース端子間に存在する図示しない寄生コンデンサに切り替わる。整流側の寄生ダイオード22はオンを継続し、転流側の寄生ダイオード30もリカバリ動作を継続する。

【0068】

その後、転流側の寄生ダイオード30のリカバリ動作がある程度回復し、電流Id14,Id24がゼロアンペアに近くなって電圧Vd24が上昇し始めたところで期間t33が終了する。

【0069】

期間t34に入ると、主スイッチング素子14はオフを継続し、整流側の寄生ダイオード22はオンを継続し、転流側の寄生ダイオード30のリカバリ動作の回復が進んだことによって、寄生ダイオード30の両端にサージ状の電圧Vd24が発生する。このサージ状の電圧Vd24のピーク値は、期間t34が開始する時の電流Id24に大きく依存するが、上述した期間t32の動作によって電流Id24が小さく抑えられているので、電圧Vd24が危険電圧にまで上昇する心配はない。

【0070】

その後、転流側の寄生ダイオード30のリカバリ動作が回復し、平滑インダクタ26が放出する電流が順方向に流れ始めたところで期間t34が終了する。

【0071】

期間t35に入ると、主スイッチング素子14はオフを継続し、整流側の寄生ダイオードが逆方向にバイアスされてオフに転じる。そして、転流側の寄生ダイオード30に、平滑インダクタ26の励磁エネルギーが出力電流Ioとして放出される電流が順方向に流れ始め、電圧Vd24がほぼゼロボルトに低下する。この電流は、電流Id24の波形のように、時間の経過とともに電流値が所定の傾きで徐々に減少する略台形状の波形となる。この電流Id24は、平滑インダクタ26、寄生ダイオード30、負荷36及び平滑コンデンサ28の経路に流れ、概ねそのピーク値が出力電流Ioとなる。

【0072】

期間t35は、PWM制御回路16が主スイッチング素子14のオンのタイミングを一定間隔にしようとする動作により、主スイッチング素子14をオフさせるべき期間が経過し、駆動パルスV16がハイレベルに転じたところで終了する。

【0073】

スイッチング電源装置10が短絡保護動作をするときは、上記の期間t31〜t35を1周期Tとするスイッチング動作を繰り返す。このような動作により、スイッチング電流Id14のピーク値が第2基準値Ir2を超えないように制限する高速制御を行い、転流側の寄生ダイオード30に逆方向に流れるリカバリ電流を制限し、転流側スイッチング素子24のドレイン・ソース端子間の電圧Vd24が危険電圧まで上昇するのを防止する。また、他の回路素子に対しても過剰な電気的ストレスが加わらないように保護することができ、同時に出力電流Ioも制限され、故障した負荷36が焼損する事故を未然に防止することができる。

【0074】

例えば、上記実施形態のスイッチング電源装置10に可変抵抗素子46と可変制御回路48を設けていない不完全なスイッチング電源装置の場合、出力短絡時に適切な短絡保護が行われない。

【0075】

この不完全なスイッチング電源装置は、第2基準値Vr2に基づいてスイッチング電流Id14を制限する機能を有していないので、図6に示すように、期間t41に入ったときに流れ始める電流Id14,Id24が、遅延時間Tmが経過するまで増加し続ける。そして、期間t42に入って主スイッチング素子14がオフすることによって初めて電流Id14,Id24の増加が抑制され、期間t43に入る直前の電流Id14,Id24が、図5の期間t34に入る直前の電流Id14,Id24よりも大きくなってしまう。その結果、期間t43に入って寄生ダイオード30の両端に発生するサージ状の電圧Vd24が非常に高くなり、転流側スイッチング素子24に大きな電気的ストレスが加わることになる。

【0076】

この場合、転流側スイッチング素子24が故障しないように、定格電圧の高いMOS型FETを選択する必要がある。しかし、MOS型FETは定格電圧が高いものほど導通抵抗が大きくなるという傾向があるので、定格電圧の高いMOS型FETを選択することによって通常動作中の整流損失が大きくなり、外形が大きく高価なMOS型FETを選択しなければならなくなる。

【0077】

以上説明したように、スイッチング電源装置10は、主スイッチング素子14に流れるスイッチング電流Id14を第1基準値Ir1に基づいて制限する過電流保護機能と、第1基準値Ir1よりも大きい第2基準値Ir2に基づいて高速に制限する短絡保護機能とを備えている。従って、負荷36が故障して出力が短絡し、転流側スイッチング素子24の同期整流動作が停止し、転流側の寄生ダイオード30にリカバリ電流Id24が流れた時、スイッチング電流Id14及びリカバリ電流Id24を小さく抑え、転流側スイッチング素子24のドレイン・ソース端子間に過大な電圧Vd24が発生するのを防止することができる。従って、転流側スイッチング素子24として、定格電圧が低く導通抵抗の小さいMOS型FETを選択することができ、低損失化を図ることができる。

【0078】

また、可変抵抗素子46及び可変制御回路48は、NPNトランジスタ、ツェナーダイオード、抵抗という3点の部品を組み合わせてシンプルに構成することができ、狭いスペースにも容易に実装することができる。

【0079】

次に、上記のスイッチング電源装置10の第1変形例について、図7に基づいて説明する。ここで、上記実施形態と同様の構成は、同一の符号を付して説明を省略する。第1変形例では、上記のPWM制御回路16に代えて、スロープ補正回路80を有したPWM制御回路82が設けられ、上記の電流検出回路38に代えて、電流検出抵抗64を主スイッチング素子14のソース端子側に挿入することによって電流トランス60等を省略した電流検出回路84が設けられている。さらに、上記のバッファ回路44が省略され、上記の可変抵抗素子46のコレクタ端子側に抵抗46aが挿入され、上記の可変制御回路48の第1抵抗68と並列に電圧保持コンデンサ90が接続されている。その他の構成は、上記実施形態と同様である。

【0080】

例えば、出力電力の小さいスイッチング電源装置や高入力電圧仕様のスイッチング電源装置の場合、主スイッチング素子14に流れるスイッチング電流Id14が小さいので、電流検出抵抗64に直接スイッチング電流Id14を流しても大きな損失が発生しない。従って、電流検出回路84を使用して構成を簡単化することができる。また、主スイッチング素子14として、ゲート・ソース端子間の駆動が容易な定格電流の小さいMOS型FETを選択することができるので、バッファ回路44を省略することができる。

【0081】

PWM制御回路82のスロープ補正回路80は、誤差信号ΔVoに基づくカレントモード式のパルス幅変調を行うときに問題となる電流発振現象を防止するために設けられたもので、図7に示すように、スイッチング周期に同期してスイッチ86がオン・オフすることによって、比較器42の反転入力端子と電流検出回路84の出力との間に挿入した抵抗88の両端にノコギリ波状の補正電圧Vdを発生させる動作を行う。

【0082】

スロープ補正回路80を設けることで、過電流保護動作及び短絡保護動作に関して以下のような差異が生じる。上記実施形態の場合は、第1基準電圧Vr1が、ツェナーダイオード66が導通した時のツェナー電圧で定まる一定の電圧であったが、第1変形例の場合は、第1基準電圧Vr1が、ツェナーダイオード66が導通した時のツェナー電圧Vcから補正電圧Vdを差し引いた電圧(時間と共に補正電圧Vdの範囲で変化する電圧)になる。しかしながら、第1基準電圧Vr1を第2基準電圧Vr2を超えない範囲に設定することにより、図5、図6を用いて説明した上記実施形態の動作と同様の動作を行い、スイッチング電流Id14を制限することができる。

【0083】

上記実施形態では、出力短絡時、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、遅延時間Tmが経過するまでの間、可変抵抗素子46が小さな抵抗値の状態を維持し、かつ遅延時間Tmが経過した後、速やかに可変抵抗素子46の抵抗値を大きく変化させる、という動作を第1抵抗68の調整により実現していた。しかし、第1抵抗68だけでは調整が困難な場合は、図7の第1変形例のように、可変抵抗素子46のコレクタ端子側に所定の抵抗46aを挿入したり、第1抵抗68と並列に電圧保持コンデンサ90を接続したりすることにより、調整を容易にすることができる。

【0084】

次に、上記のスイッチング電源装置10の第2変形例について、図8に基づいて説明する。ここで、上記実施形態と同様の構成は、同一の符号を付して説明を省略する。第2変形例では、上記のPWM制御回路16に代えて、誤差信号ΔVoに基づくボルテージモード式のパルス幅変調を行う駆動パルス発生回路91と、反転入力端子に電流検出回路96のスイッチング電流信号が入力され、非反転入力端子に負の第1基準電圧Vr1が入力される比較器42とで成るPWM制御回路92とが設けられている。また、上記の可変制御回路48のツェナーダイオード70が第2抵抗94に置き換えられ、第1抵抗68と並列に電圧保持コンデンサ90が接続されている。また、上記実施形態の電流検出回路38に代えて第1変形例の電流検出回路84が設けられ、電流検出回路84と直列に、負のスイッチング電流信号を発生し比較器42の反転入力端子に向けて出力する電流検出回路96が新たに設けられている。その他の構成は、上記実施形態と同様である。

【0085】

第2変形例のPWM制御回路92は、比較器42の非反転入力端子に負の第1基準電圧Vr1が入力されているので、その反転入力端子に負のスイッチング電流信号を入力しなければならない。そこで、電流検出回路84とは別に、スイッチング電流Id14に比例した負のスイッチング電流信号を出力する電流検出回路96が設けられている。電流検出回路96は、スイッチング電流Id14が流れて負の電圧が発生する電流検出抵抗98と、その負電圧を分圧する分圧抵抗100a,100bと、分圧抵抗100bに発生する負のスイッチング電流信号からスパイク成分を除去するコンデンサ102で構成されている。このコンデンサ102は、可変抵抗素子46の抵抗値を高速に変化させる動作には影響しない。また、可変抵抗素子46の抵抗値制御の調整のしやすさを考慮し、可変制御回路48に第2抵抗94が設けられている。

【0086】

このように構成の一部が変更された第2変形例においても、過電流保護動作及び短絡保護動作に関しては、図5、図6を用いて説明した上記実施形態の動作と同様の動作を行い、スイッチング電流Id14を制限することができる。

【0087】

なお、この発明のスイッチング電源装置は、上記実施形態及び変形例に限定されるものではない。例えば、上記実施形態及び変形例では、出力短絡時、スイッチング電流信号のピーク値が第2基準電圧Vr2に達した後、遅延時間Tmが経過するまでの間、可変抵抗素子46が小さな抵抗値の状態を維持し、かつ遅延時間Tmが経過した後、速やかに可変抵抗素子46の抵抗値を大きく変化させる、という動作を行う構成になっているが、遅延時間Tmが経過する前に可変抵抗素子46の抵抗値が大きく変化するよう設定してもよい。この場合、遅延時間Tmの間に主スイッチング素子が複数回オン・オフし、主スイッチンング素子14のクロス損失が増加する可能性がある。しかし、遅延時間Tmというごく短い期間だけの動作であり、主スイッチング素子14の損失増加はさほど大きくない。従って、主スイッチング素子14が故障する心配がなければ、このような動作を許容することができる。

【0088】

また、同期整流駆動回路は、上記実施形態のような主トランスの巻線に発生する電圧を利用した巻線駆動方式に限定するものではなく、出力短絡時など主スイッチング素子のオン時間が一定以下に短くなると、転流側スイッチング素子をオフ状態に保持する機能を備えたものであれば、例えば、転流側スイッチング素子を、主トランスの2次側に設けた専用ICを用いて駆動する方式や、PWM制御回路の駆動パルスを駆動トランスを介して転流側スイッチング素子に伝達して駆動する方式などであってもよい。

【符号の説明】

【0089】

10 スイッチング電源装置

14 主スイッチング素子

16,82,92 PWM制御回路

18 主トランス

20 整流側スイッチング素子

24 転流側スイッチング素子

22,30 寄生ダイオード

32 同期整流駆動回路

34 平滑回路

38,84,96 電流検出回路

46 可変抵抗素子

48 可変制御回路

68 第1抵抗

70 ツェナーダイオード

90 電圧保持コンデンサ

94 第2抵抗

Ir1 第1基準値

Ir2 第2基準値

Vr1 第1基準電圧

Vr2 第2基準電圧

【特許請求の範囲】

【請求項1】

入力電源と直列に接続されたN−chのMOS型FETであって、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、

前記交流電圧が印加される1次巻線及びそれに磁気結合した2次巻線を有する主トランスと、

一端が前記2次巻線の一端に接続され、前記主スイッチング素子がオンの期間中に前記2次巻線に発生した電圧を整流する整流側スイッチング素子と、

前記2次巻線の他の一端と前記整流側スイッチング素子の他の一端にドレイン端子とソース端子が各々接続され、前記主スイッチング素子がオフの期間中にオンして前記ソース端子から前記ドレイン端子の向きに電流を流すN−chのMOS型FETである転流側スイッチング素子と、

前記転流側スイッチング素子の内部のドレイン・ソース端子間に形成された寄生ダイオードと、

前記転流側スイッチング素子をオン・オフ駆動する回路であって、前記主スイッチング素子のオン時間が一定以下に短くなると、前記転流側スイッチング素子をオフ状態に保持する同期整流駆動回路と、

平滑チョーク及び平滑コンデンサで成るローパスフィルタであって、前記転流側スイッチング素子のドレイン・ソース端子間にその入力側が接続され、前記平滑コンデンサ両端に直流の出力電圧を生成して負荷に電力を供給する平滑回路と、

前記主スイッチング素子に流れるスイッチング電流を検出する電流検出回路と、

前記出力電圧の誤差信号に基づいてパルス幅変調した矩形の駆動パルスを出力して前記主スイッチング素子のオン・オフを制御すると共に、前記電流検出回路の出力信号を受け前記スイッチング電流のピーク値が第1基準値に達すると前記主スイッチング素子をオフさせるため前記駆動パルスをローレベルにするパルス・バイ・パルス式の過電流保護動作を行うPWM制御回路と、を備えたシングルエンディッド・フォワード型のスイッチング電源装置において、

前記主スイッチング素子のゲート・ソース端子間に接続された可変抵抗素子と、前記電流検出回路の出力信号に基づいて前記可変抵抗素子の抵抗値を変化させる可変制御回路とを備え、

前記可変制御回路は、前記電流検出回路の出力信号を受けスイッチング周期ごとに前記スイッチング電流のピーク値と前記第1基準値よりも高い第2基準値とを比較し、前記スイッチング電流が前記第2基準値に達すると前記可変抵抗素子の抵抗値を低下させ、前記主スイッチング素子のゲート・ソース端子間電圧を上げないように制御することによって前記スイッチング電流のピーク値の上昇を抑制し、前記転流側スイッチング素子の寄生ダイオードのリカバリ電流のピーク値を制限することを特徴とするスイッチング電源装置。

【請求項2】

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記可変抵抗素子の抵抗値を低下させる動作を継続する請求項1記載のスイッチング電源装置。

【請求項3】

前記抵抗値可変素子は、コレクタ端子が前記主スイッチング素子のゲート端子側に接続され、エミッタ端子が前記主スイッチング素子のソース端子に接続されたNPNトランジスタであり、

前記可変制御回路は、前記NPNトランジスタのベース電流を制御することによって前記NPNトランジスタのコレクタ・エミッタ端子間の導通抵抗を変化させる請求項1又は2記載のスイッチング電源装置。

【請求項4】

前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、

前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、カソード端子が前記電流検出回路の出力端に接続され、アノード端子が前記NPNトランジスタのベース端子に接続されたツェナーダイオードとで構成されている請求項3記載のスイッチング電源装置。

【請求項5】

前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、

前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、両端が前記電流検出回路の出力端と前記NPNトランジスタのベース端子の間に接続された第2抵抗とで構成されている請求項3記載のスイッチング電源装置。

【請求項6】

前記第1抵抗と並列に電圧保持コンデンサが接続され、

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記NPNトランジスタのベース電流を前記電圧保持コンデンサから供給することによって、前記可変抵抗素子の抵抗値を低下させる動作を継続する請求項4又は5記載のスイッチング電源装置。

【請求項1】

入力電源と直列に接続されたN−chのMOS型FETであって、所定のスイッチング周波数でオン・オフすることによって入力電圧を断続し交流電圧を発生させる主スイッチング素子と、

前記交流電圧が印加される1次巻線及びそれに磁気結合した2次巻線を有する主トランスと、

一端が前記2次巻線の一端に接続され、前記主スイッチング素子がオンの期間中に前記2次巻線に発生した電圧を整流する整流側スイッチング素子と、

前記2次巻線の他の一端と前記整流側スイッチング素子の他の一端にドレイン端子とソース端子が各々接続され、前記主スイッチング素子がオフの期間中にオンして前記ソース端子から前記ドレイン端子の向きに電流を流すN−chのMOS型FETである転流側スイッチング素子と、

前記転流側スイッチング素子の内部のドレイン・ソース端子間に形成された寄生ダイオードと、

前記転流側スイッチング素子をオン・オフ駆動する回路であって、前記主スイッチング素子のオン時間が一定以下に短くなると、前記転流側スイッチング素子をオフ状態に保持する同期整流駆動回路と、

平滑チョーク及び平滑コンデンサで成るローパスフィルタであって、前記転流側スイッチング素子のドレイン・ソース端子間にその入力側が接続され、前記平滑コンデンサ両端に直流の出力電圧を生成して負荷に電力を供給する平滑回路と、

前記主スイッチング素子に流れるスイッチング電流を検出する電流検出回路と、

前記出力電圧の誤差信号に基づいてパルス幅変調した矩形の駆動パルスを出力して前記主スイッチング素子のオン・オフを制御すると共に、前記電流検出回路の出力信号を受け前記スイッチング電流のピーク値が第1基準値に達すると前記主スイッチング素子をオフさせるため前記駆動パルスをローレベルにするパルス・バイ・パルス式の過電流保護動作を行うPWM制御回路と、を備えたシングルエンディッド・フォワード型のスイッチング電源装置において、

前記主スイッチング素子のゲート・ソース端子間に接続された可変抵抗素子と、前記電流検出回路の出力信号に基づいて前記可変抵抗素子の抵抗値を変化させる可変制御回路とを備え、

前記可変制御回路は、前記電流検出回路の出力信号を受けスイッチング周期ごとに前記スイッチング電流のピーク値と前記第1基準値よりも高い第2基準値とを比較し、前記スイッチング電流が前記第2基準値に達すると前記可変抵抗素子の抵抗値を低下させ、前記主スイッチング素子のゲート・ソース端子間電圧を上げないように制御することによって前記スイッチング電流のピーク値の上昇を抑制し、前記転流側スイッチング素子の寄生ダイオードのリカバリ電流のピーク値を制限することを特徴とするスイッチング電源装置。

【請求項2】

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記可変抵抗素子の抵抗値を低下させる動作を継続する請求項1記載のスイッチング電源装置。

【請求項3】

前記抵抗値可変素子は、コレクタ端子が前記主スイッチング素子のゲート端子側に接続され、エミッタ端子が前記主スイッチング素子のソース端子に接続されたNPNトランジスタであり、

前記可変制御回路は、前記NPNトランジスタのベース電流を制御することによって前記NPNトランジスタのコレクタ・エミッタ端子間の導通抵抗を変化させる請求項1又は2記載のスイッチング電源装置。

【請求項4】

前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、

前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、カソード端子が前記電流検出回路の出力端に接続され、アノード端子が前記NPNトランジスタのベース端子に接続されたツェナーダイオードとで構成されている請求項3記載のスイッチング電源装置。

【請求項5】

前記電流検出回路は、前記スイッチング電流を電圧信号に変換して出力し、

前記可変制御回路は、両端が前記NPNトランジスタのベース・エミッタ端子間に接続された第1抵抗と、両端が前記電流検出回路の出力端と前記NPNトランジスタのベース端子の間に接続された第2抵抗とで構成されている請求項3記載のスイッチング電源装置。

【請求項6】

前記第1抵抗と並列に電圧保持コンデンサが接続され、

前記可変制御回路は、前記スイッチング電流のピーク値が前記第2基準値に達した後、前記PWM制御回路の過電流保護動作の遅延時間が経過するまでの期間、前記NPNトランジスタのベース電流を前記電圧保持コンデンサから供給することによって、前記可変抵抗素子の抵抗値を低下させる動作を継続する請求項4又は5記載のスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−157191(P2012−157191A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−15165(P2011−15165)

【出願日】平成23年1月27日(2011.1.27)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年1月27日(2011.1.27)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

[ Back to top ]