スイッチング電源装置

【課題】主スイッチング素子のZVSが可能であり、特定の回路素子に過大な電気的ストレスが加わることなく安全性の高い小型のスイッチング電源装置を提供する。

【解決手段】フルブリッジ構成の主スイッチング素子18a,18b,20a,20bから成る第一アーム18と第二アーム20をオンオフ駆動し、フェイズシフト制御を行うスイッチング制御回路44を備える。トランス22の一次巻線22aと直列の位置に挿入されトランス22の直流偏磁を抑制する第一コンデンサ24を備える。一次巻線22a及び第一コンデンサ24と直列であって、一端が第二アーム20の中点20cに接続された共振インダクタ26を備える。共振インダクタ26の一次巻線22a側の一端に、第一及び第二回生ダイオード28a,28bを備える。スイッチング制御回路44は、第二アーム20のターンオン又はターンオフによってトランス22aの電圧印加を停止させる。

【解決手段】フルブリッジ構成の主スイッチング素子18a,18b,20a,20bから成る第一アーム18と第二アーム20をオンオフ駆動し、フェイズシフト制御を行うスイッチング制御回路44を備える。トランス22の一次巻線22aと直列の位置に挿入されトランス22の直流偏磁を抑制する第一コンデンサ24を備える。一次巻線22a及び第一コンデンサ24と直列であって、一端が第二アーム20の中点20cに接続された共振インダクタ26を備える。共振インダクタ26の一次巻線22a側の一端に、第一及び第二回生ダイオード28a,28bを備える。スイッチング制御回路44は、第二アーム20のターンオン又はターンオフによってトランス22aの電圧印加を停止させる。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、フェイズシフト制御により出力電圧を安定化するフルブリッジ型のスイッチング電源装置に関する。

【背景技術】

【0002】

従来から、1kWを超えるような電力を取り扱うスイッチング電源装置では、高効率化やスイッチング周波数の固定化などの観点から、フェイズシフト制御によって出力電圧を安定化するフルブリッジ型の電源回路が使用されている。

【0003】

この種のスイッチング電源装置として、例えば、特許文献1に従来技術として開示されているように、トランスの一次巻線に接続された主スイッチング素子に流れるスイッチング電流を共振(いわゆる電流共振)させて電力変換を行い、フェイズシフト制御によって出力電圧を安定化するスイッチング電源装置がある。スイッチング電流を共振させる共振回路は、共振インダクタ及び共振コンデンサの直列回路で構成され、トランスの一次巻線と直列の位置に挿入されている。

【0004】

また、特許文献2に開示されたDC−DCコンバータは、トランスの一次巻線と直列の位置にゼロ電圧スイッチング(以下、ZVSと称す。)用の共振インダクタが挿入され、共振インダクタのエネルギー放出動作によって主スイッチング素子の両端に在るコンデンサの電荷の放出を補助し、ZVS動作を可能にしたものである。このDC−DCコンバータは、トランスの一次巻線及び共振インダクタの接続点と入力電源の両端との間に第1及び第2の回生ダイオードが設けられ、トランスの二次巻線に接続された整流ダイオードの両端に発生するサージ電圧を低減させている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−197711号公報

【特許文献2】国際公開WO2007/000830号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の従来技術に係るスイッチング電源装置の場合、出力電流の状態によっては主スイッチング素子のZVS動作が不可能であり、主スイッチング素子のスイッチング損失が増加して効率低下を招くという問題がある。また、この問題を解決するため、特許文献1の発明に係るスイッチング電源装置では、2つのコンデンサと補助共振インダクタを用いた補助共振回路が設けられている。しかし、この補助共振回路を付加することによって、比較的外形の大きなインダクタ素子が少なくとも2つ(共振インダクタ及び補助共振インダクタ)必要になるので、実装スペースやコストの面で不利である。

【0007】

また、特許文献2のDC−DCコンバータの場合、入力電源が投入された起動時や出力電流が急峻に変化した時に、トランスが過渡的に直流偏磁して磁気飽和し、主スイッチング素子等に過大な電気的ストレスが加わって回路素子が破損するおそれがある。従って、磁気飽和に対して余裕を持たせるため、トランスの外形を大きくする必要があった。また、回生ダイオードに流れる電流の大小については特に考慮されておらず、共振インダクタを接続する位置によっては、回生ダイオードに過大な電流が流れ破損する心配があった。

【0008】

この発明は、上記背景技術に鑑みて成されたものであり、主スイッチング素子のZVS動作を確実に行うことができ、特定の回路素子に過大な電気的ストレスが加わることなく安全性の高い小型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

この発明は、ハイサイド側及びグランド側に各々設けられた主スイッチング素子の直列回路で構成され、その両端に直流入力源が接続される第一アームと、ハイサイド側及びグランド側に各々設けられた他の主スイッチング素子の直列回路で構成され、前記第一のアームに並列接続された第二アームと、一次巻線及び二次巻線を有し、前記一次巻線が前記第一アームの中点と前記第二アームの中点との間に設けられたトランスと、前記トランスの前記二次巻線に接続され、前記二次巻線に発生した交流電圧を直流の出力電圧に変換して出力する整流平滑回路と、前記各主スイッチング素子をオンオフ駆動することによって、前記一次巻線に入力電圧が正方向に印加される第一の期間、入力電圧が印加されない第二の期間、負方向に印加される第三の期間、及び再度電圧が出力されない第四の期間を1周期とするフェイズシフト制御を行い、前記整流平滑回路の出力電圧を安定化するスイッチング制御回路と、を備えたフルブリッジ型のスイッチング電源装置であって、前記一次巻線と直列の位置に挿入され、前記トランスの直流偏磁を抑制する第一コンデンサと、前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入された共振インダクタと、前記共振インダクタの前記一次巻線側の一端にアノード端子が接続され、前記第一及び第二アームのハイサイド側の接続点にカソード端子が接続された第一回生ダイオードと、前記第一及び第二アームのグランド側の接続点にアノード端子が接続され、前記共振インダクタの前記一次巻線側の一端にカソード端子が接続された第二回生ダイオードとを備え、前記スイッチング制御回路は、前記第一アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第一及び第三の期間を開始させ、前記第二アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第二及び第四の期間を開始させる制御を行うスイッチング電源装置である。

【0010】

前記第一及び第二アームが有する前記主スイッチング素子はN−chのMOS型FETで構成され、個々のドレイン・ソース間に、並列コンデンサとソース端子からドレイン端子の向きに導通可能な並列ダイオードとが設けられ、さらに、前記スイッチング制御回路は、前記第一アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせ、前記第二アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせる制御を行うようにしてもよい。

【0011】

前記トランスの前記一次及び二次巻線は、前記一次巻線側からみた漏れインダクタンスが、前記共振インダクタのインダクタンスよりも小さくなるように密に磁気結合していることが好ましい。また、前記第一及び第二回生ダイオードの中点と前記共振インダクタの前記一次巻線側の一端との間に、前記第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサが挿入されていてもよい。

【0012】

前記整流平滑回路は、全波整流方式、センタタップ方式、又はカレントダブラ方式の構成を備えている。また、前記整流平滑回路が有する整流部は、MOS型FETによる同期整流を行う構成にしてもよい。

【発明の効果】

【0013】

この発明のスイッチング電源装置は、共振インダクタの動作によって主スイッチング素子のZVS動作を確実に行うことが可能であり、さらにトランスの直流偏磁を抑制する第一コンデンサが設けられているので、入力投入などの過渡時においてもトランスの直流偏磁による磁気飽和を容易に回避し、各回路素子が破損するのを防止することができる。

【0014】

また、第一及び第二回生ダイオードが行う回生動作によって整流平滑回路の整流素子に発生するサージ電圧が低く抑えられるので、整流素子として導通抵抗又は電圧降下の小さい低耐圧半導体を選定することが可能になり、電源効率を向上させることができる。また、共振インダクタを、前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入することによって、第一及び第二回生ダイオードに過大な電流が流れなくなるので安全性も高いものである。

【図面の簡単な説明】

【0015】

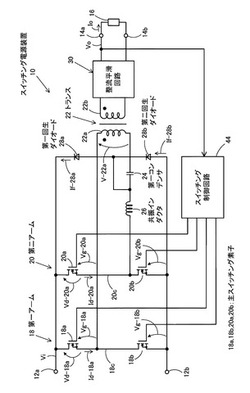

【図1】この発明のスイッチング電源装置の第一実施形態を示す回路図である。

【図2】第一コンデンサを設ける位置の各変形例を示す回路図(a),(b)である。

【図3】第一実施形態のスイッチング電源装置の整流平滑回路の構成を示す回路図である。

【図4】第一実施形態のスイッチング電源装置の定常動作を説明するタイムチャートである。

【図5】第一実施形態のスイッチング電源装置の整流ダイオード38b両端の電圧波形(a)、第一及び第二回生ダイオードを設けない場合の整流ダイオード38b両端の電圧波形(b)である。

【図6】共振インダクタが不適切な位置に挿入された比較例のスイッチング電源装置の回路図である。

【図7】図6のスイッチング電源装置の定常動作を説明するタイムチャートである。

【図8】第一実施形態のスイッチング電源装置の整流平滑回路の各変形例を示す回路図(a),(b),(c)である。

【図9】第一実施形態のスイッチング電源装置に追加する第二コンデンサを示す回路図である。

【発明を実施するための形態】

【0016】

以下、この発明のスイッチング電源装置の第一実施形態について、図面に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1に示すように、入力端子12a,12b間に入力された直流の入力電圧Viを直流の出力電圧Voに変換し、出力端子14a,14b間に接続された負荷16に、出力電圧Vo及び電流Ioを供給する電源装置である。ここで、入力及び出力端子12b,14bは、入力及び出力電圧Vi,Voのグランド側の電位であり、入力及び出力端子12a,14aがプラス側の電位である。

【0017】

入力端子12a,12b間には、ハイサイド側及びグランド側の主スイッチング素子18a,18bの直列回路である第一アーム18が接続され、さらに第一アーム18と並列に、ハイサイド側及びグランド側の主スイッチング素子20a,20bの直列回路である第二アーム20が接続されている。ここでは、主スイッチング素子18a,18b,20a,20bとしてN−chのMOS型FETが使用され、主スイッチング素子18a,20aのドレイン端子が入力端子12aに、主スイッチング素子18b,20bのソース端子が入力端子12bに各々接続されている。そして、主スイッチング素子18aのソース端子と主スイッチング素子18bのドレイン端子との接続点が第一アーム18の中点(以下、第一中点18cと称す。)であり、主スイッチング素子20aのソース端子と主スイッチング素子20bのドレイン端子との接続点が第二アーム20の中点20c(以下、第二中点20cと称す。)である。また、主スイッチング素子18a,18b,20a,20bの各チップ内部には、図示しない回路素子であって、ソース端子からドレイン端子の向きの寄生ダイオード、及びそれと並列の寄生コンデンサが形成されている。

【0018】

なお、この実施形態では、各主スイッチング素子のドレイン・ソース間に設ける並列ダイオードと並列コンデンサが、寄生ダイオードと寄生コンデンサで構成されているが、さらに外部に高性能のダイオード素子を接続したり、静電容量調整用のコンデンサ素子を接続して構成してもよい。

【0019】

第一中点18cと第二中点20cの間には、トランス22の一次巻線22aが設けられ、ドットが付された一端が第一中点18cに接続されている。トランス22は、一次巻線22aと二次巻線22bとを有し、それらは互いに密に磁気結合しており、一次巻線22a側から見た漏れインダクタンスは、後述する共振インダクタ26のインダクタンスよりも十分に小さい。

【0020】

一次巻線22aの第二中点20c側の一端には、第一コンデンサ24の一端が接続され、第一コンデンサ24の他の一端と第二中点20cとの間に共振インダクタ26が接続されている。第一コンデンサ24は、トランス22の直流偏磁を抑制するコンデンサであり、一定以上の大きい容量値に設定され、スイッチング周波数におけるインピーダンスが十分小さい。従って、主スイッチング素子18a,18b,20a,20bに流れるスイッチング電流や一次巻線22aに発生する電圧の波形の形状に与える影響は小さい。共振インダクタ26は、自身のエネルギー放出動作によって主スイッチング素子18a,18b,20a,20bの両端にある図示しない寄生コンデンサの電荷放出を補助し、ZVS動作を可能にするものである。

【0021】

この一次巻線22a、第一コンデンサ24及び共振インダクタ26から成る直列回路は、共振インダクタ26の一端が第二中点20cに接続されるように構成されていればよく、例えば、図2(a)に示すように、一次巻線22aと第一コンデンサ24の配置を逆にしたり、図2(b)に示すように、複数に分割した第一コンデンサ24を一次巻線22aの両側に配置したりする構成にすることも可能である。

【0022】

共振インダクタ26の一端には、第一及び第二回生ダイオード28a,28bが接続されている。第一回生ダイオード28aは、共振インダクタ26の一次巻線22a側の一端にアノード端子が接続され、第一及び第二アーム18,20のハイサイド側の接続点にカソード端子が接続されている。第二回生ダイオード28bは、共振インダクタ26の一次巻線22a側の一端にカソード端子が接続され、第一及び第二アーム18,20のグランド側の接続点にアノード端子が接続されている。

【0023】

トランス22の二次巻線22bの両端に、二次巻線22bに発生する交流電圧を直流の出力電圧Voに変換して出力端子14a,14bに出力する整流平滑回路30が設けられている。整流平滑回路30は、図3に示すように全波整流方式の構成を有し、整流部32及び平滑部34で構成されている。整流部32は、二次巻線22bのドットが付された端子にアノード端子及びカソード端子が各々接続された整流ダイオード36a,36bと、二次巻線22bの他の一端にアノード端子及びカソード端子が各々接続された整流ダイオード38a,38bとで構成されている。整流ダイオード36a,38aはカソード端子同士が接続され、整流ダイオード36b,38bはアノード端子同士が接続され、当該2つの接続点の間に、二次巻線22aの交流電圧を全波整流した波形が出力される。平滑部34は、平滑インダクタ40及び平滑コンデンサ42で構成されたローパスフィルタであり、整流部32が出力した全波整流波形を平滑して直流の出力電圧Voを出力する。

【0024】

主スイッチング素子18a,18b,20a,20bは、スイッチング制御回路44によってオンオフ駆動される。スイッチング制御回路44は、出力電圧Voに基づき、時比率が約50%で個々に位相が異なる4種類の駆動パルスを生成し、主スイッチング素子18a,18b,20a,20bの駆動端子に向けて出力する。そして、4つの主スイッチング素子を互いに異なる位相でオンオフさせることによって、一次巻線22aに入力電圧Viが正方向(ドットを付した側が高電位)に印加される第一の期間T11、入力電圧Viが印加されない第二の期間T12、負方向(ドットと反対側が高電位)に印加される第三の期間T13、及び再度電圧が出力されない第四の期間T14を設け、期間T11〜T14を1周期とする一定周波数のフェイズシフト制御を行い、出力電圧Voを安定化する。このとき、スイッチング制御回路44は、第一アーム18側の主スイッチング素子18a,18bのターンオン又はターンオフによって第一及び第三の期間T11,T13を開始させ、第二アーム20側の主スイッチング素子20a,20bのターンオン又はターンオフによって第二及び第四の期間T12,T14を開始させる制御を行う。

【0025】

次に、スイッチング電源装置10の定常動作について、図4のタイムチャートに基づいて説明する。ここで、定常動作とは、入力端子12a,12b間に入力電圧Viが投入された後ある程度の時間が経過し、負荷16に一定の出力電圧Vo及び電流Ioを安定的に供給している状態をいう。また、図4において、電圧Vg−−18a,Vg−18b,Vg−20a,Vg−20bは、それぞれ主スイッチング素子18a,18b,20a,20bの駆動端子に印加される駆動パルスであり、駆動パルスを受けた各主スイッチング素子は、ハイレベルのときにオンし、ローレベルのときにオフする。電圧V−22aは、トランス22の一次巻線22aの電圧(ドットが付されていない端子が基準電位)である。電圧Vd−18a,Vd−20aは、主スイッチング素子18a,20aのドレイン・ソース間の電圧(ソース端子が基準電位)であり、電流Id−18a,Id−20aは、主スイッチング素子18a,20aに流れるスイッチング電流(ドレイン端子からソース端子の向きが正方向)である。電圧Vf−38b,Vf−36bは、整流ダイオード38b,36bの両端電圧(アノード端子が基準電位)であり、電流If−38b,If−36bは、整流ダイオード38b,36bに流れる電流(アノード端子からカソード端子の向きが正方向)である。電流If−28a,If−28bは、第一及び第二回生ダイオード28a,28bに流れる回生電流(アノード端子からカソード端子の向きが正方向)である。

【0026】

第一の期間T11は、主スイッチング素子18a,18b,20a,20bは、各々オン、オフ、オフ、オンの状態である。このとき、第一コンデンサ24と共振インダクタ26のインピーダンスが一次巻線22a両端のインピーダンスよりも十分小さいので、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が正方向に印加される。

【0027】

期間T11に移行した直後のごく短い期間に行われるZVS動作については後述するが、それ以降の期間は、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20b、入力端子12bの経路に流れる。このスイッチング電流は、電流Id−18a,If−38bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに増加する波形となり、負荷16に出力電流Ioを供給すると同時に、平滑インダクタ40及び共振インダクタ26に励磁エネルギーを蓄積する。また、整流ダイオード36b,38aはオフしており、電圧Vf−36bの波形に示す電圧、すなわち二次巻線22bにドットの向きに発生する一定電圧が印加される。また、第一回生ダイオード28aの両端にはほぼ入力電圧Viが逆方向に印加され、第二回生ダイオード28bの両端は電位差がほぼゼロになるので、電流If−28a,If−28bは流れない。

【0028】

第二の期間T12になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オン、オフの状態になる。期間T11から期間T12に移行する時、スイッチング制御回路44は、まず主スイッチング素子20bをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子20aをターンオンさせることによって、主スイッチング素子20aのZVS動作を実現する。

【0029】

期間T11の間、主スイッチング素子20aの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間12に移行する時、まず主スイッチング素子20bがターンオフすることによって、共振インダクタ26の励磁エネルギーを放出する電流が、共振インダクタ26、当該寄生コンデンサ、主スイッチング素子18a、一次巻線22a、第一コンデンサ24の経路に流れ始める。この電流により当該寄生コンデンサが放電され、主スイッチング素子20aの電圧Vd−20aが低下する。そして、期間Tdが経過して電圧Vd−20aがほぼゼロボルトになった時に主スイッチング素子20aがターンオンする。この動作により、主スイッチング素子20aのZVS動作が行われる。 期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出する電流が、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36aの経路に流れる。この電流は、電流Id−18a,Id−20a,If−38bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに減少する波形となり、負荷16に出力電流Ioを供給する。また、整流ダイオード36b,38aにはほとんど電流が流れず、電圧Vf−36bの波形に示すように、両端の電位差もほぼゼロになる。

【0030】

このとき、共振インダクタ26は、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に、第一中点18c側の一端から第二中点20c側一端の向きに僅かな電圧が発生し、第一回生ダイオード28aの両端に逆電圧が印加される。また、第二回生ダイオード28bの両端にはほぼ入力電圧Viが逆方向に印加される。従って、電流If−28a,If−28bは流れない。

【0031】

第三の期間T13になると、主スイッチング素子18a,18b,20a,20bが、各々オフ、オン、オン、オフの状態になる。期間T12から期間T13に移行する時、スイッチング制御回路44は、まず主スイッチング素子18aをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子18bをターンオンさせることによって、主スイッチング素子18bのZVS動作を実現する。

【0032】

期間T12の間、主スイッチング素子18bの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間13に移行する時、まず主スイッチング素子18aがターンオフすることによって、共振インダクタ26の励磁エネルギーを放出する電流が、共振インダクタ26、主スイッチング素子20a、入力端子12a、直流入力電源、入力端子12b、当該寄生コンデンサ、一次巻線22a、第一コンデンサ24の経路に流れ始め、この電流により当該寄生コンデンサが放電され、主スイッチング素子18bの両端電圧が低下する。そして、期間Tdが経過して両端電圧がほぼゼロボルトになった時に主スイッチング素子18bがターンオンする。このような動作により、主スイッチング素子18bのZVS動作が安定に行われる。

【0033】

期間Tdが経過すると、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が負方向に印加される。すると、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子20a、共振インダクタ26、第一コンデンサ24、一次巻線22a、二次巻線22b、整流ダイオード38a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード36b、二次巻線22b、一次巻線22a、主スイッチング素子18b、入力端子12bの経路に流れ始める。このスイッチング電流は、電流Id−20a,If−36bの波形に示すように急峻な傾きで増加し、共振インダクタ26に励磁エネルギーを蓄積する。

【0034】

一方、整流ダイオード38bは、電流If−38bが急峻な傾きでゼロアンペアまで減少してオフし、その両端に電圧Vf−38bの波形に示す電圧、すなわち二次巻線22bにドットと反対の向きに発生する一定電圧が印加される。このとき、電圧Vf−38bに大きなサージ電圧が発生しないのは、第一回生ダイオード28aの働きによる。

【0035】

仮に第一回生ダイオード28aが設けられていないとすると、電圧Vf−38bが一定電圧まで上昇すると、整流ダイオード38bの図示しない寄生容量と共振インダクタ26との間の共振によるリンギングが起こり、図5(b)に示すように、大きなサージ電圧が発生する。このサージ電圧は、整流ダイオード38bにリカバリ電流が生じやすいファストリカバリダイオードを用いた場合に特に大きくなり、リカバリ電流がほとんど生じないショットキバリアダイオード等を用いた場合でも発生する。しかし、スイッチング電源装置10は、第一回生ダイオード28aが設けられているので、電圧Vf−38bが一定電圧(入力電圧Viをトランス22の巻数比倍した電圧)を超えようとし、一次巻線22aの電圧V−22aも入力電圧Viを超えようとすると、第一回生ダイオード28aが導通し、直流入力電源が一次巻線22aの両端に並列接続された状態になる。そして、直流入力電源に向けて電流If−28aの波形に示す回生電流が流れることによって、電圧V−22aの上昇が停止し、入力電圧Viにクランプされる。従って、電圧Vf−38bも一定電圧を超えて上昇できず、図5(a)に示すように、サージ電圧が小さく抑えられる。また、整流ダイオード38bと同タイミングでオフする整流ダイオード36aについても、同様の動作により、両端に大きなサージ電圧が発生しない。

【0036】

第一回生ダイオード28aに回生電流が流れた後、スイッチング電流は、電流Id−20a,If−36bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに増加する波形となり、負荷16に出力電流Ioを供給すると同時に、平滑インダクタ40及び共振インダクタ26に励磁エネルギーを蓄積する。また、整流ダイオード36b,38aはオフのまま、電圧Vf−36bの波形に示す一定電圧が印加される。また、第一回生ダイオード28aの両端は電位差がほぼゼロになり、第二回生ダイオード28bの両端にはほぼ入力電圧Viが逆方向に印加されるので、電流If−28a,If−28bは流れない。

【0037】

第四の期間T14になると、主スイッチング素子18a,18b,20a,20bが、各々オフ、オン、オフ、オンの状態になる。期間T13から期間T14に移行する時、スイッチング制御回路44は、まず主スイッチング素子20aをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子20bをターンオンさせることによって、主スイッチング素子20bのZVS動作を実現する。

【0038】

期間T13の間、主スイッチング素子20bの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間14に移行する時、まず主スイッチング素子20aがターンオフすることによって、共振インダクタ26が励磁エネルギーを放出する電流が、共振インダクタ26、第一コンデンサ24、一次巻線22a、主スイッチング素子18b、当該寄生コンデンサの経路に流れ始める。この電流により当該寄生コンデンサが放電され、主スイッチング素子20bの両端電圧が低下する。そして、期間Tdが経過して両端電圧がゼロボルトになった時に主スイッチング素子20bがターンオンする。この動作により、主スイッチング素子20bのZVS動作が安定に行われる。

【0039】

期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出する電流が、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード36b、二次巻線22b、一次巻線22a、主スイッチング素子18b、主スイッチング素子20b、共振インダクタ26、第一コンデンサ24、一次巻線22a、二次巻線22b、整流ダイオード38aの経路に流れる。この電流は、If−36bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに減少する波形となり、負荷16に出力電流Ioを供給する。また、整流ダイオード36a,38bにはほとんど電流が流れず、電圧Vf−38bの波形に示すように両端の電位差もほぼゼロになる。

【0040】

このとき、共振インダクタ26は、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に、第二中点20c側の一端から第一中点18c側の一端の向きに僅かな電圧が発生し、第二回生ダイオード28bの両端に逆電圧が印加される。また、第一回生ダイオード28aの両端にはほぼ入力電圧Viが逆方向に印加される。従って、電流If−28a,If−28bは流れない。

【0041】

再び、第一の期間T11になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オフ、オンの状態になる。期間T14から期間T11に移行する時、スイッチング制御回路44は、まず主スイッチング素子18bをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子18aをターンオンさせることによって、主スイッチング素子18aのZVS動作を実現する。

【0042】

期間T14の間、主スイッチング素子18aの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間11に移行する時、まず主スイッチング素子18bがターンオフすることによって、共振インダクタ26が励磁エネルギーを放出する電流が、共振インダクタ26、第一コンデンサ24、一次巻線22a、当該寄生コンデンサ、入力端子12a、直流入力電源、入力端子12b、主スイッチング素子20bの経路に流れ始め、この電流により当該寄生コンデンサが放電され、主スイッチング素子18aの両端電圧が低下する。そして、期間Tdが経過して両端電圧がほぼゼロボルトになった時に主スイッチング素子18aがターンオンする。このような動作により、主スイッチング素子18aのZVS動作が安定に行われる。

【0043】

期間Tdが経過すると、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が正方向に印加される。すると、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20b、入力端子12bの経路に流れ始める。このスイッチング電流は、電流Id−18a,If−38bの波形に示すように急峻な傾きで増加し、共振インダクタ26に励磁エネルギーを蓄積する。

【0044】

一方、整流ダイオード36bは、電流If−36bが急峻な傾きでゼロアンペアまで減少してオフし、その両端に電圧Vf−36bの波形に示す電圧、すなわち二次巻線22bにドットの向きに発生する一定電圧が印加される。このとき、電圧Vf−36bに大きなサージ電圧が発生しないのは、第二回生ダイオード28bの働きによる。

【0045】

仮に第二回生ダイオード28bが設けられていないとすると、電圧Vf−36bが一定電圧まで上昇すると、整流ダイオード36bの図示しない寄生容量と共振インダクタ26との間の共振によるリンギングが起こり、大きなサージ電圧が発生する。しかし、スイッチング電源装置10は、第二回生ダイオード28bが設けられているので、電圧Vf−36bが一定電圧(入力電圧Viをトランス22の巻数比倍した電圧)を超えようとし、一次巻線22aの電圧V−22aが入力電圧Viを超えようとすると、第二回生ダイオード28aが導通し、入力直流電源が一次巻線22aの両端に並列接続された状態になる。そして、直流入力電源に向けて電流If−28bの波形に示す回生電流が流れることによって、電圧V−22aの上昇が停止し、入力電圧Viにクランプされる。従って、電圧Vf−36bも一定電圧を超えて上昇できず、サージ電圧が小さく抑えられる。また、整流ダイオード36bと同タイミングでオフする整流ダイオード38aについても、同様の動作により、両端に大きなサージ電圧が発生しない。回生電流が流れた後の期間T11の動作は、最初の期間T11で説明した通りである。

【0046】

ここで、期間T11〜T14の各期間Tdに行われるZVS動作に関し、各主スイッチング素子のドレイン・ソース間に設けた寄生ダイオード(並列ダイオード)の働きについて説明する。期間Tdの長さは、ここではスイッチング制御回路44の初期設定により、一律の時間になっている。それに対して、例えば主スイッチング素子20aの電圧Vd−20aが低下する速度は、主スイッチング素子20aの寄生コンデンサと共振インダクタ26との間の共振の周波数に依存し、各素子の個体差によってばらつきやすい。従って、例えば、共振周波数が高めにばらついた場合、電圧Vd−20aの低下が速くなり、期間Tdの途中でゼロボルトに達してしまい、さらに共振動作が継続して逆方向に電圧が発生しようとする。しかし、電圧Vd−20aが逆方向に上昇しようとすると、主スイッチング素子20aのドレイン・ソース間の図示しない寄生ダイオードが導通し、電圧Vd−20aが逆方向に上昇するのを抑えられる。その結果、期間Tdが終了するまでほぼゼロボルトに保持され、確実に上記のZVS動作を行うことができる。なお、期間Tdの途中で電圧Vd−20aがゼロボルトに達しない場合は、寄生ダイオードは導通せずZVS動作に関与しない。他の主スイッチング素子18a,18b,20bの寄生ダイオードについても同様である。

【0047】

次に、第一実施形態のスイッチング電源装置10の動作と、一般的なスイッチング電源装置50の動作とを比較する。図6に示すスイッチング電源装置50の構成は、第一アーム18の中点18cと第二アーム20の中点20cの間に設けられた一次巻線22a、第一コンデンサ24及び共振インダクタ26で成る直列回路において、共振インダクタ26の一端が第一中点18cに接続されるように構成されている。この共振インダクタ26が設けられた位置が異なる点を除き、本実施形態のスイッチング電源装置10と同様の構成を備えている。従って、各部品には同一の符号を付して説明を省略する。

【0048】

一般的なスイッチング電源装置50の定常動作は、図7のタイムチャートのように表わされる。図7における第一及び第三の期間T11,T13の動作は、図4で説明したスイッチング電源装置10の第一及び第三の期間T11,T13の動作とほぼ同様であるが、第二及び第四の期間T12,T14の動作に問題が発生する。

【0049】

第二の期間T12になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オン、オフの状態になる。期間T12に移行した直後、上記と同様に、図示しない期間Tdに主スイッチング素子20aのZVS動作が行われる。

【0050】

期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出し、負荷16に出力電流Ioを供給する電流が流れる。このとき、第二回生ダイオード28bは、両端にほぼ入力電圧Viが逆方向に印加されるので導通しない。一方、共振インダクタ26が、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に第一中点18c側の一端から第二中点20c側一端の向きに僅かな電圧が発生し、第一回生ダイオード28aの両端に僅かに順電圧が印加され、導通可能な状態になる。第一回生ダイオード28aが導通すると、平滑インダクタ40及び共振インダクタ26が励磁エネルギーを放出する電流が、電流Id−18a,Id−20a,If−36b,If−38b,If−28aの波形に示すように、各回路素子に複雑な経路で流れることになる。特に、電流If−28の波形に示すように、第一回生ダイオード28aに鋸波状の大きな電流が発生する。

【0051】

上述した第一実施形態のスイッチング電源装置10の場合は、第一回生ダイオード28aに流れる電流は、図4のIf−28aの波形に示すように、第三の期間T13に流れる小さな回生電流だけなので、電流定格の小さい安価なダイオード素子を使用することができた。それに対して、この一般的なスイッチング電源装置50の場合は、第一回生ダイオード28aに流れる電流は、図7のIf−28aの波形に示すように、第一の期間T11に流れる小さな回生電流に加え、第二の期間T12にも鋸波状の大きな電流になるので、第一回生ダイオード28aとして、電流定格の大きい高価なダイオード素子を使用しなければならない。

【0052】

第四の期間T14においても、期間T12に第一回生ダイオード28aに鋸波状の大きな電流が流れるのと同様の現象が、第二回生ダイオード28bで発生する。従って、第二回生ダイオード28bも、電流定格の大きい高価なダイオード素子を使用しなければならない。

【0053】

このように、一般的なスイッチング電源装置50の場合、第二及び第四の期間T12,T14を開始させる第二アーム20側ではなく、第一及び第三の期間T11,T13を開始させる第一アーム18側に共振インダクタ26が設けられているので、図7に示すように、第一回生ダイオード28a,28bに過大電流が流れるという問題が発生する。この問題は、背景技術で説明した特許文献2のDC−DCコンバータにおいても、共振インダクタを接続する位置によっては、同様の発生し得るものである。第一実施形態のスイッチング電源装置10の場合においても、この問題をより発生しにくくするため、トランス22の一次及び二次巻線22a,22bを密に磁気結合させ、漏れインダクタンスが共振インダクタ26のインダクタンスよりも十分小さくなるようにすることが好ましい。

【0054】

以上説明したように、第一実施形態のスイッチング電源装置10は、第一及び第二回生ダイオード28a,28bが行う回生動作により、整流平滑回路30の整流ダイオード36a,36b,38a,38bの両端に発生するサージ電圧が抑えられるので、低耐圧のダイオード素子を使用することにより導通時の電圧降下を抑え、電源効率を向上させることができる。また、共振インダクタ26が、一次巻線22a及び第一コンデンサ24と直列の位置であって、一端が第二アーム20の中点20cに接続される位置に挿入することによって、第一及び第二回生ダイオード28a,28bに過大な電流が流れる現象(図7の期間T12,T14の現象)が回避することができ、電流定格の小さい安価なダイオード素子を使用しても安全である。また、共振インダクタ26の動作によって主スイッチング素子18a,18b,20a,20bのZVS動作も確実に行われ、スイッチング損失も低減できる。

【0055】

また、トランス22の直流偏磁を抑制する第一コンデンサ24が設けられているので、入力投入などの過渡時、トランス22が直流偏磁して磁気飽和するのを容易に回避することができ、磁気飽和に余裕のある大型のトランスを使用しなくても、各部の回路素子が破損するのを防止することができる。

【0056】

次に、この発明のスイッチング電源装置に設けられる整流平滑回路の変形例について、図8に基づいて説明する。第一変形例の整流平滑回路52は、図8(a)に示すように、上記の整流平滑回路30を構成する4つの整流ダイオード36a,36b,38a,38bを、導通抵抗の小さいN−chのMOS型FET54a,54b,56a,56bに置き換えて同期整流を行うものである。この整流平滑回路52によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに整流部32の損失を低減させることができる。

【0057】

第二変形例の整流平滑回路58は、図8(b)に示すように、トランス22の二次巻線22bを2分割し、2つのN―chのMOS型FET60,62によって同期整流を行う整流部63を構成したセンタタップ方式の整流平滑回路である。この整流部63は、2つのダイオード素子で構成してもよい。整流平滑回路58によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに整流部63の構成をシンプルにすることができる等の利点がある。

【0058】

第三変形例の整流平滑回路64は、図8(c)に示すように、トランス22の二次巻線22bの両端に接続した2つのN―chのMOS型FET66,68によって同期整流を行う整流部69を構成し、2つの平滑インダクタ70,72及び平滑コンデンサ42で平滑部74を構成したカレントダブラ方式の整流平滑回路である。この整流部69は、2つのダイオードで構成してもよい。整流平滑回路64によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに平滑コンデンサ42のリップル電圧を低減できる等の利点がある。

【0059】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。例えば、第一及び第二回生ダイオードの中点と共振インダクタの一次巻線側の一端との間に、第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサを挿入することができる(例えば、図9に示す第二コンデンサ66)。この第二コンデンサの静電容量を適宜調整することによって、第一及び第二回生ダイオードに流れる回生電流による電流ストレスをより小さく抑えつつ、整流平滑回路の整流素子に加わるサージ電圧による電圧ストレスも一定以下に制限する、というバランス設計を無損失で行うことができる。

【0060】

また、出力電圧Voを安定化するスイッチング制御回路は、出力電圧Voを直接モニタして制御を行う構成に限定されず、例えば、トランスの巻線電圧又は平滑インダクタの電圧等を利用して間接的に出力電圧Voをモニタして制御を行う構成や、入力電圧Viなどをモニタしてフィードフォワード制御を行う構成であってもよい。

【符号の説明】

【0061】

10,50 スイッチング電源装置

18 第一アーム

18a,18b 主スイッチング素子

18c 第一中点

20 第二アーム

20a,20b 主スイッチング素子

20c 第二中点

22 トランス

22a 一次巻線

22b 二次巻線

24 第一コンデンサ

26 共振インダクタ

28a 第一回生ダイオード

28b 第二回生ダイオード

30,52,58,64 整流平滑回路

44 スイッチング制御回路

66 第二コンデンサ

【技術分野】

【0001】

この発明は、フェイズシフト制御により出力電圧を安定化するフルブリッジ型のスイッチング電源装置に関する。

【背景技術】

【0002】

従来から、1kWを超えるような電力を取り扱うスイッチング電源装置では、高効率化やスイッチング周波数の固定化などの観点から、フェイズシフト制御によって出力電圧を安定化するフルブリッジ型の電源回路が使用されている。

【0003】

この種のスイッチング電源装置として、例えば、特許文献1に従来技術として開示されているように、トランスの一次巻線に接続された主スイッチング素子に流れるスイッチング電流を共振(いわゆる電流共振)させて電力変換を行い、フェイズシフト制御によって出力電圧を安定化するスイッチング電源装置がある。スイッチング電流を共振させる共振回路は、共振インダクタ及び共振コンデンサの直列回路で構成され、トランスの一次巻線と直列の位置に挿入されている。

【0004】

また、特許文献2に開示されたDC−DCコンバータは、トランスの一次巻線と直列の位置にゼロ電圧スイッチング(以下、ZVSと称す。)用の共振インダクタが挿入され、共振インダクタのエネルギー放出動作によって主スイッチング素子の両端に在るコンデンサの電荷の放出を補助し、ZVS動作を可能にしたものである。このDC−DCコンバータは、トランスの一次巻線及び共振インダクタの接続点と入力電源の両端との間に第1及び第2の回生ダイオードが設けられ、トランスの二次巻線に接続された整流ダイオードの両端に発生するサージ電圧を低減させている。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2006−197711号公報

【特許文献2】国際公開WO2007/000830号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

特許文献1の従来技術に係るスイッチング電源装置の場合、出力電流の状態によっては主スイッチング素子のZVS動作が不可能であり、主スイッチング素子のスイッチング損失が増加して効率低下を招くという問題がある。また、この問題を解決するため、特許文献1の発明に係るスイッチング電源装置では、2つのコンデンサと補助共振インダクタを用いた補助共振回路が設けられている。しかし、この補助共振回路を付加することによって、比較的外形の大きなインダクタ素子が少なくとも2つ(共振インダクタ及び補助共振インダクタ)必要になるので、実装スペースやコストの面で不利である。

【0007】

また、特許文献2のDC−DCコンバータの場合、入力電源が投入された起動時や出力電流が急峻に変化した時に、トランスが過渡的に直流偏磁して磁気飽和し、主スイッチング素子等に過大な電気的ストレスが加わって回路素子が破損するおそれがある。従って、磁気飽和に対して余裕を持たせるため、トランスの外形を大きくする必要があった。また、回生ダイオードに流れる電流の大小については特に考慮されておらず、共振インダクタを接続する位置によっては、回生ダイオードに過大な電流が流れ破損する心配があった。

【0008】

この発明は、上記背景技術に鑑みて成されたものであり、主スイッチング素子のZVS動作を確実に行うことができ、特定の回路素子に過大な電気的ストレスが加わることなく安全性の高い小型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

この発明は、ハイサイド側及びグランド側に各々設けられた主スイッチング素子の直列回路で構成され、その両端に直流入力源が接続される第一アームと、ハイサイド側及びグランド側に各々設けられた他の主スイッチング素子の直列回路で構成され、前記第一のアームに並列接続された第二アームと、一次巻線及び二次巻線を有し、前記一次巻線が前記第一アームの中点と前記第二アームの中点との間に設けられたトランスと、前記トランスの前記二次巻線に接続され、前記二次巻線に発生した交流電圧を直流の出力電圧に変換して出力する整流平滑回路と、前記各主スイッチング素子をオンオフ駆動することによって、前記一次巻線に入力電圧が正方向に印加される第一の期間、入力電圧が印加されない第二の期間、負方向に印加される第三の期間、及び再度電圧が出力されない第四の期間を1周期とするフェイズシフト制御を行い、前記整流平滑回路の出力電圧を安定化するスイッチング制御回路と、を備えたフルブリッジ型のスイッチング電源装置であって、前記一次巻線と直列の位置に挿入され、前記トランスの直流偏磁を抑制する第一コンデンサと、前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入された共振インダクタと、前記共振インダクタの前記一次巻線側の一端にアノード端子が接続され、前記第一及び第二アームのハイサイド側の接続点にカソード端子が接続された第一回生ダイオードと、前記第一及び第二アームのグランド側の接続点にアノード端子が接続され、前記共振インダクタの前記一次巻線側の一端にカソード端子が接続された第二回生ダイオードとを備え、前記スイッチング制御回路は、前記第一アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第一及び第三の期間を開始させ、前記第二アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第二及び第四の期間を開始させる制御を行うスイッチング電源装置である。

【0010】

前記第一及び第二アームが有する前記主スイッチング素子はN−chのMOS型FETで構成され、個々のドレイン・ソース間に、並列コンデンサとソース端子からドレイン端子の向きに導通可能な並列ダイオードとが設けられ、さらに、前記スイッチング制御回路は、前記第一アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせ、前記第二アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせる制御を行うようにしてもよい。

【0011】

前記トランスの前記一次及び二次巻線は、前記一次巻線側からみた漏れインダクタンスが、前記共振インダクタのインダクタンスよりも小さくなるように密に磁気結合していることが好ましい。また、前記第一及び第二回生ダイオードの中点と前記共振インダクタの前記一次巻線側の一端との間に、前記第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサが挿入されていてもよい。

【0012】

前記整流平滑回路は、全波整流方式、センタタップ方式、又はカレントダブラ方式の構成を備えている。また、前記整流平滑回路が有する整流部は、MOS型FETによる同期整流を行う構成にしてもよい。

【発明の効果】

【0013】

この発明のスイッチング電源装置は、共振インダクタの動作によって主スイッチング素子のZVS動作を確実に行うことが可能であり、さらにトランスの直流偏磁を抑制する第一コンデンサが設けられているので、入力投入などの過渡時においてもトランスの直流偏磁による磁気飽和を容易に回避し、各回路素子が破損するのを防止することができる。

【0014】

また、第一及び第二回生ダイオードが行う回生動作によって整流平滑回路の整流素子に発生するサージ電圧が低く抑えられるので、整流素子として導通抵抗又は電圧降下の小さい低耐圧半導体を選定することが可能になり、電源効率を向上させることができる。また、共振インダクタを、前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入することによって、第一及び第二回生ダイオードに過大な電流が流れなくなるので安全性も高いものである。

【図面の簡単な説明】

【0015】

【図1】この発明のスイッチング電源装置の第一実施形態を示す回路図である。

【図2】第一コンデンサを設ける位置の各変形例を示す回路図(a),(b)である。

【図3】第一実施形態のスイッチング電源装置の整流平滑回路の構成を示す回路図である。

【図4】第一実施形態のスイッチング電源装置の定常動作を説明するタイムチャートである。

【図5】第一実施形態のスイッチング電源装置の整流ダイオード38b両端の電圧波形(a)、第一及び第二回生ダイオードを設けない場合の整流ダイオード38b両端の電圧波形(b)である。

【図6】共振インダクタが不適切な位置に挿入された比較例のスイッチング電源装置の回路図である。

【図7】図6のスイッチング電源装置の定常動作を説明するタイムチャートである。

【図8】第一実施形態のスイッチング電源装置の整流平滑回路の各変形例を示す回路図(a),(b),(c)である。

【図9】第一実施形態のスイッチング電源装置に追加する第二コンデンサを示す回路図である。

【発明を実施するための形態】

【0016】

以下、この発明のスイッチング電源装置の第一実施形態について、図面に基づいて説明する。第一実施形態のスイッチング電源装置10は、図1に示すように、入力端子12a,12b間に入力された直流の入力電圧Viを直流の出力電圧Voに変換し、出力端子14a,14b間に接続された負荷16に、出力電圧Vo及び電流Ioを供給する電源装置である。ここで、入力及び出力端子12b,14bは、入力及び出力電圧Vi,Voのグランド側の電位であり、入力及び出力端子12a,14aがプラス側の電位である。

【0017】

入力端子12a,12b間には、ハイサイド側及びグランド側の主スイッチング素子18a,18bの直列回路である第一アーム18が接続され、さらに第一アーム18と並列に、ハイサイド側及びグランド側の主スイッチング素子20a,20bの直列回路である第二アーム20が接続されている。ここでは、主スイッチング素子18a,18b,20a,20bとしてN−chのMOS型FETが使用され、主スイッチング素子18a,20aのドレイン端子が入力端子12aに、主スイッチング素子18b,20bのソース端子が入力端子12bに各々接続されている。そして、主スイッチング素子18aのソース端子と主スイッチング素子18bのドレイン端子との接続点が第一アーム18の中点(以下、第一中点18cと称す。)であり、主スイッチング素子20aのソース端子と主スイッチング素子20bのドレイン端子との接続点が第二アーム20の中点20c(以下、第二中点20cと称す。)である。また、主スイッチング素子18a,18b,20a,20bの各チップ内部には、図示しない回路素子であって、ソース端子からドレイン端子の向きの寄生ダイオード、及びそれと並列の寄生コンデンサが形成されている。

【0018】

なお、この実施形態では、各主スイッチング素子のドレイン・ソース間に設ける並列ダイオードと並列コンデンサが、寄生ダイオードと寄生コンデンサで構成されているが、さらに外部に高性能のダイオード素子を接続したり、静電容量調整用のコンデンサ素子を接続して構成してもよい。

【0019】

第一中点18cと第二中点20cの間には、トランス22の一次巻線22aが設けられ、ドットが付された一端が第一中点18cに接続されている。トランス22は、一次巻線22aと二次巻線22bとを有し、それらは互いに密に磁気結合しており、一次巻線22a側から見た漏れインダクタンスは、後述する共振インダクタ26のインダクタンスよりも十分に小さい。

【0020】

一次巻線22aの第二中点20c側の一端には、第一コンデンサ24の一端が接続され、第一コンデンサ24の他の一端と第二中点20cとの間に共振インダクタ26が接続されている。第一コンデンサ24は、トランス22の直流偏磁を抑制するコンデンサであり、一定以上の大きい容量値に設定され、スイッチング周波数におけるインピーダンスが十分小さい。従って、主スイッチング素子18a,18b,20a,20bに流れるスイッチング電流や一次巻線22aに発生する電圧の波形の形状に与える影響は小さい。共振インダクタ26は、自身のエネルギー放出動作によって主スイッチング素子18a,18b,20a,20bの両端にある図示しない寄生コンデンサの電荷放出を補助し、ZVS動作を可能にするものである。

【0021】

この一次巻線22a、第一コンデンサ24及び共振インダクタ26から成る直列回路は、共振インダクタ26の一端が第二中点20cに接続されるように構成されていればよく、例えば、図2(a)に示すように、一次巻線22aと第一コンデンサ24の配置を逆にしたり、図2(b)に示すように、複数に分割した第一コンデンサ24を一次巻線22aの両側に配置したりする構成にすることも可能である。

【0022】

共振インダクタ26の一端には、第一及び第二回生ダイオード28a,28bが接続されている。第一回生ダイオード28aは、共振インダクタ26の一次巻線22a側の一端にアノード端子が接続され、第一及び第二アーム18,20のハイサイド側の接続点にカソード端子が接続されている。第二回生ダイオード28bは、共振インダクタ26の一次巻線22a側の一端にカソード端子が接続され、第一及び第二アーム18,20のグランド側の接続点にアノード端子が接続されている。

【0023】

トランス22の二次巻線22bの両端に、二次巻線22bに発生する交流電圧を直流の出力電圧Voに変換して出力端子14a,14bに出力する整流平滑回路30が設けられている。整流平滑回路30は、図3に示すように全波整流方式の構成を有し、整流部32及び平滑部34で構成されている。整流部32は、二次巻線22bのドットが付された端子にアノード端子及びカソード端子が各々接続された整流ダイオード36a,36bと、二次巻線22bの他の一端にアノード端子及びカソード端子が各々接続された整流ダイオード38a,38bとで構成されている。整流ダイオード36a,38aはカソード端子同士が接続され、整流ダイオード36b,38bはアノード端子同士が接続され、当該2つの接続点の間に、二次巻線22aの交流電圧を全波整流した波形が出力される。平滑部34は、平滑インダクタ40及び平滑コンデンサ42で構成されたローパスフィルタであり、整流部32が出力した全波整流波形を平滑して直流の出力電圧Voを出力する。

【0024】

主スイッチング素子18a,18b,20a,20bは、スイッチング制御回路44によってオンオフ駆動される。スイッチング制御回路44は、出力電圧Voに基づき、時比率が約50%で個々に位相が異なる4種類の駆動パルスを生成し、主スイッチング素子18a,18b,20a,20bの駆動端子に向けて出力する。そして、4つの主スイッチング素子を互いに異なる位相でオンオフさせることによって、一次巻線22aに入力電圧Viが正方向(ドットを付した側が高電位)に印加される第一の期間T11、入力電圧Viが印加されない第二の期間T12、負方向(ドットと反対側が高電位)に印加される第三の期間T13、及び再度電圧が出力されない第四の期間T14を設け、期間T11〜T14を1周期とする一定周波数のフェイズシフト制御を行い、出力電圧Voを安定化する。このとき、スイッチング制御回路44は、第一アーム18側の主スイッチング素子18a,18bのターンオン又はターンオフによって第一及び第三の期間T11,T13を開始させ、第二アーム20側の主スイッチング素子20a,20bのターンオン又はターンオフによって第二及び第四の期間T12,T14を開始させる制御を行う。

【0025】

次に、スイッチング電源装置10の定常動作について、図4のタイムチャートに基づいて説明する。ここで、定常動作とは、入力端子12a,12b間に入力電圧Viが投入された後ある程度の時間が経過し、負荷16に一定の出力電圧Vo及び電流Ioを安定的に供給している状態をいう。また、図4において、電圧Vg−−18a,Vg−18b,Vg−20a,Vg−20bは、それぞれ主スイッチング素子18a,18b,20a,20bの駆動端子に印加される駆動パルスであり、駆動パルスを受けた各主スイッチング素子は、ハイレベルのときにオンし、ローレベルのときにオフする。電圧V−22aは、トランス22の一次巻線22aの電圧(ドットが付されていない端子が基準電位)である。電圧Vd−18a,Vd−20aは、主スイッチング素子18a,20aのドレイン・ソース間の電圧(ソース端子が基準電位)であり、電流Id−18a,Id−20aは、主スイッチング素子18a,20aに流れるスイッチング電流(ドレイン端子からソース端子の向きが正方向)である。電圧Vf−38b,Vf−36bは、整流ダイオード38b,36bの両端電圧(アノード端子が基準電位)であり、電流If−38b,If−36bは、整流ダイオード38b,36bに流れる電流(アノード端子からカソード端子の向きが正方向)である。電流If−28a,If−28bは、第一及び第二回生ダイオード28a,28bに流れる回生電流(アノード端子からカソード端子の向きが正方向)である。

【0026】

第一の期間T11は、主スイッチング素子18a,18b,20a,20bは、各々オン、オフ、オフ、オンの状態である。このとき、第一コンデンサ24と共振インダクタ26のインピーダンスが一次巻線22a両端のインピーダンスよりも十分小さいので、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が正方向に印加される。

【0027】

期間T11に移行した直後のごく短い期間に行われるZVS動作については後述するが、それ以降の期間は、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20b、入力端子12bの経路に流れる。このスイッチング電流は、電流Id−18a,If−38bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに増加する波形となり、負荷16に出力電流Ioを供給すると同時に、平滑インダクタ40及び共振インダクタ26に励磁エネルギーを蓄積する。また、整流ダイオード36b,38aはオフしており、電圧Vf−36bの波形に示す電圧、すなわち二次巻線22bにドットの向きに発生する一定電圧が印加される。また、第一回生ダイオード28aの両端にはほぼ入力電圧Viが逆方向に印加され、第二回生ダイオード28bの両端は電位差がほぼゼロになるので、電流If−28a,If−28bは流れない。

【0028】

第二の期間T12になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オン、オフの状態になる。期間T11から期間T12に移行する時、スイッチング制御回路44は、まず主スイッチング素子20bをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子20aをターンオンさせることによって、主スイッチング素子20aのZVS動作を実現する。

【0029】

期間T11の間、主スイッチング素子20aの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間12に移行する時、まず主スイッチング素子20bがターンオフすることによって、共振インダクタ26の励磁エネルギーを放出する電流が、共振インダクタ26、当該寄生コンデンサ、主スイッチング素子18a、一次巻線22a、第一コンデンサ24の経路に流れ始める。この電流により当該寄生コンデンサが放電され、主スイッチング素子20aの電圧Vd−20aが低下する。そして、期間Tdが経過して電圧Vd−20aがほぼゼロボルトになった時に主スイッチング素子20aがターンオンする。この動作により、主スイッチング素子20aのZVS動作が行われる。 期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出する電流が、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36aの経路に流れる。この電流は、電流Id−18a,Id−20a,If−38bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに減少する波形となり、負荷16に出力電流Ioを供給する。また、整流ダイオード36b,38aにはほとんど電流が流れず、電圧Vf−36bの波形に示すように、両端の電位差もほぼゼロになる。

【0030】

このとき、共振インダクタ26は、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に、第一中点18c側の一端から第二中点20c側一端の向きに僅かな電圧が発生し、第一回生ダイオード28aの両端に逆電圧が印加される。また、第二回生ダイオード28bの両端にはほぼ入力電圧Viが逆方向に印加される。従って、電流If−28a,If−28bは流れない。

【0031】

第三の期間T13になると、主スイッチング素子18a,18b,20a,20bが、各々オフ、オン、オン、オフの状態になる。期間T12から期間T13に移行する時、スイッチング制御回路44は、まず主スイッチング素子18aをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子18bをターンオンさせることによって、主スイッチング素子18bのZVS動作を実現する。

【0032】

期間T12の間、主スイッチング素子18bの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間13に移行する時、まず主スイッチング素子18aがターンオフすることによって、共振インダクタ26の励磁エネルギーを放出する電流が、共振インダクタ26、主スイッチング素子20a、入力端子12a、直流入力電源、入力端子12b、当該寄生コンデンサ、一次巻線22a、第一コンデンサ24の経路に流れ始め、この電流により当該寄生コンデンサが放電され、主スイッチング素子18bの両端電圧が低下する。そして、期間Tdが経過して両端電圧がほぼゼロボルトになった時に主スイッチング素子18bがターンオンする。このような動作により、主スイッチング素子18bのZVS動作が安定に行われる。

【0033】

期間Tdが経過すると、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が負方向に印加される。すると、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子20a、共振インダクタ26、第一コンデンサ24、一次巻線22a、二次巻線22b、整流ダイオード38a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード36b、二次巻線22b、一次巻線22a、主スイッチング素子18b、入力端子12bの経路に流れ始める。このスイッチング電流は、電流Id−20a,If−36bの波形に示すように急峻な傾きで増加し、共振インダクタ26に励磁エネルギーを蓄積する。

【0034】

一方、整流ダイオード38bは、電流If−38bが急峻な傾きでゼロアンペアまで減少してオフし、その両端に電圧Vf−38bの波形に示す電圧、すなわち二次巻線22bにドットと反対の向きに発生する一定電圧が印加される。このとき、電圧Vf−38bに大きなサージ電圧が発生しないのは、第一回生ダイオード28aの働きによる。

【0035】

仮に第一回生ダイオード28aが設けられていないとすると、電圧Vf−38bが一定電圧まで上昇すると、整流ダイオード38bの図示しない寄生容量と共振インダクタ26との間の共振によるリンギングが起こり、図5(b)に示すように、大きなサージ電圧が発生する。このサージ電圧は、整流ダイオード38bにリカバリ電流が生じやすいファストリカバリダイオードを用いた場合に特に大きくなり、リカバリ電流がほとんど生じないショットキバリアダイオード等を用いた場合でも発生する。しかし、スイッチング電源装置10は、第一回生ダイオード28aが設けられているので、電圧Vf−38bが一定電圧(入力電圧Viをトランス22の巻数比倍した電圧)を超えようとし、一次巻線22aの電圧V−22aも入力電圧Viを超えようとすると、第一回生ダイオード28aが導通し、直流入力電源が一次巻線22aの両端に並列接続された状態になる。そして、直流入力電源に向けて電流If−28aの波形に示す回生電流が流れることによって、電圧V−22aの上昇が停止し、入力電圧Viにクランプされる。従って、電圧Vf−38bも一定電圧を超えて上昇できず、図5(a)に示すように、サージ電圧が小さく抑えられる。また、整流ダイオード38bと同タイミングでオフする整流ダイオード36aについても、同様の動作により、両端に大きなサージ電圧が発生しない。

【0036】

第一回生ダイオード28aに回生電流が流れた後、スイッチング電流は、電流Id−20a,If−36bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに増加する波形となり、負荷16に出力電流Ioを供給すると同時に、平滑インダクタ40及び共振インダクタ26に励磁エネルギーを蓄積する。また、整流ダイオード36b,38aはオフのまま、電圧Vf−36bの波形に示す一定電圧が印加される。また、第一回生ダイオード28aの両端は電位差がほぼゼロになり、第二回生ダイオード28bの両端にはほぼ入力電圧Viが逆方向に印加されるので、電流If−28a,If−28bは流れない。

【0037】

第四の期間T14になると、主スイッチング素子18a,18b,20a,20bが、各々オフ、オン、オフ、オンの状態になる。期間T13から期間T14に移行する時、スイッチング制御回路44は、まず主スイッチング素子20aをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子20bをターンオンさせることによって、主スイッチング素子20bのZVS動作を実現する。

【0038】

期間T13の間、主スイッチング素子20bの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間14に移行する時、まず主スイッチング素子20aがターンオフすることによって、共振インダクタ26が励磁エネルギーを放出する電流が、共振インダクタ26、第一コンデンサ24、一次巻線22a、主スイッチング素子18b、当該寄生コンデンサの経路に流れ始める。この電流により当該寄生コンデンサが放電され、主スイッチング素子20bの両端電圧が低下する。そして、期間Tdが経過して両端電圧がゼロボルトになった時に主スイッチング素子20bがターンオンする。この動作により、主スイッチング素子20bのZVS動作が安定に行われる。

【0039】

期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出する電流が、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード36b、二次巻線22b、一次巻線22a、主スイッチング素子18b、主スイッチング素子20b、共振インダクタ26、第一コンデンサ24、一次巻線22a、二次巻線22b、整流ダイオード38aの経路に流れる。この電流は、If−36bの波形に示すように、ほぼ平滑インダクタ40によって規定される傾きで緩やかに減少する波形となり、負荷16に出力電流Ioを供給する。また、整流ダイオード36a,38bにはほとんど電流が流れず、電圧Vf−38bの波形に示すように両端の電位差もほぼゼロになる。

【0040】

このとき、共振インダクタ26は、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に、第二中点20c側の一端から第一中点18c側の一端の向きに僅かな電圧が発生し、第二回生ダイオード28bの両端に逆電圧が印加される。また、第一回生ダイオード28aの両端にはほぼ入力電圧Viが逆方向に印加される。従って、電流If−28a,If−28bは流れない。

【0041】

再び、第一の期間T11になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オフ、オンの状態になる。期間T14から期間T11に移行する時、スイッチング制御回路44は、まず主スイッチング素子18bをターンオフさせ、その後、図示しない短い期間Tdが経過した時に主スイッチング素子18aをターンオンさせることによって、主スイッチング素子18aのZVS動作を実現する。

【0042】

期間T14の間、主スイッチング素子18aの図示しない寄生コンデンサは、ほぼ入力電圧Viに充電されている。期間11に移行する時、まず主スイッチング素子18bがターンオフすることによって、共振インダクタ26が励磁エネルギーを放出する電流が、共振インダクタ26、第一コンデンサ24、一次巻線22a、当該寄生コンデンサ、入力端子12a、直流入力電源、入力端子12b、主スイッチング素子20bの経路に流れ始め、この電流により当該寄生コンデンサが放電され、主スイッチング素子18aの両端電圧が低下する。そして、期間Tdが経過して両端電圧がほぼゼロボルトになった時に主スイッチング素子18aがターンオンする。このような動作により、主スイッチング素子18aのZVS動作が安定に行われる。

【0043】

期間Tdが経過すると、電圧V−22aに示すように、一次巻線22aに入力電圧Viとほぼ等しい電圧が正方向に印加される。すると、スイッチング電流が、直流入力電源、入力端子12a、主スイッチング素子18a、一次巻線22a、二次巻線22b、整流ダイオード36a、平滑インダクタ40、平滑コンデンサ42及び負荷16、整流ダイオード38b、二次巻線22b、一次巻線22a、第一コンデンサ24、共振インダクタ26、主スイッチング素子20b、入力端子12bの経路に流れ始める。このスイッチング電流は、電流Id−18a,If−38bの波形に示すように急峻な傾きで増加し、共振インダクタ26に励磁エネルギーを蓄積する。

【0044】

一方、整流ダイオード36bは、電流If−36bが急峻な傾きでゼロアンペアまで減少してオフし、その両端に電圧Vf−36bの波形に示す電圧、すなわち二次巻線22bにドットの向きに発生する一定電圧が印加される。このとき、電圧Vf−36bに大きなサージ電圧が発生しないのは、第二回生ダイオード28bの働きによる。

【0045】

仮に第二回生ダイオード28bが設けられていないとすると、電圧Vf−36bが一定電圧まで上昇すると、整流ダイオード36bの図示しない寄生容量と共振インダクタ26との間の共振によるリンギングが起こり、大きなサージ電圧が発生する。しかし、スイッチング電源装置10は、第二回生ダイオード28bが設けられているので、電圧Vf−36bが一定電圧(入力電圧Viをトランス22の巻数比倍した電圧)を超えようとし、一次巻線22aの電圧V−22aが入力電圧Viを超えようとすると、第二回生ダイオード28aが導通し、入力直流電源が一次巻線22aの両端に並列接続された状態になる。そして、直流入力電源に向けて電流If−28bの波形に示す回生電流が流れることによって、電圧V−22aの上昇が停止し、入力電圧Viにクランプされる。従って、電圧Vf−36bも一定電圧を超えて上昇できず、サージ電圧が小さく抑えられる。また、整流ダイオード36bと同タイミングでオフする整流ダイオード38aについても、同様の動作により、両端に大きなサージ電圧が発生しない。回生電流が流れた後の期間T11の動作は、最初の期間T11で説明した通りである。

【0046】

ここで、期間T11〜T14の各期間Tdに行われるZVS動作に関し、各主スイッチング素子のドレイン・ソース間に設けた寄生ダイオード(並列ダイオード)の働きについて説明する。期間Tdの長さは、ここではスイッチング制御回路44の初期設定により、一律の時間になっている。それに対して、例えば主スイッチング素子20aの電圧Vd−20aが低下する速度は、主スイッチング素子20aの寄生コンデンサと共振インダクタ26との間の共振の周波数に依存し、各素子の個体差によってばらつきやすい。従って、例えば、共振周波数が高めにばらついた場合、電圧Vd−20aの低下が速くなり、期間Tdの途中でゼロボルトに達してしまい、さらに共振動作が継続して逆方向に電圧が発生しようとする。しかし、電圧Vd−20aが逆方向に上昇しようとすると、主スイッチング素子20aのドレイン・ソース間の図示しない寄生ダイオードが導通し、電圧Vd−20aが逆方向に上昇するのを抑えられる。その結果、期間Tdが終了するまでほぼゼロボルトに保持され、確実に上記のZVS動作を行うことができる。なお、期間Tdの途中で電圧Vd−20aがゼロボルトに達しない場合は、寄生ダイオードは導通せずZVS動作に関与しない。他の主スイッチング素子18a,18b,20bの寄生ダイオードについても同様である。

【0047】

次に、第一実施形態のスイッチング電源装置10の動作と、一般的なスイッチング電源装置50の動作とを比較する。図6に示すスイッチング電源装置50の構成は、第一アーム18の中点18cと第二アーム20の中点20cの間に設けられた一次巻線22a、第一コンデンサ24及び共振インダクタ26で成る直列回路において、共振インダクタ26の一端が第一中点18cに接続されるように構成されている。この共振インダクタ26が設けられた位置が異なる点を除き、本実施形態のスイッチング電源装置10と同様の構成を備えている。従って、各部品には同一の符号を付して説明を省略する。

【0048】

一般的なスイッチング電源装置50の定常動作は、図7のタイムチャートのように表わされる。図7における第一及び第三の期間T11,T13の動作は、図4で説明したスイッチング電源装置10の第一及び第三の期間T11,T13の動作とほぼ同様であるが、第二及び第四の期間T12,T14の動作に問題が発生する。

【0049】

第二の期間T12になると、主スイッチング素子18a,18b,20a,20bが、各々オン、オフ、オン、オフの状態になる。期間T12に移行した直後、上記と同様に、図示しない期間Tdに主スイッチング素子20aのZVS動作が行われる。

【0050】

期間Td以降の期間は、一次巻線22aの電圧V−22aがほぼゼロボルトとなり、平滑インダクタ40が励磁エネルギーを放出し、負荷16に出力電流Ioを供給する電流が流れる。このとき、第二回生ダイオード28bは、両端にほぼ入力電圧Viが逆方向に印加されるので導通しない。一方、共振インダクタ26が、直前の期間Tdから継続して励磁エネルギーを放出する動作を行うので、共振インダクタ26の両端に第一中点18c側の一端から第二中点20c側一端の向きに僅かな電圧が発生し、第一回生ダイオード28aの両端に僅かに順電圧が印加され、導通可能な状態になる。第一回生ダイオード28aが導通すると、平滑インダクタ40及び共振インダクタ26が励磁エネルギーを放出する電流が、電流Id−18a,Id−20a,If−36b,If−38b,If−28aの波形に示すように、各回路素子に複雑な経路で流れることになる。特に、電流If−28の波形に示すように、第一回生ダイオード28aに鋸波状の大きな電流が発生する。

【0051】

上述した第一実施形態のスイッチング電源装置10の場合は、第一回生ダイオード28aに流れる電流は、図4のIf−28aの波形に示すように、第三の期間T13に流れる小さな回生電流だけなので、電流定格の小さい安価なダイオード素子を使用することができた。それに対して、この一般的なスイッチング電源装置50の場合は、第一回生ダイオード28aに流れる電流は、図7のIf−28aの波形に示すように、第一の期間T11に流れる小さな回生電流に加え、第二の期間T12にも鋸波状の大きな電流になるので、第一回生ダイオード28aとして、電流定格の大きい高価なダイオード素子を使用しなければならない。

【0052】

第四の期間T14においても、期間T12に第一回生ダイオード28aに鋸波状の大きな電流が流れるのと同様の現象が、第二回生ダイオード28bで発生する。従って、第二回生ダイオード28bも、電流定格の大きい高価なダイオード素子を使用しなければならない。

【0053】

このように、一般的なスイッチング電源装置50の場合、第二及び第四の期間T12,T14を開始させる第二アーム20側ではなく、第一及び第三の期間T11,T13を開始させる第一アーム18側に共振インダクタ26が設けられているので、図7に示すように、第一回生ダイオード28a,28bに過大電流が流れるという問題が発生する。この問題は、背景技術で説明した特許文献2のDC−DCコンバータにおいても、共振インダクタを接続する位置によっては、同様の発生し得るものである。第一実施形態のスイッチング電源装置10の場合においても、この問題をより発生しにくくするため、トランス22の一次及び二次巻線22a,22bを密に磁気結合させ、漏れインダクタンスが共振インダクタ26のインダクタンスよりも十分小さくなるようにすることが好ましい。

【0054】

以上説明したように、第一実施形態のスイッチング電源装置10は、第一及び第二回生ダイオード28a,28bが行う回生動作により、整流平滑回路30の整流ダイオード36a,36b,38a,38bの両端に発生するサージ電圧が抑えられるので、低耐圧のダイオード素子を使用することにより導通時の電圧降下を抑え、電源効率を向上させることができる。また、共振インダクタ26が、一次巻線22a及び第一コンデンサ24と直列の位置であって、一端が第二アーム20の中点20cに接続される位置に挿入することによって、第一及び第二回生ダイオード28a,28bに過大な電流が流れる現象(図7の期間T12,T14の現象)が回避することができ、電流定格の小さい安価なダイオード素子を使用しても安全である。また、共振インダクタ26の動作によって主スイッチング素子18a,18b,20a,20bのZVS動作も確実に行われ、スイッチング損失も低減できる。

【0055】

また、トランス22の直流偏磁を抑制する第一コンデンサ24が設けられているので、入力投入などの過渡時、トランス22が直流偏磁して磁気飽和するのを容易に回避することができ、磁気飽和に余裕のある大型のトランスを使用しなくても、各部の回路素子が破損するのを防止することができる。

【0056】

次に、この発明のスイッチング電源装置に設けられる整流平滑回路の変形例について、図8に基づいて説明する。第一変形例の整流平滑回路52は、図8(a)に示すように、上記の整流平滑回路30を構成する4つの整流ダイオード36a,36b,38a,38bを、導通抵抗の小さいN−chのMOS型FET54a,54b,56a,56bに置き換えて同期整流を行うものである。この整流平滑回路52によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに整流部32の損失を低減させることができる。

【0057】

第二変形例の整流平滑回路58は、図8(b)に示すように、トランス22の二次巻線22bを2分割し、2つのN―chのMOS型FET60,62によって同期整流を行う整流部63を構成したセンタタップ方式の整流平滑回路である。この整流部63は、2つのダイオード素子で構成してもよい。整流平滑回路58によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに整流部63の構成をシンプルにすることができる等の利点がある。

【0058】

第三変形例の整流平滑回路64は、図8(c)に示すように、トランス22の二次巻線22bの両端に接続した2つのN―chのMOS型FET66,68によって同期整流を行う整流部69を構成し、2つの平滑インダクタ70,72及び平滑コンデンサ42で平滑部74を構成したカレントダブラ方式の整流平滑回路である。この整流部69は、2つのダイオードで構成してもよい。整流平滑回路64によれば、上記の整流平滑回路30の場合と同様の効果を得ることができ、さらに平滑コンデンサ42のリップル電圧を低減できる等の利点がある。

【0059】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。例えば、第一及び第二回生ダイオードの中点と共振インダクタの一次巻線側の一端との間に、第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサを挿入することができる(例えば、図9に示す第二コンデンサ66)。この第二コンデンサの静電容量を適宜調整することによって、第一及び第二回生ダイオードに流れる回生電流による電流ストレスをより小さく抑えつつ、整流平滑回路の整流素子に加わるサージ電圧による電圧ストレスも一定以下に制限する、というバランス設計を無損失で行うことができる。

【0060】

また、出力電圧Voを安定化するスイッチング制御回路は、出力電圧Voを直接モニタして制御を行う構成に限定されず、例えば、トランスの巻線電圧又は平滑インダクタの電圧等を利用して間接的に出力電圧Voをモニタして制御を行う構成や、入力電圧Viなどをモニタしてフィードフォワード制御を行う構成であってもよい。

【符号の説明】

【0061】

10,50 スイッチング電源装置

18 第一アーム

18a,18b 主スイッチング素子

18c 第一中点

20 第二アーム

20a,20b 主スイッチング素子

20c 第二中点

22 トランス

22a 一次巻線

22b 二次巻線

24 第一コンデンサ

26 共振インダクタ

28a 第一回生ダイオード

28b 第二回生ダイオード

30,52,58,64 整流平滑回路

44 スイッチング制御回路

66 第二コンデンサ

【特許請求の範囲】

【請求項1】

ハイサイド側及びグランド側に各々設けられた主スイッチング素子の直列回路で構成され、その両端に直流入力源が接続される第一アームと、

ハイサイド側及びグランド側に各々設けられた他の主スイッチング素子の直列回路で構成され、前記第一のアームに並列接続された第二アームと、

一次巻線及び二次巻線を有し、前記一次巻線が前記第一アームの中点と前記第二アームの中点との間に設けられたトランスと、

前記トランスの前記二次巻線に接続され、前記二次巻線に発生した交流電圧を直流の出力電圧に変換して出力する整流平滑回路と、

前記各主スイッチング素子をオンオフ駆動することによって、前記一次巻線に入力電圧が正方向に印加される第一の期間、入力電圧が印加されない第二の期間、負方向に印加される第三の期間、及び再度電圧が出力されない第四の期間を1周期とするフェイズシフト制御を行い、前記整流平滑回路の出力電圧を安定化するスイッチング制御回路と、を備えたフルブリッジ型のスイッチング電源装置において、

前記一次巻線と直列の位置に挿入され、前記トランスの直流偏磁を抑制する第一コンデンサと、

前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入された共振インダクタと、

前記共振インダクタの前記一次巻線側の一端にアノード端子が接続され、前記第一及び第二アームのハイサイド側の接続点にカソード端子が接続された第一回生ダイオードと、

前記第一及び第二アームのグランド側の接続点にアノード端子が接続され、前記共振インダクタの前記一次巻線側の一端にカソード端子が接続された第二回生ダイオードとを備え、

前記スイッチング制御回路は、前記第一アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第一及び第三の期間を開始させ、前記第二アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第二及び第四の期間を開始させる制御を行うことを特徴とするスイッチング電源装置。

【請求項2】

前記第一及び第二アームが有する前記主スイッチング素子はN−chのMOS型FETで構成され、個々のドレイン・ソース間に、並列コンデンサとソース端子からドレイン端子の向きに導通可能な並列ダイオードとが設けられ、

前記スイッチング制御回路は、

前記第一アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせ、

前記第二アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせる制御を行う請求項1記載のスイッチング電源装置。

【請求項3】

前記トランスの前記一次及び二次巻線は、前記一次巻線側からみた漏れインダクタンスが、前記共振インダクタのインダクタンスよりも小さくなるように密に磁気結合している請求項1又は2記載のスイッチング電源装置。

【請求項4】

前記第一及び第二回生ダイオードの中点と前記共振インダクタの前記一次巻線側の一端との間に、前記第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサが挿入された請求項1乃至3の何れか記載のスイッチング電源装置。

【請求項5】

前記整流平滑回路は、全波整流方式、センタタップ方式、又はカレントダブラ方式の構成を備えている請求項1乃至3の何れか記載のスイッチング電源装置。

【請求項6】

前記整流平滑回路が有する整流部は、MOS型FETによる同期整流を行う請求項5記載のスイッチング電源装置。

【請求項1】

ハイサイド側及びグランド側に各々設けられた主スイッチング素子の直列回路で構成され、その両端に直流入力源が接続される第一アームと、

ハイサイド側及びグランド側に各々設けられた他の主スイッチング素子の直列回路で構成され、前記第一のアームに並列接続された第二アームと、

一次巻線及び二次巻線を有し、前記一次巻線が前記第一アームの中点と前記第二アームの中点との間に設けられたトランスと、

前記トランスの前記二次巻線に接続され、前記二次巻線に発生した交流電圧を直流の出力電圧に変換して出力する整流平滑回路と、

前記各主スイッチング素子をオンオフ駆動することによって、前記一次巻線に入力電圧が正方向に印加される第一の期間、入力電圧が印加されない第二の期間、負方向に印加される第三の期間、及び再度電圧が出力されない第四の期間を1周期とするフェイズシフト制御を行い、前記整流平滑回路の出力電圧を安定化するスイッチング制御回路と、を備えたフルブリッジ型のスイッチング電源装置において、

前記一次巻線と直列の位置に挿入され、前記トランスの直流偏磁を抑制する第一コンデンサと、

前記一次巻線及び前記第一コンデンサと直列の位置であって、一端が前記第二アームの中点に接続される位置に挿入された共振インダクタと、

前記共振インダクタの前記一次巻線側の一端にアノード端子が接続され、前記第一及び第二アームのハイサイド側の接続点にカソード端子が接続された第一回生ダイオードと、

前記第一及び第二アームのグランド側の接続点にアノード端子が接続され、前記共振インダクタの前記一次巻線側の一端にカソード端子が接続された第二回生ダイオードとを備え、

前記スイッチング制御回路は、前記第一アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第一及び第三の期間を開始させ、前記第二アームを構成する前記主スイッチング素子のターンオン又はターンオフによって前記第二及び第四の期間を開始させる制御を行うことを特徴とするスイッチング電源装置。

【請求項2】

前記第一及び第二アームが有する前記主スイッチング素子はN−chのMOS型FETで構成され、個々のドレイン・ソース間に、並列コンデンサとソース端子からドレイン端子の向きに導通可能な並列ダイオードとが設けられ、

前記スイッチング制御回路は、

前記第一アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせ、

前記第二アームのハイサイド側及びグランド側の前記主スイッチング素子を相補的にオンオフ反転させるとき、オンしている一方の前記主スイッチング素子をターンオフさせた後、オフしている他方の前記主スイッチング素子の両端電圧が、前記共振インダクタと前記並列コンデンサとの共振動作によってゼロボルトに向かって低下したタイミングで、当該他方の前記主スイッチング素子をターンオンさせる制御を行う請求項1記載のスイッチング電源装置。

【請求項3】

前記トランスの前記一次及び二次巻線は、前記一次巻線側からみた漏れインダクタンスが、前記共振インダクタのインダクタンスよりも小さくなるように密に磁気結合している請求項1又は2記載のスイッチング電源装置。

【請求項4】

前記第一及び第二回生ダイオードの中点と前記共振インダクタの前記一次巻線側の一端との間に、前記第一及び第二回生ダイオードに流れる回生電流を制限する第二コンデンサが挿入された請求項1乃至3の何れか記載のスイッチング電源装置。

【請求項5】

前記整流平滑回路は、全波整流方式、センタタップ方式、又はカレントダブラ方式の構成を備えている請求項1乃至3の何れか記載のスイッチング電源装置。

【請求項6】

前記整流平滑回路が有する整流部は、MOS型FETによる同期整流を行う請求項5記載のスイッチング電源装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2012−239341(P2012−239341A)

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願番号】特願2011−108058(P2011−108058)

【出願日】平成23年5月13日(2011.5.13)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

【公開日】平成24年12月6日(2012.12.6)

【国際特許分類】

【出願日】平成23年5月13日(2011.5.13)

【出願人】(000103208)コーセル株式会社 (80)

【Fターム(参考)】

[ Back to top ]