スイッチング電源装置

【課題】電源装置の外部環境の急変に対する過渡的な出力電圧の変動を小さくする高速応答特性を有し、小形化、低コスト化が容易なスイッチング電源装置を提供する。

【解決手段】演算手段28には、負の一次関数等で出力電圧Voと出力微分値Vdの関係を規定する制御関数式が定義される。演算手段28は、主スイッチング素子14のスイッチング周期に同期したタイミングで、入力電圧信号Vi,出力電圧信号Voをサンプリングし、以降の主スイッチング素子14のオン時間及びオフ時間を、上記制御関数式を満足するように算出する。駆動パルス生成手段30は、演算手段28が決定したオン時間及びオフ時間に基づいて、主スイッチング素子14をオン・オフさせる駆動パルスV14を生成する。演算手段110は、定期的に回路定数のパラメータ推定を行い、回路定数を定期的に更新する。

【解決手段】演算手段28には、負の一次関数等で出力電圧Voと出力微分値Vdの関係を規定する制御関数式が定義される。演算手段28は、主スイッチング素子14のスイッチング周期に同期したタイミングで、入力電圧信号Vi,出力電圧信号Voをサンプリングし、以降の主スイッチング素子14のオン時間及びオフ時間を、上記制御関数式を満足するように算出する。駆動パルス生成手段30は、演算手段28が決定したオン時間及びオフ時間に基づいて、主スイッチング素子14をオン・オフさせる駆動パルスV14を生成する。演算手段110は、定期的に回路定数のパラメータ推定を行い、回路定数を定期的に更新する。

【発明の詳細な説明】

【技術分野】

【0001】

この発明は、デジタル制御型の制御回路を用いて出力を定電圧化するスイッチング電源装置に関する。

【背景技術】

【0002】

従来から、デジタルプロセッサ等を用いたインテリジェント性の高いデジタル制御型の制御回路を用いて、PWM(Pulse Width Modulation)制御やPFM(Pulse

Frequency Modulation)制御等を行って出力を定電圧化するスイッチング電源装置があった。特に近年は、電源装置の外部環境の急変に対して出力電圧の過渡的な変動を小さくすることが強く求められている。

【0003】

スイッチング電源装置の外部環境が急変する状況として、動作中に入力電圧が急峻に変動したり、負荷の状態が変化し出力電流が急峻に増減したりすることが考えられる。また、停止しているスイッチング電源装置に入力電圧が投入されて起動するときの動作も問題になる。

【0004】

例えば、情報通信機器やサーバ等に用いられるスイッチング電源装置の場合、出力電流がほぼゼロから定格負荷まで急峻に変化する状況が頻繁に起こり得ることから、負荷急変に対する出力電圧制御の高速応答特性が求められる。また、1つの入力電源ラインから多数のボード基板に電圧供給するシステムにおいては、メンテナンス時に他のボード基板が活線挿抜されることによって、システムの電源ラインの負荷状態が変化し、当該電源ラインから電力供給を受けているスイッチング電源装置の入力電圧が急変することが想定される。従って、この種のシステムに用いられるスイッチング電源装置は、入力急変に対する出力電圧制御の高速応答特性が求められる。さらに、一般的な事項として、入力電圧を投入した時、出力電圧がゼロから上昇して所定の出力電圧に達する過程でオーバーシュートや振動が生じると、負荷である電子機器が誤動作したり故障したりするおそれがあるので、スイッチング電源装置は、出力電圧が単調に増加して立ち上がることが求められる。

【0005】

これらの課題を解決するため、例えば特許文献1に開示されているように、動作中の入力電圧に相当する信号(入力電圧信号)、出力電圧に相当する信号(出力電圧信号)、及び当該出力電圧の変化を示す出力電圧微分値に相当する信号(出力微分信号)を取得し、各信号に基づいて所定のデジタル演算処理を行い、主スイッチング素子のオン時間及びオフ時間を決定するスイッチング電源装置が提案されている。このスイッチング電源装置は、制御回路の演算手段に、傾きが負の一次関数等で出力電圧信号と出力微分値の関係を規定する制御関数式が定義されている。演算手段は、主スイッチング素子のスイッチング周期に同期したタイミングで、入力電圧信号、出力電圧信号及び出力微分信号をサンプリングし、以降の主スイッチング素子のオン時間及びオフ時間を、上記の制御関数式を満足するように算出する。そして、演算手段が決定したオン時間及びオフ時間に基づき、駆動パルス生成手段が、主スイッチング素子をオン・オフさせる駆動パルスを生成する。このとき、出力微分信号は、平滑コンデンサの電流を測定するコンデンサ電流検出手段、又は出力電圧信号を微分する微分手段などを通じて入手する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2011−91974号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1のスイッチング電源装置の場合、入力電圧信号及び出力電圧信号は、いずれも入力電圧及び出力電圧のアナログ情報を単純にA/D変換器でデジタル化したものであり入手が容易であるが、出力微分信号を入手するのは容易ではない。例えば、平滑コンデンサに流れる電流を測定し、そのアナログ情報をデジタル化して出力微分信号を入手する方法の場合、通常は、電流−電圧変換回路を設け、コンデンサ電流をアナログ/アナログ変換した後、A/D変換器でデジタル化しなければならず、電源装置が大形化したり損失が増加したりする問題があった。また、A/D変換器でデジタル化した出力電圧信号を微分演算して出力微分信号を入手する方法の場合、計算回数の増大により制御の遅れが問題になるので、制御回路を高速動作させるためには、制御回路の機能を削って計算回数を減らしたり、高速動作可能な高価なマイクロコンピュータを使用したりしなければならなかった。

【0008】

この発明は、上記背景技術に鑑みて成されたもので、電源装置の外部環境の急変に対する過渡的な出力電圧の変動を小さくする高速応答特性を有し、小形化、低コスト化が容易なデジタル制御型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

この発明は、オン・オフ動作する主スイッチング素子を含む電力変換回路と、当該オン・オフ動作を制御することによって出力電圧を定電圧化する制御回路とを備えたスイッチング電源装置であって、

前記制御回路は、前記主スイッチング素子のオン時間及びオフ時間を決定する演算手段と、前記主スイッチング素子をオン・オフさせる駆動パルスを生成する駆動パルス生成手段とを有し、

前記演算手段には、出力電圧と、当該出力電圧の変化を示す出力微分値とを変数として含み、当該2つの変数の関係を、出力電圧の一つの値に対応する出力微分値が一つだけ存在する連続関数式であって、出力電圧がその出力電圧を定電圧化する目標値よりも低い範囲にあるときは、対応する出力微分値が正の値になり、出力電圧が目標値よりも高い範囲にあるときは、対応する出力微分値が負の値になり、出力電圧が目標値に等しいときは、対応する出力微分値がゼロになるように規定する制御関数式が定義され、

前記演算手段は、主スイッチング素子のスイッチング周期に同期したタイミングで、入力電圧を検出した入力電圧信号と、出力電圧を検出又は推定した出力電圧信号とをサンプリングし、サンプリングした当該2つの信号に基づいて導出される次回又はそれ以降のサンプリングタイミングにおける出力電圧信号及び出力微分値が前記制御関数式に規定される関係を満たすように、当該サンプリングタイミング以降のスイッチング周期における主スイッチング素子のオン時間及びオフ時間のうちの少なくとも一方を算出する演算処理を行い、

前記駆動パルス生成手段は、上記2つの信号のサンプリングタイミング以降のスイッチング周期において、前記演算手段が決定したオン時間及びオフ時間に基づいて前記主スイッチング素子をオン・オフさせるよう、駆動パルスを生成するスイッチング電源装置である。

【0010】

前記演算手段は、前記各信号のサンプリングと、オン時間及びオフ時間のうちの少なくとも一方を算出する演算処理とを、前記主スイッチング素子のスイッチング周期ごとに行うものでもよい。その場合、前記電力変換回路は、前記主スイッチング素子のオン期間に、入力直流電源から出力への電力供給を止めて入力直流電源によって内蔵するインダクタンス素子を励磁し、前記主スイッチング素子のオフ期間に、前記インダクタンス素子に蓄積された励磁エネルギーを出力に放出して電力供給をする動作を行い、前記演算手段は、前記各信号のサンプリングを、前記インダクタンス素子が励磁エネルギーを放出している期間に行う。あるいは、前記駆動パルス生成手段は、前記各信号のサンプリング周期の中間時点を挟んで前後に等しい期間を前記主スイッチング素子のオン期間とする駆動パルスを生成し、又は、当該サンプリング周期の中間時点を挟んで前後に等しい期間を前記主スイッチング素子のオフ期間とする駆動パルスを生成する。

【0011】

前記電力変換回路は、前記主スイッチング素子のオン期間に、入力直流電源から出力への電力供給をすると共に、入力直流電源によって内蔵するインダクタンス素子を励磁し、前記主スイッチング素子のオフ期間に、前記インダクタンス素子に蓄積された励磁エネルギーを出力に放出して電力供給し続ける動作を行い、前記演算手段は、前記各信号のサンプリングと、オン時間及びオフ時間のうちの少なくとも一方を算出する演算処理とを、前記主スイッチング素子のスイッチング周期の半分の周期で行い、前記駆動パルス生成手段は、スイッチングの1周期の中の2回目のサンプリングタイミングを挟んで前後の期間を前記主スイッチング素子のオン期間とする駆動パルスを生成し、又は、当該2回目のサンプリングタイミングを挟んで前後の期間を前記主スイッチング素子のオフ期間とする駆動パルスを生成するものでもよい。

【0012】

前記制御回路は、状態変数の推定手段であるオブザーバを備え、前記オブザーバは、前記演算手段が入力電圧信号をサンプリングするタイミングで、当該入力電圧信号及び出力電圧を検出した出力電圧信号を入手すると共に、前記演算手段がその直前に決定したオン時間及びオフ時間を入手し、入手した入力電圧信号、出力電圧信号、オン時間及びオフ時間に基づいて、次のサンプリングタイミングにおける出力電圧信号を推定する処理を行い、前記演算手段は、当該入力電圧信号、出力電圧信号、オン時間及びオフ時間と、前記オブザーバが推定した出力電圧信号とをサンプリングし、それらに基づいて上記の演算処理を行う。

【0013】

前記オブザーバは、入手した入力電圧信号、出力電圧信号、オン時間及びオフ時間に基づいて、次のサンプリングタイミングにおける出力電圧信号、及び出力電流が流れる経路に存在する寄生インピーダンスによる電圧降下成分を推定する処理を行い、前記演算手段は、当該入力電圧信号、出力電圧信号及びオン時間及びオフ時間と、前記オブザーバが推定した出力電圧信号及び前記電圧降下成分とをサンプリングし、それらに基づいて上記の演算処理を行うものでもよい。また、前記演算手段に定義された制御関数式は、出力電圧と出力微分値との関係を、負の傾きを有する一次関数で規定されていてもよい。

【0014】

前記演算手段に定義された制御関数式は、出力電圧と目標値の差が所定の値を超える範囲では、出力微分値が出力電圧によらず一定になるよう規定されている。

【0015】

前記演算手段は、オン時間及びオフ時間の双方を、互いの合計時間が一定になるように算出する。あるいは、前記演算手段は、オフ時間を、オン時間が一定になるように算出する。あるいは、前記演算手段は、オン時間を、オフ時間が一定になるように算出するものでも良い。その場合、前記演算手段が決定したオン時間及びオフ時間が、オンの時比率として可変可能な最大時比率を超える関係にあるとき、前記駆動パルス生成手段は、当該最大時比率で前記主スイッチング素子をオン・オフさせる駆動パルスを生成し、前記演算手段が決定したオン時間及びオフ時間が、オンの時比率として可変可能な最小時比率を下回る関係にあるとき、前記駆動パルス生成手段は、当該最小時比率で前記主スイッチング素子をオン・オフさせる駆動パルスを生成する。

【0016】

前記演算手段は、オン時間及びオフ時間の双方を、スイッチング周期に対するオンの時比率が一定になるように算出するものでもよい。その場合、前記演算手段が決定したオン時間及びオフ時間の合計値が、可変可能な最大時間を超えたとき、前記駆動パルス生成手段は、当該最大時間で前記主スイッチング素子をオン・オフさせる駆動パルスを生成し、

前記演算手段が決定したオン時間及びオフ時間の合計値が、可変可能な最小時間を下回ったとき、前記駆動パルス生成手段は、当該最小時間で前記主スイッチング素子をオン・オフさせる駆動パルスを生成する。

【0017】

前記演算手段は、デフォルト値として初期設定されている回路定数についてパラメータ推定を行い、前記演算手段がサンプリングした実際の出力電圧信号と、過去にオン時間及びオフ時間を決定したときに予想した当該サンプリングタイミングにおける出力電圧信号との差が小さくなるように更新する。複数の前記回路定数を組み合わせて成る定数である複合定数が定義され、前記パラメータ推定は、当該複合定数の単位で行われるものでもよい。また、前記回路定数又は前記複合定数に基づく前記パラメータ推定は、オフライン最小二乗法を用いて行われるものでもよい。

【0018】

例えば、前記電力変換回路は、入力電圧を断続する前記主スイッチング素子と、前記主スイッチング素子と相補的にオン・オフする整流素子と、前記整流素子の両端の断続電圧を平滑する平滑インダクタ及び平滑コンデンサとを備えた降圧チョッパ回路であり、

前記演算処理回路には、前記主スイッチング素子のスイッチング周期T、前記平滑インダクタのインダクタンスL、前記平滑コンデンサの容量C、前記出力電流Io、前記平滑インダクタの寄生抵抗の抵抗値Rを用いて次式(1)、(2)で定義される前記複合定数であるp及びVofsがデフォルト値として初期設定され、

【数1】

【数2】

前記演算手段は、電源動作中に前記複合定数p及びVofsをパラメータ推定によって定期的に更新し、

前記パラメータ推定は、前記演算手段が、タイミングt(k),t(k−1),t(k−2)ごとにサンプリングした検出値である出力電圧信号Vo(k),Vo(k−1),Vo(k−2),Vi(k−1),Vi(k−2)、及び、タイミングt(k−1),t(k−2)ごとの時比率として算出したδ(k−1),δ(k−2)の各値を取得し、前記各値を含む以下の式(3)〜式(5)により表される評価関数J(N)が最小になる前記複合定数p及びVofsを算出することによって行われるスイッチング電源装置である。

【数3】

【数4】

【数5】

【0019】

さらに、前記演算手段は、前記パラメータ推定を行うタイミングごとに、上記の演算処理を経て決定されるオン時間及びオフ時間を僅かに拡散変動させ、当該拡散変動によって出力電圧が変動している期間中に各信号のサンプリングを行って、前記パラメータ推定を行うものである。

【発明の効果】

【0020】

この発明のスイッチング電源装置は、検出値である入力電圧信号及び出力電圧信号の2つの信号に基づき、上記制御関数を充足するようにオン時間及びオフ時間等を算出し、主スイッチング素子のオン・オフを制御する。従って、電源装置の外部環境の急変に対する高速応答特性を、シンプルで安価な制御回路によって実現することができる。

【0021】

また、オブザーバを用いて出力電圧信号を推定する構成にすることによって、安価で低速のマイクロコンピュータ等を使用した場合でも、制御回路の動作遅れの影響を最小限に抑えることができる。さらに、出力電流に相当する信号(例えば、上記の電圧降下成分)も合わせてオブザーバが推定する構成にすることによって、出力電流が流れる経路にある寄生インピーダンスの影響を考慮した制御が可能になり、出力電圧制御の精度を向上させることができる。

【0022】

さらに、デフォルト値として初期設定されている回路定数についてパラメータ推定を行い、定期的に更新する構成にすることによって、各回路素子のインピーダンス(抵抗値、インダクタンス、キャパシタンス、半導体の導通抵抗など)の個体差、温度変動、経時変化の影響が確実にキャンセルされ、出力電圧制御をより高精度に行うことができる。

【図面の簡単な説明】

【0023】

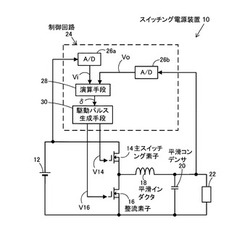

【図1】この発明のスイッチング電源装置の第一の実施形態を示す回路図である。

【図2】この発明の第一の実施形態の定常動作を説明するフローチャートである。

【図3】この発明の第一の実施形態の定常動作を説明するタイムチャートである。

【図4】この発明の第一の実施形態の入力投入時の動作を説明する制御関数式のグラフ(a)、タイムチャート(b)、及び、期間Bの動作を説明するグラフ(c)である。

【図5】図4の制御関数式の変形例のグラフ(a)と、そのときの動作を説明するタイムチャート(b)である。

【図6】この発明のスイッチング電源装置の第二の実施形態を示す回路図である。

【図7】この発明の第二の実施形態の定常動作を説明するタイムチャートである。

【図8】この発明のスイッチング電源装置の第三の実施形態を示す回路図である。

【図9】この発明の第三の実施形態の定常動作を説明するフローチャートである。

【図10】この発明の第三の実施形態の定常動作を説明するタイムチャートである。

【図11】この発明のスイッチング電源装置の第四の実施形態を示す回路図である。

【図12】この発明の第四の実施形態の定常動作を説明するフローチャートである。

【図13】この発明の第四の実施形態の通常動作を説明するタイムチャートである。

【図14】この発明のスイッチング電源装置の第五の実施形態を示す回路図である。

【図15】この発明のスイッチング電源装置の第六の実施形態を示す回路図である。

【図16】この発明のスイッチング電源装置の第七の実施形態を示す回路図である。

【図17】この発明のスイッチング電源装置の第八の実施形態を示す回路図である。

【図18】この発明のスイッチング電源装置の第九の実施形態を示す回路図である。

【図19】この発明のスイッチング電源装置の第十の実施形態を示す回路図である。

【図20】この発明のスイッチング電源装置の第十一の実施形態を示す回路図である。

【図21】この発明の第十一の実施形態の定常動作を説明するフローチャートである。

【図22】この発明のスイッチング電源装置の第十二の実施形態を示す回路図である。

【図23】この発明の第十二の実施形態の定常動作を説明するタイムチャートである。

【図24】制御関数式の他の変形例のグラフ(a)と不適切な制御関数式の例を示すグラフ(b)である。

【発明を実施するための形態】

【0024】

以下、この発明のスイッチング電源装置の第一の実施形態について、図1〜図5に基づいて説明する。第一の実施形態のスイッチング電源装置10は、入力直流電源12から供給される入力電圧をオン・オフする主スイッチング素子14と、主スイッチング素子14の出力とグランドの間に接続され、主スイッチング素子14と相補的にオン・オフする整流素子16と、整流素子16の両端に生じる断続電圧を平滑するローパスフィルタ構成の平滑インダクタ18及び平滑コンデンサ20を備え、平滑コンデンサ20の両端に発生する直流の出力電圧が負荷22に供給される。主スイッチング素子14と整流素子16は、ここではN−chのMOS型FETが用いられ、出力電圧の定電圧化制御を行う制御回路24が出力する所定の時比率の駆動パルスによってオン・オフ駆動される。

【0025】

これらの構成は降圧チョッパ回路と呼ばれる一般的な電力変換回路であり、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を行うと共に、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間も、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって負荷22に電力供給し続ける動作を行う。

【0026】

制御回路24は、複数のアナログ/デジタル変換器(以下、A/D変換器と称す)26a,26b、演算手段28、及び駆動パルス生成手段30を備えている。A/D変換器26aは、入力電圧を検出したアナログ情報が入力され、主スイッチング素子14のスイッチング周期に同期したタイミングであって、主スイッチング素子14がオンの期間又は平滑インダクタ18が励磁エネルギーを放出している期間における所定のタイミングごとにサンプリングし、デジタル情報の入力電圧信号Viに変換して出力する。A/D変換器26bは、出力電圧を検出したアナログ情報が入力され、同様のサンプリング周期でデジタル情報の出力電圧信号Voに変換して出力する。

【0027】

演算手段28には、出力電圧と出力微分値を変数として含み、当該2つの変数相互の関係を規定する制御関数式が定義されている。この制御関数式は、出力電圧の定電圧化の目標値等を定数として含み、出力電圧の一つの値に対応する出力微分値が一つだけ存在する連続関数式であって、出力電圧が目標値よりも低い範囲にあるときは対応する出力微分値が正の値になり、出力電圧が目標値よりも高い範囲にあるときは対応する出力微分値が負の値になり、出力電圧が目標値に等しいときは対応する出力微分値がゼロになる、という関係を規定する。

【0028】

ここでは、制御関数式は負の傾きを有する一次関数式であり、具体的には、出力電圧と出力微分値との関係を式(6)のように規定する。

【数6】

式(6)において、Voは出力電圧、Vdは出力微分値である。τは正の定数であり、(−1/τ)が傾きである。Vrefは、出力電圧を定電圧化する目標値である。また、出力微分値Vdは、平滑コンデンサ20に流れるコンデンサ電流Icを容量Cで除算したものに相当する。

【0029】

演算手段28は、A/D変換器26a,26bから、上記のサンプリング周期で、入力電圧を検出した入力電圧信号Vi、出力電圧を検出した出力電圧信号Voをサンプリングする。そして、当該2つの信号等に基づいて所定の演算処理を行い、次回のサンプリングタイミングで検出されるであろう出力電圧Vo及びその時の出力微分値Vdの関係が式(6)を充足するように、当該サンプリング以降の主スイッチング素子14のオン時間とオフ時間を算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるように、オン時間及びオフ時間を算出する。具体的な演算処理の内容については、後の動作説明の中で述べる。

【0030】

駆動パルス生成手段30は、演算手段28が決定したオン時間及びオフ時間(スイッチング周期及び主スイッチング素子がオンする時比率δ)に基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。駆動パルスV14は、一定のスイッチング周期Tを有し、時比率δの期間は主スイッチング素子14をオンさせるハイレベルを示し、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間は整流素子16をオフさせるローレベルを示し、その他の期間はハイレベルを示す。詳しくは、後の動作説明の中で述べる。

【0031】

以下、スイッチング電源装置10の動作について説明する。ここで、制御回路24で行われる各種の演算処理等に要する時間は十分短く無視できるものとする。図2、図3は、スイッチング電源装置10に入力が投入された後、定常動作を行なっている様子を示している。演算手段28が各信号をサンプリングする周期はスイッチング周期と等しくTであり、サンプリング周期Tごとにt(k−1),t(k),t(k+1)、t(k+2)のタイミングでサンプリングを行う。

【0032】

なお、スイッチング電源装置10は、定常動作中においても、比較的小さな外乱(例えば、環境温度の変化など)の影響により、主スイッチング素子14のオン時間及びオフ時間がスイッチング周期毎に微妙に変化する。図3では、定常動作を説明する便宜のため、その微妙な変化を誇張して現わしてある。

【0033】

まず、図2に示すように、演算手段28がt(k)のタイミングで、自らがt(k)以前のタイミングに決定した時比率δ(k−1)を取得し、同じく、自らがt(k)以前のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS11)。同じくt(k)のタイミングで、演算手段28が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS12)。そして、サンプリングした信号Vi(k),Vo(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)及び出力電圧信号Vo(k−1)に基づいて所定の演算処理を行い、主スイッチング素子14の次の時比率δ(k)を算出する(ステップS13)。時比率δ(k)は、式(7)のように定義されている。

【数7】

Tはスイッチング周期であり、ton(k),toff(k)は主スイッチング素子14のオン時間とオフ時間である。

【0034】

以下、演算手段28が時比率δ(k)を算出するための演算処理の内容を説明する。平滑コンデンサ20に流れるコンデンサ電流Icの傾きは平滑インダクタ18のインダクタンスLの逆数に比例するため、次のサンプリングタイミングt(k+1)におけるコンデンサ電流Ic(k+1)は、t(k)のタイミングでサンプリングした各信号と、ton(k)及びtoff(k)を用いて、式(8)のように表すことができる。

【数8】

式(8)のオン時間ton(k)とオフ時間toff(k)をスイッチング周期Tと時比率δ(k)に置き換えて表すと式(9)のようになり、同様に式(10)が得られる。

【数9】

【数10】

【0035】

また、次のサンプリングタイミングt(k+1)における出力電圧Vo(k+1)は、式(11)のように表わすことができ、同様に式(12)が得られる。

【数11】

【数12】

【0036】

そして、式(9)〜式(12)からコンデンサ電流Ic(k+1),Ic(k),Ic(k−1)を消去すると、式(13)が得られる。同様に、式(9)〜式(12)からコンデンサ電流Ic(k),Ic(k−1)及びVo(k+1)を消去すると、式(14)が得られる。

【数13】

【数14】

ここで、式(13),(14)のu(k),u(k−1)は、式(15)に示すように定義した複合信号であり、a1,a2,b1,b2は、スイッチング周期T、インダクタンスL、容量Cという複数の回路定数を組み合わせて成る複合定数であり、それぞれ式(16)〜式(18)のように定義されている。

【数15】

【数16】

【数17】

【数18】

【0037】

上述したように、演算手段28は、次回のサンプリングタイミングt(k+1)で検出されるであろう出力電圧Vo及びその時の出力微分値Vdが式(6)の関係を充足するように時比率δ(k)を決定する。式(6)の制御関数式にサンプリングタイミングの概念を盛り込み、かつ、出力微分値Vdをコンデンサ電流Ic及び容量Cで表わすと、式(19)を導出することができる。

【数19】

そして、式(19)に式(13),(14)を代入することによってコンデンサ電流Ic(k+1)と出力電圧Vo(k+1)を消去して整理すると、時比率δ(k)を算出する式(20)が得られる。

【数20】

ここで、sは(−T/τ)である。式(20)によれば、当初からデフォルト設定されている回路定数等を除き、δ(k)を算出するのに必要な情報は、入力電圧Vi(k)、出力電圧Vo(k),Vo(k−1)、及び、入力電圧信号Vi(k−1)と時比率δ(k−1)との積である複合信号u(k−1)である。これらは、いずれもサンプリングタイミングt(k)が経過した時点で既知の情報であり、式(20)に基づいて時比率δ(k)を算出することが可能であることが分かる。

【0038】

このように、演算手段28は、ステップS13において、ステップS11,S12で入手した信号等を式(20)に代入することによって、次のサンプリングタイミングt(k+1)までの時比率δ(k)を算出する。

【0039】

次に、駆動パルス生成手段30が、ステップS13で決定した時比率δ(k)に基づいて、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する(ステップS14)。駆動パルスV14は、サンプリング周期Tの中間時点を挟んで前後に等しい期間が時比率δ(k)の期間に設定され、当該期間は主スイッチング素子14をオンさせるハイレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該時比率δ(k)の期間は整流素子16をオフさせるローレベルを示す。

【0040】

スイッチング電源装置10は、ステップS11〜S14を繰り返すことによって、出力電圧が目標値Vrefに等しくなるようにPWM制御される。

【0041】

次に、スイッチング電源装置10の過渡的な動作について説明する。ここで、駆動パルス生成手段30が生成可能な駆動パルスV14は、オンの最大時比率δmaxと最小時比率δminが設定されている。最大時比率δmaxは、電力変換回路の安全性を向上させたり、各機能ブロックの同期をとって適正に動作させたりする目的で、100%よりも狭い値、例えば、60〜95%程度に設定することが考えられる。

【0042】

動作を停止しているスイッチング電源装置10に入力直流電源12が投入され、出力電圧が目標値Vrefに達するまでの過渡的な動作を、図4に示す。図4(a)は、横軸が出力電圧信号Vo、縦軸が出力微分値Vdのグラフであり、破線が式(6)の制御関数式を示す直線である。スイッチング電源装置10が停止しているとき、出力電圧信号Voはゼロである。そして、入力が投入されると、出力電圧が上昇を開始し、出力電圧信号Vo及び出力微分値Vdが実線で示す軌跡を辿って変化し、出力電圧信号Voが目標値Vrefに等しくなって安定する。

【0043】

入力投入直後の期間Aは、図4(b)に示すように、出力電圧信号Voと目標値Vrefとの差が大きいので、式(20)を用いて算出される時比率δ(k)は、オンの最大時比率δmaxを超えてしまう。駆動パルス生成手段30は、演算手段28で算出された時比率δ(k)が最大時比率δmaxよりも大きいときは、一律に最大時比率δmaxの駆動パルスV14を出力する。従って、期間Aは、最大時比率δmaxという非常に大きな制御量によって、出力電圧が急速に上昇する。

【0044】

期間Bになると、出力電圧信号Voと目標値Vrefとの差が比較的小さくなり、式(20)を用いて算出される時比率δ(k)が最大時比率δmax以下の値まで小さくなる。すると、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動し、出力電圧信号Vo及び出力微分値Vdの関係がグラフの破線に沿って(すなわち、式(6)の関係を満たしながら)変化する。詳しくは、スイッチング周期Tごとに、図4(c)に示す動作が行われる。式(6)は、いわゆる一次遅れ系の制御を表す制御関数式なので、出力電圧信号Voは、図4(b)に示すように、定数τを時定数とする指数関数の曲線を描きながら上昇する。そして、期間Cになると、出力電圧信号Voと目標値Vrefとの差がなくなり、図2、図3で説明した定常動作を行う。

【0045】

入力急変や負荷急変のときの過渡的動作も、上述した入力投入のときの動作と基本的に同様である。例えば、定常動作を行っている最中に入力電圧が急激に上昇したり負荷が急激に軽くなったりすると、出力電圧が上昇して、一時的に出力電圧信号Vo及び出力微分値Vdが式(6)を充足しなくなる。出力電圧信号Voが上昇して目標値Vrefとの差が大きくなると、式(20)を用いて算出される時比率δ(k)は、オンの最小時比率δminよりも小さな値(例えば、マイナスの値)になる。駆動パルス生成手段30は、算出された時比率δ(k)が最小時比率δminよりも小さいときは、一律に最小時比率δmin(例えばゼロ%)の駆動パルスV14を出力する。従って、入力電圧が急激に上昇した直後の期間等は、一律に最小時比率δminで動作し、入力からの電力供給を最小限に抑えることによって、出力電圧を急速に低下させようとする。

【0046】

その後、出力電圧信号Voと目標値Vrefとの差が比較的小さくなり、式(20)を用いて算出される時比率δ(k)がオンの最小時比率δmin以上の値になり、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動する。そして、出力電圧信号Vo及び出力微分値Vdがグラフの破線に沿って変化し、出力電圧信号Voと目標値Vrefとの差がなくなって、図2、図3で説明した定常動作を行う。

【0047】

以上説明したように、スイッチング電源装置10は、制御回路24の演算手段28に、制御関数式である式(6)が定義され、出力電圧と出力電圧の変化を示す出力微分値とを変数にとり、出力電圧の目標値Vrefを介して所定の関係を規定する。そして、演算手段28は、入力電圧信号Vi、出力電圧信号Voをサンプリングし、式(6)を充足するように導出された式(20)を用いて、オン時間及びオフ時間を決定する時比率δを算出する。従って、計算回数が多い微分計算による動作遅れが解消され、シンプルで安価な制御回路で高速応答特性を実現することができる。また、入力電圧や出力電圧が急変したとき、その急変の情報が即座に演算処理に反映されるので、入力急変や負荷急変に対する応答が速い。また、式(20)で算出した時比率δが最小時比率δminから最大時比率δmaxの範囲にないときは、主スイッチング素子のオンの時比率が一律に最小時比率δmin又は最大時比率δmaxに設定され、出力電圧と目標値の偏差を小さくするための制御量が瞬時に最大になる。

【0048】

さらに、演算手段28が算出する時比率δ(k)は、出力電圧信号Voと出力微分値Vdが式(6)の直線関係を充足するように変化するため、出力電圧が所定の目標値Vrefに達して定常動作に入るまでの過程で(例えば、図4における期間A,B)、出力電圧にオーバーシュートや振動が発生しない。

【0049】

また、式(6)の制御関数式を変更することによって、入力投入時の出力電圧等の変化の具合を容易に調整することができる。例えば、式(6)の係数τを大きめに変更すれば、図4(a)の破線の傾きが小さくなって短時間で期間Aが終了するので、コンデンサ電流(Icに相当)のピーク値が小さくなり電子部品のストレスが軽減され、同時に、出力電圧の上昇速度が緩やかになって期間Bが長くなり、スイッチング電源装置10の起動時間が長くなる。

【0050】

また、式(6)に条件を加え、出力電圧信号Voと目標値Vrefの差がεを超える範囲では、出力微分値Vdが一定の値Vddになるよう規定することもできる。その場合の制御関数式は、式(21)〜式(23)のように表される。

【数21】

【数22】

【数23】

演算手段28に式(21)〜式(23)の制御関数式が定義されると、上記の式(20)に相当する時比率δ(k)の演算式が3種類になり、出力電圧信号Voの値によって使い分けることになる。図5に示すように、入力投入直後の期間Aは、該当する一つの演算式から求まる時比率δ(k)がオンの最大時比率δmaxを超えるので、一律に最大時比率δmaxの駆動パルスV14を出力するが、出力電圧信号Vo及び出力微分値Vdの関係が、短時間のうちに式(21)〜式(23)を示す破線上に達して期間B1に移行する。従って、コンデンサ電流(Icに相当)のピーク値を、比較的小さな値に制限することができる。

【0051】

期間B1,B2は、期間ごとに該当する演算式が選択され、選択された演算式から時比率δ(k)を求める。ここで求まる時比率δ(k)は、最大時比率δmax以下の値になるので、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動し、出力電圧信号Vo及び出力微分値Vdの関係がグラフの破線に沿って変化する。そして、期間Cになると、出力電圧信号Voと目標値Vrefとの差がなくなり、図2、図3で説明した定常動作が行われる。

【0052】

このとき、式(22)の係数τを調節すれば、コンデンサ電流のピーク値を小さく抑えつつ、期間B1,B2の時間を短くすることができる。例えば、係数τを小さな値に設定することによって、図4における期間Bと同等の時間に設定することも可能である。すなわち、式(6)に代えて式(21)〜式(23)を制御関数式に用いれば、スイッチング電源装置10の起動時間とコンデンサ電流のピーク値を、各々独立に調整することができる。

【0053】

次に、この発明の第二の実施形態のスイッチング電源装置40について図6、図7を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置40は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器42a,42b、演算手段44及び駆動パルス生成手段46が設けられている。

【0054】

A/D変換器42a,42bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期の半分の周期ごとに行われ、そのタイミングは、主スイッチング素子14がオンの期間、及び、平滑インダクタ18がオンの期間に蓄えられた励磁エネルギーを出力に放出している期間における任意のタイミングである。ここで、「励磁エネルギーを出力に放出している」状態とは、当該励磁エネルギーを放出する電流が、出力から平滑インダクタ18の向きに流れている状態も含む。

【0055】

演算手段44には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。しかし、演算手段28と異なり、入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器42a,42bから、上述したスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングする。そして、当該2つの信号等に基づいて、式(20)に類似する所定の演算を行い、次回のサンプリングタイミングまでの期間の時比率δを算出する。

【0056】

駆動パルス生成手段46は、演算手段44が決定した時比率δに基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。しかし、駆動パルスV14は、上記駆動パルス生成手段30のものとは異なり、スイッチングの1周期Tの中の2回目のサンプリングタイミングを挟んで前後の期間を主スイッチング素子14のオン期間とするパルス電圧であって、時比率δの期間は主スイッチング素子14をオンさせるハイレベル、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間はローレベル、その他の期間は整流素子16をオンさせるハイレベルを示す。

【0057】

上記の演算手段44及び駆動パルス生成手段46の場合、サンプリングが、平滑インダクタ18に電流が流れていない期間(電流ゼロ期間)中に行われると、出力微分値Vdを利用した式(6)に基づく出力の制御が不能になる。しかし、スイッチング電源装置40は、スイッチング電源装置10と同様に、主スイッチング素子14及び整流素子16として双方向に導通可能なN−chのMOS型FETが使用されているので、例えば負荷22に供給する出力電流が小さくなって臨界点以下になっても、平滑インダクタ18は電流を連続して流し続け、上記の電流ゼロ期間は生じない。従って、スイッチング周期Tにおける任意のタイミングでサンプリングを行うことができる。

【0058】

以下、スイッチング電源装置40の動作について説明する。入力が投入された後の定常動作を示すフローチャートは、上記スイッチング電源装置10で説明した図2と同様である。その結果、図7のタイムチャートに示すように、スイッチング周期Tの半分の周期ごとに時比率δが可変調整される。従って、上記スイッチング電源装置10と比較すると、時比率δを調整する頻度が2倍となり、出力電圧の制御の遅れが半分になるので、制御の応答が一段と高速化される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。

【0059】

次に、この発明の第三の実施形態のスイッチング電源装置50について図8〜図10を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置50は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器52a,52b、演算手段54及び駆動パルス生成手段56が設けられている。

【0060】

A/D変換器52a,52bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期ごとに行われ、そのタイミングは、主スイッチング素子14がオフからオンに転じるタイミングである。

【0061】

演算手段54には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。しかし、演算手段28と異なり、入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器52a,52bから、上述したスイッチング周期ごとに主スイッチング素子14がオンに転じるタイミングでサンプリングする。そして、当該2つの信号等に基づいて所定の演算を行い、時比率δを算出する。

【0062】

スイッチング電源装置50の制御回路24は、比較的安価で汎用的なデジタルICを用いて構成されているため、演算手段54が行う演算処理等に要する時間が無視できない。従って、高速演算可能なデジタルIC等で構成された上記の演算手段28の場合は、次回のサンプリングタイミングまでの期間の時比率δを算出したのに対して、この演算手段54の場合は、次回のサンプリングタイミング後の期間の時比率δを算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるようにオンの時比率δを算出する。

【0063】

駆動パルス生成手段56は、演算手段54が決定した時比率δに基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。しかし、駆動パルスV14は、上記駆動パルス生成手段30のものとは異なり、サンプリングのタイミングから開始する時比率δの期間を主スイッチング素子14のオン期間とするパルス電圧であり、時比率δの期間は主スイッチング素子14をオンさせるハイレベル、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間はローレベル、その他の期間は整流素子16をオンさせるハイレベルを示す。

【0064】

以下、スイッチング電源装置50の動作について説明する。図10は、スイッチング電源装置50に入力が投入された後、定常動作を行なっている様子を示している。演算手段54が各信号をサンプリングする周期はスイッチング周期と等しくTであり、主スイッチング素子14がオフからオンに転じるサンプリング周期Tごとにt(k−1),t(k),t(k+1)、t(k+2)のタイミングでサンプリングを行う。

【0065】

まず、図9に示すように、演算手段54がt(k)のタイミングで、自らがt(k)以前のタイミングに決定した時比率δ(k),δ(k−1)を取得し、同じく、自らがt(k)以前のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS21)。同じくt(k)のタイミングで、演算手段54が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS22)。その後、時比率δ(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)を上記の式(13)に代入し、t(k+1)のタイミングの出力電圧信号の予測値であるVo1(k+1)を算出する。(ステップS23)。そして、時比率δ(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び予測値Vo1(k+1)を次の式(24)に代入し、次のサンプリングタイミングt(k+1)後の時比率δ(k+1)を算出する(ステップ24)。

【数24】

式(24)は、上記の式(20)のkをk+1とし、k−1をkとして表したものである。ただし、式(24)の右辺の分母に含まれるVi(k)は、本来ならVi(k+1)となるところであるが、t(k)直後のタイミングで入力電圧信号Vi(k+1)は未知なので、既知のVi(k)で代用している。

【0066】

このようにして、演算手段54は、サンプリングタイミングt(k+2)における出力電圧信号Vo及び出力微分値Vdの関係が式(6)を充足するように、タイミングt(k+1)後の時比率δ(k+1)を算出する。なお、スイッチング電源装置50の場合、サンプリングが主スイッチング素子14がオフからオンに転じるタイミングで行うため、コンデンサ電流Icのスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得る。従って、式(24)は、この点を考慮した形に変形することが望ましいが、ここでは説明を省略する。

【0067】

次に、駆動パルス生成手段56が、ステップS24で決定した時比率δ(k+1)に基づいて、タイミングt(k+1)後の駆動パルスV14と駆動パルスV16を生成する(ステップS25)。駆動パルスV14は、時比率δ(k+1)の期間がタイミングt(k+1)から始まるように設定されているので、当該期間に主スイッチング素子14をオンさせるハイレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該時比率δ(k)の期間は整流素子16をオフさせるローレベルを示す。

【0068】

スイッチング電源装置50は、ステップS21〜S25を繰り返すことによって、図10に示す動作を行い、出力電圧が目標値Vrefに等しくなるようにPWM制御される。演算手段54は、次回のサンプリングタイミング後の時比率δを算出するため、上記スイッチング電源装置10と比較すると、制御動作にスイッチングの1周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置50は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路24を構成することができる。

【0069】

次に、この発明の第四の実施形態のスイッチング電源装置60について図11〜図13を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置60は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器62a,62b、演算手段64及び駆動パルス生成手段66が設けられている。

【0070】

A/D変換器62a,62bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期ごとに行われ、そのタイミングは、主スイッチング素子14のスイッチング周期に同期したタイミングであって、主スイッチング素子14がオンの期間又は平滑インダクタ18が励磁エネルギーを放出している期間における所定のタイミングである。ただし、後述するように、演算手段64が決定するスイッチング周期は変化する。

【0071】

演算手段64には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。そして、上述のサンプリングタイミングで入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器62a,62bからサンプリングする。そして、当該2つの信号等に基づいて所定の演算処理を行い、オン時間及びオフ時間を算出する。

【0072】

スイッチング電源装置60の制御回路24は、比較的安価で汎用的なデジタルICを用いて構成されているため、演算手段64が行う演算処理等に要する時間が無視できない。従って、ここでは、次回のサンプリングタイミング後の主スイッチング素子14のオン時間とオフ時間を算出する。また、ここでは、オン時間が一定のPFM制御が行われるようにオフ時間を算出する。従って、スイッチング周期及びサンプリング周期が変化する。

【0073】

駆動パルス生成手段66は、演算手段64が決定したオン時間及びオフ時間に基づき、駆動パルスV14と、駆動パルスV16を生成する。駆動パルスV14は、サンプリング周期の中間時点を挟んで前後に等しい期間が主スイッチング素子14のオン期間になるように設定され、当該オンの期間はハイレベルを示し、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、当該オン期間は整流素子16をオフさせるローレベルを示し、その他の期間はハイレベルを示す。

【0074】

以下、スイッチング電源装置60の動作について説明する。図13は、スイッチング電源装置60に入力が投入された後、定常動作を行なっている様子を示している。演算手段64が各信号をサンプリングする周期は、スイッチング周期と同期してT(k−1),T(k),T(k+1)のように変化する。サンプリングのタイミングは、t(k−1),t(k),t(k+1)、t(k+2)である。

【0075】

まず、図12に示すように、t(k)のタイミングで、演算手段64が、自らt(k)以前のタイミングに決定したオフ時間toff(k),toff(k−1)と、t(k−1)のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS31)。同じくt(k)のタイミングで、演算手段64が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS32)。その後、オフ時間toff(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び過去のオフ時間toff(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)を上記の式(13)に代入し、t(k+1)のタイミングの出力電圧信号の予測値であるVo1(k+1)を算出する。(ステップS33)。ここで、式(13)はtoff,Viを含んでいないが、式(7),(15)を用いてuをtoffとViに展開すれば、予測値Vo1を算出可能であることが分かる。そして、上記の式(24)を用いて、次のサンプリングタイミングt(k+1)後のオフ時間toff(k+1)を算出する(ステップ34)。

【0076】

このようにして、演算手段64は、次のサンプリングタイミングt(k+2)で検出されるであろう出力電圧信号Vo及び出力微分値Vdの関係が式(6)を充足するように、オフ時間toff(k+1)を算出する。

【0077】

次に、駆動パルス生成手段66が、ステップS34で決定したオフ時間toff(k+1)と固定値であるオン時間tonに基づいて、タイミングt(k+1)後における駆動パルスV14と駆動パルスV16を生成する(ステップS35)。駆動パルスV14は、サンプリング周期T(k+1)の中間時点を挟んで前後に等しい期間がオン時間tonの期間に設定され、当該期間は主スイッチング素子14をオンさせるハイレベルを示し、オン時間tonの前後にオフ時間toff(k+1)の半分の期間が各々設けられ、当該期間は主スイッチング素子14をオフさせるローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該オン時間tonの期間はローレベルを示し、その前後のtoff(k+1)の期間は整流素子16をオンさせるハイレベルを示す。

【0078】

スイッチング電源装置60は、ステップS31〜S35を繰り返すことによって、図13に示す動作を行い、出力電圧が目標値Vrefに等しくなるようにPFM制御される。スイッチング電源装置60は、次回のサンプリングタイミング後のオフ時間toffを算出するため、上記スイッチング電源装置10と比較すると、制御動作にスイッチングの1周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置60は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路24を構成することができる。

【0079】

次に、この発明の第五の実施形態のスイッチング電源装置70について、図14に基づいて説明する。ここで、第三の実施形態のスイッチング電源装置50と同様の構成は、同一の符号を付して説明する。スイッチング電源装置70は、上記スイッチング電源装置50と同様に、一般的な降圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を行うと共に、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを放出して出力の負荷22に電力供給する動作を行う。

【0080】

しかし、スイッチング電源装置70は、MOS型FETの整流素子16に代えて、グランドから主スイッチング素子14及び平滑インダクタ18の接続点に向けて導通可能なダイオードである整流素子72が設けられ、制御回路24に代わる制御回路74は、駆動パルス14のみを出力するよう構成されている。整流素子72は一方向にしか導通しないので、負荷22に供給する出力電流が小さくなって臨界点以下になると、平滑インダクタ18の電流が連続せず、電流ゼロ期間が生じる。

【0081】

制御回路74は、上記スイッチング電源装置50の制御回路24の動作と異なり、図示しない演算手段等が、スイッチング周期ごとに主スイッチング素子14がオフに転じるタイミングでサンプリングを行って時比率δを算出する。このサンプリングタイミングは、電流ゼロ期間ではないので、出力微分値Vdを利用した式(6)に基づく出力制御が不能になることはない。また、出力電流が小さくなって臨界点以下になると、式(24)が成立しなくなるので、式(24)と異なる特有の演算式に基づいて時比率δを算出する。そして、図示しない駆動パルス生成手段が、サンプリングのタイミングから開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する動作を行う。制御回路74の上記以外の動作、すなわち、次回のサンプリングタイミング後の期間の時比率δを算出し、その時比率δはスイッチング周期一定の条件の下で算出される(PWM制御を行う)という動作は、スイッチング電源装置50の制御回路24と同様である。

【0082】

以上の構成を備えたスイッチング電源装置70は、整流素子72としてダイオードが使用されているが、上記のスイッチング電源装置50と同様の優れた作用効果を奏する。ただし、スイッチング電源装置70は、いわゆる電流ゼロ期間が存在するため、図6で説明した第二の実施形態のスイッチング電源装置40のように、制御回路74に設けられた図示しない演算手段等が、入力電圧信号Vi等のサンプリングをスイッチング周期の半分の周期ごとに行い、スイッチングの1周期の中の2回目のサンプリングタイミングを挟んで前後の期間を主スイッチング素子14のオン期間とする、という制御回路24の構成を適用することができないので注意が必要である。

【0083】

次に、この発明の第六の実施形態のスイッチング電源装置76について、図15に基づいて説明する。ここで、上記スイッチング電源装置70と同様の構成は、同一の符号を付して説明する。スイッチング電源装置76は、上記スイッチング電源装置70と異なり、一般的な昇圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。また、主スイッチング素子14のオフ期間は、入力直流電源12から出力の負荷22へ電力供給も同時に行われる。

【0084】

スイッチング電源装置76は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止する点で、上記スイッチング電源装置70と動作が異なる。従って、後述する制御回路78の演算手段等がサンプリングを行うタイミングを主スイッチング素子のオフ期間に設定しないと、出力の制御が不能になる。さらに、整流素子72は一方向にしか導通しないので、負荷22に供給する出力電流が小さくなって臨界点以下になると、平滑インダクタ18の電流が連続せず電流ゼロ期間が生じる。従って、当該サンプリングのタイミングを上記の電流ゼロ期間を除いた期間中に設定する必要がある。

【0085】

制御回路78は、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに主スイッチング素子14がオンからオフに転じた直後(平滑インダクタ18が励磁エネルギーを放出している状態)のタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、当該サンプリングタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する。また、当該演算手段が行う演算内容は、降圧チョッパ回路の式(24)等とは異なる昇圧チョッパ回路特有の演算式で表される。特に、コンデンサ電流のスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得るので、この点を考慮した演算式を導出する必要がある。制御回路78の上記以外の動作、すなわち、次回のサンプリングタイミング後の期間の時比率δを算出し、その時比率δはスイッチング周期一定の条件の下で算出される(PWM制御を行う)という動作は、スイッチング電源装置70の制御回路74と同様である。

【0086】

以上の構成を備えたスイッチング電源装置76は、昇圧チョッパ型の電力変換回路を備え、整流素子72にダイオードを用いているが、上記のスイッチング電源装置70と同様の優れた作用効果を奏する。

【0087】

次に、この発明の第七の実施形態のスイッチング電源装置80について、図16に基づいて説明する。ここで、上記スイッチング電源装置76と同様の構成は、同一の符号を付して説明する。スイッチング電源装置80は、上記スイッチング電源装置76と異なり、一般的な昇降圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。

【0088】

スイッチング電源装置80の場合、主スイッチング素子14のオフ期間に、入力直流電源12から出力の負荷22へ電力供給が行われない点で、上記スイッチング電源装置76と動作が異なる。しかし、出力の制御不能状態を回避するための条件は同様であり、後述する制御回路82は、演算手段等がサンプリングを行うタイミングを主スイッチング素子のオフ期間であって、且つ、上記の電流ゼロ期間を除いた期間に設定する必要がある。

【0089】

制御回路82は、上記スイッチング電源装置76の制御回路78と同様に、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに主スイッチング素子14がオンからオフに転じた直後のタイミングでサンプリングを行う。図示しない駆動パルス生成手段は、サンプリングのタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する。また、当該演算手段が行う演算内容は、昇圧チョッパ回路の演算式とは異なる昇降圧チョッパ回路特有の演算式が用いられる。特に、コンデンサ電流のスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得るので、この点を考慮した演算式を導出する必要がある。

【0090】

以上の構成を備えたスイッチング電源装置80は、昇降圧チョッパ型の電力変換回路を備えているが、上記のスイッチング電源装置76と同様の優れた作用効果を奏する。

【0091】

次に、この発明の第八の実施形態のスイッチング電源装置84について、図17に基づいて説明する。ここで、第一の実施形態のスイッチング電源装置10と同様の構成は、同一の符号を付して説明する。スイッチング電源装置84は、上記スイッチング電源装置10の電力変換回路にトランス86、整流側同期整流素子88及び転流側同期整流素子89が追加された、シングルエンディドフォワード型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ、トランス86及び整流側同期整流素子88を介して電力供給を行うと共に、入力直流電源12によって平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間も、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって出力の負荷22に電力供給し続ける動作を行う。従って、整流側同期整流素子88を主スイッチング素子14の駆動パルスV14と同位相のパルス電圧で駆動し、転流側同期整流素子89を駆動パルスV14と逆位相の駆動パルスV16で駆動することによって、上記スイッチング電源装置10と同様の動作で出力電圧が制御される。

【0092】

以上の構成を備えたスイッチング電源装置84は、シングルエンディッドフォワード型の電力変換回路を備えているが、降圧チョッパ型の電力変換回路を備えたスイッチング電源装置10と同様の方法で制御が行われ、同様の優れた作用効果を奏する。

【0093】

次に、この発明の第九の実施形態のスイッチング電源装置90について、図18に基づいて説明する。ここで、第七の実施形態のスイッチング電源装置80と同様の構成は、同一の符号を付して説明する。スイッチング電源装置90は、上記スイッチング電源装置80の電力変換回路にトランス86が追加された、フライバック型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によってインダクタンス素子であるトランス86を励磁する。そして、主スイッチング素子14のオフ期間に、トランス86に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。

【0094】

制御回路82は、上記スイッチング電源装置80の制御回路82と同様の動作を行う。すなわち、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに、主スイッチング素子14がオンからオフに転じた直後のタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、サンプリングのタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する動作を行う。

【0095】

以上の構成を備えたスイッチング電源装置90は、フライバック型の電力変換回路を備えているが、昇降圧チョッパ型の電力変換回路を備えたスイッチング電源装置80と同様の方法で制御が行われ、同様の優れた作用効果を奏する。

【0096】

次に、この発明の第十の実施形態のスイッチング電源装置92について、図19に基づいて説明する。ここで、第五の実施形態のスイッチング電源装置70と同様の構成は、同一の符号を付して説明する。スイッチング電源装置92は、2つの主スイッチング素子14a,14b、カップリングコンデンサ94、トランス86、ダイオードである2つの整流素子72a,72b、平滑インダクタ18及び平滑コンデンサ20で構成された、一般的なハーフブリッジ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14aと14bが制御回路96から駆動パルスV14a,V14bを受け、スイッチング周期ごとに交互にオン・オフ制御される。主スイッチング素子14a,14bのオン期間は、入力直流電源12から出力の負荷22へ、トランス86及び整流素子72a,72bを介して電力供給を行うと共に、入力直流電源12によって平滑インダクタ18を励磁する。主スイッチング素子14a,14bのオフ期間は、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって出力の負荷22に電力供給する動作を行う。

【0097】

制御回路96は、上記スイッチング電源装置70の制御回路74の動作と同様に、出力の制御不能状態を回避すべく、図示しない演算手段等が、スイッチング周期ごとに主スイッチング素子14a又は14bがオフに転じるタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、サンプリングのタイミングから開始する期間を主スイッチング素子14a又は14bのオフ期間とする駆動パルスV14a,V14bを生成する動作を行う。

【0098】

以上の構成を備えたスイッチング電源装置92は、複数の主スイッチング素子を有するハーフブリッジ型の電力変換回路を備えているが、降圧チョッパ型の電力変換回路を備えたスイッチング電源装置70と同様の方法で制御が行われ、同様の優れた作用効果を奏する。また、プッシュプル型、フルブリッジ型、カスケードフォワード型等の多石式電力変換回路を備えたスイッチング電源装置も、スイッチング電源装置92と同様の考え方で構成することができる。

【0099】

次に、この発明の第十一の実施形態のスイッチング電源装置98について、図20に基づいて説明する。ここで、上記スイッチング電源装置40と同様の構成は、同一の符号を付して説明する。スイッチング電源装置98の電力変換回路の構成は、図6に示すスイッチング電源装置40と同じく降圧チョッパ型である。

【0100】

制御回路100は、A/D変換器42a,42b、オブザーバ102、演算手段104、及び駆動パルス生成手段46で構成されている。すなわち、図4に示す上記スイッチング電源装置40の制御回路24の構成に加え、オブザーバ102が新設され、演算手段44に代えてオブザーバ102に対応した動作を行う演算手段104が設けられている。また、平滑インダクタ18のコイルの寄生抵抗18aを回路図上に明記した。この寄生抵抗18aは、出力電流Ioが流れる経路に存在する寄生インピーダンスの一種でありこの実施形態では、出力電圧精度を向上させるため、寄生抵抗18aに起因する電圧降下成分Vofsを含めて、演算手段104が時比率δを算出する。

【0101】

A/D変換器42a,42bには、入力電圧及び出力電圧を検出したアナログ情報が入力され、所定のタイミングでサンプリングされ、デジタル情報に変換された入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期の半分の周期ごとに行われ、そのタイミングは、主スイッチング素子14がオンの期間、又は、平滑インダクタ18がオンの期間に蓄えられた励磁エネルギーを出力に放出している期間における任意のタイミングである。

【0102】

オブザーバ102は、観測器とも呼ばれる状態変数の推定手段であって、特定の回路部分の検出値(測定値)を利用して、検出困難な箇所の動作状態を推定する機能を備えている。ここでは、検出が比較的容易な入力電圧信号Vi及び出力電圧信号Voと、当該サンプリングの直前に演算手段104が決定した時比率δとに基づいて、次のサンプリングタイミングで検出されるであろう出力電圧信号の推定値Vo2、及び、次のサンプリングタイミングにおける電圧降下成分の推定値Vofs2を算出する。

【0103】

スイッチング電源装置98の制御回路100は、比較的安価な汎用デジタルICを用いて構成されているため、演算手段104が行う演算処理等に要する時間が無視できない。従って、この演算手段104は、次回のサンプリングタイミング後の期間の時比率δを算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるようにオンの時比率δを算出する。

【0104】

演算手段104は、検出値である入力電圧信号Viと、オブザーバ102の推定値である出力電圧信号Vo2及び電圧降下成分Vofs2を、上述したスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングする。そして、これらの信号に基づいて所定の演算処理を行い、次回のサンプリングタイミング後の期間の時比率δを算出する。また、演算手段104は、以前に算出した時比率δ等をオブザーバ102に向けて出力する働きもする。

【0105】

以下、スイッチング電源装置98の定常動作について、図21のフローチャートに基づいて説明する。ここで、スイッチング電源装置98の動作を示すタイムチャートは、上記スイッチング電源装置40の動作を示す図7とほぼ同様に表されるので、参照するとよい。

【0106】

まず、オブザーバ102がt(k)のタイミングで、t(k)以前のタイミングに演算手段104が決定した時比率δ(k),δ(k−1)を取得し、同じく、t(k)以前のタイミングに演算手段104がサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS41)。同じくt(k)のタイミングで、オブザーバ102が、検出値である入力電圧信号Vi(k)及び出力電圧信号Vo(k)をサンプリングする(ステップS42)。そして、オブザーバ102が、入力電圧信号Vi(k)、出力電圧信号Vo(k)、時比率δ(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)に基づいて、t(k+1)のタイミングの出力電圧信号の推定値Vo2(k+1)と電圧降下成分の推定値Vofs2(k+1)を算出する(ステップS43)。

【0107】

その後、演算手段104が、時比率δ(k)、入力電圧信号Vi(k)及び出力電圧信号Vo(k)と、推定値Vo2(k+1)及び電圧降下成分Vofs(k+1)とを、次の式(25)に代入し、次のサンプリングタイミングt(k+1)後の時比率δ(k+1)を算出する(ステップS44)。

【数25】

【数26】

式(25)は、右辺最終項に電圧降下成分Vofsを含んでおり、電圧降下成分Vofsは式(26)のように定義され、平滑インダクタ18の寄生抵抗18aの抵抗値R等で表わされる。式(26)は、上述の式(2)である。式(25)は、式(8)の「Vo(k)」を「Vo(k)+R・Io」に置き換え、上記と同様の考え方で導出できる。ここでは、出力電流Io及び寄生抵抗18aの抵抗値Rを、平滑インダクタ18のインダクタンスLや平滑コンデンサ20の容量C等の回路定数と同等に取り扱っており、電圧降下成分Vofsは複合定数として扱うことができる。

【0108】

そして、ステップS44の後、駆動パルス生成手段46が、演算手段104が算出した時比率δ(k+1)に基づき、タイミングt(k+1)後の駆動パルスV14と駆動パルスV16を生成する(ステップS45)。

【0109】

スイッチング電源装置98は、ステップS41〜S45を繰り返すことによって、出力電圧が目標値Vrefに等しくなるようにPWM制御される。演算手段104は、次回のサンプリングタイミング後の時比率δを算出するため、上記スイッチング電源装置40と比較すると、制御動作にスイッチングの半周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、出力電流Ioが流れる経路に存在する寄生抵抗18aに起因する電圧降下成分Vofsも考慮した出力電圧制御が行われるので、出力電圧の精度がさらに向上する。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置40の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置98は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路100を構成することができる。

【0110】

次に、この発明の第十二の実施形態のスイッチング電源装置106について、図22に基づいて説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明する。スイッチング電源装置106の電力変換回路は、上記スイッチング電源装置10と同じく降圧チョッパ回路である。また、制御回路108は、上記スイッチング電源装置10の制御回路24の演算手段28に代えて、演算手段110が設けられている。また、平滑インダクタ18のコイルの寄生抵抗18aを回路図上に明記した。ここでは、寄生抵抗18aに起因する電圧降下成分Vofsが大きいため出力電圧制御への影響が無視できず、出力電圧精度を向上させるため、演算手段110が時比率δを算出するときに考慮される。

【0111】

演算手段110は、上記スイッチング電源装置10の制御回路28と同様の動作を行い、さらに、演算手段110にデフォルト値として初期設定されている回路定数について定期的にパラメータ推定を行って更新し、回路定数の個体差、温度による変化又は経時的な変化を考慮した出力電圧制御を行う。回路定数とは、ここでは主スイッチング素子14のスイッチング周期T、平滑インダクタ18のインダクタンスL、平滑コンデンサ20の容量C、出力電流Io、寄生抵抗18aの抵抗値R及び電圧降下成分Vofsをいう。

【0112】

ここで、演算手段110に定義されているパラメータ推定用の評価関数J(N)ついて説明する。まず、上記の式(13)に電圧降下成分Vofsを盛り込み、k+1をkに、kをk−1に、k−1をk−2にそれぞれ置き換えて、式(27)を得る。

【数27】

式(27)に含まれる複合定数a1,a2,b1,b2,及び電圧降下成分である複合定数Vofsは、式(16)〜式(18)、式(26)で定義されている。また、u(k−1),u(k−2)は、式(15)と同様のものである。

【0113】

パラメータ推定は、インダクタンスL、容量C等の多数個の回路定数の単位、又はa1,a2等の複合定数の単位でも行うことが可能であるが、ここでは、推定する複合定数の数を少なくして演算回数を減らすことにより、同等の推定精度を維持しつつ、演算手段110の処理の高速化を図っている。

【0114】

式(27)の複合定数a1,a2,b1,b2を個々の回路定数で表わし、式(28)に示す新たな複合定数pを定義すると、式(27)を式(29)のように変形することができる。式(28)は、上述の式(1)である。

【数28】

【数29】

【0115】

式(29)は、左辺に複合定数を含んでおらず、右辺第1項のカッコ内にも複合定数を含んでいない。そこで、左辺全体を、式(30)のように複合信号ν1(k)と表わし、右辺第1項のカッコ内を式(31)のように複合信号ν2(k)と表わす。すると、式(32)が得られる。式(30)、(31)は、上述の式(4)、(5)である。

【数30】

【数31】

【数32】

【0116】

次に、パラメータ推定のための評価関数を定義する。制御回路108の本来の目的は、出力電圧を高精度に制御することである。従って、出力電圧信号Voを基にしてパラメータ推定を行うことが望ましく、特に高精度にパラメータ推定を行うためには、タイミングt(k)における検出値Voa(k)と、それ以前に予測したタイミングt(k)の予測値Vob(k)との差を評価することとし、評価関数Jx(N)を式(33)のように定義する方法が考えられる。

【数33】

この場合、t(1)〜t(N)の各タイミングで得られる予測誤差を二乗したものの平均値を評価関数Jx(N)としている。

【0117】

しかし、制御回路108では、演算手段110の処理の高速化を図るため、複合定数の種類をさらに削減すると共に、単独の出力電圧信号Voの予測誤差に代えて、複数の出力電圧信号を組み合わせた複合信号ν1(k)の予測誤差を用いる。すなわち、複合信号ν1を基にしてパラメータ推定を行うこととし、タイミングt(k)における検出値ν1a(k)と、それ以前に予測したタイミングt(k)の予測値ν1b(k)との差(以下、予測誤差と称す。)を評価するため、式(34)のように評価関数J(N)を定義している。

【数34】

さらに、式(34)は、予測値ν1b(k)を式(32)の右辺に置き換えることによって、式(35)のように表わすことができる。式(35)は、上述の式(3)である。

【数35】

【0118】

このとき、式(34)に含まれるν1a(k)は、式(30)から分かるように、タイミングt(k),t(k−1),t(k−2)にサンプリングした検出値である出力電圧信号Vo(k),Vo(k−1),Vo(k−2)により算出可能である。従って、複合信号ν1a(k)は、現時点の検出値である出力電圧信号Vo(k)の項が含まれるので、式(33)における検出値Voa(k)に相当するものといえる。

【0119】

また、式(35)の複合信号ν2b(k)は、式(31)から分かるように、タイミングt(k−1),t(k−2)にサンプリングした検出値である出力電圧信号Vo(k−1),Vo(k−2),Vi(k−1),Vi(k−2)、及び、タイミングt(k−1),t(k−2)の時比率として算出した時比率δ(k−1),δ(k−2)により算出可能である。従って、複合信号ν2b(k)を含む複合信号ν1b(k)は、現時点の検出値である出力電圧信号Vo(k)を含まず、いずれも過去の検出値等だけから成るので、式(33)における予測値Vob(k)に相当するものといえる。

【0120】

次に、演算手段110が行うパラメータ推定の動作について、図23に基づいて説明する。この実施形態のスイッチング電源装置106は、図1〜図3を用いて説明したように、第一実施形態のスイッチング電源装置10と同様の定常動作を行い、定常動作と並行して演算手段110がパラメータ推定を行う。パラメータ推定は、図23に示すように、スイッチング周期Tよりも十分長い周期Taごとに1回行われ、その1回が期間Tbの間に行われる。

【0121】

期間Tbに入ると、まず、演算手段110が、N個の予測誤差を求めることができるように、期間Tcの間にN回のサンプリング等を行って上記の各信号を取得する。次に、取得した各信号に基づき、N個の予測誤差の二乗の平均値である評価関数J(N)が最小になる複合定数p及びVofsを算出する。そして、タイミングtdになると、従前の複合定数p及びVofsを新たに算出したものに更新する。従って、更新後は新たな複合定数p及びVofsに基づいて出力電圧制御が行われるので、図23に示すように、出力電圧Voが従前の電圧V1から新たな電圧V2に変化する。

【0122】

上記の期間Tbの動作は周期Taごとに繰り返し行われ、定期的に複合定数p及びVofsが更新される。従って、制御回路108は常に適正な複合定数を用いて出力電圧制御を行うことができる。なお、式(35)の評価関数J(N)を使用し、定期的に複合定数p及びVofsを算出する動作は、オフライン最小二乗法を用いたパラメータ推定の一種であるといえる。

【0123】

ここで、スイッチング電源装置106は、図23に示すように、出力電圧信号Vo(1)〜Vo(N)をサンプリングする期間Tcの間、出力電圧Voが電圧V1を挟んで上下に変動している。これは、演算手段110が、上記の定常動作を行うために時比率δを決定するに際して、パラメータ推定を行う期間Tcの間、時比率δを僅かに拡散変動させていることによる。拡散変動とは、図2のフローチャートに従って算出した時比率δをランダム増減させることをいい、この拡散変動によって出力電圧VoをΔVoだけ変動させることができる。従って、この演算手段110を用いて出力電圧Voを意図的に変動させることによって、複合定数p及びVofsの推定を、より高精度に行うことができる。

【0124】

なお、上記のパラメータ推定は、出力電圧Voの変動ΔVoが1m〜10mVもあれば、一定以上の高い精度で行うことができるので、時比率δの拡散変動の幅を必要以上に大きくする必要はない。パラメータ推定の精度がさほど高くなくてよいときは、拡散変動を行わなくても構わない。

【0125】

以上説明したように、この実施形態のスイッチング電源装置106は、第一の実施形態のスイッチング電源装置10と同様の優れた作用効果を得ることができ、さらに、定期的にオフライン最小二乗法を用いたパラメータ推定を行うことによって回路定数の個体差、温度による変化又は経時的な変化を定期的に監視して適正な値に更新するので、高精度な出力電圧制御を継続して行うことができる。

【0126】

また、式(27)と式(33)を用いてパラメータ推定を行うことも可能であるが、その場合、推定する複合定数(a1,a2等)の種類が多くなるので、その分、パラメータ推定の処理にある程度の時間が掛かってしまう。それに対してこの演算手段110は、推定する複合定数が少ない(p,Vofsの2種類のみ)ので、推定の処理を極めて高速に行うことができるという利点がある。

【0127】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。例えば、制御回路の演算手段に定義される制御関数式は、入力投入時等の出力電圧の変化の具合を調節するため、式(6)、式(21)〜式(23)のような直線的な関係式ではなく、図24(a)に示すように曲線的な関係式にしてもよい。ただし、図24(b)のような、出力電圧の1つの値に対応する出力微分値が複数存在する制御関数式を使用すると、上述した演算手段の処理を適正に行うことができない。

【0128】

また、第一から第十の実施形態の説明で述べたように、制御回路の演算手段が主スイッチング素子のオン時間、オフ時間、時比率などを算出するとき、「スイッチング周期を一定にする」等の条件設定をすることが望ましい。それによって、時比率などを算出する演算式が、式(20)のように比較的シンプルな形に表すことができるからである。この発明は、様々な電力変換回路のスイッチング電源装置に適用することができ、上記の条件設定は、個々の電力変換回路の動作に応じて適当な方法を選択することができる。

【0129】

例えば、スイッチング周期が一定になることを条件としてオン時間及びオフ時間を決定するPWM制御(図3、図10)、主スイッチング素子14のオン時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御(図13)、及び、主スイッチング素子14のオフ時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御は、上記実施形態で例示した電力変換回路に適用可能である。特に、主スイッチング素子14のオン時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御(図13)は、いわゆる電流共振回路を備えた電力変換回路等の制御に好適である。

【0130】

また、実施形態として例示していないが、主スイッチング素子14のオフ時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御も可能である。このPFM制御は、いわゆる電圧共振回路を備えた電力変換回路等の制御に好適である。また、スイッチングの1周期に対するオン時間の時比率が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御も可能であり、例えば、上記実施形態で例示した昇圧チョッパ型、昇降圧チョッパ型、又はフライバック型の電力変換回路に適用し、意図的に電流ゼロ期間が生じるように動作させれば、ダイオードで成る整流素子のリカバリ電流の発生を防止し、スイッチングノイズや主スイッチング素子のクロス損失の発生を抑える効果を得ることができる。

【0131】

また、演算手段等がスイッチング周期に同期した周期でサンプリングし、駆動パルス生成手段がそのサンプリング周期の中間点を挟んで前後の期間を主スイッチング素子のオン期間又はオフ期間とする駆動パルスを生成する、という構成は(図3、図13)、演算手段等がサンプリングするタイミングをいわゆる電流ゼロ期間以外の期間に設定することにより、上記実施形態で例示したいずれの電力変換回路にも適用可能である。当該構成によれば、演算手段が時比率などを算出する演算式が、例えば式(20)のように比較的シンプルな一次式の形に表すことができて処理が簡単になり、また、演算手段等で多少の処理時間が生じたとしても、最大時比率Dmaxや最小時比率Dminの設定を適宜調節すれば当該処理時間の影響をマスクすることも可能である。従って、比較的安価な中低速デジタルICで、上記の制御回路を構成することができるという利点がある。

【0132】

また、演算手段等がスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングし、所定の演算を行って次回のサンプリングタイミングまでの期間の時比率δを算出する、という構成は(図6)、演算手段等が主スイッチング素子のオン期間にもサンプリングを行われるので、昇圧チョッパ型、昇降圧チョッパ型、フライバック型等の電力変換回路には適用できないが、降圧チョッパ型、シングルエンディッドフォワード型、ハーフブリッジ型等の電力変換回路に適用が可能である。

【0133】

また、パラメータ推定を行って回路定数又は複合定数を更新する構成は、電力変換回路の形態や定常動作の形態によらず、適用することができる。ただし、上記の式(27)〜式(35)は降圧チョッパ回路に特有の式なので、他の電力変換回路にそのまま適用することができず、個別に式を導出する必要がある。また、パラメータ推定は、上記のオフライン最小二乗法を用いる以外にも、逐次最小二乗法、その他最小二乗法以外の公知の方法を使用してもよい。

【符号の説明】

【0134】

10,40,50,60,70,76,80,84,90,92,98,106 スイッチング電源装置

14,14a,14b 主スイッチング素子

16,72,72a,72b 整流素子

18 平滑インダクタ

20 平滑コンデンサ

24,74,78,82,96,100,108 制御回路

26a,26b,42a,42b,52a,52b,62a,62b A/D変換器

28,44,54,64,104,110 演算手段

30,46,56,66 駆動パルス生成手段

86 トランス

88 整流側同期整流素子

89 転流側同期整流素子

94 カップリングコンデンサ

102 オブザーバ

【技術分野】

【0001】

この発明は、デジタル制御型の制御回路を用いて出力を定電圧化するスイッチング電源装置に関する。

【背景技術】

【0002】

従来から、デジタルプロセッサ等を用いたインテリジェント性の高いデジタル制御型の制御回路を用いて、PWM(Pulse Width Modulation)制御やPFM(Pulse

Frequency Modulation)制御等を行って出力を定電圧化するスイッチング電源装置があった。特に近年は、電源装置の外部環境の急変に対して出力電圧の過渡的な変動を小さくすることが強く求められている。

【0003】

スイッチング電源装置の外部環境が急変する状況として、動作中に入力電圧が急峻に変動したり、負荷の状態が変化し出力電流が急峻に増減したりすることが考えられる。また、停止しているスイッチング電源装置に入力電圧が投入されて起動するときの動作も問題になる。

【0004】

例えば、情報通信機器やサーバ等に用いられるスイッチング電源装置の場合、出力電流がほぼゼロから定格負荷まで急峻に変化する状況が頻繁に起こり得ることから、負荷急変に対する出力電圧制御の高速応答特性が求められる。また、1つの入力電源ラインから多数のボード基板に電圧供給するシステムにおいては、メンテナンス時に他のボード基板が活線挿抜されることによって、システムの電源ラインの負荷状態が変化し、当該電源ラインから電力供給を受けているスイッチング電源装置の入力電圧が急変することが想定される。従って、この種のシステムに用いられるスイッチング電源装置は、入力急変に対する出力電圧制御の高速応答特性が求められる。さらに、一般的な事項として、入力電圧を投入した時、出力電圧がゼロから上昇して所定の出力電圧に達する過程でオーバーシュートや振動が生じると、負荷である電子機器が誤動作したり故障したりするおそれがあるので、スイッチング電源装置は、出力電圧が単調に増加して立ち上がることが求められる。

【0005】

これらの課題を解決するため、例えば特許文献1に開示されているように、動作中の入力電圧に相当する信号(入力電圧信号)、出力電圧に相当する信号(出力電圧信号)、及び当該出力電圧の変化を示す出力電圧微分値に相当する信号(出力微分信号)を取得し、各信号に基づいて所定のデジタル演算処理を行い、主スイッチング素子のオン時間及びオフ時間を決定するスイッチング電源装置が提案されている。このスイッチング電源装置は、制御回路の演算手段に、傾きが負の一次関数等で出力電圧信号と出力微分値の関係を規定する制御関数式が定義されている。演算手段は、主スイッチング素子のスイッチング周期に同期したタイミングで、入力電圧信号、出力電圧信号及び出力微分信号をサンプリングし、以降の主スイッチング素子のオン時間及びオフ時間を、上記の制御関数式を満足するように算出する。そして、演算手段が決定したオン時間及びオフ時間に基づき、駆動パルス生成手段が、主スイッチング素子をオン・オフさせる駆動パルスを生成する。このとき、出力微分信号は、平滑コンデンサの電流を測定するコンデンサ電流検出手段、又は出力電圧信号を微分する微分手段などを通じて入手する。

【先行技術文献】

【特許文献】

【0006】

【特許文献1】特開2011−91974号公報

【発明の概要】

【発明が解決しようとする課題】

【0007】

しかし、特許文献1のスイッチング電源装置の場合、入力電圧信号及び出力電圧信号は、いずれも入力電圧及び出力電圧のアナログ情報を単純にA/D変換器でデジタル化したものであり入手が容易であるが、出力微分信号を入手するのは容易ではない。例えば、平滑コンデンサに流れる電流を測定し、そのアナログ情報をデジタル化して出力微分信号を入手する方法の場合、通常は、電流−電圧変換回路を設け、コンデンサ電流をアナログ/アナログ変換した後、A/D変換器でデジタル化しなければならず、電源装置が大形化したり損失が増加したりする問題があった。また、A/D変換器でデジタル化した出力電圧信号を微分演算して出力微分信号を入手する方法の場合、計算回数の増大により制御の遅れが問題になるので、制御回路を高速動作させるためには、制御回路の機能を削って計算回数を減らしたり、高速動作可能な高価なマイクロコンピュータを使用したりしなければならなかった。

【0008】

この発明は、上記背景技術に鑑みて成されたもので、電源装置の外部環境の急変に対する過渡的な出力電圧の変動を小さくする高速応答特性を有し、小形化、低コスト化が容易なデジタル制御型のスイッチング電源装置を提供することを目的とする。

【課題を解決するための手段】

【0009】

この発明は、オン・オフ動作する主スイッチング素子を含む電力変換回路と、当該オン・オフ動作を制御することによって出力電圧を定電圧化する制御回路とを備えたスイッチング電源装置であって、

前記制御回路は、前記主スイッチング素子のオン時間及びオフ時間を決定する演算手段と、前記主スイッチング素子をオン・オフさせる駆動パルスを生成する駆動パルス生成手段とを有し、

前記演算手段には、出力電圧と、当該出力電圧の変化を示す出力微分値とを変数として含み、当該2つの変数の関係を、出力電圧の一つの値に対応する出力微分値が一つだけ存在する連続関数式であって、出力電圧がその出力電圧を定電圧化する目標値よりも低い範囲にあるときは、対応する出力微分値が正の値になり、出力電圧が目標値よりも高い範囲にあるときは、対応する出力微分値が負の値になり、出力電圧が目標値に等しいときは、対応する出力微分値がゼロになるように規定する制御関数式が定義され、

前記演算手段は、主スイッチング素子のスイッチング周期に同期したタイミングで、入力電圧を検出した入力電圧信号と、出力電圧を検出又は推定した出力電圧信号とをサンプリングし、サンプリングした当該2つの信号に基づいて導出される次回又はそれ以降のサンプリングタイミングにおける出力電圧信号及び出力微分値が前記制御関数式に規定される関係を満たすように、当該サンプリングタイミング以降のスイッチング周期における主スイッチング素子のオン時間及びオフ時間のうちの少なくとも一方を算出する演算処理を行い、

前記駆動パルス生成手段は、上記2つの信号のサンプリングタイミング以降のスイッチング周期において、前記演算手段が決定したオン時間及びオフ時間に基づいて前記主スイッチング素子をオン・オフさせるよう、駆動パルスを生成するスイッチング電源装置である。

【0010】

前記演算手段は、前記各信号のサンプリングと、オン時間及びオフ時間のうちの少なくとも一方を算出する演算処理とを、前記主スイッチング素子のスイッチング周期ごとに行うものでもよい。その場合、前記電力変換回路は、前記主スイッチング素子のオン期間に、入力直流電源から出力への電力供給を止めて入力直流電源によって内蔵するインダクタンス素子を励磁し、前記主スイッチング素子のオフ期間に、前記インダクタンス素子に蓄積された励磁エネルギーを出力に放出して電力供給をする動作を行い、前記演算手段は、前記各信号のサンプリングを、前記インダクタンス素子が励磁エネルギーを放出している期間に行う。あるいは、前記駆動パルス生成手段は、前記各信号のサンプリング周期の中間時点を挟んで前後に等しい期間を前記主スイッチング素子のオン期間とする駆動パルスを生成し、又は、当該サンプリング周期の中間時点を挟んで前後に等しい期間を前記主スイッチング素子のオフ期間とする駆動パルスを生成する。

【0011】

前記電力変換回路は、前記主スイッチング素子のオン期間に、入力直流電源から出力への電力供給をすると共に、入力直流電源によって内蔵するインダクタンス素子を励磁し、前記主スイッチング素子のオフ期間に、前記インダクタンス素子に蓄積された励磁エネルギーを出力に放出して電力供給し続ける動作を行い、前記演算手段は、前記各信号のサンプリングと、オン時間及びオフ時間のうちの少なくとも一方を算出する演算処理とを、前記主スイッチング素子のスイッチング周期の半分の周期で行い、前記駆動パルス生成手段は、スイッチングの1周期の中の2回目のサンプリングタイミングを挟んで前後の期間を前記主スイッチング素子のオン期間とする駆動パルスを生成し、又は、当該2回目のサンプリングタイミングを挟んで前後の期間を前記主スイッチング素子のオフ期間とする駆動パルスを生成するものでもよい。

【0012】

前記制御回路は、状態変数の推定手段であるオブザーバを備え、前記オブザーバは、前記演算手段が入力電圧信号をサンプリングするタイミングで、当該入力電圧信号及び出力電圧を検出した出力電圧信号を入手すると共に、前記演算手段がその直前に決定したオン時間及びオフ時間を入手し、入手した入力電圧信号、出力電圧信号、オン時間及びオフ時間に基づいて、次のサンプリングタイミングにおける出力電圧信号を推定する処理を行い、前記演算手段は、当該入力電圧信号、出力電圧信号、オン時間及びオフ時間と、前記オブザーバが推定した出力電圧信号とをサンプリングし、それらに基づいて上記の演算処理を行う。

【0013】

前記オブザーバは、入手した入力電圧信号、出力電圧信号、オン時間及びオフ時間に基づいて、次のサンプリングタイミングにおける出力電圧信号、及び出力電流が流れる経路に存在する寄生インピーダンスによる電圧降下成分を推定する処理を行い、前記演算手段は、当該入力電圧信号、出力電圧信号及びオン時間及びオフ時間と、前記オブザーバが推定した出力電圧信号及び前記電圧降下成分とをサンプリングし、それらに基づいて上記の演算処理を行うものでもよい。また、前記演算手段に定義された制御関数式は、出力電圧と出力微分値との関係を、負の傾きを有する一次関数で規定されていてもよい。

【0014】

前記演算手段に定義された制御関数式は、出力電圧と目標値の差が所定の値を超える範囲では、出力微分値が出力電圧によらず一定になるよう規定されている。

【0015】

前記演算手段は、オン時間及びオフ時間の双方を、互いの合計時間が一定になるように算出する。あるいは、前記演算手段は、オフ時間を、オン時間が一定になるように算出する。あるいは、前記演算手段は、オン時間を、オフ時間が一定になるように算出するものでも良い。その場合、前記演算手段が決定したオン時間及びオフ時間が、オンの時比率として可変可能な最大時比率を超える関係にあるとき、前記駆動パルス生成手段は、当該最大時比率で前記主スイッチング素子をオン・オフさせる駆動パルスを生成し、前記演算手段が決定したオン時間及びオフ時間が、オンの時比率として可変可能な最小時比率を下回る関係にあるとき、前記駆動パルス生成手段は、当該最小時比率で前記主スイッチング素子をオン・オフさせる駆動パルスを生成する。

【0016】

前記演算手段は、オン時間及びオフ時間の双方を、スイッチング周期に対するオンの時比率が一定になるように算出するものでもよい。その場合、前記演算手段が決定したオン時間及びオフ時間の合計値が、可変可能な最大時間を超えたとき、前記駆動パルス生成手段は、当該最大時間で前記主スイッチング素子をオン・オフさせる駆動パルスを生成し、

前記演算手段が決定したオン時間及びオフ時間の合計値が、可変可能な最小時間を下回ったとき、前記駆動パルス生成手段は、当該最小時間で前記主スイッチング素子をオン・オフさせる駆動パルスを生成する。

【0017】

前記演算手段は、デフォルト値として初期設定されている回路定数についてパラメータ推定を行い、前記演算手段がサンプリングした実際の出力電圧信号と、過去にオン時間及びオフ時間を決定したときに予想した当該サンプリングタイミングにおける出力電圧信号との差が小さくなるように更新する。複数の前記回路定数を組み合わせて成る定数である複合定数が定義され、前記パラメータ推定は、当該複合定数の単位で行われるものでもよい。また、前記回路定数又は前記複合定数に基づく前記パラメータ推定は、オフライン最小二乗法を用いて行われるものでもよい。

【0018】

例えば、前記電力変換回路は、入力電圧を断続する前記主スイッチング素子と、前記主スイッチング素子と相補的にオン・オフする整流素子と、前記整流素子の両端の断続電圧を平滑する平滑インダクタ及び平滑コンデンサとを備えた降圧チョッパ回路であり、

前記演算処理回路には、前記主スイッチング素子のスイッチング周期T、前記平滑インダクタのインダクタンスL、前記平滑コンデンサの容量C、前記出力電流Io、前記平滑インダクタの寄生抵抗の抵抗値Rを用いて次式(1)、(2)で定義される前記複合定数であるp及びVofsがデフォルト値として初期設定され、

【数1】

【数2】

前記演算手段は、電源動作中に前記複合定数p及びVofsをパラメータ推定によって定期的に更新し、

前記パラメータ推定は、前記演算手段が、タイミングt(k),t(k−1),t(k−2)ごとにサンプリングした検出値である出力電圧信号Vo(k),Vo(k−1),Vo(k−2),Vi(k−1),Vi(k−2)、及び、タイミングt(k−1),t(k−2)ごとの時比率として算出したδ(k−1),δ(k−2)の各値を取得し、前記各値を含む以下の式(3)〜式(5)により表される評価関数J(N)が最小になる前記複合定数p及びVofsを算出することによって行われるスイッチング電源装置である。

【数3】

【数4】

【数5】

【0019】

さらに、前記演算手段は、前記パラメータ推定を行うタイミングごとに、上記の演算処理を経て決定されるオン時間及びオフ時間を僅かに拡散変動させ、当該拡散変動によって出力電圧が変動している期間中に各信号のサンプリングを行って、前記パラメータ推定を行うものである。

【発明の効果】

【0020】

この発明のスイッチング電源装置は、検出値である入力電圧信号及び出力電圧信号の2つの信号に基づき、上記制御関数を充足するようにオン時間及びオフ時間等を算出し、主スイッチング素子のオン・オフを制御する。従って、電源装置の外部環境の急変に対する高速応答特性を、シンプルで安価な制御回路によって実現することができる。

【0021】

また、オブザーバを用いて出力電圧信号を推定する構成にすることによって、安価で低速のマイクロコンピュータ等を使用した場合でも、制御回路の動作遅れの影響を最小限に抑えることができる。さらに、出力電流に相当する信号(例えば、上記の電圧降下成分)も合わせてオブザーバが推定する構成にすることによって、出力電流が流れる経路にある寄生インピーダンスの影響を考慮した制御が可能になり、出力電圧制御の精度を向上させることができる。

【0022】

さらに、デフォルト値として初期設定されている回路定数についてパラメータ推定を行い、定期的に更新する構成にすることによって、各回路素子のインピーダンス(抵抗値、インダクタンス、キャパシタンス、半導体の導通抵抗など)の個体差、温度変動、経時変化の影響が確実にキャンセルされ、出力電圧制御をより高精度に行うことができる。

【図面の簡単な説明】

【0023】

【図1】この発明のスイッチング電源装置の第一の実施形態を示す回路図である。

【図2】この発明の第一の実施形態の定常動作を説明するフローチャートである。

【図3】この発明の第一の実施形態の定常動作を説明するタイムチャートである。

【図4】この発明の第一の実施形態の入力投入時の動作を説明する制御関数式のグラフ(a)、タイムチャート(b)、及び、期間Bの動作を説明するグラフ(c)である。

【図5】図4の制御関数式の変形例のグラフ(a)と、そのときの動作を説明するタイムチャート(b)である。

【図6】この発明のスイッチング電源装置の第二の実施形態を示す回路図である。

【図7】この発明の第二の実施形態の定常動作を説明するタイムチャートである。

【図8】この発明のスイッチング電源装置の第三の実施形態を示す回路図である。

【図9】この発明の第三の実施形態の定常動作を説明するフローチャートである。

【図10】この発明の第三の実施形態の定常動作を説明するタイムチャートである。

【図11】この発明のスイッチング電源装置の第四の実施形態を示す回路図である。

【図12】この発明の第四の実施形態の定常動作を説明するフローチャートである。

【図13】この発明の第四の実施形態の通常動作を説明するタイムチャートである。

【図14】この発明のスイッチング電源装置の第五の実施形態を示す回路図である。

【図15】この発明のスイッチング電源装置の第六の実施形態を示す回路図である。

【図16】この発明のスイッチング電源装置の第七の実施形態を示す回路図である。

【図17】この発明のスイッチング電源装置の第八の実施形態を示す回路図である。

【図18】この発明のスイッチング電源装置の第九の実施形態を示す回路図である。

【図19】この発明のスイッチング電源装置の第十の実施形態を示す回路図である。

【図20】この発明のスイッチング電源装置の第十一の実施形態を示す回路図である。

【図21】この発明の第十一の実施形態の定常動作を説明するフローチャートである。

【図22】この発明のスイッチング電源装置の第十二の実施形態を示す回路図である。

【図23】この発明の第十二の実施形態の定常動作を説明するタイムチャートである。

【図24】制御関数式の他の変形例のグラフ(a)と不適切な制御関数式の例を示すグラフ(b)である。

【発明を実施するための形態】

【0024】

以下、この発明のスイッチング電源装置の第一の実施形態について、図1〜図5に基づいて説明する。第一の実施形態のスイッチング電源装置10は、入力直流電源12から供給される入力電圧をオン・オフする主スイッチング素子14と、主スイッチング素子14の出力とグランドの間に接続され、主スイッチング素子14と相補的にオン・オフする整流素子16と、整流素子16の両端に生じる断続電圧を平滑するローパスフィルタ構成の平滑インダクタ18及び平滑コンデンサ20を備え、平滑コンデンサ20の両端に発生する直流の出力電圧が負荷22に供給される。主スイッチング素子14と整流素子16は、ここではN−chのMOS型FETが用いられ、出力電圧の定電圧化制御を行う制御回路24が出力する所定の時比率の駆動パルスによってオン・オフ駆動される。

【0025】

これらの構成は降圧チョッパ回路と呼ばれる一般的な電力変換回路であり、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を行うと共に、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間も、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって負荷22に電力供給し続ける動作を行う。

【0026】

制御回路24は、複数のアナログ/デジタル変換器(以下、A/D変換器と称す)26a,26b、演算手段28、及び駆動パルス生成手段30を備えている。A/D変換器26aは、入力電圧を検出したアナログ情報が入力され、主スイッチング素子14のスイッチング周期に同期したタイミングであって、主スイッチング素子14がオンの期間又は平滑インダクタ18が励磁エネルギーを放出している期間における所定のタイミングごとにサンプリングし、デジタル情報の入力電圧信号Viに変換して出力する。A/D変換器26bは、出力電圧を検出したアナログ情報が入力され、同様のサンプリング周期でデジタル情報の出力電圧信号Voに変換して出力する。

【0027】

演算手段28には、出力電圧と出力微分値を変数として含み、当該2つの変数相互の関係を規定する制御関数式が定義されている。この制御関数式は、出力電圧の定電圧化の目標値等を定数として含み、出力電圧の一つの値に対応する出力微分値が一つだけ存在する連続関数式であって、出力電圧が目標値よりも低い範囲にあるときは対応する出力微分値が正の値になり、出力電圧が目標値よりも高い範囲にあるときは対応する出力微分値が負の値になり、出力電圧が目標値に等しいときは対応する出力微分値がゼロになる、という関係を規定する。

【0028】

ここでは、制御関数式は負の傾きを有する一次関数式であり、具体的には、出力電圧と出力微分値との関係を式(6)のように規定する。

【数6】

式(6)において、Voは出力電圧、Vdは出力微分値である。τは正の定数であり、(−1/τ)が傾きである。Vrefは、出力電圧を定電圧化する目標値である。また、出力微分値Vdは、平滑コンデンサ20に流れるコンデンサ電流Icを容量Cで除算したものに相当する。

【0029】

演算手段28は、A/D変換器26a,26bから、上記のサンプリング周期で、入力電圧を検出した入力電圧信号Vi、出力電圧を検出した出力電圧信号Voをサンプリングする。そして、当該2つの信号等に基づいて所定の演算処理を行い、次回のサンプリングタイミングで検出されるであろう出力電圧Vo及びその時の出力微分値Vdの関係が式(6)を充足するように、当該サンプリング以降の主スイッチング素子14のオン時間とオフ時間を算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるように、オン時間及びオフ時間を算出する。具体的な演算処理の内容については、後の動作説明の中で述べる。

【0030】

駆動パルス生成手段30は、演算手段28が決定したオン時間及びオフ時間(スイッチング周期及び主スイッチング素子がオンする時比率δ)に基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。駆動パルスV14は、一定のスイッチング周期Tを有し、時比率δの期間は主スイッチング素子14をオンさせるハイレベルを示し、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間は整流素子16をオフさせるローレベルを示し、その他の期間はハイレベルを示す。詳しくは、後の動作説明の中で述べる。

【0031】

以下、スイッチング電源装置10の動作について説明する。ここで、制御回路24で行われる各種の演算処理等に要する時間は十分短く無視できるものとする。図2、図3は、スイッチング電源装置10に入力が投入された後、定常動作を行なっている様子を示している。演算手段28が各信号をサンプリングする周期はスイッチング周期と等しくTであり、サンプリング周期Tごとにt(k−1),t(k),t(k+1)、t(k+2)のタイミングでサンプリングを行う。

【0032】

なお、スイッチング電源装置10は、定常動作中においても、比較的小さな外乱(例えば、環境温度の変化など)の影響により、主スイッチング素子14のオン時間及びオフ時間がスイッチング周期毎に微妙に変化する。図3では、定常動作を説明する便宜のため、その微妙な変化を誇張して現わしてある。

【0033】

まず、図2に示すように、演算手段28がt(k)のタイミングで、自らがt(k)以前のタイミングに決定した時比率δ(k−1)を取得し、同じく、自らがt(k)以前のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS11)。同じくt(k)のタイミングで、演算手段28が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS12)。そして、サンプリングした信号Vi(k),Vo(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)及び出力電圧信号Vo(k−1)に基づいて所定の演算処理を行い、主スイッチング素子14の次の時比率δ(k)を算出する(ステップS13)。時比率δ(k)は、式(7)のように定義されている。

【数7】

Tはスイッチング周期であり、ton(k),toff(k)は主スイッチング素子14のオン時間とオフ時間である。

【0034】

以下、演算手段28が時比率δ(k)を算出するための演算処理の内容を説明する。平滑コンデンサ20に流れるコンデンサ電流Icの傾きは平滑インダクタ18のインダクタンスLの逆数に比例するため、次のサンプリングタイミングt(k+1)におけるコンデンサ電流Ic(k+1)は、t(k)のタイミングでサンプリングした各信号と、ton(k)及びtoff(k)を用いて、式(8)のように表すことができる。

【数8】

式(8)のオン時間ton(k)とオフ時間toff(k)をスイッチング周期Tと時比率δ(k)に置き換えて表すと式(9)のようになり、同様に式(10)が得られる。

【数9】

【数10】

【0035】

また、次のサンプリングタイミングt(k+1)における出力電圧Vo(k+1)は、式(11)のように表わすことができ、同様に式(12)が得られる。

【数11】

【数12】

【0036】

そして、式(9)〜式(12)からコンデンサ電流Ic(k+1),Ic(k),Ic(k−1)を消去すると、式(13)が得られる。同様に、式(9)〜式(12)からコンデンサ電流Ic(k),Ic(k−1)及びVo(k+1)を消去すると、式(14)が得られる。

【数13】

【数14】

ここで、式(13),(14)のu(k),u(k−1)は、式(15)に示すように定義した複合信号であり、a1,a2,b1,b2は、スイッチング周期T、インダクタンスL、容量Cという複数の回路定数を組み合わせて成る複合定数であり、それぞれ式(16)〜式(18)のように定義されている。

【数15】

【数16】

【数17】

【数18】

【0037】

上述したように、演算手段28は、次回のサンプリングタイミングt(k+1)で検出されるであろう出力電圧Vo及びその時の出力微分値Vdが式(6)の関係を充足するように時比率δ(k)を決定する。式(6)の制御関数式にサンプリングタイミングの概念を盛り込み、かつ、出力微分値Vdをコンデンサ電流Ic及び容量Cで表わすと、式(19)を導出することができる。

【数19】

そして、式(19)に式(13),(14)を代入することによってコンデンサ電流Ic(k+1)と出力電圧Vo(k+1)を消去して整理すると、時比率δ(k)を算出する式(20)が得られる。

【数20】

ここで、sは(−T/τ)である。式(20)によれば、当初からデフォルト設定されている回路定数等を除き、δ(k)を算出するのに必要な情報は、入力電圧Vi(k)、出力電圧Vo(k),Vo(k−1)、及び、入力電圧信号Vi(k−1)と時比率δ(k−1)との積である複合信号u(k−1)である。これらは、いずれもサンプリングタイミングt(k)が経過した時点で既知の情報であり、式(20)に基づいて時比率δ(k)を算出することが可能であることが分かる。

【0038】

このように、演算手段28は、ステップS13において、ステップS11,S12で入手した信号等を式(20)に代入することによって、次のサンプリングタイミングt(k+1)までの時比率δ(k)を算出する。

【0039】

次に、駆動パルス生成手段30が、ステップS13で決定した時比率δ(k)に基づいて、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する(ステップS14)。駆動パルスV14は、サンプリング周期Tの中間時点を挟んで前後に等しい期間が時比率δ(k)の期間に設定され、当該期間は主スイッチング素子14をオンさせるハイレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該時比率δ(k)の期間は整流素子16をオフさせるローレベルを示す。

【0040】

スイッチング電源装置10は、ステップS11〜S14を繰り返すことによって、出力電圧が目標値Vrefに等しくなるようにPWM制御される。

【0041】

次に、スイッチング電源装置10の過渡的な動作について説明する。ここで、駆動パルス生成手段30が生成可能な駆動パルスV14は、オンの最大時比率δmaxと最小時比率δminが設定されている。最大時比率δmaxは、電力変換回路の安全性を向上させたり、各機能ブロックの同期をとって適正に動作させたりする目的で、100%よりも狭い値、例えば、60〜95%程度に設定することが考えられる。

【0042】

動作を停止しているスイッチング電源装置10に入力直流電源12が投入され、出力電圧が目標値Vrefに達するまでの過渡的な動作を、図4に示す。図4(a)は、横軸が出力電圧信号Vo、縦軸が出力微分値Vdのグラフであり、破線が式(6)の制御関数式を示す直線である。スイッチング電源装置10が停止しているとき、出力電圧信号Voはゼロである。そして、入力が投入されると、出力電圧が上昇を開始し、出力電圧信号Vo及び出力微分値Vdが実線で示す軌跡を辿って変化し、出力電圧信号Voが目標値Vrefに等しくなって安定する。

【0043】

入力投入直後の期間Aは、図4(b)に示すように、出力電圧信号Voと目標値Vrefとの差が大きいので、式(20)を用いて算出される時比率δ(k)は、オンの最大時比率δmaxを超えてしまう。駆動パルス生成手段30は、演算手段28で算出された時比率δ(k)が最大時比率δmaxよりも大きいときは、一律に最大時比率δmaxの駆動パルスV14を出力する。従って、期間Aは、最大時比率δmaxという非常に大きな制御量によって、出力電圧が急速に上昇する。

【0044】

期間Bになると、出力電圧信号Voと目標値Vrefとの差が比較的小さくなり、式(20)を用いて算出される時比率δ(k)が最大時比率δmax以下の値まで小さくなる。すると、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動し、出力電圧信号Vo及び出力微分値Vdの関係がグラフの破線に沿って(すなわち、式(6)の関係を満たしながら)変化する。詳しくは、スイッチング周期Tごとに、図4(c)に示す動作が行われる。式(6)は、いわゆる一次遅れ系の制御を表す制御関数式なので、出力電圧信号Voは、図4(b)に示すように、定数τを時定数とする指数関数の曲線を描きながら上昇する。そして、期間Cになると、出力電圧信号Voと目標値Vrefとの差がなくなり、図2、図3で説明した定常動作を行う。

【0045】

入力急変や負荷急変のときの過渡的動作も、上述した入力投入のときの動作と基本的に同様である。例えば、定常動作を行っている最中に入力電圧が急激に上昇したり負荷が急激に軽くなったりすると、出力電圧が上昇して、一時的に出力電圧信号Vo及び出力微分値Vdが式(6)を充足しなくなる。出力電圧信号Voが上昇して目標値Vrefとの差が大きくなると、式(20)を用いて算出される時比率δ(k)は、オンの最小時比率δminよりも小さな値(例えば、マイナスの値)になる。駆動パルス生成手段30は、算出された時比率δ(k)が最小時比率δminよりも小さいときは、一律に最小時比率δmin(例えばゼロ%)の駆動パルスV14を出力する。従って、入力電圧が急激に上昇した直後の期間等は、一律に最小時比率δminで動作し、入力からの電力供給を最小限に抑えることによって、出力電圧を急速に低下させようとする。

【0046】

その後、出力電圧信号Voと目標値Vrefとの差が比較的小さくなり、式(20)を用いて算出される時比率δ(k)がオンの最小時比率δmin以上の値になり、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動する。そして、出力電圧信号Vo及び出力微分値Vdがグラフの破線に沿って変化し、出力電圧信号Voと目標値Vrefとの差がなくなって、図2、図3で説明した定常動作を行う。

【0047】

以上説明したように、スイッチング電源装置10は、制御回路24の演算手段28に、制御関数式である式(6)が定義され、出力電圧と出力電圧の変化を示す出力微分値とを変数にとり、出力電圧の目標値Vrefを介して所定の関係を規定する。そして、演算手段28は、入力電圧信号Vi、出力電圧信号Voをサンプリングし、式(6)を充足するように導出された式(20)を用いて、オン時間及びオフ時間を決定する時比率δを算出する。従って、計算回数が多い微分計算による動作遅れが解消され、シンプルで安価な制御回路で高速応答特性を実現することができる。また、入力電圧や出力電圧が急変したとき、その急変の情報が即座に演算処理に反映されるので、入力急変や負荷急変に対する応答が速い。また、式(20)で算出した時比率δが最小時比率δminから最大時比率δmaxの範囲にないときは、主スイッチング素子のオンの時比率が一律に最小時比率δmin又は最大時比率δmaxに設定され、出力電圧と目標値の偏差を小さくするための制御量が瞬時に最大になる。

【0048】

さらに、演算手段28が算出する時比率δ(k)は、出力電圧信号Voと出力微分値Vdが式(6)の直線関係を充足するように変化するため、出力電圧が所定の目標値Vrefに達して定常動作に入るまでの過程で(例えば、図4における期間A,B)、出力電圧にオーバーシュートや振動が発生しない。

【0049】

また、式(6)の制御関数式を変更することによって、入力投入時の出力電圧等の変化の具合を容易に調整することができる。例えば、式(6)の係数τを大きめに変更すれば、図4(a)の破線の傾きが小さくなって短時間で期間Aが終了するので、コンデンサ電流(Icに相当)のピーク値が小さくなり電子部品のストレスが軽減され、同時に、出力電圧の上昇速度が緩やかになって期間Bが長くなり、スイッチング電源装置10の起動時間が長くなる。

【0050】

また、式(6)に条件を加え、出力電圧信号Voと目標値Vrefの差がεを超える範囲では、出力微分値Vdが一定の値Vddになるよう規定することもできる。その場合の制御関数式は、式(21)〜式(23)のように表される。

【数21】

【数22】

【数23】

演算手段28に式(21)〜式(23)の制御関数式が定義されると、上記の式(20)に相当する時比率δ(k)の演算式が3種類になり、出力電圧信号Voの値によって使い分けることになる。図5に示すように、入力投入直後の期間Aは、該当する一つの演算式から求まる時比率δ(k)がオンの最大時比率δmaxを超えるので、一律に最大時比率δmaxの駆動パルスV14を出力するが、出力電圧信号Vo及び出力微分値Vdの関係が、短時間のうちに式(21)〜式(23)を示す破線上に達して期間B1に移行する。従って、コンデンサ電流(Icに相当)のピーク値を、比較的小さな値に制限することができる。

【0051】

期間B1,B2は、期間ごとに該当する演算式が選択され、選択された演算式から時比率δ(k)を求める。ここで求まる時比率δ(k)は、最大時比率δmax以下の値になるので、駆動パルス生成手段30は、時比率δ(k)の駆動パルスV14を出力して主スイッチング素子14を駆動し、出力電圧信号Vo及び出力微分値Vdの関係がグラフの破線に沿って変化する。そして、期間Cになると、出力電圧信号Voと目標値Vrefとの差がなくなり、図2、図3で説明した定常動作が行われる。

【0052】

このとき、式(22)の係数τを調節すれば、コンデンサ電流のピーク値を小さく抑えつつ、期間B1,B2の時間を短くすることができる。例えば、係数τを小さな値に設定することによって、図4における期間Bと同等の時間に設定することも可能である。すなわち、式(6)に代えて式(21)〜式(23)を制御関数式に用いれば、スイッチング電源装置10の起動時間とコンデンサ電流のピーク値を、各々独立に調整することができる。

【0053】

次に、この発明の第二の実施形態のスイッチング電源装置40について図6、図7を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置40は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器42a,42b、演算手段44及び駆動パルス生成手段46が設けられている。

【0054】

A/D変換器42a,42bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期の半分の周期ごとに行われ、そのタイミングは、主スイッチング素子14がオンの期間、及び、平滑インダクタ18がオンの期間に蓄えられた励磁エネルギーを出力に放出している期間における任意のタイミングである。ここで、「励磁エネルギーを出力に放出している」状態とは、当該励磁エネルギーを放出する電流が、出力から平滑インダクタ18の向きに流れている状態も含む。

【0055】

演算手段44には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。しかし、演算手段28と異なり、入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器42a,42bから、上述したスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングする。そして、当該2つの信号等に基づいて、式(20)に類似する所定の演算を行い、次回のサンプリングタイミングまでの期間の時比率δを算出する。

【0056】

駆動パルス生成手段46は、演算手段44が決定した時比率δに基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。しかし、駆動パルスV14は、上記駆動パルス生成手段30のものとは異なり、スイッチングの1周期Tの中の2回目のサンプリングタイミングを挟んで前後の期間を主スイッチング素子14のオン期間とするパルス電圧であって、時比率δの期間は主スイッチング素子14をオンさせるハイレベル、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間はローレベル、その他の期間は整流素子16をオンさせるハイレベルを示す。

【0057】

上記の演算手段44及び駆動パルス生成手段46の場合、サンプリングが、平滑インダクタ18に電流が流れていない期間(電流ゼロ期間)中に行われると、出力微分値Vdを利用した式(6)に基づく出力の制御が不能になる。しかし、スイッチング電源装置40は、スイッチング電源装置10と同様に、主スイッチング素子14及び整流素子16として双方向に導通可能なN−chのMOS型FETが使用されているので、例えば負荷22に供給する出力電流が小さくなって臨界点以下になっても、平滑インダクタ18は電流を連続して流し続け、上記の電流ゼロ期間は生じない。従って、スイッチング周期Tにおける任意のタイミングでサンプリングを行うことができる。

【0058】

以下、スイッチング電源装置40の動作について説明する。入力が投入された後の定常動作を示すフローチャートは、上記スイッチング電源装置10で説明した図2と同様である。その結果、図7のタイムチャートに示すように、スイッチング周期Tの半分の周期ごとに時比率δが可変調整される。従って、上記スイッチング電源装置10と比較すると、時比率δを調整する頻度が2倍となり、出力電圧の制御の遅れが半分になるので、制御の応答が一段と高速化される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。

【0059】

次に、この発明の第三の実施形態のスイッチング電源装置50について図8〜図10を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置50は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器52a,52b、演算手段54及び駆動パルス生成手段56が設けられている。

【0060】

A/D変換器52a,52bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期ごとに行われ、そのタイミングは、主スイッチング素子14がオフからオンに転じるタイミングである。

【0061】

演算手段54には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。しかし、演算手段28と異なり、入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器52a,52bから、上述したスイッチング周期ごとに主スイッチング素子14がオンに転じるタイミングでサンプリングする。そして、当該2つの信号等に基づいて所定の演算を行い、時比率δを算出する。

【0062】

スイッチング電源装置50の制御回路24は、比較的安価で汎用的なデジタルICを用いて構成されているため、演算手段54が行う演算処理等に要する時間が無視できない。従って、高速演算可能なデジタルIC等で構成された上記の演算手段28の場合は、次回のサンプリングタイミングまでの期間の時比率δを算出したのに対して、この演算手段54の場合は、次回のサンプリングタイミング後の期間の時比率δを算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるようにオンの時比率δを算出する。

【0063】

駆動パルス生成手段56は、演算手段54が決定した時比率δに基づき、主スイッチング素子14の駆動パルスV14と、整流素子16の駆動パルスV16を生成する。しかし、駆動パルスV14は、上記駆動パルス生成手段30のものとは異なり、サンプリングのタイミングから開始する時比率δの期間を主スイッチング素子14のオン期間とするパルス電圧であり、時比率δの期間は主スイッチング素子14をオンさせるハイレベル、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、時比率δの期間はローレベル、その他の期間は整流素子16をオンさせるハイレベルを示す。

【0064】

以下、スイッチング電源装置50の動作について説明する。図10は、スイッチング電源装置50に入力が投入された後、定常動作を行なっている様子を示している。演算手段54が各信号をサンプリングする周期はスイッチング周期と等しくTであり、主スイッチング素子14がオフからオンに転じるサンプリング周期Tごとにt(k−1),t(k),t(k+1)、t(k+2)のタイミングでサンプリングを行う。

【0065】

まず、図9に示すように、演算手段54がt(k)のタイミングで、自らがt(k)以前のタイミングに決定した時比率δ(k),δ(k−1)を取得し、同じく、自らがt(k)以前のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS21)。同じくt(k)のタイミングで、演算手段54が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS22)。その後、時比率δ(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)を上記の式(13)に代入し、t(k+1)のタイミングの出力電圧信号の予測値であるVo1(k+1)を算出する。(ステップS23)。そして、時比率δ(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び予測値Vo1(k+1)を次の式(24)に代入し、次のサンプリングタイミングt(k+1)後の時比率δ(k+1)を算出する(ステップ24)。

【数24】

式(24)は、上記の式(20)のkをk+1とし、k−1をkとして表したものである。ただし、式(24)の右辺の分母に含まれるVi(k)は、本来ならVi(k+1)となるところであるが、t(k)直後のタイミングで入力電圧信号Vi(k+1)は未知なので、既知のVi(k)で代用している。

【0066】

このようにして、演算手段54は、サンプリングタイミングt(k+2)における出力電圧信号Vo及び出力微分値Vdの関係が式(6)を充足するように、タイミングt(k+1)後の時比率δ(k+1)を算出する。なお、スイッチング電源装置50の場合、サンプリングが主スイッチング素子14がオフからオンに転じるタイミングで行うため、コンデンサ電流Icのスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得る。従って、式(24)は、この点を考慮した形に変形することが望ましいが、ここでは説明を省略する。

【0067】

次に、駆動パルス生成手段56が、ステップS24で決定した時比率δ(k+1)に基づいて、タイミングt(k+1)後の駆動パルスV14と駆動パルスV16を生成する(ステップS25)。駆動パルスV14は、時比率δ(k+1)の期間がタイミングt(k+1)から始まるように設定されているので、当該期間に主スイッチング素子14をオンさせるハイレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該時比率δ(k)の期間は整流素子16をオフさせるローレベルを示す。

【0068】

スイッチング電源装置50は、ステップS21〜S25を繰り返すことによって、図10に示す動作を行い、出力電圧が目標値Vrefに等しくなるようにPWM制御される。演算手段54は、次回のサンプリングタイミング後の時比率δを算出するため、上記スイッチング電源装置10と比較すると、制御動作にスイッチングの1周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置50は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路24を構成することができる。

【0069】

次に、この発明の第四の実施形態のスイッチング電源装置60について図11〜図13を基にして説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明を省略する。スイッチング電源装置60は、図1に示すスイッチング電源装置10の構成とほぼ同様であるが、A/D変換器26a,26b、演算手段28及び駆動パルス生成手段30に代えて、動作の異なるA/D変換器62a,62b、演算手段64及び駆動パルス生成手段66が設けられている。

【0070】

A/D変換器62a,62bには、各部のアナログ情報が入力され、所定のタイミングでサンプリングし、デジタル情報に変換した入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期ごとに行われ、そのタイミングは、主スイッチング素子14のスイッチング周期に同期したタイミングであって、主スイッチング素子14がオンの期間又は平滑インダクタ18が励磁エネルギーを放出している期間における所定のタイミングである。ただし、後述するように、演算手段64が決定するスイッチング周期は変化する。

【0071】

演算手段64には、上記演算手段28と同様に、式(6)の制御関数式が定義されている。そして、上述のサンプリングタイミングで入力電圧信号Vi、出力電圧信号Voを、上記A/D変換器62a,62bからサンプリングする。そして、当該2つの信号等に基づいて所定の演算処理を行い、オン時間及びオフ時間を算出する。

【0072】

スイッチング電源装置60の制御回路24は、比較的安価で汎用的なデジタルICを用いて構成されているため、演算手段64が行う演算処理等に要する時間が無視できない。従って、ここでは、次回のサンプリングタイミング後の主スイッチング素子14のオン時間とオフ時間を算出する。また、ここでは、オン時間が一定のPFM制御が行われるようにオフ時間を算出する。従って、スイッチング周期及びサンプリング周期が変化する。

【0073】

駆動パルス生成手段66は、演算手段64が決定したオン時間及びオフ時間に基づき、駆動パルスV14と、駆動パルスV16を生成する。駆動パルスV14は、サンプリング周期の中間時点を挟んで前後に等しい期間が主スイッチング素子14のオン期間になるように設定され、当該オンの期間はハイレベルを示し、その他の期間はローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と同期した逆位相のパルス電圧であって、当該オン期間は整流素子16をオフさせるローレベルを示し、その他の期間はハイレベルを示す。

【0074】

以下、スイッチング電源装置60の動作について説明する。図13は、スイッチング電源装置60に入力が投入された後、定常動作を行なっている様子を示している。演算手段64が各信号をサンプリングする周期は、スイッチング周期と同期してT(k−1),T(k),T(k+1)のように変化する。サンプリングのタイミングは、t(k−1),t(k),t(k+1)、t(k+2)である。

【0075】

まず、図12に示すように、t(k)のタイミングで、演算手段64が、自らt(k)以前のタイミングに決定したオフ時間toff(k),toff(k−1)と、t(k−1)のタイミングにサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS31)。同じくt(k)のタイミングで、演算手段64が入力電圧信号Vi(k)、出力電圧信号Vo(k)をサンプリングする(ステップS32)。その後、オフ時間toff(k)、入力電圧信号Vi(k)、出力電圧信号Vo(k)、及び過去のオフ時間toff(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)を上記の式(13)に代入し、t(k+1)のタイミングの出力電圧信号の予測値であるVo1(k+1)を算出する。(ステップS33)。ここで、式(13)はtoff,Viを含んでいないが、式(7),(15)を用いてuをtoffとViに展開すれば、予測値Vo1を算出可能であることが分かる。そして、上記の式(24)を用いて、次のサンプリングタイミングt(k+1)後のオフ時間toff(k+1)を算出する(ステップ34)。

【0076】

このようにして、演算手段64は、次のサンプリングタイミングt(k+2)で検出されるであろう出力電圧信号Vo及び出力微分値Vdの関係が式(6)を充足するように、オフ時間toff(k+1)を算出する。

【0077】

次に、駆動パルス生成手段66が、ステップS34で決定したオフ時間toff(k+1)と固定値であるオン時間tonに基づいて、タイミングt(k+1)後における駆動パルスV14と駆動パルスV16を生成する(ステップS35)。駆動パルスV14は、サンプリング周期T(k+1)の中間時点を挟んで前後に等しい期間がオン時間tonの期間に設定され、当該期間は主スイッチング素子14をオンさせるハイレベルを示し、オン時間tonの前後にオフ時間toff(k+1)の半分の期間が各々設けられ、当該期間は主スイッチング素子14をオフさせるローレベルを示す。一方、駆動パルスV16は、駆動パルスV14と位相が逆転したパルス電圧であり、当該オン時間tonの期間はローレベルを示し、その前後のtoff(k+1)の期間は整流素子16をオンさせるハイレベルを示す。

【0078】

スイッチング電源装置60は、ステップS31〜S35を繰り返すことによって、図13に示す動作を行い、出力電圧が目標値Vrefに等しくなるようにPFM制御される。スイッチング電源装置60は、次回のサンプリングタイミング後のオフ時間toffを算出するため、上記スイッチング電源装置10と比較すると、制御動作にスイッチングの1周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置10の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置60は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路24を構成することができる。

【0079】

次に、この発明の第五の実施形態のスイッチング電源装置70について、図14に基づいて説明する。ここで、第三の実施形態のスイッチング電源装置50と同様の構成は、同一の符号を付して説明する。スイッチング電源装置70は、上記スイッチング電源装置50と同様に、一般的な降圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を行うと共に、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを放出して出力の負荷22に電力供給する動作を行う。

【0080】

しかし、スイッチング電源装置70は、MOS型FETの整流素子16に代えて、グランドから主スイッチング素子14及び平滑インダクタ18の接続点に向けて導通可能なダイオードである整流素子72が設けられ、制御回路24に代わる制御回路74は、駆動パルス14のみを出力するよう構成されている。整流素子72は一方向にしか導通しないので、負荷22に供給する出力電流が小さくなって臨界点以下になると、平滑インダクタ18の電流が連続せず、電流ゼロ期間が生じる。

【0081】

制御回路74は、上記スイッチング電源装置50の制御回路24の動作と異なり、図示しない演算手段等が、スイッチング周期ごとに主スイッチング素子14がオフに転じるタイミングでサンプリングを行って時比率δを算出する。このサンプリングタイミングは、電流ゼロ期間ではないので、出力微分値Vdを利用した式(6)に基づく出力制御が不能になることはない。また、出力電流が小さくなって臨界点以下になると、式(24)が成立しなくなるので、式(24)と異なる特有の演算式に基づいて時比率δを算出する。そして、図示しない駆動パルス生成手段が、サンプリングのタイミングから開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する動作を行う。制御回路74の上記以外の動作、すなわち、次回のサンプリングタイミング後の期間の時比率δを算出し、その時比率δはスイッチング周期一定の条件の下で算出される(PWM制御を行う)という動作は、スイッチング電源装置50の制御回路24と同様である。

【0082】

以上の構成を備えたスイッチング電源装置70は、整流素子72としてダイオードが使用されているが、上記のスイッチング電源装置50と同様の優れた作用効果を奏する。ただし、スイッチング電源装置70は、いわゆる電流ゼロ期間が存在するため、図6で説明した第二の実施形態のスイッチング電源装置40のように、制御回路74に設けられた図示しない演算手段等が、入力電圧信号Vi等のサンプリングをスイッチング周期の半分の周期ごとに行い、スイッチングの1周期の中の2回目のサンプリングタイミングを挟んで前後の期間を主スイッチング素子14のオン期間とする、という制御回路24の構成を適用することができないので注意が必要である。

【0083】

次に、この発明の第六の実施形態のスイッチング電源装置76について、図15に基づいて説明する。ここで、上記スイッチング電源装置70と同様の構成は、同一の符号を付して説明する。スイッチング電源装置76は、上記スイッチング電源装置70と異なり、一般的な昇圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。また、主スイッチング素子14のオフ期間は、入力直流電源12から出力の負荷22へ電力供給も同時に行われる。

【0084】

スイッチング電源装置76は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止する点で、上記スイッチング電源装置70と動作が異なる。従って、後述する制御回路78の演算手段等がサンプリングを行うタイミングを主スイッチング素子のオフ期間に設定しないと、出力の制御が不能になる。さらに、整流素子72は一方向にしか導通しないので、負荷22に供給する出力電流が小さくなって臨界点以下になると、平滑インダクタ18の電流が連続せず電流ゼロ期間が生じる。従って、当該サンプリングのタイミングを上記の電流ゼロ期間を除いた期間中に設定する必要がある。

【0085】

制御回路78は、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに主スイッチング素子14がオンからオフに転じた直後(平滑インダクタ18が励磁エネルギーを放出している状態)のタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、当該サンプリングタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する。また、当該演算手段が行う演算内容は、降圧チョッパ回路の式(24)等とは異なる昇圧チョッパ回路特有の演算式で表される。特に、コンデンサ電流のスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得るので、この点を考慮した演算式を導出する必要がある。制御回路78の上記以外の動作、すなわち、次回のサンプリングタイミング後の期間の時比率δを算出し、その時比率δはスイッチング周期一定の条件の下で算出される(PWM制御を行う)という動作は、スイッチング電源装置70の制御回路74と同様である。

【0086】

以上の構成を備えたスイッチング電源装置76は、昇圧チョッパ型の電力変換回路を備え、整流素子72にダイオードを用いているが、上記のスイッチング電源装置70と同様の優れた作用効果を奏する。

【0087】

次に、この発明の第七の実施形態のスイッチング電源装置80について、図16に基づいて説明する。ここで、上記スイッチング電源装置76と同様の構成は、同一の符号を付して説明する。スイッチング電源装置80は、上記スイッチング電源装置76と異なり、一般的な昇降圧チョッパ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によって内蔵する平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間に、平滑インダクタ18に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。

【0088】

スイッチング電源装置80の場合、主スイッチング素子14のオフ期間に、入力直流電源12から出力の負荷22へ電力供給が行われない点で、上記スイッチング電源装置76と動作が異なる。しかし、出力の制御不能状態を回避するための条件は同様であり、後述する制御回路82は、演算手段等がサンプリングを行うタイミングを主スイッチング素子のオフ期間であって、且つ、上記の電流ゼロ期間を除いた期間に設定する必要がある。

【0089】

制御回路82は、上記スイッチング電源装置76の制御回路78と同様に、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに主スイッチング素子14がオンからオフに転じた直後のタイミングでサンプリングを行う。図示しない駆動パルス生成手段は、サンプリングのタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する。また、当該演算手段が行う演算内容は、昇圧チョッパ回路の演算式とは異なる昇降圧チョッパ回路特有の演算式が用いられる。特に、コンデンサ電流のスイッチング周期ごとの振幅成分が出力電圧設定の偏差の要因となり得るので、この点を考慮した演算式を導出する必要がある。

【0090】

以上の構成を備えたスイッチング電源装置80は、昇降圧チョッパ型の電力変換回路を備えているが、上記のスイッチング電源装置76と同様の優れた作用効果を奏する。

【0091】

次に、この発明の第八の実施形態のスイッチング電源装置84について、図17に基づいて説明する。ここで、第一の実施形態のスイッチング電源装置10と同様の構成は、同一の符号を付して説明する。スイッチング電源装置84は、上記スイッチング電源装置10の電力変換回路にトランス86、整流側同期整流素子88及び転流側同期整流素子89が追加された、シングルエンディドフォワード型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ、トランス86及び整流側同期整流素子88を介して電力供給を行うと共に、入力直流電源12によって平滑インダクタ18を励磁する。そして、主スイッチング素子14のオフ期間も、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって出力の負荷22に電力供給し続ける動作を行う。従って、整流側同期整流素子88を主スイッチング素子14の駆動パルスV14と同位相のパルス電圧で駆動し、転流側同期整流素子89を駆動パルスV14と逆位相の駆動パルスV16で駆動することによって、上記スイッチング電源装置10と同様の動作で出力電圧が制御される。

【0092】

以上の構成を備えたスイッチング電源装置84は、シングルエンディッドフォワード型の電力変換回路を備えているが、降圧チョッパ型の電力変換回路を備えたスイッチング電源装置10と同様の方法で制御が行われ、同様の優れた作用効果を奏する。

【0093】

次に、この発明の第九の実施形態のスイッチング電源装置90について、図18に基づいて説明する。ここで、第七の実施形態のスイッチング電源装置80と同様の構成は、同一の符号を付して説明する。スイッチング電源装置90は、上記スイッチング電源装置80の電力変換回路にトランス86が追加された、フライバック型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14のオン期間に、入力直流電源12から出力の負荷22へ電力供給を停止し、入力直流電源12によってインダクタンス素子であるトランス86を励磁する。そして、主スイッチング素子14のオフ期間に、トランス86に蓄積された励磁エネルギーを、ダイオードである整流素子72を介して出力に放出し、負荷22に電力供給する動作を行う。

【0094】

制御回路82は、上記スイッチング電源装置80の制御回路82と同様の動作を行う。すなわち、出力の制御不能状態を回避すべく、図示しない演算手段等が、主スイッチング素子14のスイッチング周期ごとに、主スイッチング素子14がオンからオフに転じた直後のタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、サンプリングのタイミングの直前から開始する期間を主スイッチング素子14のオフ期間とする駆動パルスV14を生成する動作を行う。

【0095】

以上の構成を備えたスイッチング電源装置90は、フライバック型の電力変換回路を備えているが、昇降圧チョッパ型の電力変換回路を備えたスイッチング電源装置80と同様の方法で制御が行われ、同様の優れた作用効果を奏する。

【0096】

次に、この発明の第十の実施形態のスイッチング電源装置92について、図19に基づいて説明する。ここで、第五の実施形態のスイッチング電源装置70と同様の構成は、同一の符号を付して説明する。スイッチング電源装置92は、2つの主スイッチング素子14a,14b、カップリングコンデンサ94、トランス86、ダイオードである2つの整流素子72a,72b、平滑インダクタ18及び平滑コンデンサ20で構成された、一般的なハーフブリッジ型の電力変換回路を備えている。すなわち、この電力変換回路は、主スイッチング素子14aと14bが制御回路96から駆動パルスV14a,V14bを受け、スイッチング周期ごとに交互にオン・オフ制御される。主スイッチング素子14a,14bのオン期間は、入力直流電源12から出力の負荷22へ、トランス86及び整流素子72a,72bを介して電力供給を行うと共に、入力直流電源12によって平滑インダクタ18を励磁する。主スイッチング素子14a,14bのオフ期間は、平滑インダクタ18に蓄積された励磁エネルギーを放出することによって出力の負荷22に電力供給する動作を行う。

【0097】

制御回路96は、上記スイッチング電源装置70の制御回路74の動作と同様に、出力の制御不能状態を回避すべく、図示しない演算手段等が、スイッチング周期ごとに主スイッチング素子14a又は14bがオフに転じるタイミングでサンプリングを行い、図示しない駆動パルス生成手段が、サンプリングのタイミングから開始する期間を主スイッチング素子14a又は14bのオフ期間とする駆動パルスV14a,V14bを生成する動作を行う。

【0098】

以上の構成を備えたスイッチング電源装置92は、複数の主スイッチング素子を有するハーフブリッジ型の電力変換回路を備えているが、降圧チョッパ型の電力変換回路を備えたスイッチング電源装置70と同様の方法で制御が行われ、同様の優れた作用効果を奏する。また、プッシュプル型、フルブリッジ型、カスケードフォワード型等の多石式電力変換回路を備えたスイッチング電源装置も、スイッチング電源装置92と同様の考え方で構成することができる。

【0099】

次に、この発明の第十一の実施形態のスイッチング電源装置98について、図20に基づいて説明する。ここで、上記スイッチング電源装置40と同様の構成は、同一の符号を付して説明する。スイッチング電源装置98の電力変換回路の構成は、図6に示すスイッチング電源装置40と同じく降圧チョッパ型である。

【0100】

制御回路100は、A/D変換器42a,42b、オブザーバ102、演算手段104、及び駆動パルス生成手段46で構成されている。すなわち、図4に示す上記スイッチング電源装置40の制御回路24の構成に加え、オブザーバ102が新設され、演算手段44に代えてオブザーバ102に対応した動作を行う演算手段104が設けられている。また、平滑インダクタ18のコイルの寄生抵抗18aを回路図上に明記した。この寄生抵抗18aは、出力電流Ioが流れる経路に存在する寄生インピーダンスの一種でありこの実施形態では、出力電圧精度を向上させるため、寄生抵抗18aに起因する電圧降下成分Vofsを含めて、演算手段104が時比率δを算出する。

【0101】

A/D変換器42a,42bには、入力電圧及び出力電圧を検出したアナログ情報が入力され、所定のタイミングでサンプリングされ、デジタル情報に変換された入力電圧信号Vi、出力電圧信号Voを出力する。サンプリングは、主スイッチング素子14のスイッチング周期の半分の周期ごとに行われ、そのタイミングは、主スイッチング素子14がオンの期間、又は、平滑インダクタ18がオンの期間に蓄えられた励磁エネルギーを出力に放出している期間における任意のタイミングである。

【0102】

オブザーバ102は、観測器とも呼ばれる状態変数の推定手段であって、特定の回路部分の検出値(測定値)を利用して、検出困難な箇所の動作状態を推定する機能を備えている。ここでは、検出が比較的容易な入力電圧信号Vi及び出力電圧信号Voと、当該サンプリングの直前に演算手段104が決定した時比率δとに基づいて、次のサンプリングタイミングで検出されるであろう出力電圧信号の推定値Vo2、及び、次のサンプリングタイミングにおける電圧降下成分の推定値Vofs2を算出する。

【0103】

スイッチング電源装置98の制御回路100は、比較的安価な汎用デジタルICを用いて構成されているため、演算手段104が行う演算処理等に要する時間が無視できない。従って、この演算手段104は、次回のサンプリングタイミング後の期間の時比率δを算出する。また、ここでは、オン時間とオフ時間の合計を常に一定にする条件を加え、スイッチング周期一定のPWM制御が行われるようにオンの時比率δを算出する。

【0104】

演算手段104は、検出値である入力電圧信号Viと、オブザーバ102の推定値である出力電圧信号Vo2及び電圧降下成分Vofs2を、上述したスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングする。そして、これらの信号に基づいて所定の演算処理を行い、次回のサンプリングタイミング後の期間の時比率δを算出する。また、演算手段104は、以前に算出した時比率δ等をオブザーバ102に向けて出力する働きもする。

【0105】

以下、スイッチング電源装置98の定常動作について、図21のフローチャートに基づいて説明する。ここで、スイッチング電源装置98の動作を示すタイムチャートは、上記スイッチング電源装置40の動作を示す図7とほぼ同様に表されるので、参照するとよい。

【0106】

まず、オブザーバ102がt(k)のタイミングで、t(k)以前のタイミングに演算手段104が決定した時比率δ(k),δ(k−1)を取得し、同じく、t(k)以前のタイミングに演算手段104がサンプリングしたVi(k−1),Vo(k−1)を取得する(ステップS41)。同じくt(k)のタイミングで、オブザーバ102が、検出値である入力電圧信号Vi(k)及び出力電圧信号Vo(k)をサンプリングする(ステップS42)。そして、オブザーバ102が、入力電圧信号Vi(k)、出力電圧信号Vo(k)、時比率δ(k)、及び過去の時比率δ(k−1)、入力電圧信号Vi(k−1)、出力電圧信号Vo(k−1)に基づいて、t(k+1)のタイミングの出力電圧信号の推定値Vo2(k+1)と電圧降下成分の推定値Vofs2(k+1)を算出する(ステップS43)。

【0107】

その後、演算手段104が、時比率δ(k)、入力電圧信号Vi(k)及び出力電圧信号Vo(k)と、推定値Vo2(k+1)及び電圧降下成分Vofs(k+1)とを、次の式(25)に代入し、次のサンプリングタイミングt(k+1)後の時比率δ(k+1)を算出する(ステップS44)。

【数25】

【数26】

式(25)は、右辺最終項に電圧降下成分Vofsを含んでおり、電圧降下成分Vofsは式(26)のように定義され、平滑インダクタ18の寄生抵抗18aの抵抗値R等で表わされる。式(26)は、上述の式(2)である。式(25)は、式(8)の「Vo(k)」を「Vo(k)+R・Io」に置き換え、上記と同様の考え方で導出できる。ここでは、出力電流Io及び寄生抵抗18aの抵抗値Rを、平滑インダクタ18のインダクタンスLや平滑コンデンサ20の容量C等の回路定数と同等に取り扱っており、電圧降下成分Vofsは複合定数として扱うことができる。

【0108】

そして、ステップS44の後、駆動パルス生成手段46が、演算手段104が算出した時比率δ(k+1)に基づき、タイミングt(k+1)後の駆動パルスV14と駆動パルスV16を生成する(ステップS45)。

【0109】

スイッチング電源装置98は、ステップS41〜S45を繰り返すことによって、出力電圧が目標値Vrefに等しくなるようにPWM制御される。演算手段104は、次回のサンプリングタイミング後の時比率δを算出するため、上記スイッチング電源装置40と比較すると、制御動作にスイッチングの半周期分の時間遅れが生じるものの、十分に実用的な応答速度が確保される。また、出力電流Ioが流れる経路に存在する寄生抵抗18aに起因する電圧降下成分Vofsも考慮した出力電圧制御が行われるので、出力電圧の精度がさらに向上する。また、入力投入、入力急変及び負荷急変等の過渡的動作も、上記スイッチング電源装置40の動作と基本的に同様であり、出力電圧が変化する際にオーバーシュートや振動が発生しない。このように、スイッチング電源装置98は、比較的安価な中低速デジタルICでも、優れた制御特性を備えた制御回路100を構成することができる。

【0110】

次に、この発明の第十二の実施形態のスイッチング電源装置106について、図22に基づいて説明する。ここで、上記スイッチング電源装置10と同様の構成は、同一の符号を付して説明する。スイッチング電源装置106の電力変換回路は、上記スイッチング電源装置10と同じく降圧チョッパ回路である。また、制御回路108は、上記スイッチング電源装置10の制御回路24の演算手段28に代えて、演算手段110が設けられている。また、平滑インダクタ18のコイルの寄生抵抗18aを回路図上に明記した。ここでは、寄生抵抗18aに起因する電圧降下成分Vofsが大きいため出力電圧制御への影響が無視できず、出力電圧精度を向上させるため、演算手段110が時比率δを算出するときに考慮される。

【0111】

演算手段110は、上記スイッチング電源装置10の制御回路28と同様の動作を行い、さらに、演算手段110にデフォルト値として初期設定されている回路定数について定期的にパラメータ推定を行って更新し、回路定数の個体差、温度による変化又は経時的な変化を考慮した出力電圧制御を行う。回路定数とは、ここでは主スイッチング素子14のスイッチング周期T、平滑インダクタ18のインダクタンスL、平滑コンデンサ20の容量C、出力電流Io、寄生抵抗18aの抵抗値R及び電圧降下成分Vofsをいう。

【0112】

ここで、演算手段110に定義されているパラメータ推定用の評価関数J(N)ついて説明する。まず、上記の式(13)に電圧降下成分Vofsを盛り込み、k+1をkに、kをk−1に、k−1をk−2にそれぞれ置き換えて、式(27)を得る。

【数27】

式(27)に含まれる複合定数a1,a2,b1,b2,及び電圧降下成分である複合定数Vofsは、式(16)〜式(18)、式(26)で定義されている。また、u(k−1),u(k−2)は、式(15)と同様のものである。

【0113】

パラメータ推定は、インダクタンスL、容量C等の多数個の回路定数の単位、又はa1,a2等の複合定数の単位でも行うことが可能であるが、ここでは、推定する複合定数の数を少なくして演算回数を減らすことにより、同等の推定精度を維持しつつ、演算手段110の処理の高速化を図っている。

【0114】

式(27)の複合定数a1,a2,b1,b2を個々の回路定数で表わし、式(28)に示す新たな複合定数pを定義すると、式(27)を式(29)のように変形することができる。式(28)は、上述の式(1)である。

【数28】

【数29】

【0115】

式(29)は、左辺に複合定数を含んでおらず、右辺第1項のカッコ内にも複合定数を含んでいない。そこで、左辺全体を、式(30)のように複合信号ν1(k)と表わし、右辺第1項のカッコ内を式(31)のように複合信号ν2(k)と表わす。すると、式(32)が得られる。式(30)、(31)は、上述の式(4)、(5)である。

【数30】

【数31】

【数32】

【0116】

次に、パラメータ推定のための評価関数を定義する。制御回路108の本来の目的は、出力電圧を高精度に制御することである。従って、出力電圧信号Voを基にしてパラメータ推定を行うことが望ましく、特に高精度にパラメータ推定を行うためには、タイミングt(k)における検出値Voa(k)と、それ以前に予測したタイミングt(k)の予測値Vob(k)との差を評価することとし、評価関数Jx(N)を式(33)のように定義する方法が考えられる。

【数33】

この場合、t(1)〜t(N)の各タイミングで得られる予測誤差を二乗したものの平均値を評価関数Jx(N)としている。

【0117】

しかし、制御回路108では、演算手段110の処理の高速化を図るため、複合定数の種類をさらに削減すると共に、単独の出力電圧信号Voの予測誤差に代えて、複数の出力電圧信号を組み合わせた複合信号ν1(k)の予測誤差を用いる。すなわち、複合信号ν1を基にしてパラメータ推定を行うこととし、タイミングt(k)における検出値ν1a(k)と、それ以前に予測したタイミングt(k)の予測値ν1b(k)との差(以下、予測誤差と称す。)を評価するため、式(34)のように評価関数J(N)を定義している。

【数34】

さらに、式(34)は、予測値ν1b(k)を式(32)の右辺に置き換えることによって、式(35)のように表わすことができる。式(35)は、上述の式(3)である。

【数35】

【0118】

このとき、式(34)に含まれるν1a(k)は、式(30)から分かるように、タイミングt(k),t(k−1),t(k−2)にサンプリングした検出値である出力電圧信号Vo(k),Vo(k−1),Vo(k−2)により算出可能である。従って、複合信号ν1a(k)は、現時点の検出値である出力電圧信号Vo(k)の項が含まれるので、式(33)における検出値Voa(k)に相当するものといえる。

【0119】

また、式(35)の複合信号ν2b(k)は、式(31)から分かるように、タイミングt(k−1),t(k−2)にサンプリングした検出値である出力電圧信号Vo(k−1),Vo(k−2),Vi(k−1),Vi(k−2)、及び、タイミングt(k−1),t(k−2)の時比率として算出した時比率δ(k−1),δ(k−2)により算出可能である。従って、複合信号ν2b(k)を含む複合信号ν1b(k)は、現時点の検出値である出力電圧信号Vo(k)を含まず、いずれも過去の検出値等だけから成るので、式(33)における予測値Vob(k)に相当するものといえる。

【0120】

次に、演算手段110が行うパラメータ推定の動作について、図23に基づいて説明する。この実施形態のスイッチング電源装置106は、図1〜図3を用いて説明したように、第一実施形態のスイッチング電源装置10と同様の定常動作を行い、定常動作と並行して演算手段110がパラメータ推定を行う。パラメータ推定は、図23に示すように、スイッチング周期Tよりも十分長い周期Taごとに1回行われ、その1回が期間Tbの間に行われる。

【0121】

期間Tbに入ると、まず、演算手段110が、N個の予測誤差を求めることができるように、期間Tcの間にN回のサンプリング等を行って上記の各信号を取得する。次に、取得した各信号に基づき、N個の予測誤差の二乗の平均値である評価関数J(N)が最小になる複合定数p及びVofsを算出する。そして、タイミングtdになると、従前の複合定数p及びVofsを新たに算出したものに更新する。従って、更新後は新たな複合定数p及びVofsに基づいて出力電圧制御が行われるので、図23に示すように、出力電圧Voが従前の電圧V1から新たな電圧V2に変化する。

【0122】

上記の期間Tbの動作は周期Taごとに繰り返し行われ、定期的に複合定数p及びVofsが更新される。従って、制御回路108は常に適正な複合定数を用いて出力電圧制御を行うことができる。なお、式(35)の評価関数J(N)を使用し、定期的に複合定数p及びVofsを算出する動作は、オフライン最小二乗法を用いたパラメータ推定の一種であるといえる。

【0123】

ここで、スイッチング電源装置106は、図23に示すように、出力電圧信号Vo(1)〜Vo(N)をサンプリングする期間Tcの間、出力電圧Voが電圧V1を挟んで上下に変動している。これは、演算手段110が、上記の定常動作を行うために時比率δを決定するに際して、パラメータ推定を行う期間Tcの間、時比率δを僅かに拡散変動させていることによる。拡散変動とは、図2のフローチャートに従って算出した時比率δをランダム増減させることをいい、この拡散変動によって出力電圧VoをΔVoだけ変動させることができる。従って、この演算手段110を用いて出力電圧Voを意図的に変動させることによって、複合定数p及びVofsの推定を、より高精度に行うことができる。

【0124】

なお、上記のパラメータ推定は、出力電圧Voの変動ΔVoが1m〜10mVもあれば、一定以上の高い精度で行うことができるので、時比率δの拡散変動の幅を必要以上に大きくする必要はない。パラメータ推定の精度がさほど高くなくてよいときは、拡散変動を行わなくても構わない。

【0125】

以上説明したように、この実施形態のスイッチング電源装置106は、第一の実施形態のスイッチング電源装置10と同様の優れた作用効果を得ることができ、さらに、定期的にオフライン最小二乗法を用いたパラメータ推定を行うことによって回路定数の個体差、温度による変化又は経時的な変化を定期的に監視して適正な値に更新するので、高精度な出力電圧制御を継続して行うことができる。

【0126】

また、式(27)と式(33)を用いてパラメータ推定を行うことも可能であるが、その場合、推定する複合定数(a1,a2等)の種類が多くなるので、その分、パラメータ推定の処理にある程度の時間が掛かってしまう。それに対してこの演算手段110は、推定する複合定数が少ない(p,Vofsの2種類のみ)ので、推定の処理を極めて高速に行うことができるという利点がある。

【0127】

なお、この発明のスイッチング電源装置は、上記実施形態に限定されるものではない。例えば、制御回路の演算手段に定義される制御関数式は、入力投入時等の出力電圧の変化の具合を調節するため、式(6)、式(21)〜式(23)のような直線的な関係式ではなく、図24(a)に示すように曲線的な関係式にしてもよい。ただし、図24(b)のような、出力電圧の1つの値に対応する出力微分値が複数存在する制御関数式を使用すると、上述した演算手段の処理を適正に行うことができない。

【0128】

また、第一から第十の実施形態の説明で述べたように、制御回路の演算手段が主スイッチング素子のオン時間、オフ時間、時比率などを算出するとき、「スイッチング周期を一定にする」等の条件設定をすることが望ましい。それによって、時比率などを算出する演算式が、式(20)のように比較的シンプルな形に表すことができるからである。この発明は、様々な電力変換回路のスイッチング電源装置に適用することができ、上記の条件設定は、個々の電力変換回路の動作に応じて適当な方法を選択することができる。

【0129】

例えば、スイッチング周期が一定になることを条件としてオン時間及びオフ時間を決定するPWM制御(図3、図10)、主スイッチング素子14のオン時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御(図13)、及び、主スイッチング素子14のオフ時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御は、上記実施形態で例示した電力変換回路に適用可能である。特に、主スイッチング素子14のオン時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御(図13)は、いわゆる電流共振回路を備えた電力変換回路等の制御に好適である。

【0130】

また、実施形態として例示していないが、主スイッチング素子14のオフ時間が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御も可能である。このPFM制御は、いわゆる電圧共振回路を備えた電力変換回路等の制御に好適である。また、スイッチングの1周期に対するオン時間の時比率が一定になることを条件としてオン時間及びオフ時間を決定するPFM制御も可能であり、例えば、上記実施形態で例示した昇圧チョッパ型、昇降圧チョッパ型、又はフライバック型の電力変換回路に適用し、意図的に電流ゼロ期間が生じるように動作させれば、ダイオードで成る整流素子のリカバリ電流の発生を防止し、スイッチングノイズや主スイッチング素子のクロス損失の発生を抑える効果を得ることができる。

【0131】

また、演算手段等がスイッチング周期に同期した周期でサンプリングし、駆動パルス生成手段がそのサンプリング周期の中間点を挟んで前後の期間を主スイッチング素子のオン期間又はオフ期間とする駆動パルスを生成する、という構成は(図3、図13)、演算手段等がサンプリングするタイミングをいわゆる電流ゼロ期間以外の期間に設定することにより、上記実施形態で例示したいずれの電力変換回路にも適用可能である。当該構成によれば、演算手段が時比率などを算出する演算式が、例えば式(20)のように比較的シンプルな一次式の形に表すことができて処理が簡単になり、また、演算手段等で多少の処理時間が生じたとしても、最大時比率Dmaxや最小時比率Dminの設定を適宜調節すれば当該処理時間の影響をマスクすることも可能である。従って、比較的安価な中低速デジタルICで、上記の制御回路を構成することができるという利点がある。

【0132】

また、演算手段等がスイッチング周期の半分の周期ごとの所定のタイミングでサンプリングし、所定の演算を行って次回のサンプリングタイミングまでの期間の時比率δを算出する、という構成は(図6)、演算手段等が主スイッチング素子のオン期間にもサンプリングを行われるので、昇圧チョッパ型、昇降圧チョッパ型、フライバック型等の電力変換回路には適用できないが、降圧チョッパ型、シングルエンディッドフォワード型、ハーフブリッジ型等の電力変換回路に適用が可能である。

【0133】

また、パラメータ推定を行って回路定数又は複合定数を更新する構成は、電力変換回路の形態や定常動作の形態によらず、適用することができる。ただし、上記の式(27)〜式(35)は降圧チョッパ回路に特有の式なので、他の電力変換回路にそのまま適用することができず、個別に式を導出する必要がある。また、パラメータ推定は、上記のオフライン最小二乗法を用いる以外にも、逐次最小二乗法、その他最小二乗法以外の公知の方法を使用してもよい。

【符号の説明】

【0134】

10,40,50,60,70,76,80,84,90,92,98,106 スイッチング電源装置

14,14a,14b 主スイッチング素子

16,72,72a,72b 整流素子

18 平滑インダクタ

20 平滑コンデンサ

24,74,78,82,96,100,108 制御回路

26a,26b,42a,42b,52a,52b,62a,62b A/D変換器

28,44,54,64,104,110 演算手段

30,46,56,66 駆動パルス生成手段

86 トランス

88 整流側同期整流素子

89 転流側同期整流素子

94 カップリングコンデンサ

102 オブザーバ

【特許請求の範囲】

【請求項1】

オン・オフ動作する主スイッチング素子を含む電力変換回路と、当該オン・オフ動作を制御することによって出力電圧を定電圧化する制御回路とを備えたスイッチング電源装置において、

前記制御回路は、前記主スイッチング素子のオン時間及びオフ時間を決定する演算手段と、前記主スイッチング素子をオン・オフさせる駆動パルスを生成する駆動パルス生成手段とを有し、

前記演算手段には、出力電圧と、当該出力電圧の変化を示す出力微分値とを変数として含み、当該2つの変数の関係を、出力電圧の一つの値に対応する出力微分値が一つだけ存在する連続関数式であって、出力電圧がその出力電圧を定電圧化する目標値よりも低い範囲にあるときは、対応する出力微分値が正の値になり、出力電圧が目標値よりも高い範囲にあるときは、対応する出力微分値が負の値になり、出力電圧が目標値に等しいときは、対応する出力微分値がゼロになるように規定する制御関数式が定義され、

前記演算手段は、

主スイッチング素子のスイッチング周期に同期したタイミングで、入力電圧を検出した入力電圧信号と、出力電圧を検出又は推定した出力電圧信号とをサンプリングし、

サンプリングした当該2つの信号に基づいて導出される次回又はそれ以降のサンプリングタイミングにおける出力電圧信号及び出力微分値が前記制御関数式に規定される関係を満たすように、当該サンプリングタイミング以降のスイッチング周期における主スイッチング素子のオン時間及びオフ時間のうちの少なくとも一方を算出する演算処理を行い、

前記駆動パルス生成手段は、上記2つの信号のサンプリングタイミング以降のスイッチング周期において、前記演算手段が決定したオン時間及びオフ時間に基づいて前記主スイッチング素子をオン・オフさせるよう、駆動パルスを生成することを特徴とするスイッチング電源装置。

【請求項2】

前記演算手段は、前記各信号のサンプリングと、オン時間及びオフ時間のうちの少なくとも一方を算出する演算処理とを、前記主スイッチング素子のスイッチング周期ごとに行う請求項1記載のスイッチング電源装置。

【請求項3】

前記電力変換回路は、前記主スイッチング素子のオン期間に、入力直流電源から出力への電力供給を止めて入力直流電源によって内蔵するインダクタンス素子を励磁し、前記主スイッチング素子のオフ期間に、前記インダクタンス素子に蓄積された励磁エネルギーを出力に放出して電力供給をする動作を行い、

前記演算手段は、前記各信号のサンプリングを、前記インダクタンス素子が励磁エネルギーを放出している期間に行う請求項2記載のスイッチング電源装置。

【請求項4】