パルスパターン発生装置及び該装置を用いた誤り率測定システム並びにパルスパターン発生方法

【課題】発生できるパルスパターンの種類を増やす。

【解決手段】差動クロック発生部4は、所定周期の正相クロックと、正相クロックと位相が反転した反転クロックとを発生する。クロック選択部5は、差動クロック発生部4が発生する正相クロック又は反転クロックの何れかのクロックを選択する。データ保持部3は、クロック選択部5で選択された正相クロック又は反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力する。パルスパターン発生部7は、データ保持部3から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生する。

【解決手段】差動クロック発生部4は、所定周期の正相クロックと、正相クロックと位相が反転した反転クロックとを発生する。クロック選択部5は、差動クロック発生部4が発生する正相クロック又は反転クロックの何れかのクロックを選択する。データ保持部3は、クロック選択部5で選択された正相クロック又は反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力する。パルスパターン発生部7は、データ保持部3から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、所望のパルスパターンを発生するパルスパターン発生装置及びパルスパターン発生方法に関するとともに、パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物に入力し、この試験用信号の入力に伴う被測定信号の誤り率を測定する誤り率測定システムに関する。

【背景技術】

【0002】

近年、各種のディジタル有線通信装置は、利用者数の増加やマルチメディア通信の普及に伴い、より大容量の伝送能力が求められている。そして、これらのディジタル有線通信装置におけるディジタル信号の品質評価の指標の一つとして、受信データのうち符号誤りが発生した数と受信データの総数との比較として定義されるビット誤り率(Bit Error Rate)が知られている。

【0003】

上述したビット誤り率を測定する誤り率測定システムでは、試験対象物(DUT:Device Under Test )に対して予め決められた試験用信号を送信し、この試験用信号の送信に伴って試験対象物を介して入力される被測定信号と、試験対象物に送信した試験用信号とを比較して被測定信号の誤り率を測定している。

【0004】

ところで、安価かつ高速化を図った高速バスを有するコネクタ付き回路実装基板を試験対象物(DUT)とした場合、この試験対象物に同軸ケーブルを介して電気信号や光信号を用いたデジタル信号を入力すると、試験対象物の特性によってデジタル信号の波形品質が劣化する。そして、この波形品質の劣化によりビット誤り率の増加、ジッタの増加、波形の振幅変動、アイパターンの形状変化などが生じる。

【0005】

ここで、上記試験対象物の波形品質の劣化を試験する場合には、図4に示すような測定系100が一般的に用いられる。図4の測定系100では、試験対象物Wの入力側にパルスパターン発生装置101を接続し、試験対象物Wの出力側に誤り率測定装置102を接続した状態で、パルスパターン発生装置101から所定パターンの試験用信号を試験対象物Wに入力し、この試験用信号の入力に伴って試験対象物Wから出力される信号を誤り率測定装置102で受信する。そして、誤り率測定装置102において、受信信号と試験対象物Wに入力した試験用信号とを比較し、ビット誤り率やアイパターンを測定して試験対象物Wの各種試験を行っている。

【0006】

しかしながら、図4の測定系100において、プリエンファシスされていない試験用信号をそのまま同軸ケーブルを介して試験対象物Wに入力すると、周波数の高い方に向うに連れて信号に歪みが生じて減衰し、これによりビット誤り率が悪化し、正常なビット誤り率測定を行うことができなかった。

【0007】

そこで、上述した信号の歪みを克服するべく信号の減衰する部分を補って試験用信号を忠実に生成するための有効な解決策として、元信号となる試験用信号にプリエンファシスをかけることが考えられる。このプリエンファシスされた信号を生成する装置及び方法としては、例えば下記特許文献1に開示されるものが知られている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−271552号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、上述した試験対象物Wの各種試験を行うにあたっては、信号の高速化や新しい規格に対応するべく、発生できるパルスパターンの任意度を高めることが要求される。このため、パルスパターン発生装置としては、より多くの種類のパルスパターンを発生できることが好ましく、誤り率測定システムとしては、より細かい測定が行えることが望まれていた。

【0010】

そこで、本発明は上記問題点に鑑みてなされたものであって、発生できるパルスパターンの種類を増やすことができるパルスパターン発生装置及びパルスパターン発生装置を提供すること、また、より細かい誤り率測定が可能な誤り率測定システムを提供することを目的としている。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の請求項1に記載されたパルスパターン発生装置は、所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生する差動クロック発生部4と、

前記差動クロック発生部が発生する前記正相クロック又は前記反転クロックの何れかのクロックを選択するクロック選択部5と、

前記クロック選択部で選択された前記正相クロック又は前記反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力するデータ保持部3と、

前記データ保持部から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するパルスパターン発生部7とを備えたことを特徴とする。

【0012】

請求項2に記載されたパルスパターン発生装置は、請求項1のパルスパターン発生装置において、

前記データ保持部3は、ホールドタイムが半ビットより短い時間の複数段のD型フリップフロップ回路からなることを特徴とする。

【0013】

請求項3に記載された誤り率測定システムは、請求項1又は2記載のパルスパターン発生装置を用いた誤り率測定システムであって、

前記パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物Wに入力し、この試験用信号の入力に伴う前記試験対象物からの被測定信号と、前記試験対象物に入力した前記試験用信号とを比較して前記被測定信号の誤り率を測定することを特徴とする。

【0014】

請求項4に記載されたパルスパターン発生方法は、所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生するステップと、

前記正相クロック又は前記反転クロックの何れかのクロックを選択するステップと、

前記選択されたクロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力ステップと、

前記保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するステップとを含むことを特徴とする。

【発明の効果】

【0015】

本発明に係るパルスパターン発生装置及びパルスパターン発生方法によれば、発生できるパルスパターンの種類を増やすことができ、発生できるパルスパターンの任意度を高めることができる。

【0016】

本発明に係る誤り率測定システムによれば、上記パルスパターン発生装置を用いることにより、試験対象物に入力されるパルスパターンの種類も増えるので、より細かい誤り率測定を行うことができる。

【図面の簡単な説明】

【0017】

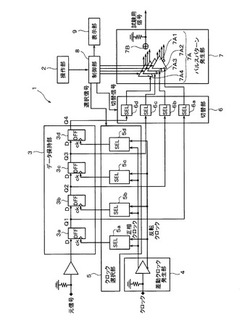

【図1】本発明に係るパルスパターン発生装置の内部構成の一例を示すブロック図である。

【図2】本発明に係るパルスパターン発生装置のタイミングチャートを示す図である。

【図3】本発明に係るパルスパターン発生装置を用いた誤り率測定システムの一例を示すブロック図である。

【図4】試験対象物の波形品質の劣化を試験する場合の一般的な測定系の概略構成図である。

【発明を実施するための形態】

【0018】

以下、本発明を実施するための形態について図面を参照しながら具体的に説明する。図1は本発明に係るパルスパターン発生装置の内部構成の一例を示すブロック図、図2は図1のパルスパターン発生装置のタイミングチャートを示す図、図3は本発明に係るパルスパターン発生装置を用いた誤り率測定システムの一例を示すブロック図である。

【0019】

図1に示すように、パルスパターン発生装置1は、操作部2、データ保持部3、差動クロック発生部4、クロック選択部5、切替部6、パルスパターン発生部7、制御部8、表示部9を備えて概略構成される。

【0020】

操作部2は、所望のパルスパターンを発生させるための各種操作として、例えば後述するクロック選択部5の正相クロック又は反転クロックの選択操作、後述する切替部6の切替操作、発生するパルスパターン(試験用信号)の元信号の1ビット単位又は半ビット単位の振幅可変を指示する操作、発生するパルスパターン(試験用信号)の波形表示を指示する操作などを行っている。

【0021】

データ保持部3は、ck(クロック)端子の立ち上がりのエッジでD端子の入力の値がQ出力として保持される4つのD型フリップフロップ回路(以下、DFFと略称する)3a、3b、3c、3dを直列接続して構成される。データ保持部3は、初段のDFF3aのD端子に図2(b)に示すような元信号が入力され、クロック選択部5によるクロックの選択に応じて位相が1ビットずれ又は半ビットずれとなる4つのデータ信号に分岐して各DFF3a,3b,3c,3dのQ端子から出力している。

【0022】

尚、データ保持部3の各段のDFF3a,3b,3c,3dは、クロック選択部5で選択されたクロック(正相クロック又は反転クロック)のエッジのタイミングでD端子の入力を保持出力している。これらDFF3a,3b,3c,3dのホールドタイムは、最小の強調時間幅である半ビットよりも短い時間であることが条件となる。また、セットアップタイムに関しては、0又は最小の強調時間幅より長い時間であることが条件となる。

【0023】

差動クロック発生部4は、最小の強調時間幅を決定付けるための差動クロックを発生している。この差動クロック発生部4が発生する差動クロックは、図2(a)に示すような所定周期の正相クロックと、この正相クロックを反転した反転クロックとからなる。

【0024】

クロック選択部5は、入力側が差動クロック発生部4に接続され、出力側がデータ保持部3の各DFF3a,3b,3c,3dのck端子と1対1に対応して接続される4つのセレクタ5a,5b,5c,5dで構成される。クロック選択部5の各セレクタ5a,5b,5c,5dは、操作部2の操作に基づく制御部8からの選択信号により、差動クロック発生部4が発生する差動クロックにおける正相クロックと反転クロックの何れかのクロックを選択している。

【0025】

切替部6は、データ保持部3の4つのDFF3a,3b,3c,3dのQ端子と1対1に対応して接続される4つのセレクタ6a,6b,6c,6dで構成される。切替部6の各セレクタ6a,6b,6c,6dは、操作部2の操作に基づく制御部8から切替信号の入力により、極性が「POS(ポジティブ)」又は「NEG(ネガティブ)」の何れかの状態に予め設定されている。

【0026】

パルスパターン発生部7は、試験対象物Wの試験用信号として用いるためのパルスパターンを発生するもので、増幅回路7Aと加算回路7Bを備えている。

【0027】

増幅回路7Aは、切替部6の4つのセレクタ6a,6b,6c,6dの出力と1対1に対応して接続される4つの増幅器7A1,7A2,7A3,7A4で構成される。これら4つの増幅器7A1,7A2,7A3,7A4は、操作部2の操作に基づく制御部8からの制御信号(4つの制御電圧)によって個別に電圧が制御される。

【0028】

加算回路7Bは、増幅回路7Aの4つの増幅器7A1,7A2,7A3,7A4の出力を加算し、元信号を1ビット単位又は半ビット単位で振幅を可変した信号を試験用信号として出力している。

【0029】

制御部8は、操作部2からの操作により、データ保持部3からのデータの取り込み、差動クロック発生部4によるクロックの発生、クロック選択部5への選択信号の出力、切替部6への切替信号の出力、パルスパターン発生部7によるパルスパターンの出力、表示部9へのパルスパターンの波形表示などを統括制御している。

【0030】

表示部9は、例えば液晶表示器などで構成され、操作部2の操作に基づく制御部8の制御により、パルスパターン発生部7が発生するパルスパターン(試験用信号)の波形を表示している。

【0031】

尚、図1の例では、操作部2と表示部9を機能分けして別々のブロックで示したが、これらをコンピュータグラフィックスとマウスなどのポインティングデバイスを用いた直感的な操作により各種の操作・設定が行える機能を有するGUI(graphical user interface)で構成することもできる。

【0032】

次に、上記のように構成されるパルスパターン発生装置1の動作について図2(a)〜(e)を参照しながら説明する。尚、図2(a)〜(e)は、説明の簡略化を図るため、2タップのパルスパターンを発生する場合のタイミングチャートの一例を示しており、データ保持部3の初段のDFF3aに接続されるセレクタ5aが正相クロックを選択し、2段目のDFF3bに接続されるセレクタ5bが反転クロックを選択しているものとしている。

【0033】

データ保持部3の初段のDFF3aは、図2(b)に示す元信号のデータ(1,1,0,0,0,1,0,0,1,・・・)が入力されると、図2(a)の正相クロックの立ち上がりのタイミング(図中A)で元信号のデータをラッチする。このラッチした元信号のデータは、DFF3aの遅延時間tだけ遅れて出力される。また、データ保持部3の2段目のDFF3bは、初段のDFF3aからデータが入力されると、反転クロックの立ち上がりのタイミング(図中B)でデータをラッチする。このラッチしたデータは、DFF3bの遅延時間tだけ遅れて出力される。これにより、データ保持部3の初段のDFF3aと2段目のDFF3bからは、半ビット位相の異なるデータが出力される。そして、パルスパターン発生部7では、これら半ビット位相の異なるデータに対し、例えばDFF3aの出力Q1−(DFF3bの出力Q2×0.5)の処理を施すと、図2(e)に示すような振幅が半ビッチ幅で可変されたパルスパターンを試験用信号として発生する。

【0034】

そして、上記のように構成されて動作するパルスパターン発生装置1は、例えば図3に示すような誤り率測定システム11に採用することができる。

【0035】

図3の誤り率測定システム11は、上述したパルスパターン発生装置1と、誤り率測定装置21とから構築され、例えば高速バスを有するコネクタ付き回路実装基板などの試験対象物(DUT)Wに対し、同軸ケーブルなどの伝送路を介してパルスパターン発生装置1から所望のパルスパターンからなる試験用信号を入力し、この試験用信号の入力に伴って試験対象物Wから出力される信号を受信し、受信信号と試験対象物Wに入力した試験用信号とを比較し、ビット誤り率やアイパターンを測定して試験対象物Wの各種試験を行っている。

【0036】

すなわち、この誤り率測定システム11では、パルスパターン発生装置1が所望のパルスパターン(基準パターン)の試験用信号を発生し、この発生したパルスパターンの試験用信号を試験対象物Wに出力している。

【0037】

誤り率測定装置21は、図3に示すように、誤り率検出部22、波形表示部23、制御部24を備えて概略構成される。

【0038】

誤り率検出部22は、パルスパターン発生装置1が発生する試験用信号の入力に伴う試験対象物Wからの被測定信号と、試験対象物Wに入力しているパルスパターンとを比較して被測定信号の誤り率を検出している。

【0039】

波形表示部23は、例えばサンプリングオシロスコープなどのアナログ測定波形をデジタル信号に変換し、この変換されたデジタル信号を波形データとして内部メモリに取り込み、電圧や電流の値が時間的に変化する事象を離散的にサンプリングして得た波形データに基づいて表示画面上に波形画像を再生表示している。

【0040】

制御部24は、試験対象物Wへの試験用信号の入力制御、この試験対象物Wへの試験用信号の入力に伴う試験対象物Wからの被測定信号の誤り率を測定しつつ入力信号の波形を表示するべく、パルスパターン発生装置1、誤り率検出部22、波形表示部23を統括制御している。

【0041】

尚、図3の例では、パルスパターン発生装置1を誤り率測定装置21と別体の構成として説明したが、パルスパターン発生装置1を誤り率測定装置21と一体に構成することもできる。また、誤り率測定装置21としては、パルスパターン発生装置1が発生するパルスパターンを試験用信号として試験対象物Wに入力し、この試験用信号の入力に伴う試験対象物Wからの被測定信号のビット誤り率やアイパターンを測定できる機能を少なくとも有する構成であればよい。

【0042】

このように、本例の図1に示すパルスパターン発生装置1では、複数段のDFF3a,3b,3c,3dでデータ保持部3を構成し、初段のDFF3aに正相クロックを選択して用い、2段目のDFF3bについて、初段のDFF3aと位相が反転した反転クロックを用いてDFF3bを通過させると、半ビット位相の異なるデータを出力する。これに対し、2段目のDFF3bについて、初段のDFF3aと位相が同じ正相クロックを用いてDFF3bを通過させると、1ビット位相の異なるデータを出力する。すなわち、データ保持部3では、前段のDFFのクロックと位相が同じ正相クロックを用いてDFFを通過させれば、1ビット位相の異なるデータを出力し、前段のDFFのクロックと位相が反転した反転クロックを用いてDFFを通過させれば、半ビット位相の異なるデータを出力する。

【0043】

これにより、パルスパターン発生部7が発生できるパルスパターンの種類を増やすことができ、発生できるパルスパターンの任意度を高めることができる。具体的には、半ビット幅単位又は1ビット幅単位で振幅方向を強調、抑制することができる。

【0044】

ここで、上述したような位相の異なる複数の同じパターンを発生させるにあたっては、キャパシタの電圧維持機能を利用した遅延回路を複数段接続する構成が考えられる。しかしながら、この構成では、遅延回路の後段に向かうに連れてS/Nが蓄積されて悪化するという問題がある。

【0045】

これに対し、本例のパルスパターン発生装置1におけるデータ保持部3の各段のDFF3a,3b,3c,3dは、差動クロック発生部4からの同じクロックのエッジで出力タイミングが決まるので、各DFF3a,3b,3c,3dの位相タイミングのずれも少なく、DFFのホールドタイム(最小の強調時間幅)に制限され、S/Nの悪化を抑えることができる。

【0046】

そして、上述したパルスパターン発生装置1を用いた誤り率測定システム11によれば、試験対象物Wに入力できるパルスパターンの種類が増えるため、より細かい誤り率測定を行うことができる。

【符号の説明】

【0047】

1 パルスパターン発生装置

2 操作部

3 データ保持部

4 差動クロック発生部

5 クロック選択部

6 切替部

7 パルスパターン発生部

8 制御部

9 表示部

11 誤り率測定システム

21 誤り率測定装置

22 誤り率検出部

23 波形表示部

24 制御部

W 試験対象物(DUT)

【技術分野】

【0001】

本発明は、所望のパルスパターンを発生するパルスパターン発生装置及びパルスパターン発生方法に関するとともに、パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物に入力し、この試験用信号の入力に伴う被測定信号の誤り率を測定する誤り率測定システムに関する。

【背景技術】

【0002】

近年、各種のディジタル有線通信装置は、利用者数の増加やマルチメディア通信の普及に伴い、より大容量の伝送能力が求められている。そして、これらのディジタル有線通信装置におけるディジタル信号の品質評価の指標の一つとして、受信データのうち符号誤りが発生した数と受信データの総数との比較として定義されるビット誤り率(Bit Error Rate)が知られている。

【0003】

上述したビット誤り率を測定する誤り率測定システムでは、試験対象物(DUT:Device Under Test )に対して予め決められた試験用信号を送信し、この試験用信号の送信に伴って試験対象物を介して入力される被測定信号と、試験対象物に送信した試験用信号とを比較して被測定信号の誤り率を測定している。

【0004】

ところで、安価かつ高速化を図った高速バスを有するコネクタ付き回路実装基板を試験対象物(DUT)とした場合、この試験対象物に同軸ケーブルを介して電気信号や光信号を用いたデジタル信号を入力すると、試験対象物の特性によってデジタル信号の波形品質が劣化する。そして、この波形品質の劣化によりビット誤り率の増加、ジッタの増加、波形の振幅変動、アイパターンの形状変化などが生じる。

【0005】

ここで、上記試験対象物の波形品質の劣化を試験する場合には、図4に示すような測定系100が一般的に用いられる。図4の測定系100では、試験対象物Wの入力側にパルスパターン発生装置101を接続し、試験対象物Wの出力側に誤り率測定装置102を接続した状態で、パルスパターン発生装置101から所定パターンの試験用信号を試験対象物Wに入力し、この試験用信号の入力に伴って試験対象物Wから出力される信号を誤り率測定装置102で受信する。そして、誤り率測定装置102において、受信信号と試験対象物Wに入力した試験用信号とを比較し、ビット誤り率やアイパターンを測定して試験対象物Wの各種試験を行っている。

【0006】

しかしながら、図4の測定系100において、プリエンファシスされていない試験用信号をそのまま同軸ケーブルを介して試験対象物Wに入力すると、周波数の高い方に向うに連れて信号に歪みが生じて減衰し、これによりビット誤り率が悪化し、正常なビット誤り率測定を行うことができなかった。

【0007】

そこで、上述した信号の歪みを克服するべく信号の減衰する部分を補って試験用信号を忠実に生成するための有効な解決策として、元信号となる試験用信号にプリエンファシスをかけることが考えられる。このプリエンファシスされた信号を生成する装置及び方法としては、例えば下記特許文献1に開示されるものが知られている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開2008−271552号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

ところで、上述した試験対象物Wの各種試験を行うにあたっては、信号の高速化や新しい規格に対応するべく、発生できるパルスパターンの任意度を高めることが要求される。このため、パルスパターン発生装置としては、より多くの種類のパルスパターンを発生できることが好ましく、誤り率測定システムとしては、より細かい測定が行えることが望まれていた。

【0010】

そこで、本発明は上記問題点に鑑みてなされたものであって、発生できるパルスパターンの種類を増やすことができるパルスパターン発生装置及びパルスパターン発生装置を提供すること、また、より細かい誤り率測定が可能な誤り率測定システムを提供することを目的としている。

【課題を解決するための手段】

【0011】

上記目的を達成するため、本発明の請求項1に記載されたパルスパターン発生装置は、所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生する差動クロック発生部4と、

前記差動クロック発生部が発生する前記正相クロック又は前記反転クロックの何れかのクロックを選択するクロック選択部5と、

前記クロック選択部で選択された前記正相クロック又は前記反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力するデータ保持部3と、

前記データ保持部から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するパルスパターン発生部7とを備えたことを特徴とする。

【0012】

請求項2に記載されたパルスパターン発生装置は、請求項1のパルスパターン発生装置において、

前記データ保持部3は、ホールドタイムが半ビットより短い時間の複数段のD型フリップフロップ回路からなることを特徴とする。

【0013】

請求項3に記載された誤り率測定システムは、請求項1又は2記載のパルスパターン発生装置を用いた誤り率測定システムであって、

前記パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物Wに入力し、この試験用信号の入力に伴う前記試験対象物からの被測定信号と、前記試験対象物に入力した前記試験用信号とを比較して前記被測定信号の誤り率を測定することを特徴とする。

【0014】

請求項4に記載されたパルスパターン発生方法は、所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生するステップと、

前記正相クロック又は前記反転クロックの何れかのクロックを選択するステップと、

前記選択されたクロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力ステップと、

前記保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するステップとを含むことを特徴とする。

【発明の効果】

【0015】

本発明に係るパルスパターン発生装置及びパルスパターン発生方法によれば、発生できるパルスパターンの種類を増やすことができ、発生できるパルスパターンの任意度を高めることができる。

【0016】

本発明に係る誤り率測定システムによれば、上記パルスパターン発生装置を用いることにより、試験対象物に入力されるパルスパターンの種類も増えるので、より細かい誤り率測定を行うことができる。

【図面の簡単な説明】

【0017】

【図1】本発明に係るパルスパターン発生装置の内部構成の一例を示すブロック図である。

【図2】本発明に係るパルスパターン発生装置のタイミングチャートを示す図である。

【図3】本発明に係るパルスパターン発生装置を用いた誤り率測定システムの一例を示すブロック図である。

【図4】試験対象物の波形品質の劣化を試験する場合の一般的な測定系の概略構成図である。

【発明を実施するための形態】

【0018】

以下、本発明を実施するための形態について図面を参照しながら具体的に説明する。図1は本発明に係るパルスパターン発生装置の内部構成の一例を示すブロック図、図2は図1のパルスパターン発生装置のタイミングチャートを示す図、図3は本発明に係るパルスパターン発生装置を用いた誤り率測定システムの一例を示すブロック図である。

【0019】

図1に示すように、パルスパターン発生装置1は、操作部2、データ保持部3、差動クロック発生部4、クロック選択部5、切替部6、パルスパターン発生部7、制御部8、表示部9を備えて概略構成される。

【0020】

操作部2は、所望のパルスパターンを発生させるための各種操作として、例えば後述するクロック選択部5の正相クロック又は反転クロックの選択操作、後述する切替部6の切替操作、発生するパルスパターン(試験用信号)の元信号の1ビット単位又は半ビット単位の振幅可変を指示する操作、発生するパルスパターン(試験用信号)の波形表示を指示する操作などを行っている。

【0021】

データ保持部3は、ck(クロック)端子の立ち上がりのエッジでD端子の入力の値がQ出力として保持される4つのD型フリップフロップ回路(以下、DFFと略称する)3a、3b、3c、3dを直列接続して構成される。データ保持部3は、初段のDFF3aのD端子に図2(b)に示すような元信号が入力され、クロック選択部5によるクロックの選択に応じて位相が1ビットずれ又は半ビットずれとなる4つのデータ信号に分岐して各DFF3a,3b,3c,3dのQ端子から出力している。

【0022】

尚、データ保持部3の各段のDFF3a,3b,3c,3dは、クロック選択部5で選択されたクロック(正相クロック又は反転クロック)のエッジのタイミングでD端子の入力を保持出力している。これらDFF3a,3b,3c,3dのホールドタイムは、最小の強調時間幅である半ビットよりも短い時間であることが条件となる。また、セットアップタイムに関しては、0又は最小の強調時間幅より長い時間であることが条件となる。

【0023】

差動クロック発生部4は、最小の強調時間幅を決定付けるための差動クロックを発生している。この差動クロック発生部4が発生する差動クロックは、図2(a)に示すような所定周期の正相クロックと、この正相クロックを反転した反転クロックとからなる。

【0024】

クロック選択部5は、入力側が差動クロック発生部4に接続され、出力側がデータ保持部3の各DFF3a,3b,3c,3dのck端子と1対1に対応して接続される4つのセレクタ5a,5b,5c,5dで構成される。クロック選択部5の各セレクタ5a,5b,5c,5dは、操作部2の操作に基づく制御部8からの選択信号により、差動クロック発生部4が発生する差動クロックにおける正相クロックと反転クロックの何れかのクロックを選択している。

【0025】

切替部6は、データ保持部3の4つのDFF3a,3b,3c,3dのQ端子と1対1に対応して接続される4つのセレクタ6a,6b,6c,6dで構成される。切替部6の各セレクタ6a,6b,6c,6dは、操作部2の操作に基づく制御部8から切替信号の入力により、極性が「POS(ポジティブ)」又は「NEG(ネガティブ)」の何れかの状態に予め設定されている。

【0026】

パルスパターン発生部7は、試験対象物Wの試験用信号として用いるためのパルスパターンを発生するもので、増幅回路7Aと加算回路7Bを備えている。

【0027】

増幅回路7Aは、切替部6の4つのセレクタ6a,6b,6c,6dの出力と1対1に対応して接続される4つの増幅器7A1,7A2,7A3,7A4で構成される。これら4つの増幅器7A1,7A2,7A3,7A4は、操作部2の操作に基づく制御部8からの制御信号(4つの制御電圧)によって個別に電圧が制御される。

【0028】

加算回路7Bは、増幅回路7Aの4つの増幅器7A1,7A2,7A3,7A4の出力を加算し、元信号を1ビット単位又は半ビット単位で振幅を可変した信号を試験用信号として出力している。

【0029】

制御部8は、操作部2からの操作により、データ保持部3からのデータの取り込み、差動クロック発生部4によるクロックの発生、クロック選択部5への選択信号の出力、切替部6への切替信号の出力、パルスパターン発生部7によるパルスパターンの出力、表示部9へのパルスパターンの波形表示などを統括制御している。

【0030】

表示部9は、例えば液晶表示器などで構成され、操作部2の操作に基づく制御部8の制御により、パルスパターン発生部7が発生するパルスパターン(試験用信号)の波形を表示している。

【0031】

尚、図1の例では、操作部2と表示部9を機能分けして別々のブロックで示したが、これらをコンピュータグラフィックスとマウスなどのポインティングデバイスを用いた直感的な操作により各種の操作・設定が行える機能を有するGUI(graphical user interface)で構成することもできる。

【0032】

次に、上記のように構成されるパルスパターン発生装置1の動作について図2(a)〜(e)を参照しながら説明する。尚、図2(a)〜(e)は、説明の簡略化を図るため、2タップのパルスパターンを発生する場合のタイミングチャートの一例を示しており、データ保持部3の初段のDFF3aに接続されるセレクタ5aが正相クロックを選択し、2段目のDFF3bに接続されるセレクタ5bが反転クロックを選択しているものとしている。

【0033】

データ保持部3の初段のDFF3aは、図2(b)に示す元信号のデータ(1,1,0,0,0,1,0,0,1,・・・)が入力されると、図2(a)の正相クロックの立ち上がりのタイミング(図中A)で元信号のデータをラッチする。このラッチした元信号のデータは、DFF3aの遅延時間tだけ遅れて出力される。また、データ保持部3の2段目のDFF3bは、初段のDFF3aからデータが入力されると、反転クロックの立ち上がりのタイミング(図中B)でデータをラッチする。このラッチしたデータは、DFF3bの遅延時間tだけ遅れて出力される。これにより、データ保持部3の初段のDFF3aと2段目のDFF3bからは、半ビット位相の異なるデータが出力される。そして、パルスパターン発生部7では、これら半ビット位相の異なるデータに対し、例えばDFF3aの出力Q1−(DFF3bの出力Q2×0.5)の処理を施すと、図2(e)に示すような振幅が半ビッチ幅で可変されたパルスパターンを試験用信号として発生する。

【0034】

そして、上記のように構成されて動作するパルスパターン発生装置1は、例えば図3に示すような誤り率測定システム11に採用することができる。

【0035】

図3の誤り率測定システム11は、上述したパルスパターン発生装置1と、誤り率測定装置21とから構築され、例えば高速バスを有するコネクタ付き回路実装基板などの試験対象物(DUT)Wに対し、同軸ケーブルなどの伝送路を介してパルスパターン発生装置1から所望のパルスパターンからなる試験用信号を入力し、この試験用信号の入力に伴って試験対象物Wから出力される信号を受信し、受信信号と試験対象物Wに入力した試験用信号とを比較し、ビット誤り率やアイパターンを測定して試験対象物Wの各種試験を行っている。

【0036】

すなわち、この誤り率測定システム11では、パルスパターン発生装置1が所望のパルスパターン(基準パターン)の試験用信号を発生し、この発生したパルスパターンの試験用信号を試験対象物Wに出力している。

【0037】

誤り率測定装置21は、図3に示すように、誤り率検出部22、波形表示部23、制御部24を備えて概略構成される。

【0038】

誤り率検出部22は、パルスパターン発生装置1が発生する試験用信号の入力に伴う試験対象物Wからの被測定信号と、試験対象物Wに入力しているパルスパターンとを比較して被測定信号の誤り率を検出している。

【0039】

波形表示部23は、例えばサンプリングオシロスコープなどのアナログ測定波形をデジタル信号に変換し、この変換されたデジタル信号を波形データとして内部メモリに取り込み、電圧や電流の値が時間的に変化する事象を離散的にサンプリングして得た波形データに基づいて表示画面上に波形画像を再生表示している。

【0040】

制御部24は、試験対象物Wへの試験用信号の入力制御、この試験対象物Wへの試験用信号の入力に伴う試験対象物Wからの被測定信号の誤り率を測定しつつ入力信号の波形を表示するべく、パルスパターン発生装置1、誤り率検出部22、波形表示部23を統括制御している。

【0041】

尚、図3の例では、パルスパターン発生装置1を誤り率測定装置21と別体の構成として説明したが、パルスパターン発生装置1を誤り率測定装置21と一体に構成することもできる。また、誤り率測定装置21としては、パルスパターン発生装置1が発生するパルスパターンを試験用信号として試験対象物Wに入力し、この試験用信号の入力に伴う試験対象物Wからの被測定信号のビット誤り率やアイパターンを測定できる機能を少なくとも有する構成であればよい。

【0042】

このように、本例の図1に示すパルスパターン発生装置1では、複数段のDFF3a,3b,3c,3dでデータ保持部3を構成し、初段のDFF3aに正相クロックを選択して用い、2段目のDFF3bについて、初段のDFF3aと位相が反転した反転クロックを用いてDFF3bを通過させると、半ビット位相の異なるデータを出力する。これに対し、2段目のDFF3bについて、初段のDFF3aと位相が同じ正相クロックを用いてDFF3bを通過させると、1ビット位相の異なるデータを出力する。すなわち、データ保持部3では、前段のDFFのクロックと位相が同じ正相クロックを用いてDFFを通過させれば、1ビット位相の異なるデータを出力し、前段のDFFのクロックと位相が反転した反転クロックを用いてDFFを通過させれば、半ビット位相の異なるデータを出力する。

【0043】

これにより、パルスパターン発生部7が発生できるパルスパターンの種類を増やすことができ、発生できるパルスパターンの任意度を高めることができる。具体的には、半ビット幅単位又は1ビット幅単位で振幅方向を強調、抑制することができる。

【0044】

ここで、上述したような位相の異なる複数の同じパターンを発生させるにあたっては、キャパシタの電圧維持機能を利用した遅延回路を複数段接続する構成が考えられる。しかしながら、この構成では、遅延回路の後段に向かうに連れてS/Nが蓄積されて悪化するという問題がある。

【0045】

これに対し、本例のパルスパターン発生装置1におけるデータ保持部3の各段のDFF3a,3b,3c,3dは、差動クロック発生部4からの同じクロックのエッジで出力タイミングが決まるので、各DFF3a,3b,3c,3dの位相タイミングのずれも少なく、DFFのホールドタイム(最小の強調時間幅)に制限され、S/Nの悪化を抑えることができる。

【0046】

そして、上述したパルスパターン発生装置1を用いた誤り率測定システム11によれば、試験対象物Wに入力できるパルスパターンの種類が増えるため、より細かい誤り率測定を行うことができる。

【符号の説明】

【0047】

1 パルスパターン発生装置

2 操作部

3 データ保持部

4 差動クロック発生部

5 クロック選択部

6 切替部

7 パルスパターン発生部

8 制御部

9 表示部

11 誤り率測定システム

21 誤り率測定装置

22 誤り率検出部

23 波形表示部

24 制御部

W 試験対象物(DUT)

【特許請求の範囲】

【請求項1】

所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生する差動クロック発生部(4)と、

前記差動クロック発生部が発生する前記正相クロック又は前記反転クロックの何れかのクロックを選択するクロック選択部(5)と、

前記クロック選択部で選択された前記正相クロック又は前記反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力するデータ保持部(3)と、

前記データ保持部から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するパルスパターン発生部(7)とを備えたことを特徴とするパルスパターン発生装置。

【請求項2】

前記データ保持部(3)は、ホールドタイムが半ビットより短い時間の複数段のD型フリップフロップ回路からなることを特徴とする請求項1記載のパルスパターン発生装置。

【請求項3】

請求項1又は2記載のパルスパターン発生装置(1)を用いた誤り率測定システム(11)であって、

前記パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物(W)に入力し、この試験用信号の入力に伴う前記試験対象物からの被測定信号と、前記試験対象物に入力した前記試験用信号とを比較して前記被測定信号の誤り率を測定することを特徴とする誤り率測定システム。

【請求項4】

所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生するステップと、

前記正相クロック又は前記反転クロックの何れかのクロックを選択するステップと、

前記選択されたクロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力ステップと、

前記保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するステップとを含むことを特徴とするパルスパターン発生方法。

【請求項1】

所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生する差動クロック発生部(4)と、

前記差動クロック発生部が発生する前記正相クロック又は前記反転クロックの何れかのクロックを選択するクロック選択部(5)と、

前記クロック選択部で選択された前記正相クロック又は前記反転クロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力するデータ保持部(3)と、

前記データ保持部から保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するパルスパターン発生部(7)とを備えたことを特徴とするパルスパターン発生装置。

【請求項2】

前記データ保持部(3)は、ホールドタイムが半ビットより短い時間の複数段のD型フリップフロップ回路からなることを特徴とする請求項1記載のパルスパターン発生装置。

【請求項3】

請求項1又は2記載のパルスパターン発生装置(1)を用いた誤り率測定システム(11)であって、

前記パルスパターン発生装置が発生するパルスパターンを試験用信号として試験対象物(W)に入力し、この試験用信号の入力に伴う前記試験対象物からの被測定信号と、前記試験対象物に入力した前記試験用信号とを比較して前記被測定信号の誤り率を測定することを特徴とする誤り率測定システム。

【請求項4】

所定周期の正相クロックと、該正相クロックと位相が反転した反転クロックとを発生するステップと、

前記正相クロック又は前記反転クロックの何れかのクロックを選択するステップと、

前記選択されたクロックにより、1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータを保持出力ステップと、

前記保持出力される1ビット又は半ビットずつ位相の異なる複数の同じパターンのデータの振幅方向が1ビット又は半ビット単位で強調又は抑制されたパルスパターンを発生するステップとを含むことを特徴とするパルスパターン発生方法。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2012−142902(P2012−142902A)

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願番号】特願2011−1316(P2011−1316)

【出願日】平成23年1月6日(2011.1.6)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

【公開日】平成24年7月26日(2012.7.26)

【国際特許分類】

【出願日】平成23年1月6日(2011.1.6)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

[ Back to top ]