フォノイコライザアンプ

【課題】アナログレコードの再生時の音質の劣化を防止することができるフォノイコライザアンプを提供する。

【解決手段】シングルRIAAタイプのフォノイコライザアンプ100において、増幅回路1は、レコードプレーヤのカートリッジ5から入力された入力信号61を増幅して増幅信号62を出力する。バッファ回路3は、増幅回路1の出力インピーダンスを変換し、増幅信号62を出力信号63として出力する。イコライザ回路2は、増幅回路1とバッファ回路3との間に接続され、増幅信号62の交流成分62aにRIAA特性を付与して、交流成分62aを増幅回路1に負帰還させる。DCサーボ回路4は、バッファ回路3の出力側に接続され、出力信号63の直流成分63dを増幅回路1に負帰還させる。

【解決手段】シングルRIAAタイプのフォノイコライザアンプ100において、増幅回路1は、レコードプレーヤのカートリッジ5から入力された入力信号61を増幅して増幅信号62を出力する。バッファ回路3は、増幅回路1の出力インピーダンスを変換し、増幅信号62を出力信号63として出力する。イコライザ回路2は、増幅回路1とバッファ回路3との間に接続され、増幅信号62の交流成分62aにRIAA特性を付与して、交流成分62aを増幅回路1に負帰還させる。DCサーボ回路4は、バッファ回路3の出力側に接続され、出力信号63の直流成分63dを増幅回路1に負帰還させる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、フォノイコライザアンプに関し、さらに詳しくは、RIAA(Record Industry Association of America)規格に基づいて録音されたアナログレコードの再生に用いるフォノイコライザアンプに関する。

【背景技術】

【0002】

アナログレコードには、RIAAによって定められた周波数特性に基づいた音溝が形成されている。レコードプレーヤに装着されたカートリッジは、アナログレコードに形成された音溝の振幅を電気信号に変換する。この電気信号は、フォノイコライザアンプ、プリアンプ、及びメインアンプなどを介して、音声信号として出力される。

【0003】

フォノイコライザアンプは、音声信号をアナログレコードに記録するときの周波数特性と逆の周波数特性(RIAA特性)を電気信号に付与するとともに、電気信号を増幅する装置である。特許文献1には、デュアルRIAAタイプと呼ばれるフォノイコライザアンプが開示されている。非特許文献1には、デュアルRIAAタイプの他に、シングルRIAAタイプのフォノイコライザアンプが開示されている。デュアルRIAAタイプは、RIAA特性を有するイコライザ回路を二つ備えている。シングルRIAAタイプは、イコライザ回路を一つ備えている。

【0004】

また、カートリッジには、MM(Moving Magnet)型及びMC(Moving Coil)型がある。カートリッジから出力される電気信号のレベルは、MM型及びMC型でそれぞれ異なる。このため、フォノイコライザアンプのゲインを、レコードプレーヤに装着されるカートリッジの型に応じて変更したり、MC型のカートリッジを使用する際に、フォノイコライザアンプの前段にヘッドアンプを接続する必要がある。

【0005】

非特許文献1には、さらに、MC型及びMM型の両者のカートリッジに対応したフォノイコライザアンプが開示されている。

【0006】

非特許文献1に係るフォノイコライザアンプにおいて、プッシュプル増幅回路が、カートリッジから入力された電気信号を、カートリッジの型に応じたゲインで増幅する。増幅された電気信号の交流成分は、イコライザ回路を介して負帰還される。直流成分は、DCサーボ回路などを介して負帰還され、プッシュプル増幅回路のオフセットを調整する。

【0007】

しかしながら、非特許文献1に係るフォノイコライザアンプでは、DCサーボ回路がイコライザ回路に干渉するため、負帰還される交流成分に正確なRIAA特性を付与することができなかった。この結果、非特許文献1に係るフォノイコライザアンプは、アナログレコードから再生される音声信号の音質に悪影響を及ぼしていた。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭59−48817号公報

【非特許文献】

【0009】

【非特許文献1】「MJ無線と実験 2008年6月号」、88〜91ページ、株式会社誠文堂新光社、2008年6月1日発行

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の目的は、アナログレコードの再生時の音質の劣化を防止することができるフォノイコライザアンプを提供することである。

【課題を解決するための手段及び発明の効果】

【0011】

本発明によるフォノイコライザアンプは、第1の増幅回路と、バッファ回路と、交流成分帰還回路と、直流成分帰還回路とを備える。第1の増幅回路は、入力信号を増幅して増幅信号を出力する。バッファ回路は、第1の増幅回路の出力に接続され、増幅信号を出力信号として出力する。交流成分帰還回路は、第1の増幅回路とバッファ回路との間に接続され、増幅信号の交流成分に所定の周波数特性を付与して第1の増幅回路に負帰還させる。直流成分帰還回路は、バッファ回路の出力に接続され、出力信号の直流成分を第1の増幅回路に負帰還させる。

【0012】

この場合、交流成分帰還回路と直流成分帰還回路との間にバッファ回路が接続されるため、交流成分帰還回路が有する周波数特性に対して直流成分帰還回路が干渉することがない。そのため、本発明によるフォノイコライザアンプは、アナログレコードの再生時の音質の劣化を防止することができる。

【0013】

好ましくは、直流成分帰還回路は、フィルタと、位相反転回路とを含む。フィルタは、直流成分帰還回路に入力された出力信号の位相を反転させ、かつ、出力信号の交流成分を減衰させることにより交流成分減衰信号を生成する。位相反転回路は、交流成分減衰信号の位相を反転させて出力信号の直流成分として出力する。また、フィルタは、第2の増幅回路と、帰還回路とを含む。第2の増幅回路は、出力信号を増幅する。帰還回路は、互いに並列に接続されたコンデンサ及び抵抗素子を有し、第2の増幅回路により増幅された出力信号をコンデンサ及び抵抗素子を介して第2の増幅回路に負帰還させる。

【0014】

この場合、帰還用信号に含まれる交流成分の減衰に用いるコンデンサの静電容量を、数百μF程度とすることができる。そのため、直流成分帰還回路の回路規模を縮小することができるとともに、コストの低減が可能となる。

【0015】

好ましくは、第1の増幅回路は、第1の増幅回路のゲインを、第1のゲイン及び第1のゲインよりも大きい第2のゲインのいずれかに設定するゲイン設定回路を含む。

【0016】

この場合、カートリッジの型に応じて、本発明によるフォノイコライザアンプのゲインを設定することができる。これにより、MC型のカートリッジを利用する際に、本発明によるフォノイコライザアンプの前段にヘッドアンプを接続することなく、アナログレコードを再生することができる。

【図面の簡単な説明】

【0017】

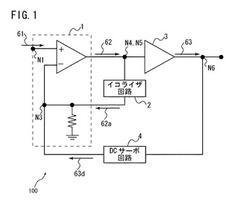

【図1】本発明の実施の形態によるフォノイコライザアンプの構成を示す機能ブロック図である。

【図2】本発明の第1の実施の形態によるフォノイコライザアンプの構成を示す回路図である。

【図3】図1中のDCサーボ回路の周波数特性を示す図である。

【図4】本発明の第2の実施の形態によるフォノイコライザアンプの構成を示す回路図である。

【発明を実施するための形態】

【0018】

以下、図面を参照し、本発明の実施の形態を詳しく説明する。図中同一又は相当部分には同一符号を付してその説明は繰り返さない。

【0019】

(第1の実施の形態)

図1は、本発明の第1の実施の形態によるフォノイコライザアンプ100の構成を示す機能ブロック図である。図1を参照して、フォノイコライザアンプ100は、増幅回路1と、イコライザ回路2と、バッファ回路3と、DCサーボ回路4とを備える。

【0020】

増幅回路1は、レコードプレーヤに装着されたカートリッジ5(図2参照)から出力される信号(以下、「入力信号」という。)61を増幅して増幅信号62を出力する。イコライザ回路2は、増幅回路1とバッファ回路3との間に接続される。イコライザ回路2は、増幅信号62の交流成分62aにRIAA特性を付与して増幅回路1に負帰還させる。バッファ回路3は、増幅回路1の出力に接続される。バッファ回路3は、増幅回路1の出力インピーダンスを変換し、増幅信号62を出力信号63として出力する。DCサーボ回路4は、バッファ回路3の出力に接続される。DCサーボ回路4は、出力信号63の直流成分63dを増幅回路1に負帰還させる。

【0021】

イコライザ回路2は、本発明において交流成分帰還回路として機能する。DCサーボ回路4は、本発明において直流成分帰還回路として機能する。

【0022】

図2は、図1に示したイコライザアンプ100の詳細な構成を示す回路図である。図2を参照して、増幅回路1は、インピーダンス整合回路11と、B級プッシュプル増幅回路(以下、「プッシュプル回路」という。)12と、ゲイン設定回路13とを備える。なお、図2において、ノードN1は、増幅回路1の非反転入力端子に対応する。ノードN3は、増幅回路1の反転入力端子に対応する。ノードN4,N5は、増幅回路1の出力端子に対応する。

【0023】

インピーダンス整合回路11は、カートリッジ5の出力インピーダンスと増幅回路1の入力インピーダンスとをマッチングする回路であり、スイッチSW111と、抵抗素子R111〜R113とを備える。

【0024】

抵抗素子R111の一端はノードN1に接続される。抵抗素子R111の他端はノードN2とスイッチSW111の一端と抵抗素子R113の一端とに接続される。スイッチSW111の他端は抵抗素子R112を介して接地される。抵抗素子R113の他端は接地される。

【0025】

プッシュプル回路12は、ゲイン設定回路13が設定したゲインで、入力信号61を増幅する。ゲイン設定回路13を除けば、プッシュプル回路12の構成は周知であるため、その説明を省略する。

【0026】

ゲイン設定回路13は、プッシュプル回路12のゲインをカートリッジ5の型に応じて設定する回路であり、スイッチSW131と、抵抗素子R131、R132とを備える。

【0027】

抵抗素子R131の一端及びスイッチSW131がノードN3に接続される。抵抗素子R131の他端は接地される。スイッチSW131の他端は抵抗素子R132を介して接地される。

【0028】

イコライザ回路2は、複数の抵抗素子及びコンデンサで構成されており、周波数特性としてRIAA特性を有する。イコライザ回路2の一端は抵抗素子R11を介してノードN3に接続される。イコライザ回路2の他端は、ノードN4に接続されるとともに、コンデンサC11を介してノードN5に接続される。

【0029】

バッファ回路3は、いわゆるエミッタフォロワ回路である。

【0030】

DCサーボ回路4は、OPアンプ41と、抵抗素子R41〜R45と、コンデンサC41,C42とを備える。

【0031】

抵抗素子R41の一端は、バッファ回路4の出力端子に対応するノードN6に接続される。抵抗素子R41の他端は、OPアンプ41の非反転入力端子とコンデンサC41の一端とに接続される。コンデンサC41の他端は接地される。抵抗素子R42の一端は、OPアンプ41の反転入力端子に接続される。抵抗素子R42の他端は接地される。抵抗素子R43の一端はOPアンプ41の反転入力端子に接続される。抵抗素子R43の他端はOPアンプ41の出力端子に接続される。抵抗素子R44の一端はOPアンプ41の出力端子に接続される。抵抗素子R44の他端はコンデンサC42の一端と抵抗素子R45の一端とに接続される。コンデンサC42の他端は接地される。抵抗素子R45の他端はノードN3に接続される。

【0032】

次に、フォノイコライザアンプ100の動作について説明する。

【0033】

インピーダンス整合回路11においては、ノードN1に接続されるカートリッジ5の型に応じてスイッチSW111はオープン又はクローズに切り替えられる。カートリッジ5がMM型である場合、スイッチSW111は、図2に示すようにオープンの状態となる。一方、カートリッジ5がMC型である場合、スイッチSW111はクローズの状態となる。このように、インピーダンス整合回路11は、スイッチSW111の開閉状態をカートリッジ5の型に応じて切り替えることにより、フォノイコライザアンプ100の入力インピーダンスをカートリッジ5の出力インピーダンスに整合させる。

【0034】

プッシュプル回路12は、ゲイン設定回路13で設定されたゲインに基づいて入力された電気信号61を増幅し、増幅信号62を出力する。ゲイン設定回路13は、カートリッジ6のタイプに応じてスイッチSW131の開閉状態を切り替えることによって、プッシュプル回路12のゲインを設定する。カートリッジ6がMM型の場合、スイッチSW131は、図2に示すようにオープンの状態となる。一方、カートリッジ6がMC型の場合、スイッチSW131は、クローズの状態となる。スイッチSW131がクローズされているときのプッシュプル回路12のゲインは、スイッチSW131がオープンされているときのゲインよりも、約20dB大きくなる。

【0035】

増幅信号62は、ノードN4,N5からイコライザ回路2及びバッファ回路3に入力される。

【0036】

イコライザ回路2は、プッシュプル回路12のオープンループゲイン特性を、RIAA特性に対応させる。また、イコライザ回路2は、ノードN4,N5から入力される増幅信号62のうち交流成分62aにRIAA特性を付与する。RIAA特性が付与された交流成分62aは、抵抗素子R11を介してノードN3に入力されることにより、プッシュプル回路12に負帰還される。これにより、プッシュプル回路12のクローズドループ特性をRIAA特性に対応させることができる。

【0037】

バッファ回路3は、プッシュプル回路12の出力インピーダンスをそれよりも低いインピーダンスに変換し、増幅信号62を出力信号63として出力する。このとき、増幅信号62は増幅されない。出力信号63は、DCサーボ回路4に帰還用信号として入力されるとともに、バッファ回路3の後段に接続されるRC回路64に入力される。

【0038】

DCサーボ回路4において、抵抗素子R41は、DCサーボ回路4に入力された出力信号63を電流から電圧に変換する。コンデンサC41は、出力信号63に含まれる交流成分を通過させることにより、出力信号63の交流成分を減衰させる。この結果、OPアンプ41の非反転入力端子には交流成分減衰信号63dが入力される。

【0039】

OPアンプ41と、抵抗素子R42,R43とは、非反転増幅回路40aを形成する。非反転増幅回路40aは、交流成分減衰信号63dを、抵抗素子R42、R43の各抵抗値により定まるゲインで増幅する。そして、交流成分減衰信号63dは,出力信号63の直流成分として、抵抗素子R44,R45、及びノードN3を介してプッシュプル回路12に負帰還される。

【0040】

図3は、DCサーボ回路4の周波数特性を示す図である。図3に示すように、DCサーボ回路4は、増幅信号63の交流成分(約1Hz以上)を減衰させていることがわかる。

【0041】

バッファ回路3の後段に接続されているRC回路64は、出力信号63に含まれる可聴周波数帯域の信号を通過させる。RC回路64から出力される信号は、プリアンプ(図示省略)及びメインアンプ(図示省略)でさらに増幅され、スピーカなどから音声信号として出力される。

【0042】

次に、DCサーボ回路4がイコライザ回路2に与える影響について説明する。

【0043】

図1及び図2に示すように、イコライザ回路2とDCサーボ回路4との間に、バッファ回路3が接続されている。これにより、イコライザ回路2のRIAA特性が、DCサーボ回路4の抵抗素子R41により変化することを防止できる。

【0044】

ここで、図2に示した回路と異なり、イコライザ回路2がバッファ回路3の出力に接続される場合を想定する。つまり、イコライザ回路2とDCサーボ回路4とが同じノードで接続される。この場合、イコライザ回路2の抵抗素子R21とDCサーボ回路4の抵抗素子R41とが並列回路を構成する。この結果、イコライザ回路2の周波数特性が本来のRIAA特性から変化する。つまり、RIAA偏差の大きい周波数特性が付与された交流成分62aがプッシュプル回路12に負帰還されるため、出力信号63の周波数特性のRIAA偏差も大きくなる。この結果、アナログレコードから再生される音声信号の品質が劣化する。

【0045】

しかし、図2に示したフォノイコライザアンプ100では、イコライザ回路2とDCサーボ回路4との間にバッファ回路3が接続されている。つまり、抵抗素子R21,R41は、並列回路を構成しない。イコライザ回路2は、抵抗素子R41の影響を受けることなく、本来のRIAA特性を付与した交流成分63dを、プッシュプル回路12に負帰還させることができる。したがって、イコライザアンプ100を用いることにより、アナログレコードを良好な音質で再生することができる。

【0046】

このように、本実施の形態によるフォノイコライザアンプ100は、バッファ回路3をイコライザ回路2とDCサーボ回路4との間に接続することによって、RIAA偏差の少ない信号を出力することができる。

【0047】

(第2の実施の形態)

図4を参照して、本発明の第2の実施の形態によるフォノイコライザアンプ100は、第1の実施の形態と異なり、DCサーボ回路4に代えてDCサーボ回路7を備える。

【0048】

DCサーボ回路7は、OPアンプ71,72と、抵抗素子R71〜R75と、コンデンサC71,C72とを備える。

【0049】

抵抗素子R71の一端はノードN6に接続される。抵抗素子R71の他端は、コンデンサC71の一端と抵抗素子R72の一端とOPアンプ71の反転入力端子とに接続される。コンデンサC71の他端と抵抗素子R72の他端とは、OPアンプ71の出力端子と抵抗素子R73の一端とに接続される。つまり、コンデンサC71及び抵抗素子R72は互いに並列に接続される。抵抗素子R73の他端は抵抗素子R74の一端とOPアンプ72の反転入力端子とに接続される。抵抗素子R74の他端はOPアンプ72の出力端子と抵抗素子R75の一端とに接続される。抵抗素子R75の他端はコンデンサC72を介して接地されるとともに、ノードN3に接続される。OPアンプ71,72の非反転入力端子は接地される。

【0050】

OPアンプ71とコンデンサC71と抵抗素子R72とはフィルタ70aを構成する。フィルタ70aは、DCサーボ回路7に入力された出力信号63の位相を反転させ、かつ、出力信号63の交流成分を減衰させることにより交流成分減衰信号63dを生成する。OPアンプ72と抵抗素子R73,R74とは位相反転回路70bを構成する。位相反転回路70bは、交流成分減衰信号63dの位相を反転させて出力信号63の直流成分として出力する。OPアンプ71は、出力信号63を増幅する増幅回路として機能する。コンデンサC71と抵抗素子R72とは帰還回路70cを構成する。帰還回路70cは、OPアンプ71により増幅された出力信号63をコンデンサC71及び抵抗素子R72を介してOPアンプ71に負帰還させる。

【0051】

次に、DCサーボ回路7の動作について説明する。

【0052】

抵抗素子R71は、出力信号63を電流から電圧に変換する。

【0053】

フィルタ70aにおいて、OPアンプ71は、出力信号63を、抵抗素子R73,R74の各抵抗値により定まるゲインで反転増幅する。増幅された出力信号63は帰還回路70cを介してOPアンプ71に負帰還される。この結果、フィルタ70aでは、出力信号63の交流成分が減衰された交流成分減衰信号63dが生成される。出力信号63と、フィルタ70aから出力される交流成分減衰信号63dとの位相差は、180度である。

【0054】

フィルタ70aは、DCサーボ回路4と同様に、図3に示す周波数特性を有する。しかし、フィルタ70aを構成するコンデンサC71の静電容量は470μFであり、DCサーボ回路4が有するコンデンサC41の静電容量(22000μF)の数十分の一以下である。このため、DCサーボ回路7の回路規模を、DCサーボ回路4よりも小さくすることができるとともに、コスト削減が可能となる。

【0055】

フィルタ70aから出力された交流成分減衰信号63dは、位相反転回路70bにおいて、抵抗素子R73,R74の各抵抗値により定まるゲインで反転増幅される。この結果、位相反転回路70bから出力される交流成分減衰信号63dは、出力信号63と同相となる。そして、交流成分減衰信号63dは、出力信号63の直流成分として、プッシュプル回路12に負帰還される。

【0056】

このように、本実施の形態では、OPアンプ71を用いたフィルタ回路70aと位相反転回路70bでDCサーボ回路7を構成することにより、回路規模を小さくすることができる。さらに、使用するコンデンサの静電容量が500μF程度であるため、DCサーボ回路4と比較して、DCサーボ回路7のコストを削減することができる。

【0057】

以上、本発明の実施の形態を説明したが、上述した実施の形態は本発明を実施するための例示に過ぎない。よって、本発明は上述した実施の形態に限定されることなく、その趣旨を逸脱しない範囲内で上述した実施の形態を適宜変形して実施することが可能である。

【符号の説明】

【0058】

1 増幅回路

2 イコライザ回路

3 バッファ回路

4,7 DCサーボ回路

12 プッシュプル回路

13 ゲイン設定回路

41,71,72 OPアンプ

70a フィルタ

70b 位相反転回路

70c 帰還回路

C41,C42,C61,C62 コンデンサ

R31〜R36,R61〜R66,R111〜R113,R131〜R133 抵抗素子

100 フォノイコライザアンプ

【技術分野】

【0001】

本発明は、フォノイコライザアンプに関し、さらに詳しくは、RIAA(Record Industry Association of America)規格に基づいて録音されたアナログレコードの再生に用いるフォノイコライザアンプに関する。

【背景技術】

【0002】

アナログレコードには、RIAAによって定められた周波数特性に基づいた音溝が形成されている。レコードプレーヤに装着されたカートリッジは、アナログレコードに形成された音溝の振幅を電気信号に変換する。この電気信号は、フォノイコライザアンプ、プリアンプ、及びメインアンプなどを介して、音声信号として出力される。

【0003】

フォノイコライザアンプは、音声信号をアナログレコードに記録するときの周波数特性と逆の周波数特性(RIAA特性)を電気信号に付与するとともに、電気信号を増幅する装置である。特許文献1には、デュアルRIAAタイプと呼ばれるフォノイコライザアンプが開示されている。非特許文献1には、デュアルRIAAタイプの他に、シングルRIAAタイプのフォノイコライザアンプが開示されている。デュアルRIAAタイプは、RIAA特性を有するイコライザ回路を二つ備えている。シングルRIAAタイプは、イコライザ回路を一つ備えている。

【0004】

また、カートリッジには、MM(Moving Magnet)型及びMC(Moving Coil)型がある。カートリッジから出力される電気信号のレベルは、MM型及びMC型でそれぞれ異なる。このため、フォノイコライザアンプのゲインを、レコードプレーヤに装着されるカートリッジの型に応じて変更したり、MC型のカートリッジを使用する際に、フォノイコライザアンプの前段にヘッドアンプを接続する必要がある。

【0005】

非特許文献1には、さらに、MC型及びMM型の両者のカートリッジに対応したフォノイコライザアンプが開示されている。

【0006】

非特許文献1に係るフォノイコライザアンプにおいて、プッシュプル増幅回路が、カートリッジから入力された電気信号を、カートリッジの型に応じたゲインで増幅する。増幅された電気信号の交流成分は、イコライザ回路を介して負帰還される。直流成分は、DCサーボ回路などを介して負帰還され、プッシュプル増幅回路のオフセットを調整する。

【0007】

しかしながら、非特許文献1に係るフォノイコライザアンプでは、DCサーボ回路がイコライザ回路に干渉するため、負帰還される交流成分に正確なRIAA特性を付与することができなかった。この結果、非特許文献1に係るフォノイコライザアンプは、アナログレコードから再生される音声信号の音質に悪影響を及ぼしていた。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開昭59−48817号公報

【非特許文献】

【0009】

【非特許文献1】「MJ無線と実験 2008年6月号」、88〜91ページ、株式会社誠文堂新光社、2008年6月1日発行

【発明の概要】

【発明が解決しようとする課題】

【0010】

本発明の目的は、アナログレコードの再生時の音質の劣化を防止することができるフォノイコライザアンプを提供することである。

【課題を解決するための手段及び発明の効果】

【0011】

本発明によるフォノイコライザアンプは、第1の増幅回路と、バッファ回路と、交流成分帰還回路と、直流成分帰還回路とを備える。第1の増幅回路は、入力信号を増幅して増幅信号を出力する。バッファ回路は、第1の増幅回路の出力に接続され、増幅信号を出力信号として出力する。交流成分帰還回路は、第1の増幅回路とバッファ回路との間に接続され、増幅信号の交流成分に所定の周波数特性を付与して第1の増幅回路に負帰還させる。直流成分帰還回路は、バッファ回路の出力に接続され、出力信号の直流成分を第1の増幅回路に負帰還させる。

【0012】

この場合、交流成分帰還回路と直流成分帰還回路との間にバッファ回路が接続されるため、交流成分帰還回路が有する周波数特性に対して直流成分帰還回路が干渉することがない。そのため、本発明によるフォノイコライザアンプは、アナログレコードの再生時の音質の劣化を防止することができる。

【0013】

好ましくは、直流成分帰還回路は、フィルタと、位相反転回路とを含む。フィルタは、直流成分帰還回路に入力された出力信号の位相を反転させ、かつ、出力信号の交流成分を減衰させることにより交流成分減衰信号を生成する。位相反転回路は、交流成分減衰信号の位相を反転させて出力信号の直流成分として出力する。また、フィルタは、第2の増幅回路と、帰還回路とを含む。第2の増幅回路は、出力信号を増幅する。帰還回路は、互いに並列に接続されたコンデンサ及び抵抗素子を有し、第2の増幅回路により増幅された出力信号をコンデンサ及び抵抗素子を介して第2の増幅回路に負帰還させる。

【0014】

この場合、帰還用信号に含まれる交流成分の減衰に用いるコンデンサの静電容量を、数百μF程度とすることができる。そのため、直流成分帰還回路の回路規模を縮小することができるとともに、コストの低減が可能となる。

【0015】

好ましくは、第1の増幅回路は、第1の増幅回路のゲインを、第1のゲイン及び第1のゲインよりも大きい第2のゲインのいずれかに設定するゲイン設定回路を含む。

【0016】

この場合、カートリッジの型に応じて、本発明によるフォノイコライザアンプのゲインを設定することができる。これにより、MC型のカートリッジを利用する際に、本発明によるフォノイコライザアンプの前段にヘッドアンプを接続することなく、アナログレコードを再生することができる。

【図面の簡単な説明】

【0017】

【図1】本発明の実施の形態によるフォノイコライザアンプの構成を示す機能ブロック図である。

【図2】本発明の第1の実施の形態によるフォノイコライザアンプの構成を示す回路図である。

【図3】図1中のDCサーボ回路の周波数特性を示す図である。

【図4】本発明の第2の実施の形態によるフォノイコライザアンプの構成を示す回路図である。

【発明を実施するための形態】

【0018】

以下、図面を参照し、本発明の実施の形態を詳しく説明する。図中同一又は相当部分には同一符号を付してその説明は繰り返さない。

【0019】

(第1の実施の形態)

図1は、本発明の第1の実施の形態によるフォノイコライザアンプ100の構成を示す機能ブロック図である。図1を参照して、フォノイコライザアンプ100は、増幅回路1と、イコライザ回路2と、バッファ回路3と、DCサーボ回路4とを備える。

【0020】

増幅回路1は、レコードプレーヤに装着されたカートリッジ5(図2参照)から出力される信号(以下、「入力信号」という。)61を増幅して増幅信号62を出力する。イコライザ回路2は、増幅回路1とバッファ回路3との間に接続される。イコライザ回路2は、増幅信号62の交流成分62aにRIAA特性を付与して増幅回路1に負帰還させる。バッファ回路3は、増幅回路1の出力に接続される。バッファ回路3は、増幅回路1の出力インピーダンスを変換し、増幅信号62を出力信号63として出力する。DCサーボ回路4は、バッファ回路3の出力に接続される。DCサーボ回路4は、出力信号63の直流成分63dを増幅回路1に負帰還させる。

【0021】

イコライザ回路2は、本発明において交流成分帰還回路として機能する。DCサーボ回路4は、本発明において直流成分帰還回路として機能する。

【0022】

図2は、図1に示したイコライザアンプ100の詳細な構成を示す回路図である。図2を参照して、増幅回路1は、インピーダンス整合回路11と、B級プッシュプル増幅回路(以下、「プッシュプル回路」という。)12と、ゲイン設定回路13とを備える。なお、図2において、ノードN1は、増幅回路1の非反転入力端子に対応する。ノードN3は、増幅回路1の反転入力端子に対応する。ノードN4,N5は、増幅回路1の出力端子に対応する。

【0023】

インピーダンス整合回路11は、カートリッジ5の出力インピーダンスと増幅回路1の入力インピーダンスとをマッチングする回路であり、スイッチSW111と、抵抗素子R111〜R113とを備える。

【0024】

抵抗素子R111の一端はノードN1に接続される。抵抗素子R111の他端はノードN2とスイッチSW111の一端と抵抗素子R113の一端とに接続される。スイッチSW111の他端は抵抗素子R112を介して接地される。抵抗素子R113の他端は接地される。

【0025】

プッシュプル回路12は、ゲイン設定回路13が設定したゲインで、入力信号61を増幅する。ゲイン設定回路13を除けば、プッシュプル回路12の構成は周知であるため、その説明を省略する。

【0026】

ゲイン設定回路13は、プッシュプル回路12のゲインをカートリッジ5の型に応じて設定する回路であり、スイッチSW131と、抵抗素子R131、R132とを備える。

【0027】

抵抗素子R131の一端及びスイッチSW131がノードN3に接続される。抵抗素子R131の他端は接地される。スイッチSW131の他端は抵抗素子R132を介して接地される。

【0028】

イコライザ回路2は、複数の抵抗素子及びコンデンサで構成されており、周波数特性としてRIAA特性を有する。イコライザ回路2の一端は抵抗素子R11を介してノードN3に接続される。イコライザ回路2の他端は、ノードN4に接続されるとともに、コンデンサC11を介してノードN5に接続される。

【0029】

バッファ回路3は、いわゆるエミッタフォロワ回路である。

【0030】

DCサーボ回路4は、OPアンプ41と、抵抗素子R41〜R45と、コンデンサC41,C42とを備える。

【0031】

抵抗素子R41の一端は、バッファ回路4の出力端子に対応するノードN6に接続される。抵抗素子R41の他端は、OPアンプ41の非反転入力端子とコンデンサC41の一端とに接続される。コンデンサC41の他端は接地される。抵抗素子R42の一端は、OPアンプ41の反転入力端子に接続される。抵抗素子R42の他端は接地される。抵抗素子R43の一端はOPアンプ41の反転入力端子に接続される。抵抗素子R43の他端はOPアンプ41の出力端子に接続される。抵抗素子R44の一端はOPアンプ41の出力端子に接続される。抵抗素子R44の他端はコンデンサC42の一端と抵抗素子R45の一端とに接続される。コンデンサC42の他端は接地される。抵抗素子R45の他端はノードN3に接続される。

【0032】

次に、フォノイコライザアンプ100の動作について説明する。

【0033】

インピーダンス整合回路11においては、ノードN1に接続されるカートリッジ5の型に応じてスイッチSW111はオープン又はクローズに切り替えられる。カートリッジ5がMM型である場合、スイッチSW111は、図2に示すようにオープンの状態となる。一方、カートリッジ5がMC型である場合、スイッチSW111はクローズの状態となる。このように、インピーダンス整合回路11は、スイッチSW111の開閉状態をカートリッジ5の型に応じて切り替えることにより、フォノイコライザアンプ100の入力インピーダンスをカートリッジ5の出力インピーダンスに整合させる。

【0034】

プッシュプル回路12は、ゲイン設定回路13で設定されたゲインに基づいて入力された電気信号61を増幅し、増幅信号62を出力する。ゲイン設定回路13は、カートリッジ6のタイプに応じてスイッチSW131の開閉状態を切り替えることによって、プッシュプル回路12のゲインを設定する。カートリッジ6がMM型の場合、スイッチSW131は、図2に示すようにオープンの状態となる。一方、カートリッジ6がMC型の場合、スイッチSW131は、クローズの状態となる。スイッチSW131がクローズされているときのプッシュプル回路12のゲインは、スイッチSW131がオープンされているときのゲインよりも、約20dB大きくなる。

【0035】

増幅信号62は、ノードN4,N5からイコライザ回路2及びバッファ回路3に入力される。

【0036】

イコライザ回路2は、プッシュプル回路12のオープンループゲイン特性を、RIAA特性に対応させる。また、イコライザ回路2は、ノードN4,N5から入力される増幅信号62のうち交流成分62aにRIAA特性を付与する。RIAA特性が付与された交流成分62aは、抵抗素子R11を介してノードN3に入力されることにより、プッシュプル回路12に負帰還される。これにより、プッシュプル回路12のクローズドループ特性をRIAA特性に対応させることができる。

【0037】

バッファ回路3は、プッシュプル回路12の出力インピーダンスをそれよりも低いインピーダンスに変換し、増幅信号62を出力信号63として出力する。このとき、増幅信号62は増幅されない。出力信号63は、DCサーボ回路4に帰還用信号として入力されるとともに、バッファ回路3の後段に接続されるRC回路64に入力される。

【0038】

DCサーボ回路4において、抵抗素子R41は、DCサーボ回路4に入力された出力信号63を電流から電圧に変換する。コンデンサC41は、出力信号63に含まれる交流成分を通過させることにより、出力信号63の交流成分を減衰させる。この結果、OPアンプ41の非反転入力端子には交流成分減衰信号63dが入力される。

【0039】

OPアンプ41と、抵抗素子R42,R43とは、非反転増幅回路40aを形成する。非反転増幅回路40aは、交流成分減衰信号63dを、抵抗素子R42、R43の各抵抗値により定まるゲインで増幅する。そして、交流成分減衰信号63dは,出力信号63の直流成分として、抵抗素子R44,R45、及びノードN3を介してプッシュプル回路12に負帰還される。

【0040】

図3は、DCサーボ回路4の周波数特性を示す図である。図3に示すように、DCサーボ回路4は、増幅信号63の交流成分(約1Hz以上)を減衰させていることがわかる。

【0041】

バッファ回路3の後段に接続されているRC回路64は、出力信号63に含まれる可聴周波数帯域の信号を通過させる。RC回路64から出力される信号は、プリアンプ(図示省略)及びメインアンプ(図示省略)でさらに増幅され、スピーカなどから音声信号として出力される。

【0042】

次に、DCサーボ回路4がイコライザ回路2に与える影響について説明する。

【0043】

図1及び図2に示すように、イコライザ回路2とDCサーボ回路4との間に、バッファ回路3が接続されている。これにより、イコライザ回路2のRIAA特性が、DCサーボ回路4の抵抗素子R41により変化することを防止できる。

【0044】

ここで、図2に示した回路と異なり、イコライザ回路2がバッファ回路3の出力に接続される場合を想定する。つまり、イコライザ回路2とDCサーボ回路4とが同じノードで接続される。この場合、イコライザ回路2の抵抗素子R21とDCサーボ回路4の抵抗素子R41とが並列回路を構成する。この結果、イコライザ回路2の周波数特性が本来のRIAA特性から変化する。つまり、RIAA偏差の大きい周波数特性が付与された交流成分62aがプッシュプル回路12に負帰還されるため、出力信号63の周波数特性のRIAA偏差も大きくなる。この結果、アナログレコードから再生される音声信号の品質が劣化する。

【0045】

しかし、図2に示したフォノイコライザアンプ100では、イコライザ回路2とDCサーボ回路4との間にバッファ回路3が接続されている。つまり、抵抗素子R21,R41は、並列回路を構成しない。イコライザ回路2は、抵抗素子R41の影響を受けることなく、本来のRIAA特性を付与した交流成分63dを、プッシュプル回路12に負帰還させることができる。したがって、イコライザアンプ100を用いることにより、アナログレコードを良好な音質で再生することができる。

【0046】

このように、本実施の形態によるフォノイコライザアンプ100は、バッファ回路3をイコライザ回路2とDCサーボ回路4との間に接続することによって、RIAA偏差の少ない信号を出力することができる。

【0047】

(第2の実施の形態)

図4を参照して、本発明の第2の実施の形態によるフォノイコライザアンプ100は、第1の実施の形態と異なり、DCサーボ回路4に代えてDCサーボ回路7を備える。

【0048】

DCサーボ回路7は、OPアンプ71,72と、抵抗素子R71〜R75と、コンデンサC71,C72とを備える。

【0049】

抵抗素子R71の一端はノードN6に接続される。抵抗素子R71の他端は、コンデンサC71の一端と抵抗素子R72の一端とOPアンプ71の反転入力端子とに接続される。コンデンサC71の他端と抵抗素子R72の他端とは、OPアンプ71の出力端子と抵抗素子R73の一端とに接続される。つまり、コンデンサC71及び抵抗素子R72は互いに並列に接続される。抵抗素子R73の他端は抵抗素子R74の一端とOPアンプ72の反転入力端子とに接続される。抵抗素子R74の他端はOPアンプ72の出力端子と抵抗素子R75の一端とに接続される。抵抗素子R75の他端はコンデンサC72を介して接地されるとともに、ノードN3に接続される。OPアンプ71,72の非反転入力端子は接地される。

【0050】

OPアンプ71とコンデンサC71と抵抗素子R72とはフィルタ70aを構成する。フィルタ70aは、DCサーボ回路7に入力された出力信号63の位相を反転させ、かつ、出力信号63の交流成分を減衰させることにより交流成分減衰信号63dを生成する。OPアンプ72と抵抗素子R73,R74とは位相反転回路70bを構成する。位相反転回路70bは、交流成分減衰信号63dの位相を反転させて出力信号63の直流成分として出力する。OPアンプ71は、出力信号63を増幅する増幅回路として機能する。コンデンサC71と抵抗素子R72とは帰還回路70cを構成する。帰還回路70cは、OPアンプ71により増幅された出力信号63をコンデンサC71及び抵抗素子R72を介してOPアンプ71に負帰還させる。

【0051】

次に、DCサーボ回路7の動作について説明する。

【0052】

抵抗素子R71は、出力信号63を電流から電圧に変換する。

【0053】

フィルタ70aにおいて、OPアンプ71は、出力信号63を、抵抗素子R73,R74の各抵抗値により定まるゲインで反転増幅する。増幅された出力信号63は帰還回路70cを介してOPアンプ71に負帰還される。この結果、フィルタ70aでは、出力信号63の交流成分が減衰された交流成分減衰信号63dが生成される。出力信号63と、フィルタ70aから出力される交流成分減衰信号63dとの位相差は、180度である。

【0054】

フィルタ70aは、DCサーボ回路4と同様に、図3に示す周波数特性を有する。しかし、フィルタ70aを構成するコンデンサC71の静電容量は470μFであり、DCサーボ回路4が有するコンデンサC41の静電容量(22000μF)の数十分の一以下である。このため、DCサーボ回路7の回路規模を、DCサーボ回路4よりも小さくすることができるとともに、コスト削減が可能となる。

【0055】

フィルタ70aから出力された交流成分減衰信号63dは、位相反転回路70bにおいて、抵抗素子R73,R74の各抵抗値により定まるゲインで反転増幅される。この結果、位相反転回路70bから出力される交流成分減衰信号63dは、出力信号63と同相となる。そして、交流成分減衰信号63dは、出力信号63の直流成分として、プッシュプル回路12に負帰還される。

【0056】

このように、本実施の形態では、OPアンプ71を用いたフィルタ回路70aと位相反転回路70bでDCサーボ回路7を構成することにより、回路規模を小さくすることができる。さらに、使用するコンデンサの静電容量が500μF程度であるため、DCサーボ回路4と比較して、DCサーボ回路7のコストを削減することができる。

【0057】

以上、本発明の実施の形態を説明したが、上述した実施の形態は本発明を実施するための例示に過ぎない。よって、本発明は上述した実施の形態に限定されることなく、その趣旨を逸脱しない範囲内で上述した実施の形態を適宜変形して実施することが可能である。

【符号の説明】

【0058】

1 増幅回路

2 イコライザ回路

3 バッファ回路

4,7 DCサーボ回路

12 プッシュプル回路

13 ゲイン設定回路

41,71,72 OPアンプ

70a フィルタ

70b 位相反転回路

70c 帰還回路

C41,C42,C61,C62 コンデンサ

R31〜R36,R61〜R66,R111〜R113,R131〜R133 抵抗素子

100 フォノイコライザアンプ

【特許請求の範囲】

【請求項1】

入力信号を増幅して増幅信号を出力する第1の増幅回路と、

前記第1の増幅回路の出力に接続され、前記増幅信号を出力信号として出力するバッファ回路と、

前記第1の増幅回路と前記バッファ回路との間に接続され、前記増幅信号の交流成分に所定の周波数特性を付与して前記第1の増幅回路に負帰還させる交流成分帰還回路と、

前記バッファ回路の出力に接続され、前記出力信号の直流成分を前記第1の増幅回路に負帰還させる直流成分帰還回路とを備えるフォノイコライザアンプ。

【請求項2】

請求項1に記載のフォノイコライザアンプであって、

前記直流成分帰還回路は、

前記直流成分帰還回路に入力された前記出力信号の位相を反転させ、かつ、前記出力信号の交流成分を減衰させることにより交流成分減衰信号を生成するフィルタと、

前記交流成分減衰信号の位相を反転させて前記出力信号の直流成分として出力する位相反転回路とを含み、

前記フィルタは、

前記出力信号を増幅する第2の増幅回路と、

互いに並列に接続されたコンデンサ及び抵抗素子を有し、前記第2の増幅回路により増幅された前記出力信号を前記コンデンサ及び前記抵抗素子を介して前記第2の増幅回路に負帰還させる帰還回路とを含むフォノイコライザアンプ。

【請求項3】

請求項1又は請求項2に記載のフォノイコライザアンプであって、

前記第1の増幅回路は、

前記第1の増幅回路のゲインを、第1のゲイン及び前記第1のゲインよりも大きい第2のゲインのいずれかに設定するゲイン設定回路を含むフォノイコライザアンプ。

【請求項1】

入力信号を増幅して増幅信号を出力する第1の増幅回路と、

前記第1の増幅回路の出力に接続され、前記増幅信号を出力信号として出力するバッファ回路と、

前記第1の増幅回路と前記バッファ回路との間に接続され、前記増幅信号の交流成分に所定の周波数特性を付与して前記第1の増幅回路に負帰還させる交流成分帰還回路と、

前記バッファ回路の出力に接続され、前記出力信号の直流成分を前記第1の増幅回路に負帰還させる直流成分帰還回路とを備えるフォノイコライザアンプ。

【請求項2】

請求項1に記載のフォノイコライザアンプであって、

前記直流成分帰還回路は、

前記直流成分帰還回路に入力された前記出力信号の位相を反転させ、かつ、前記出力信号の交流成分を減衰させることにより交流成分減衰信号を生成するフィルタと、

前記交流成分減衰信号の位相を反転させて前記出力信号の直流成分として出力する位相反転回路とを含み、

前記フィルタは、

前記出力信号を増幅する第2の増幅回路と、

互いに並列に接続されたコンデンサ及び抵抗素子を有し、前記第2の増幅回路により増幅された前記出力信号を前記コンデンサ及び前記抵抗素子を介して前記第2の増幅回路に負帰還させる帰還回路とを含むフォノイコライザアンプ。

【請求項3】

請求項1又は請求項2に記載のフォノイコライザアンプであって、

前記第1の増幅回路は、

前記第1の増幅回路のゲインを、第1のゲイン及び前記第1のゲインよりも大きい第2のゲインのいずれかに設定するゲイン設定回路を含むフォノイコライザアンプ。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2010−277619(P2010−277619A)

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願番号】特願2009−126762(P2009−126762)

【出願日】平成21年5月26日(2009.5.26)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

【公開日】平成22年12月9日(2010.12.9)

【国際特許分類】

【出願日】平成21年5月26日(2009.5.26)

【出願人】(000000273)オンキヨー株式会社 (502)

【Fターム(参考)】

[ Back to top ]