位相調整装置、系統対抗分生成装置、系統連系インバータシステム、および、位相調整方法

【課題】信号に逆相分が重畳されている場合でも、当該信号の位相を適切に調整することができる位相調整装置を提供する。

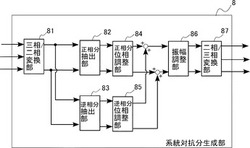

【解決手段】三相交流の各相の系統電圧に基づく3つの信号の位相を調整する位相調整装置において、検出された3つの電圧信号をα軸電圧信号およびβ軸電圧信号に変換する三相/二相変換部81と、α軸電圧信号およびβ軸電圧信号の正相分の信号を抽出する正相分抽出部82と、逆相分の信号を抽出する逆相分抽出部83と、抽出された正相分の信号の位相を調整する正相分位相調整部84と、抽出された逆相分の信号の位相を調整する逆相分位相調整部85と、位相調整後の正相分の信号と逆相分の信号とをそれぞれ加算した信号から、3つの調整後信号を生成する二相/三相変換部87とを備えた。正相分抽出部82と逆相分抽出部83は、複素係数フィルタを用いて各信号を抽出する。

【解決手段】三相交流の各相の系統電圧に基づく3つの信号の位相を調整する位相調整装置において、検出された3つの電圧信号をα軸電圧信号およびβ軸電圧信号に変換する三相/二相変換部81と、α軸電圧信号およびβ軸電圧信号の正相分の信号を抽出する正相分抽出部82と、逆相分の信号を抽出する逆相分抽出部83と、抽出された正相分の信号の位相を調整する正相分位相調整部84と、抽出された逆相分の信号の位相を調整する逆相分位相調整部85と、位相調整後の正相分の信号と逆相分の信号とをそれぞれ加算した信号から、3つの調整後信号を生成する二相/三相変換部87とを備えた。正相分抽出部82と逆相分抽出部83は、複素係数フィルタを用いて各信号を抽出する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、位相の遅延分をあらかじめ調整するための位相調整装置、当該位相調整装置を備えた系統対抗分生成装置、当該系統対抗分生成装置を備えた系統連系インバータシステム、および、位相調整方法に関する。

【背景技術】

【0002】

従来、太陽電池などによって生成される直流電力を交流電力に変換して、電力系統に供給する系統連系インバータシステムが開発されている。

【0003】

図14は、従来の一般的な系統連系インバータシステムを説明するためのブロック図である。

【0004】

系統連系インバータシステムA100は、直流電源1が生成した直流電力を交流電力に変換して三相の電力系統Bに供給するものである。なお、以下では3つの相をU相、V相およびW相とする。

【0005】

インバータ回路2は、直流電源1から入力される直流電圧をスイッチング素子(図示しない)のスイッチングにより交流電圧に変換する。フィルタ回路3は、インバータ回路2から出力される交流電圧に含まれるスイッチング周波数成分を除去する。変圧回路4は、フィルタ回路3から出力される交流電圧を電力系統Bの系統電圧に昇圧(または降圧)する。制御回路700は、電流センサ5および電圧センサ6などが検出した電流信号および電圧信号を入力され、これに基づいてPWM信号を生成してインバータ回路2に出力する。インバータ回路2は、制御回路700から入力されるPWM信号に基づいてスイッチング素子のスイッチングを行う。

【0006】

制御回路700は、電流制御部71、系統対抗分生成部800、およびPWM信号生成部72を備えている。電流制御部71は、電流センサ5より入力される電流信号I(Iu,Iv,Iw)に基づいて、電流制御のための補正値信号Xu,Xv,Xwを生成して出力する。系統対抗分生成部800は、電圧センサ6より入力される電圧信号V(Vu,Vv,Vw)に基づいて、系統指令値信号Yu,Yv,Ywを生成して出力する。系統指令値信号Yu,Yv,Ywと補正値信号Xu,Xv,Xwとをそれぞれ加算した指令値信号X’u,X’v,X’wがPWM信号生成部72に入力される。PWM信号生成部72は、入力される指令値信号X’u,X’v,X’wに基づいてPWM信号Pu,Pv,Pwを生成して、インバータ回路2に出力する。

【0007】

フィルタ回路3などのフィルタや電圧検出などの処理では、位相の遅れが生じる。この位相の遅れによる不都合を解消するための処理が、系統対抗分生成部800で行われる。例えば、位相の遅れによる電圧の変化分をあらかじめ増減させた系統指令値信号Yu,Yv,Ywを生成する方法や、位相の遅れ分だけ系統指令値信号Yu,Yv,Ywの位相をあらかじめ進めておく方法などが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平9−271176号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、電力系統Bには基本波の正相分の交流信号の他に逆相分の交流信号が含まれているので、上記の位相調整方法の場合、適切に位相の調整を行うことができない。すなわち、電圧センサ6より入力される電圧信号Vに基づく系統指令値信号Yu,Yv,Ywにも逆相分の信号が含まれている。系統指令値信号Yu,Yv,Ywの正相分の信号の位相を進める処理を行うと、正相分の信号とは相順が逆になっている逆相分の信号は、位相が遅れることになる。これにより、逆相分の信号は、フィルタなどで位相が遅れる上に更に位相が遅れるので、大幅に位相が遅れることになる。この場合、系統対抗分生成部800から出力される系統指令値信号Yu,Yv,Ywを電力系統Bの系統電圧に精度よく追従させることが困難になる。

【0010】

特に、瞬低などの系統擾乱によって電力系統Bの逆相分が増加した場合、追従の精度がより悪くなる。この結果、系統電圧と系統連系インバータシステムの出力電圧とに差が生じて過電流が流れる。過電流が流れると系統連系インバータシステムは停止され電力系統Bから切り離される。これにより、電力系統Bの系統擾乱が拡大されてしまう。

【0011】

本発明は上記した事情のもとで考え出されたものであって、信号に逆相分が重畳されている場合でも、当該信号の位相を適切に調整することができる位相調整装置を提供することをその目的としている。

【課題を解決するための手段】

【0012】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0013】

本発明の第1の側面によって提供される位相調整装置は、三相交流に基づく3つの信号の位相を調整する位相調整装置であって、前記3つの信号を第1の信号および第2の信号に変換する三相二相変換手段と、前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号とを、それぞれ抽出する正相分抽出手段と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とを、それぞれ抽出する逆相分抽出手段と、前記正相分抽出手段によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する正相分位相調整手段と、前記逆相分抽出手段によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する逆相分位相調整手段と、位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する加算手段と、前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する二相三相変換手段とを備えており、前記正相分抽出手段および前記逆相分抽出手段は、それぞれ複素係数フィルタを用いて各信号を抽出することを特徴とする。なお、「正相分の信号」とは、三相交流の基本波と周波数が同じで相順が同じ信号であり、「逆相分の信号」とは、三相交流の基本波と周波数が同じで相順が逆の信号である。

【0014】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域通過型の複素係数フィルタである。

【0015】

本発明の好ましい実施の形態においては、前記複素係数フィルタのz変換表現による伝達関数H(z)は、通過帯域の正規化中心角周波数をΩd(−π<Ωd<π)、通過帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数1】

である。

【0016】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域阻止型の複素係数フィルタである。

【0017】

本発明の好ましい実施の形態においては、前記複素係数フィルタのz変換表現による伝達関数H(z)は、阻止帯域の正規化中心角周波数をΩd(−π<Ωd<π)、阻止帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数2】

である。

【0018】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段は、複数の複素係数フィルタを多段に接続したフィルタを用いる。

【0019】

本発明の好ましい実施の形態においては、前記正相分位相調整手段は、前記第1の正相分信号をXα、前記第2の正相分信号をXβ、位相調整量をθ0とすると、位相調整後の第1の正相分信号X’αおよび第2の正相分信号X’βを、下記(1)式に示す行列式によって算出し、前記逆相分位相調整手段は、前記第1の逆相分信号をYα、前記第2の逆相分信号をYβ、位相調整量をθ0とすると、位相調整後の第1の逆相分信号Y’αおよび第2の逆相分信号Y’βを、下記(2)式に示す行列式によって算出する。

【数3】

【0020】

本発明の好ましい実施の形態においては、前記第1の調整後信号および前記第2の調整後信号の振幅を調整する振幅調整手段をさらに備えている。

【0021】

本発明の第2の側面によって提供される系統対抗分生成装置は、本発明の第1の側面によって提供される位相調整装置によって、電圧検出手段により検出された三相電力系統の各相の電圧信号の位相を調整して出力することを特徴とする。

【0022】

本発明の第3の側面によって提供される系統連系インバータシステムは、本発明の第2の側面によって提供される系統対抗分生成装置から出力される位相調整後の各相の電圧信号に基づいてPWM信号を生成して出力する制御回路と、前記制御回路から入力されるPWM信号に基づいて、直流電力を交流電力に変換するインバータ回路とを備えていることを特徴とする。

【0023】

本発明の第4の側面によって提供される位相調整方法は、三相交流に基づく3つの信号の位相を調整する位相調整方法であって、前記3つの信号を第1の信号および第2の信号に変換する第1の工程と、前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とをそれぞれ抽出する第2の工程と、前記第2の工程によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する第3の工程と、前記第2の工程によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する第4の工程と、位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する第5の工程と、前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する第6の工程とを備えており、前記第2の工程は、複素係数フィルタを用いて各信号を抽出することを特徴とする。

【発明の効果】

【0024】

本発明によれば、正相分の信号と逆相分の信号とがそれぞれ抽出され、正相分の信号は正相分位相調整手段で位相を調整され、逆相分の信号は逆相分位相調整手段で位相を調整される。そして、位相を調整された各信号から、3つの調整後信号が生成される。正相分の信号と逆相分の信号とを、それぞれに適した方法を用いて位相調整するので、三相交流に基づく信号に逆相分が重畳されている場合でも、当該信号の位相を適切に調整することができる。

【0025】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0026】

【図1】第1実施形態に係る系統連系インバータシステムを説明するためのブロック図である。

【図2】第1実施形態に係る系統対抗分生成部の内部構成を説明するためのブロック図である。

【図3】複素係数バンドパスフィルタの演算処理を示すブロック図である。

【図4】複素係数バンドパスフィルタの複素演算処理を行う回路構成を示す図である。

【図5】複素係数バンドパスフィルタの周波数特性を示す図である。

【図6】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図7】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図8】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図9】複素係数ノッチフィルタの演算処理を示すブロック図である。

【図10】複素係数ノッチフィルタの複素演算処理を行う回路構成を示す図である。

【図11】複素係数ノッチフィルタの周波数特性を示す図である。

【図12】第3実施形態に係る正相分抽出部の内部構成を説明するためのブロック図である。

【図13】第3実施形態に係る正相分抽出部の周波数特性を示す図である。

【図14】従来の一般的な系統連系インバータシステムを説明するためのブロック図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態を、本発明に係る位相調整装置を系統連系インバータシステムの系統対抗分生成部に用いた場合を例として、図面を参照して具体的に説明する。

【0028】

図1は、第1実施形態に係る系統連系インバータシステムを説明するためのブロック図である。

【0029】

同図に示すように、系統連系インバータシステムAは、直流電源1、インバータ回路2、フィルタ回路3、変圧回路4、電流センサ5、電圧センサ6、および制御回路7を備えている。

【0030】

直流電源1は、インバータ回路2に接続している。インバータ回路2、フィルタ回路3、および変圧回路4は、この順で、U相、V相、W相の出力電圧の出力ラインに直列に接続されて、三相交流の電力系統Bに接続している。電流センサ5および電圧センサ6は、変圧回路4の出力側に設置されている。制御回路7は、インバータ回路2に接続されている。系統連系インバータシステムAは、直流電源1が出力する直流電力を交流電力に変換して電力系統Bに供給する。なお、系統連系インバータシステムAの構成は、これに限られない。例えば、電流センサ5および電圧センサ6を変圧回路4の入力側に設けてもよいし、インバータ回路2の制御に必要な他のセンサを設けていてもよい。また、変圧回路4をフィルタ回路3の入力側に設けるようにしてもよいし、変圧回路4を設けない、いわゆるトランスレス方式にしてもよい。また、直流電源1とインバータ回路2との間にDC/DCコンバータ回路を設けるようにしてもよい。

【0031】

直流電源1は、直流電力を出力するものであり、例えば太陽電池を備えている。太陽電池は、太陽光エネルギーを電気エネルギーに変換することで、直流電力を生成する。直流電源1は、生成された直流電力を、インバータ回路2に出力する。なお、直流電源1は、太陽電池により直流電力を生成するものに限定されない。例えば、直流電源1は、燃料電池、蓄電池、電気二重層コンデンサやリチウムイオン電池であってもよいし、ディーゼルエンジン発電機、マイクロガスタービン発電機や風力タービン発電機などにより生成された交流電力を直流電力に変換して出力する装置であってもよい。

【0032】

インバータ回路2は、直流電源1から入力される直流電圧を交流電圧に変換して、フィルタ回路3に出力するものである。インバータ回路2は、三相インバータであり、図示しない3組6個のスイッチング素子を備えたPWM制御型インバータ回路である。インバータ回路2は、制御回路7から入力されるPWM信号に基づいて、各スイッチング素子のオンとオフとを切り替えることで、直流電源1から入力される直流電圧を交流電圧に変換する。なお、インバータ回路2はこれに限定されず、例えば、マルチレベルインバータであってもよい。

【0033】

フィルタ回路3は、インバータ回路2から入力される交流電圧から、スイッチングによる高周波成分を除去するものである。フィルタ回路3は、リアクトルとコンデンサとからなるローパスフィルタを備えている。フィルタ回路3で高周波成分を除去された交流電圧は、変圧回路4に出力される。なお、フィルタ回路3の構成はこれに限定されず、高周波成分を除去するための周知のフィルタ回路であればよい。変圧回路4は、フィルタ回路3から出力される交流電圧を系統電圧とほぼ同一のレベルに昇圧または降圧する。

【0034】

電流センサ5は、変圧回路4から出力される各相の交流電流(すなわち、系統連系インバータシステムAの出力電流)を検出するものである。検出された電流信号I(Iu,Iv,Iw)は、制御回路7に入力される。電圧センサ6は、電力系統Bの各相の系統電圧を検出するものである。検出された電圧信号V(Vu,Vv,Vw)は、制御回路7に入力される。なお、系統連系インバータシステムAが出力する出力電圧は、系統電圧とほぼ一致している。

【0035】

制御回路7は、インバータ回路2を制御するものであり、例えばマイクロコンピュータなどによって実現されている。制御回路7は、電流センサ5から入力される電流信号I、および、電圧センサ6から入力される電圧信号Vに基づいて、PWM信号を生成してインバータ回路2に出力する。制御回路7は、系統連系インバータシステムAが出力する出力電圧の波形を指令するための指令値信号を各センサから入力される検出信号に基づいて生成し、当該指令値信号に基づいて生成されるパルス信号をPWM信号として出力する。インバータ回路2は、入力されるPWM信号に基づいて各スイッチング素子のオンとオフとを切り替えることで、指令値信号に対応した波形の交流電圧を出力する。制御回路7は、指令値信号の波形を変化させて系統連系インバータシステムAの出力電圧の波形を変化させることで、出力電流を制御している。これにより、制御回路7は、各種フィードバック制御を行っている。指令値信号は、電圧センサ6が検出した電圧信号Vを基にした信号に、電流制御のための補償信号を加算することで生成される。

【0036】

図1においては、出力電流制御を行うための構成のみを記載して、その他の制御のための構成を省略している。実際には、制御回路7は、直流電圧制御(入力直流電圧が予め設定された電圧目標値となるように行うフィードバック制御)や無効電力制御(出力無効電力が予め設定された無効電力目標値となるように行うフィードバック制御)なども行っている。なお、制御回路7が行う制御の手法は、これに限られない。例えば、出力電圧制御や有効電力制御を行うようにしてもよい。

【0037】

制御回路7は、電流制御部71、PWM信号生成部72、および系統対抗分生成部8を備えている。

【0038】

電流制御部71は、電流センサ5より入力される電流信号I(Iu,Iv,Iw)に基づいて、電流制御のための補正値信号Xu,Xv,Xwを生成するものである。電流制御部71は、電流信号Iu,Iv,Iwをそれぞれの目標値に一致させるためのフィードバック制御を行うためのものであり、当該制御のための補償信号として補正値信号Xu,Xv,Xwを出力する。後述する系統対抗分生成部8が出力する系統指令値信号Yu,Yv,Ywと、電流制御部71が出力する補正値信号Xu,Xv,Xwとがそれぞれ加算されて、指令値信号X’u,X’v,X’wが算出され、PWM信号生成部72に入力される。

【0039】

PWM信号生成部72は、入力される指令値信号X’u,X’v,X’wと、所定の周波数(例えば、4kHz)の三角波信号として生成されたキャリア信号とに基づいて、三角波比較法によりPWM信号Pu,Pv,Pwを生成する。三角波比較法では、指令値信号X’u,X’v,X’wとキャリア信号とがそれぞれ比較され、例えば、指令値信号X’uがキャリア信号より大きい場合にハイレベルとなり、小さい場合にローレベルとなるパルス信号がPWM信号Puとして生成される。生成されたPWM信号Pu,Pv,Pwは、インバータ回路2に出力される。

【0040】

系統対抗分生成部8は、電圧センサ6から電圧信号V(Vu,Vv,Vw)を入力されて、系統指令値信号Yu,Yv,Ywを生成して出力する。系統指令値信号Yu,Yv,Ywは系統連系インバータシステムAが出力する出力電圧の波形を指令するための指令値信号X’u,X’v,X’wの基準となるものであり、系統指令値信号Yu,Yv,Ywが補正値信号Xu,Xv,Xwで補正されることにより指令値信号X’u,X’v,X’wが生成される。系統対抗分生成部8は、フィルタ回路3等で遅延する位相の遅れ分を進めて、系統指令値信号Yu,Yv,Ywを生成する。系統対抗分生成部8は、電圧信号Vに含まれる正相分の信号と逆相分の信号とをそれぞれ抽出し、別々に位相を進める処理を行う。正相分の信号と逆相分の信号とは、それぞれ位相を進められてから加算される。

【0041】

図2は、系統対抗分生成部8の内部構成を説明するためのブロック図である。

【0042】

同図に示すように、系統対抗分生成部8は、三相/二相変換部81、正相分抽出部82、逆相分抽出部83、正相分位相調整部84、逆相分位相調整部85、振幅調整部86、および二相/三相変換部87を備えている。

【0043】

三相/二相変換部81は、電圧センサ6より入力される3つの電圧信号Vu,Vv,Vwを、α軸電圧信号Vαおよびβ軸電圧信号Vβに変換するものである。三相/二相変換部81は、いわゆる三相/二相変換処理(αβ変換処理)を行うものであり、電圧信号Vu,Vv,Vwを互いに直交するα軸成分とβ軸成分とにそれぞれ分解して、各軸成分をまとめることでα軸電圧信号Vαおよびβ軸電圧信号Vβを生成する。

【0044】

三相/二相変換部81で行われる変換処理は、下記(3)式に示す行列式で表される。

【数4】

【0045】

正相分抽出部82および逆相分抽出部83は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、特定の周波数成分の信号を抽出するものであり、複素係数バンドパスフィルタ(帯域通過型の複素係数フィルタ)を備えている。

【0046】

当該複素係数バンドパスフィルタは、z変換表現による伝達関数H(z)が下記(4)式で表される複素係数の1次IIRフィルタで構成されている。下記(4)式において、複素係数a1におけるfdは、通過帯域の中心周波数f0をサンプリング周波数で正規化した正規化周波数である。また、Ωdは、正規化角周波数である。例えば、サンプリング周波数をfsrとすると、正規化周波数fdはf0/fsr、正規化角周波数Ωdは2π・fd=2π・(f0/fsr)となる。なお、正規化角周波数Ωdは、−π<Ωd<πである。また、rは通過帯域の帯域幅を決めるパラメータ(0<r<1)であり、jは虚数単位、exp()は自然対数の底eの指数関数である。

【0047】

【数5】

【0048】

図3は、上記(4)式の演算処理を示すブロック図である。同図に示すように、複素係数バンドパスフィルタは、上記(4)式の分母の演算処理がフィードバック回路で構成され、そのフィードバック回路の出力に分子の係数b0を乗算する回路によって構成される。

【0049】

図3に示すブロック図において、u[k](k:離散時間を表すインデックス番号)は入力データ、x[k]は状態データ、y[k]は出力データである。入力データu[k]、状態データx[k]および出力データy[k]の間には、

x[k]=r・exp(j・Ωd)・x[k-1]+u[k] …(5)

y[k]=(1−r)・x[k] …(6)

が成立する。

【0050】

複素係数バンドパスフィルタにおいては、入力データu[k]が複素データか実データ(複素データの虚数部が「0」のデータ)かに関わらず、状態データx[k]および出力データy[k]が複素データとなる。したがって、入力データu[k]、状態データx[k]および出力データy[k]をそれぞれu[k]=ur[k]+j・uj[k]、x[k]=xr[k]+j・xj[k]、y[k]=yr[k]+j・yj[k]の複素データとし、複素係数a1をa1=r・exp(j・Ωd)=ar+j・aj=r・cos(Ωd)+j・r・sin(Ωd)として、上記(5)式および(6)式に代入して、実数部と虚数部の関係式に分けると、

xr[k]=r・cos(Ωd)・xr[k-1]−r・sin(Ωd)・xj[k-1]+ur[k] …(7)

xj[k]=r・cos(Ωd)・xj[k-1]+r・sin(Ωd)・xr[k-1]+uj[k] …(8)

yr[k]=(1−r)・xr[k] …(9)

yj[k]=(1−r)・xj[k] …(10)

となる。

【0051】

図4は、上記(7)式〜(10)式に基づき複素係数バンドパスフィルタの複素演算処理を行う回路構成を示す図である。同図において、係数arおよび係数ajは、それぞれ複素係数a1=r・exp(j・Ωd)の実数部および虚数部であり、ar=r・cos(Ωd)、aj=r・sin(Ωd)である。

【0052】

同図に示すように、複素係数バンドパスフィルタは、6個の乗算器12a〜12fと、2個の加算器12g,12hと、2個の遅延回路12i,12jで構成される。遅延回路12iは、状態データの実数部xr[k-1]を生成する回路であり、遅延回路12jは、状態データの虚数部xj[k-1]を生成する回路である。乗算器12a,12bはそれぞれ上記(7)式の第1項と第2項(負の符号を含む)を演算する演算器であり、加算器12gは上記(7)式の第1項と第2項と第3項を加算する演算器である。したがって、加算器12gから上記(7)式で示す状態データの実数部xr[k]が出力される。

【0053】

一方、乗算器12c,12dはそれぞれ上記(8)式の第1項と第2項を演算する演算器であり、加算器12hは上記(8)式の第1項と第2項と第3項を加算する演算器である。したがって、加算器12hから上記(8)式で示す状態データの虚数部xj[k]が出力される。また、乗算器12e,12fはそれぞれ上記(9)式および(10)式を演算する演算器である。

【0054】

本実施形態では、三相/二相変換部81が、3つの電圧信号Vu,Vv,Vwを、互いに直交するα軸電圧信号Vαおよびβ軸電圧信号Vβに変換している。α軸電圧信号Vαおよびβ軸電圧信号Vβは、それぞれ複素データur+j・ujの実数部と虚数部に対応させることができるので、α軸電圧信号Vαのサンプリングデータを入力データの実数部ur[k]として加算器12gに入力し、β軸電圧信号Vβのサンプリングデータを入力データの虚数部uj[k]として加算器12hに入力している。

【0055】

α軸電圧信号Vαのサンプリングデータが入力される毎に、遅延回路12i、乗算器12a,12b,12eおよび加算器12gで上記(7)式および(9)式の演算処理が繰り返され、これにより、乗算器12eからは出力データyr[k]が出力される。出力データyr[k]は、α軸電圧信号Vαから正規化角周波数Ωdに対応する成分のみを抽出したものとなる。また、β軸電圧信号Vβのサンプリングデータが入力される毎に、遅延回路12j、乗算器12c,12d,12fおよび加算器12hで上記(8)式および(10)式の演算処理が繰り返され、これにより、乗算器12fからは出力データyj[k]が出力される。出力データyj[k]は、β軸電圧信号Vβから正規化角周波数Ωdに対応する成分のみを抽出したものとなる。

【0056】

バンドパスフィルタを実係数の2次IIRフィルタで構成した場合、その2次IIRフィルタの伝達関数H(z)(z=exp(j・ω))は、

H(z)=(1-r2+2(r-1)・r・cos(Ωd)・z-1)/(1-2r・cos(Ωd)・z-1+ r2・z-2)

で表わされる。この伝達関数H(z)の振幅特性M(ω)を求めると、

【数6】

となり、(1−2r・cos(Ωd±ω)+r2)=0を満たすωで極が表れるから、2次IIRフィルタはその極の周波数を通過させる特性を有する。r≒1とすると、cos(Ωd±ω)≒1より、2次IIRフィルタを通過させる正規化周波数fdはfd=±Ωd/2πとなるから、実係数の2次IIRフィルタでは、正相分、逆相分とも通過させることになる。

【0057】

一方、上記(4)式に示す伝達関数H(z)の振幅特性M(ω)求めると、

M(ω)=(1−r)/√{1−2r・cos(Ωd−ω)+r2}

となり、(1−2r・cos(Ωd−ω)+r2)=0を満たすωだけに極が表れる。したがって、複素係数の1次IIRフィルタを通過させる正規化周波数fdはfd=Ωd/2πとなるから、複素係数の1次IIRフィルタでは、正相分または逆相分のいずれか一方のみを通過させることができる。

【0058】

正相分抽出部82は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、基本波の正相分信号を抽出するものである。抽出された正相分信号Yαp,Yβpは、正相分位相調整部84に出力される。正相分抽出部82が備える複素係数バンドパスフィルタの通過帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波(正相分)の角周波数ω0(例えば、ω0=120π[rad/sec](60[Hz]))を正規化したωdがあらかじめ設定されている。正相分抽出部82は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k](図4参照)として複素係数バンドパスフィルタに入力し、出力データyr[k]およびyj[k]を正相分信号Yαp,Yβpとして出力する。

【0059】

図5(a)は、正相分抽出部82が備える複素係数バンドパスフィルタの周波数特性を示す図である。通過帯域の中心角周波数を系統電圧の基本波(正相分)の角周波数ω0としているので、その他の角周波数の信号(逆相分および高調波成分)を好適に除去して、正相分のみを抽出することができる。

【0060】

逆相分抽出部83は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、基本波の逆相分信号を抽出するものである。抽出された逆相分信号Yαn,Yβnは、逆相分位相調整部85に出力される。逆相分抽出部83が備える複素係数バンドパスフィルタの通過帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数があらかじめ設定されている。逆相分は正相分とは相順が逆なので、逆相分の角周波数は正相分の角周波数の負の値となる。つまり、正相分の角周波数ω0の負の値である「−ω0」を正規化した「−ωd」が、正規化角周波数Ωdとして設定されている。逆相分抽出部83は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k](図4参照)として複素係数バンドパスフィルタに入力し、出力データyr[k]およびyj[k]を逆相分信号Yαn,Yβnとして出力する。

【0061】

図5(b)は、逆相分抽出部83が備える複素係数バンドパスフィルタの周波数特性を示す図である。通過帯域の中心角周波数を系統電圧の基本波の逆相分の角周波数「−ω0」としているので、その他の角周波数の信号(正相分および高調波成分)を好適に除去して、基本波の逆相分のみを抽出することができる。

【0062】

なお、正相分抽出部82および逆相分抽出部83が備える複素係数バンドパスフィルタは、上記(4)式に示す伝達関数H(z)のものに限定されない。例えば、複素係数の2次以上のIIRフィルタなどで構成された複素係数バンドパスフィルタであってもよい。

【0063】

正相分位相調整部84は、遅延する位相をあらかじめ進めておくように、位相を調整するものである。遅延する位相は、実験によってあらかじめ取得されており、これを調整するための位相調整量θ0が設定されている。つまり、フィルタ等で位相がθ0だけ遅延する場合、正相分位相調整部84は、正相分信号Yαp,Yβpの位相を位相調整量θ0だけ進める処理をして、位相調整後の正相分信号Y’αp,Y’βpを出力する。

【0064】

正相分位相調整部84で行われる位相調整処理は、下記(11)式に示す行列式で表される。

【数7】

【0065】

逆相分位相調整部85は、遅延する位相をあらかじめ進めておくように、位相を調整するものである。フィルタ等で位相がθ0だけ遅延する場合、逆相分位相調整部85は、逆相分信号Yαn,Yβnの位相を位相調整量θ0だけ進める処理をして、位相調整後の逆相分信号Y’αn,Y’βnを出力する。

【0066】

逆相分の信号の位相を位相調整量θ0だけ進める場合、上記(11)式に示す行列において、θ0を(−θ0)とした行列を用いる。すなわち、逆相分位相調整部85で行われる位相調整処理は、下記(12)式に示す行列式で表される。

【数8】

【0067】

正相分位相調整部84が出力した正相分信号Y’αpと逆相分位相調整部85が出力した逆相分信号Y’αnとが加算された信号Y’αと、正相分信号Y’βpと逆相分信号Y’βnとが加算された信号Y’βとが、振幅調整部86に入力される。振幅調整部86は、信号Y’α,Y’βの振幅を調整するものであり、フィルタで減衰する分を増幅する処理を行い、振幅調整後の信号Yα,Yβを出力する。

【0068】

二相/三相変換部87は、振幅調整部86から出力される信号Yα,Yβを、3つの系統指令値信号Yu,Yv,Ywに変換するものである。二相/三相変換部87は、いわゆる二相/三相変換処理(逆αβ変換処理)を行うものであり、三相/二相変換部81とは逆の変換処理を行うものである。

【0069】

二相/三相変換部87で行われる変換処理は、下記(13)式に示す行列式で表される。

【数9】

【0070】

本実施形態において、系統対抗分生成部8は、電圧信号Vu,Vv,Vwをα軸電圧信号Vαおよびβ軸電圧信号Vβに変換し、正相分信号Yαp,Yβpと逆相分信号Yαn,Yβnとをそれぞれ抽出する。そして、正相分信号Yαp,Yβpの位相を正相分位相調整部84で調整し、逆相分信号Yαn,Yβnの位相を逆相分位相調整部85で調整する。位相を調整された各信号をそれぞれ加算し、振幅調整を行ってから、二相/三相変換によって3つの系統指令値信号Yu,Yv,Ywに変換する。位相の調整方法が異なる正相分信号と逆相分信号がそれぞれ抽出され、それぞれに適した方法で位相調整されるので、系統電圧に逆相分が重畳されている場合でも、系統対抗分生成部8は、位相が適切に調整された系統指令値信号を出力することができる。

【0071】

図6〜8は、本実施形態において行ったシミュレーション結果を説明するための図である。

【0072】

まず、系統対抗分生成部8が出力する系統指令値信号Yu,Yv,Ywを、電力系統Bの系統電圧に精度よく追従させることができるかの検証を行った。そのため、位相調整量θ0=0としてシミュレーションを行っている。図6は、このシミュレーションにおける連系点電圧(系統電圧に相当する。)と系統対抗分(系統指令値信号に相当する。)の波形を、相毎に示している。同図(a)はU相のものであり、同図(b)はV相のものであり、同図(c)はW相のものである。シミュレーション開始から0.2秒後に瞬低をおこし、更に逆相分を印加した。同図(a)〜(c)に示すように、各相とも系統対抗分が連系点電圧に高速に精度よく追従している。

【0073】

次に、位相を調整できるかを検証した。図7は、位相を進めた場合のシミュレーションにおける連系点電圧と系統対抗分の波形を、相毎に示している。当該シミュレーションは、位相調整量θ0=30度とした以外は上記シミュレーションと同じ条件で行っている。また、図8は、位相を遅らせた場合のシミュレーションにおける連系点電圧と系統対抗分の波形を、相毎に示している。当該シミュレーションは、位相調整量θ0=−30度とした以外は上記シミュレーションと同じ条件で行っている。図7および図8に示すように、系統対抗分が連系点電圧に高速に精度よく追従し、かつ、位相の調整を適切に行っている。つまり、系統電圧に逆相分が重畳された状態でも、系統指令値信号の位相を適切に調整することができる。

【0074】

上記第1実施形態においては、複素係数バンドパスフィルタを用いて正相分信号および逆相分信号を抽出する場合について説明したが、複素係数ノッチフィルタ(帯域阻止型の複素係数フィルタ)を用いて正相分信号および逆相分信号を抽出するようにしてもよい。以下に、複素係数ノッチフィルタを用いる場合を第2実施形態として説明する。

【0075】

第2実施形態に係る系統対抗分生成部の内部構成を説明するためのブロック図は、図2に示す第1実施形態の系統対抗分生成部8のものと共通する。第2実施形態においては、図2に示す正相分抽出部82および逆相分抽出部83が複素係数ノッチフィルタを備えている。正相分抽出部82は、複素係数ノッチフィルタが逆相分の通過を抑制することで正相分を抽出し、逆相分抽出部83は、複素係数ノッチフィルタが正相分の通過を抑制することで逆相分を抽出する。

【0076】

正相分抽出部82および逆相分抽出部83が備える複素係数ノッチフィルタは、z変換表現による伝達関数H(z)が下記(14)式で表される複素係数の1次IIRフィルタで構成されている。下記(14)式において、Ωdは阻止帯域の正規化中心角周波数(−π<Ωd<π)であり、rは阻止帯域の帯域幅を決めるパラメータ(0<r<1)であり、jは虚数単位、exp()は自然対数の底eの指数関数である。

【0077】

【数10】

【0078】

図9は、上記(14)式の演算処理を示すブロック図である。図9は、図3に示すブロック図に対して、出力データy[k]を入力データu[k]から減算した値を新しく出力データe[k]として出力する回路を追加したものである。出力データはe[k]となるので、以下では、y[k]を単にデータy[k]と記載する。図9に示すブロック図の詳細説明は省略する。

【0079】

図10は、複素係数ノッチフィルタの複素演算処理を行う回路構成を示す図である。図10は、図4に示すブロック図に対して、実数部の乗算器12eの後段に加算器12nを追加し、当該加算器12nで入力データの実数部ur[k]からデータy[k]の実数部yr[k]を減算して出力データの実数部er[k]を出力する構成としている。また、虚数部の乗算器12fの後段に加算器12oを追加し、当該加算器12oで入力データの虚数部uj[k]からデータy[k]の虚数部yj[k]を減算して出力データの虚数部ej[k]を出力する構成としている。図10に示す回路の演算処理の詳細説明は省略する。

【0080】

乗算器12eより出力されるデータyr[k]を入力データur[k]から減算した値が、出力データer[k]として出力される。出力データer[k]は、α軸電圧信号Vαから正規化角周波数Ωdに対応する成分のみを抑制したものとなる。また、乗算器12fより出力されるデータyj[k]を入力データuj[k]から減算した値が、出力データej[k]として出力される。出力データej[k]は、β軸電圧信号Vβから正規化角周波数Ωdに対応する成分のみを抑制したものとなる。

【0081】

正相分抽出部82が備える複素係数ノッチフィルタの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数「−ω0」を正規化した「−ωd」があらかじめ設定されている。正相分抽出部82は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k]として複素係数ノッチフィルタに入力し、出力データer[k]およびej[k]を正相分信号Yαp,Yβpとして出力する。

【0082】

図11(a)は、正相分抽出部82が備える複素係数ノッチフィルタの周波数特性を示す図である。阻止帯域の中心角周波数を系統電圧の基本波の逆相分の角周波数「−ω0」としているので、その他の角周波数の信号(正相分)を好適に通過させて、正相分のみを抽出することができる。

【0083】

逆相分抽出部83が備える複素係数ノッチフィルタの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波(正相分)の角周波数ω0を正規化したωdがあらかじめ設定されている。逆相分抽出部83は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k]として複素係数ノッチフィルタに入力し、出力データer[k]およびej[k]を逆相分信号Yαn,Yβnとして出力する。

【0084】

図11(b)は、逆相分抽出部83が備える複素係数ノッチフィルタの周波数特性を示す図である。阻止帯域の中心角周波数を系統電圧の基本波(正相分)の角周波数ω0としているので、その他の角周波数の信号(逆相分)を好適に通過させて、基本波の逆相分のみを抽出することができる。

【0085】

なお、正相分抽出部82および逆相分抽出部83が備える複素係数ノッチフィルタは、上記(14)式に示す伝達関数H(z)のものに限定されない。例えば、複素係数の2次以上のIIRフィルタなどで構成された複素係数ノッチフィルタであってもよい。

【0086】

本実施形態においても、正相分信号Yαp,Yβpと逆相分信号Yαn,Yβnとをそれぞれ抽出することができる。そして、正相分位相調整部84および逆相分位相調整部85で、それぞれに適した方法で位相調整されるので、第1実施形態と同様の効果を奏することができる。

【0087】

第2実施形態においては、正相分抽出部82が基本波の逆相分の通過を抑制することで正相分を抽出し、逆相分抽出部83が基本波(正相分)の通過を抑制することで逆相分を抽出する。したがって、α軸電圧信号Vαおよびβ軸電圧信号Vβに高調波成分が含まれていた場合、正相分抽出部82および逆相分抽出部83は、高調波成分も通過させてしまう。高調波成分が含まれている場合に当該高調波成分の通過も抑制することで、基本波の正相分または逆相分をより精度よく抽出する場合を、第3実施形態として、以下に説明する。

【0088】

図12は、第3実施形態に係る正相分抽出部の内部構成を説明するためのブロック図である。

【0089】

図12に示す正相分抽出部82’は、多段に接続された4つの複素係数ノッチフィルタ82a〜82dを備えている点で、第2実施形態に係る正相分抽出部82(図2参照)と異なる。複素係数ノッチフィルタ82aは、第2実施形態に係る正相分抽出部82が備える複素係数ノッチフィルタと同じものであり、基本波の逆相分を抑制するためのものである。複素係数ノッチフィルタ82aの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数「−ω0」を正規化した「−ωd」があらかじめ設定されている。複素係数ノッチフィルタ82b〜82dは、それぞれ5次、7次、11次高調波(正相分)を抑制するためのものである。複素係数ノッチフィルタ82b〜82dの阻止帯域を決定する正規化角周波数Ωdとして、それぞれ「−5ωd」、「7ωd」、「−11ωd」があらかじめ設定されている。

【0090】

図13(a)は、正相分抽出部82’の周波数特性を示す図である。同図(a)によると、基本波の逆相分(角周波数「−ω0」)、5次高調波成分(角周波数「−5ω0」)、7次高調波成分(角周波数「7ω0」)、11次高調波成分(角周波数「−11ω0」)が抑制され、その他の成分が通過される。正相分抽出部82’では、複素係数ノッチフィルタ82a〜82dによって、基本波の逆相分だけではなく、5次、7次、11次高調波(正相分)も抑制されるので、基本波の正相分のみをより好適に通過させることができる。

【0091】

一般的に、電力系統Bに重畳されている高調波は、5次、7次、11次高調波が多いので、本実施形態においては、これらを抑制するようにしている。なお、正相分抽出部82’は、抑制する必要がある高調波の次数に応じて設計すればよい。例えば、高調波としては5次高調波のみを抑制したい場合は、複素係数ノッチフィルタ82aおよび82bのみを備えていればよく、さらに13次高調波も抑制したい場合には、阻止帯域を決定する正規化角周波数Ωdとして「13ωd」を設定した複素係数ノッチフィルタをさらに備えるようにすればよい。

【0092】

同様に、第3実施形態に係る逆相分抽出部(図示しないが、説明上、「逆相分抽出部83’」とする。)は、第2実施形態に係る逆相分抽出部83が備える複素係数ノッチフィルタと、それぞれ5次、7次、11次高調波(正相分)を抑制するための複素係数ノッチフィルタ(図12に示す複素係数ノッチフィルタ82b〜82d)とを備えている。

【0093】

図13(b)は、逆相分抽出部83’の周波数特性を示す図である。同図(b)によると、基本波の正相分(角周波数「ω0」)、5次高調波成分(角周波数「−5ω0」)、7次高調波成分(角周波数「7ω0」)、11次高調波成分(角周波数「−11ω0」)が抑制され、その他の成分が通過される。逆相分抽出部83’では、基本波の正相分だけではなく、5次、7次、11次高調波(正相分)も抑制されるので、基本波の逆相分のみをより好適に通過させることができる。

【0094】

第3実施形態は、電力系統Bに高調波が重畳されている場合でも、基本波の正相分または逆相分を精度よく抽出することができる。

【0095】

上記第1ないし第3実施形態においては、正相分抽出部82(82’)および逆相分抽出部83(83’)がどちらも複素係数バンドパスフィルタまたは複素係数ノッチフィルタを用いる場合について説明したが、これに限られない。例えば、正相分抽出部82が複素係数バンドパスフィルタを用いて正相分信号を通過させることで抽出し、逆相分抽出部83(83’)が複素係数ノッチフィルタを用いて正相分信号の通過を抑制することで逆相分信号を抽出するようにしてもよい。また、正相分抽出部82(82’)が複素係数ノッチフィルタを用いて逆相分信号の通過を抑制することで正相分信号を抽出し、逆相分抽出部83が複素係数バンドパスフィルタを用いて逆相分信号を通過させることで抽出するようにしてもよい。

【0096】

上記第1ないし第3実施形態においては、正相分抽出部82(82’)および逆相分抽出部83(83’)で用いられる正規化角周波数Ωdをあらかじめ設定しておく場合について説明したが、これに限られない。信号処理のサンプリング周期が固定サンプリング周期の場合、系統電圧の基本波の角周波数を周波数検出装置などで検出して、検出された角周波数を正規化して用いるようにしてもよい。

【0097】

上記第1ないし第3実施形態においては、基本波の正相分および逆相分のみを抽出して位相の調整を行っているが、高調波成分も位相の調整をするようにしてもよい。すなわち、電力系統Bに含まれる高調波成分が無視できない場合は、当該高調波成分(例えば、5,7,11次高調波成分)を抽出して位相の調整を行った上で、基本波成分に重畳させるようにすればよい。その際、高調波成分の逆相分も無視できない場合は、基本波成分の場合と同様に、正相分の信号と逆相分の信号とをそれぞれ抽出して、それぞれ位相を調整するようにすればよい。

【0098】

上記第1ないし第3実施形態においては、本発明に係る位相調整装置を系統対抗分生成部に用いた場合について説明したが、これに限られない。例えば、電流制御部71(図1参照)に入力される電流信号I(Iu,Iv,Iw)の位相を調整する場合や、電流制御部71から出力される補正値信号Xu,Xv,Xwの位相を調整する場合にも、本発明に係る位相調整装置を用いることができる。

【0099】

上記第1ないし第3実施形態においては、本発明に係る位相調整装置を系統連系インバータシステムに用いた場合について説明したが、これに限られない。本発明に係る位相調整装置は、三相交流に基づく信号を用いるあらゆる装置や構成において、当該信号の位相を調整する場合に用いることができる。例えば、高調波補償装置、電力用アクティブフィルタ、不平衡補償装置、静止型無効電力補償装置(SVC、SVG)、無停電電源装置(UPS)、力率補償装置、周波数変換装置などの三相交流を扱う装置にも、本発明に係る位相調整装置を用いることができる。

【0100】

本発明に係る位相調整装置、系統対抗分生成装置、系統連系インバータシステム、および、位相調整方法は、上述した実施形態に限定されるものではない。本発明に係る位相調整装置、系統対抗分生成装置、系統連系インバータシステム、および、位相調整方法の各部の具体的な構成は、種々に設計変更自在である。

【符号の説明】

【0101】

A 系統連系インバータシステム

1 直流電源

2 インバータ回路

3 フィルタ回路

4 変圧回路

5 電流センサ

6 電圧センサ

7 制御回路

71 電流制御部

72 PWM信号生成部

8 系統対抗分生成部

81 三相/二相変換部

82,82' 正相分抽出部

82a,82b,82c,82d 複素係数ノッチフィルタ

83 逆相分抽出部

84 正相分位相調整部

85 逆相分位相調整部

86 振幅調整部

87 二相/三相変換部

B 電力系統

【技術分野】

【0001】

本発明は、位相の遅延分をあらかじめ調整するための位相調整装置、当該位相調整装置を備えた系統対抗分生成装置、当該系統対抗分生成装置を備えた系統連系インバータシステム、および、位相調整方法に関する。

【背景技術】

【0002】

従来、太陽電池などによって生成される直流電力を交流電力に変換して、電力系統に供給する系統連系インバータシステムが開発されている。

【0003】

図14は、従来の一般的な系統連系インバータシステムを説明するためのブロック図である。

【0004】

系統連系インバータシステムA100は、直流電源1が生成した直流電力を交流電力に変換して三相の電力系統Bに供給するものである。なお、以下では3つの相をU相、V相およびW相とする。

【0005】

インバータ回路2は、直流電源1から入力される直流電圧をスイッチング素子(図示しない)のスイッチングにより交流電圧に変換する。フィルタ回路3は、インバータ回路2から出力される交流電圧に含まれるスイッチング周波数成分を除去する。変圧回路4は、フィルタ回路3から出力される交流電圧を電力系統Bの系統電圧に昇圧(または降圧)する。制御回路700は、電流センサ5および電圧センサ6などが検出した電流信号および電圧信号を入力され、これに基づいてPWM信号を生成してインバータ回路2に出力する。インバータ回路2は、制御回路700から入力されるPWM信号に基づいてスイッチング素子のスイッチングを行う。

【0006】

制御回路700は、電流制御部71、系統対抗分生成部800、およびPWM信号生成部72を備えている。電流制御部71は、電流センサ5より入力される電流信号I(Iu,Iv,Iw)に基づいて、電流制御のための補正値信号Xu,Xv,Xwを生成して出力する。系統対抗分生成部800は、電圧センサ6より入力される電圧信号V(Vu,Vv,Vw)に基づいて、系統指令値信号Yu,Yv,Ywを生成して出力する。系統指令値信号Yu,Yv,Ywと補正値信号Xu,Xv,Xwとをそれぞれ加算した指令値信号X’u,X’v,X’wがPWM信号生成部72に入力される。PWM信号生成部72は、入力される指令値信号X’u,X’v,X’wに基づいてPWM信号Pu,Pv,Pwを生成して、インバータ回路2に出力する。

【0007】

フィルタ回路3などのフィルタや電圧検出などの処理では、位相の遅れが生じる。この位相の遅れによる不都合を解消するための処理が、系統対抗分生成部800で行われる。例えば、位相の遅れによる電圧の変化分をあらかじめ増減させた系統指令値信号Yu,Yv,Ywを生成する方法や、位相の遅れ分だけ系統指令値信号Yu,Yv,Ywの位相をあらかじめ進めておく方法などが提案されている。

【先行技術文献】

【特許文献】

【0008】

【特許文献1】特開平9−271176号公報

【発明の概要】

【発明が解決しようとする課題】

【0009】

しかしながら、電力系統Bには基本波の正相分の交流信号の他に逆相分の交流信号が含まれているので、上記の位相調整方法の場合、適切に位相の調整を行うことができない。すなわち、電圧センサ6より入力される電圧信号Vに基づく系統指令値信号Yu,Yv,Ywにも逆相分の信号が含まれている。系統指令値信号Yu,Yv,Ywの正相分の信号の位相を進める処理を行うと、正相分の信号とは相順が逆になっている逆相分の信号は、位相が遅れることになる。これにより、逆相分の信号は、フィルタなどで位相が遅れる上に更に位相が遅れるので、大幅に位相が遅れることになる。この場合、系統対抗分生成部800から出力される系統指令値信号Yu,Yv,Ywを電力系統Bの系統電圧に精度よく追従させることが困難になる。

【0010】

特に、瞬低などの系統擾乱によって電力系統Bの逆相分が増加した場合、追従の精度がより悪くなる。この結果、系統電圧と系統連系インバータシステムの出力電圧とに差が生じて過電流が流れる。過電流が流れると系統連系インバータシステムは停止され電力系統Bから切り離される。これにより、電力系統Bの系統擾乱が拡大されてしまう。

【0011】

本発明は上記した事情のもとで考え出されたものであって、信号に逆相分が重畳されている場合でも、当該信号の位相を適切に調整することができる位相調整装置を提供することをその目的としている。

【課題を解決するための手段】

【0012】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0013】

本発明の第1の側面によって提供される位相調整装置は、三相交流に基づく3つの信号の位相を調整する位相調整装置であって、前記3つの信号を第1の信号および第2の信号に変換する三相二相変換手段と、前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号とを、それぞれ抽出する正相分抽出手段と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とを、それぞれ抽出する逆相分抽出手段と、前記正相分抽出手段によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する正相分位相調整手段と、前記逆相分抽出手段によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する逆相分位相調整手段と、位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する加算手段と、前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する二相三相変換手段とを備えており、前記正相分抽出手段および前記逆相分抽出手段は、それぞれ複素係数フィルタを用いて各信号を抽出することを特徴とする。なお、「正相分の信号」とは、三相交流の基本波と周波数が同じで相順が同じ信号であり、「逆相分の信号」とは、三相交流の基本波と周波数が同じで相順が逆の信号である。

【0014】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域通過型の複素係数フィルタである。

【0015】

本発明の好ましい実施の形態においては、前記複素係数フィルタのz変換表現による伝達関数H(z)は、通過帯域の正規化中心角周波数をΩd(−π<Ωd<π)、通過帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数1】

である。

【0016】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域阻止型の複素係数フィルタである。

【0017】

本発明の好ましい実施の形態においては、前記複素係数フィルタのz変換表現による伝達関数H(z)は、阻止帯域の正規化中心角周波数をΩd(−π<Ωd<π)、阻止帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数2】

である。

【0018】

本発明の好ましい実施の形態においては、前記正相分抽出手段または前記逆相分抽出手段は、複数の複素係数フィルタを多段に接続したフィルタを用いる。

【0019】

本発明の好ましい実施の形態においては、前記正相分位相調整手段は、前記第1の正相分信号をXα、前記第2の正相分信号をXβ、位相調整量をθ0とすると、位相調整後の第1の正相分信号X’αおよび第2の正相分信号X’βを、下記(1)式に示す行列式によって算出し、前記逆相分位相調整手段は、前記第1の逆相分信号をYα、前記第2の逆相分信号をYβ、位相調整量をθ0とすると、位相調整後の第1の逆相分信号Y’αおよび第2の逆相分信号Y’βを、下記(2)式に示す行列式によって算出する。

【数3】

【0020】

本発明の好ましい実施の形態においては、前記第1の調整後信号および前記第2の調整後信号の振幅を調整する振幅調整手段をさらに備えている。

【0021】

本発明の第2の側面によって提供される系統対抗分生成装置は、本発明の第1の側面によって提供される位相調整装置によって、電圧検出手段により検出された三相電力系統の各相の電圧信号の位相を調整して出力することを特徴とする。

【0022】

本発明の第3の側面によって提供される系統連系インバータシステムは、本発明の第2の側面によって提供される系統対抗分生成装置から出力される位相調整後の各相の電圧信号に基づいてPWM信号を生成して出力する制御回路と、前記制御回路から入力されるPWM信号に基づいて、直流電力を交流電力に変換するインバータ回路とを備えていることを特徴とする。

【0023】

本発明の第4の側面によって提供される位相調整方法は、三相交流に基づく3つの信号の位相を調整する位相調整方法であって、前記3つの信号を第1の信号および第2の信号に変換する第1の工程と、前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とをそれぞれ抽出する第2の工程と、前記第2の工程によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する第3の工程と、前記第2の工程によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する第4の工程と、位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する第5の工程と、前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する第6の工程とを備えており、前記第2の工程は、複素係数フィルタを用いて各信号を抽出することを特徴とする。

【発明の効果】

【0024】

本発明によれば、正相分の信号と逆相分の信号とがそれぞれ抽出され、正相分の信号は正相分位相調整手段で位相を調整され、逆相分の信号は逆相分位相調整手段で位相を調整される。そして、位相を調整された各信号から、3つの調整後信号が生成される。正相分の信号と逆相分の信号とを、それぞれに適した方法を用いて位相調整するので、三相交流に基づく信号に逆相分が重畳されている場合でも、当該信号の位相を適切に調整することができる。

【0025】

本発明のその他の特徴および利点は、添付図面を参照して以下に行う詳細な説明によって、より明らかとなろう。

【図面の簡単な説明】

【0026】

【図1】第1実施形態に係る系統連系インバータシステムを説明するためのブロック図である。

【図2】第1実施形態に係る系統対抗分生成部の内部構成を説明するためのブロック図である。

【図3】複素係数バンドパスフィルタの演算処理を示すブロック図である。

【図4】複素係数バンドパスフィルタの複素演算処理を行う回路構成を示す図である。

【図5】複素係数バンドパスフィルタの周波数特性を示す図である。

【図6】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図7】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図8】第1実施形態において行ったシミュレーション結果を説明するための図である。

【図9】複素係数ノッチフィルタの演算処理を示すブロック図である。

【図10】複素係数ノッチフィルタの複素演算処理を行う回路構成を示す図である。

【図11】複素係数ノッチフィルタの周波数特性を示す図である。

【図12】第3実施形態に係る正相分抽出部の内部構成を説明するためのブロック図である。

【図13】第3実施形態に係る正相分抽出部の周波数特性を示す図である。

【図14】従来の一般的な系統連系インバータシステムを説明するためのブロック図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施の形態を、本発明に係る位相調整装置を系統連系インバータシステムの系統対抗分生成部に用いた場合を例として、図面を参照して具体的に説明する。

【0028】

図1は、第1実施形態に係る系統連系インバータシステムを説明するためのブロック図である。

【0029】

同図に示すように、系統連系インバータシステムAは、直流電源1、インバータ回路2、フィルタ回路3、変圧回路4、電流センサ5、電圧センサ6、および制御回路7を備えている。

【0030】

直流電源1は、インバータ回路2に接続している。インバータ回路2、フィルタ回路3、および変圧回路4は、この順で、U相、V相、W相の出力電圧の出力ラインに直列に接続されて、三相交流の電力系統Bに接続している。電流センサ5および電圧センサ6は、変圧回路4の出力側に設置されている。制御回路7は、インバータ回路2に接続されている。系統連系インバータシステムAは、直流電源1が出力する直流電力を交流電力に変換して電力系統Bに供給する。なお、系統連系インバータシステムAの構成は、これに限られない。例えば、電流センサ5および電圧センサ6を変圧回路4の入力側に設けてもよいし、インバータ回路2の制御に必要な他のセンサを設けていてもよい。また、変圧回路4をフィルタ回路3の入力側に設けるようにしてもよいし、変圧回路4を設けない、いわゆるトランスレス方式にしてもよい。また、直流電源1とインバータ回路2との間にDC/DCコンバータ回路を設けるようにしてもよい。

【0031】

直流電源1は、直流電力を出力するものであり、例えば太陽電池を備えている。太陽電池は、太陽光エネルギーを電気エネルギーに変換することで、直流電力を生成する。直流電源1は、生成された直流電力を、インバータ回路2に出力する。なお、直流電源1は、太陽電池により直流電力を生成するものに限定されない。例えば、直流電源1は、燃料電池、蓄電池、電気二重層コンデンサやリチウムイオン電池であってもよいし、ディーゼルエンジン発電機、マイクロガスタービン発電機や風力タービン発電機などにより生成された交流電力を直流電力に変換して出力する装置であってもよい。

【0032】

インバータ回路2は、直流電源1から入力される直流電圧を交流電圧に変換して、フィルタ回路3に出力するものである。インバータ回路2は、三相インバータであり、図示しない3組6個のスイッチング素子を備えたPWM制御型インバータ回路である。インバータ回路2は、制御回路7から入力されるPWM信号に基づいて、各スイッチング素子のオンとオフとを切り替えることで、直流電源1から入力される直流電圧を交流電圧に変換する。なお、インバータ回路2はこれに限定されず、例えば、マルチレベルインバータであってもよい。

【0033】

フィルタ回路3は、インバータ回路2から入力される交流電圧から、スイッチングによる高周波成分を除去するものである。フィルタ回路3は、リアクトルとコンデンサとからなるローパスフィルタを備えている。フィルタ回路3で高周波成分を除去された交流電圧は、変圧回路4に出力される。なお、フィルタ回路3の構成はこれに限定されず、高周波成分を除去するための周知のフィルタ回路であればよい。変圧回路4は、フィルタ回路3から出力される交流電圧を系統電圧とほぼ同一のレベルに昇圧または降圧する。

【0034】

電流センサ5は、変圧回路4から出力される各相の交流電流(すなわち、系統連系インバータシステムAの出力電流)を検出するものである。検出された電流信号I(Iu,Iv,Iw)は、制御回路7に入力される。電圧センサ6は、電力系統Bの各相の系統電圧を検出するものである。検出された電圧信号V(Vu,Vv,Vw)は、制御回路7に入力される。なお、系統連系インバータシステムAが出力する出力電圧は、系統電圧とほぼ一致している。

【0035】

制御回路7は、インバータ回路2を制御するものであり、例えばマイクロコンピュータなどによって実現されている。制御回路7は、電流センサ5から入力される電流信号I、および、電圧センサ6から入力される電圧信号Vに基づいて、PWM信号を生成してインバータ回路2に出力する。制御回路7は、系統連系インバータシステムAが出力する出力電圧の波形を指令するための指令値信号を各センサから入力される検出信号に基づいて生成し、当該指令値信号に基づいて生成されるパルス信号をPWM信号として出力する。インバータ回路2は、入力されるPWM信号に基づいて各スイッチング素子のオンとオフとを切り替えることで、指令値信号に対応した波形の交流電圧を出力する。制御回路7は、指令値信号の波形を変化させて系統連系インバータシステムAの出力電圧の波形を変化させることで、出力電流を制御している。これにより、制御回路7は、各種フィードバック制御を行っている。指令値信号は、電圧センサ6が検出した電圧信号Vを基にした信号に、電流制御のための補償信号を加算することで生成される。

【0036】

図1においては、出力電流制御を行うための構成のみを記載して、その他の制御のための構成を省略している。実際には、制御回路7は、直流電圧制御(入力直流電圧が予め設定された電圧目標値となるように行うフィードバック制御)や無効電力制御(出力無効電力が予め設定された無効電力目標値となるように行うフィードバック制御)なども行っている。なお、制御回路7が行う制御の手法は、これに限られない。例えば、出力電圧制御や有効電力制御を行うようにしてもよい。

【0037】

制御回路7は、電流制御部71、PWM信号生成部72、および系統対抗分生成部8を備えている。

【0038】

電流制御部71は、電流センサ5より入力される電流信号I(Iu,Iv,Iw)に基づいて、電流制御のための補正値信号Xu,Xv,Xwを生成するものである。電流制御部71は、電流信号Iu,Iv,Iwをそれぞれの目標値に一致させるためのフィードバック制御を行うためのものであり、当該制御のための補償信号として補正値信号Xu,Xv,Xwを出力する。後述する系統対抗分生成部8が出力する系統指令値信号Yu,Yv,Ywと、電流制御部71が出力する補正値信号Xu,Xv,Xwとがそれぞれ加算されて、指令値信号X’u,X’v,X’wが算出され、PWM信号生成部72に入力される。

【0039】

PWM信号生成部72は、入力される指令値信号X’u,X’v,X’wと、所定の周波数(例えば、4kHz)の三角波信号として生成されたキャリア信号とに基づいて、三角波比較法によりPWM信号Pu,Pv,Pwを生成する。三角波比較法では、指令値信号X’u,X’v,X’wとキャリア信号とがそれぞれ比較され、例えば、指令値信号X’uがキャリア信号より大きい場合にハイレベルとなり、小さい場合にローレベルとなるパルス信号がPWM信号Puとして生成される。生成されたPWM信号Pu,Pv,Pwは、インバータ回路2に出力される。

【0040】

系統対抗分生成部8は、電圧センサ6から電圧信号V(Vu,Vv,Vw)を入力されて、系統指令値信号Yu,Yv,Ywを生成して出力する。系統指令値信号Yu,Yv,Ywは系統連系インバータシステムAが出力する出力電圧の波形を指令するための指令値信号X’u,X’v,X’wの基準となるものであり、系統指令値信号Yu,Yv,Ywが補正値信号Xu,Xv,Xwで補正されることにより指令値信号X’u,X’v,X’wが生成される。系統対抗分生成部8は、フィルタ回路3等で遅延する位相の遅れ分を進めて、系統指令値信号Yu,Yv,Ywを生成する。系統対抗分生成部8は、電圧信号Vに含まれる正相分の信号と逆相分の信号とをそれぞれ抽出し、別々に位相を進める処理を行う。正相分の信号と逆相分の信号とは、それぞれ位相を進められてから加算される。

【0041】

図2は、系統対抗分生成部8の内部構成を説明するためのブロック図である。

【0042】

同図に示すように、系統対抗分生成部8は、三相/二相変換部81、正相分抽出部82、逆相分抽出部83、正相分位相調整部84、逆相分位相調整部85、振幅調整部86、および二相/三相変換部87を備えている。

【0043】

三相/二相変換部81は、電圧センサ6より入力される3つの電圧信号Vu,Vv,Vwを、α軸電圧信号Vαおよびβ軸電圧信号Vβに変換するものである。三相/二相変換部81は、いわゆる三相/二相変換処理(αβ変換処理)を行うものであり、電圧信号Vu,Vv,Vwを互いに直交するα軸成分とβ軸成分とにそれぞれ分解して、各軸成分をまとめることでα軸電圧信号Vαおよびβ軸電圧信号Vβを生成する。

【0044】

三相/二相変換部81で行われる変換処理は、下記(3)式に示す行列式で表される。

【数4】

【0045】

正相分抽出部82および逆相分抽出部83は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、特定の周波数成分の信号を抽出するものであり、複素係数バンドパスフィルタ(帯域通過型の複素係数フィルタ)を備えている。

【0046】

当該複素係数バンドパスフィルタは、z変換表現による伝達関数H(z)が下記(4)式で表される複素係数の1次IIRフィルタで構成されている。下記(4)式において、複素係数a1におけるfdは、通過帯域の中心周波数f0をサンプリング周波数で正規化した正規化周波数である。また、Ωdは、正規化角周波数である。例えば、サンプリング周波数をfsrとすると、正規化周波数fdはf0/fsr、正規化角周波数Ωdは2π・fd=2π・(f0/fsr)となる。なお、正規化角周波数Ωdは、−π<Ωd<πである。また、rは通過帯域の帯域幅を決めるパラメータ(0<r<1)であり、jは虚数単位、exp()は自然対数の底eの指数関数である。

【0047】

【数5】

【0048】

図3は、上記(4)式の演算処理を示すブロック図である。同図に示すように、複素係数バンドパスフィルタは、上記(4)式の分母の演算処理がフィードバック回路で構成され、そのフィードバック回路の出力に分子の係数b0を乗算する回路によって構成される。

【0049】

図3に示すブロック図において、u[k](k:離散時間を表すインデックス番号)は入力データ、x[k]は状態データ、y[k]は出力データである。入力データu[k]、状態データx[k]および出力データy[k]の間には、

x[k]=r・exp(j・Ωd)・x[k-1]+u[k] …(5)

y[k]=(1−r)・x[k] …(6)

が成立する。

【0050】

複素係数バンドパスフィルタにおいては、入力データu[k]が複素データか実データ(複素データの虚数部が「0」のデータ)かに関わらず、状態データx[k]および出力データy[k]が複素データとなる。したがって、入力データu[k]、状態データx[k]および出力データy[k]をそれぞれu[k]=ur[k]+j・uj[k]、x[k]=xr[k]+j・xj[k]、y[k]=yr[k]+j・yj[k]の複素データとし、複素係数a1をa1=r・exp(j・Ωd)=ar+j・aj=r・cos(Ωd)+j・r・sin(Ωd)として、上記(5)式および(6)式に代入して、実数部と虚数部の関係式に分けると、

xr[k]=r・cos(Ωd)・xr[k-1]−r・sin(Ωd)・xj[k-1]+ur[k] …(7)

xj[k]=r・cos(Ωd)・xj[k-1]+r・sin(Ωd)・xr[k-1]+uj[k] …(8)

yr[k]=(1−r)・xr[k] …(9)

yj[k]=(1−r)・xj[k] …(10)

となる。

【0051】

図4は、上記(7)式〜(10)式に基づき複素係数バンドパスフィルタの複素演算処理を行う回路構成を示す図である。同図において、係数arおよび係数ajは、それぞれ複素係数a1=r・exp(j・Ωd)の実数部および虚数部であり、ar=r・cos(Ωd)、aj=r・sin(Ωd)である。

【0052】

同図に示すように、複素係数バンドパスフィルタは、6個の乗算器12a〜12fと、2個の加算器12g,12hと、2個の遅延回路12i,12jで構成される。遅延回路12iは、状態データの実数部xr[k-1]を生成する回路であり、遅延回路12jは、状態データの虚数部xj[k-1]を生成する回路である。乗算器12a,12bはそれぞれ上記(7)式の第1項と第2項(負の符号を含む)を演算する演算器であり、加算器12gは上記(7)式の第1項と第2項と第3項を加算する演算器である。したがって、加算器12gから上記(7)式で示す状態データの実数部xr[k]が出力される。

【0053】

一方、乗算器12c,12dはそれぞれ上記(8)式の第1項と第2項を演算する演算器であり、加算器12hは上記(8)式の第1項と第2項と第3項を加算する演算器である。したがって、加算器12hから上記(8)式で示す状態データの虚数部xj[k]が出力される。また、乗算器12e,12fはそれぞれ上記(9)式および(10)式を演算する演算器である。

【0054】

本実施形態では、三相/二相変換部81が、3つの電圧信号Vu,Vv,Vwを、互いに直交するα軸電圧信号Vαおよびβ軸電圧信号Vβに変換している。α軸電圧信号Vαおよびβ軸電圧信号Vβは、それぞれ複素データur+j・ujの実数部と虚数部に対応させることができるので、α軸電圧信号Vαのサンプリングデータを入力データの実数部ur[k]として加算器12gに入力し、β軸電圧信号Vβのサンプリングデータを入力データの虚数部uj[k]として加算器12hに入力している。

【0055】

α軸電圧信号Vαのサンプリングデータが入力される毎に、遅延回路12i、乗算器12a,12b,12eおよび加算器12gで上記(7)式および(9)式の演算処理が繰り返され、これにより、乗算器12eからは出力データyr[k]が出力される。出力データyr[k]は、α軸電圧信号Vαから正規化角周波数Ωdに対応する成分のみを抽出したものとなる。また、β軸電圧信号Vβのサンプリングデータが入力される毎に、遅延回路12j、乗算器12c,12d,12fおよび加算器12hで上記(8)式および(10)式の演算処理が繰り返され、これにより、乗算器12fからは出力データyj[k]が出力される。出力データyj[k]は、β軸電圧信号Vβから正規化角周波数Ωdに対応する成分のみを抽出したものとなる。

【0056】

バンドパスフィルタを実係数の2次IIRフィルタで構成した場合、その2次IIRフィルタの伝達関数H(z)(z=exp(j・ω))は、

H(z)=(1-r2+2(r-1)・r・cos(Ωd)・z-1)/(1-2r・cos(Ωd)・z-1+ r2・z-2)

で表わされる。この伝達関数H(z)の振幅特性M(ω)を求めると、

【数6】

となり、(1−2r・cos(Ωd±ω)+r2)=0を満たすωで極が表れるから、2次IIRフィルタはその極の周波数を通過させる特性を有する。r≒1とすると、cos(Ωd±ω)≒1より、2次IIRフィルタを通過させる正規化周波数fdはfd=±Ωd/2πとなるから、実係数の2次IIRフィルタでは、正相分、逆相分とも通過させることになる。

【0057】

一方、上記(4)式に示す伝達関数H(z)の振幅特性M(ω)求めると、

M(ω)=(1−r)/√{1−2r・cos(Ωd−ω)+r2}

となり、(1−2r・cos(Ωd−ω)+r2)=0を満たすωだけに極が表れる。したがって、複素係数の1次IIRフィルタを通過させる正規化周波数fdはfd=Ωd/2πとなるから、複素係数の1次IIRフィルタでは、正相分または逆相分のいずれか一方のみを通過させることができる。

【0058】

正相分抽出部82は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、基本波の正相分信号を抽出するものである。抽出された正相分信号Yαp,Yβpは、正相分位相調整部84に出力される。正相分抽出部82が備える複素係数バンドパスフィルタの通過帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波(正相分)の角周波数ω0(例えば、ω0=120π[rad/sec](60[Hz]))を正規化したωdがあらかじめ設定されている。正相分抽出部82は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k](図4参照)として複素係数バンドパスフィルタに入力し、出力データyr[k]およびyj[k]を正相分信号Yαp,Yβpとして出力する。

【0059】

図5(a)は、正相分抽出部82が備える複素係数バンドパスフィルタの周波数特性を示す図である。通過帯域の中心角周波数を系統電圧の基本波(正相分)の角周波数ω0としているので、その他の角周波数の信号(逆相分および高調波成分)を好適に除去して、正相分のみを抽出することができる。

【0060】

逆相分抽出部83は、三相/二相変換部81より入力されるα軸電圧信号Vαおよびβ軸電圧信号Vβから、基本波の逆相分信号を抽出するものである。抽出された逆相分信号Yαn,Yβnは、逆相分位相調整部85に出力される。逆相分抽出部83が備える複素係数バンドパスフィルタの通過帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数があらかじめ設定されている。逆相分は正相分とは相順が逆なので、逆相分の角周波数は正相分の角周波数の負の値となる。つまり、正相分の角周波数ω0の負の値である「−ω0」を正規化した「−ωd」が、正規化角周波数Ωdとして設定されている。逆相分抽出部83は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k](図4参照)として複素係数バンドパスフィルタに入力し、出力データyr[k]およびyj[k]を逆相分信号Yαn,Yβnとして出力する。

【0061】

図5(b)は、逆相分抽出部83が備える複素係数バンドパスフィルタの周波数特性を示す図である。通過帯域の中心角周波数を系統電圧の基本波の逆相分の角周波数「−ω0」としているので、その他の角周波数の信号(正相分および高調波成分)を好適に除去して、基本波の逆相分のみを抽出することができる。

【0062】

なお、正相分抽出部82および逆相分抽出部83が備える複素係数バンドパスフィルタは、上記(4)式に示す伝達関数H(z)のものに限定されない。例えば、複素係数の2次以上のIIRフィルタなどで構成された複素係数バンドパスフィルタであってもよい。

【0063】

正相分位相調整部84は、遅延する位相をあらかじめ進めておくように、位相を調整するものである。遅延する位相は、実験によってあらかじめ取得されており、これを調整するための位相調整量θ0が設定されている。つまり、フィルタ等で位相がθ0だけ遅延する場合、正相分位相調整部84は、正相分信号Yαp,Yβpの位相を位相調整量θ0だけ進める処理をして、位相調整後の正相分信号Y’αp,Y’βpを出力する。

【0064】

正相分位相調整部84で行われる位相調整処理は、下記(11)式に示す行列式で表される。

【数7】

【0065】

逆相分位相調整部85は、遅延する位相をあらかじめ進めておくように、位相を調整するものである。フィルタ等で位相がθ0だけ遅延する場合、逆相分位相調整部85は、逆相分信号Yαn,Yβnの位相を位相調整量θ0だけ進める処理をして、位相調整後の逆相分信号Y’αn,Y’βnを出力する。

【0066】

逆相分の信号の位相を位相調整量θ0だけ進める場合、上記(11)式に示す行列において、θ0を(−θ0)とした行列を用いる。すなわち、逆相分位相調整部85で行われる位相調整処理は、下記(12)式に示す行列式で表される。

【数8】

【0067】

正相分位相調整部84が出力した正相分信号Y’αpと逆相分位相調整部85が出力した逆相分信号Y’αnとが加算された信号Y’αと、正相分信号Y’βpと逆相分信号Y’βnとが加算された信号Y’βとが、振幅調整部86に入力される。振幅調整部86は、信号Y’α,Y’βの振幅を調整するものであり、フィルタで減衰する分を増幅する処理を行い、振幅調整後の信号Yα,Yβを出力する。

【0068】

二相/三相変換部87は、振幅調整部86から出力される信号Yα,Yβを、3つの系統指令値信号Yu,Yv,Ywに変換するものである。二相/三相変換部87は、いわゆる二相/三相変換処理(逆αβ変換処理)を行うものであり、三相/二相変換部81とは逆の変換処理を行うものである。

【0069】

二相/三相変換部87で行われる変換処理は、下記(13)式に示す行列式で表される。

【数9】

【0070】

本実施形態において、系統対抗分生成部8は、電圧信号Vu,Vv,Vwをα軸電圧信号Vαおよびβ軸電圧信号Vβに変換し、正相分信号Yαp,Yβpと逆相分信号Yαn,Yβnとをそれぞれ抽出する。そして、正相分信号Yαp,Yβpの位相を正相分位相調整部84で調整し、逆相分信号Yαn,Yβnの位相を逆相分位相調整部85で調整する。位相を調整された各信号をそれぞれ加算し、振幅調整を行ってから、二相/三相変換によって3つの系統指令値信号Yu,Yv,Ywに変換する。位相の調整方法が異なる正相分信号と逆相分信号がそれぞれ抽出され、それぞれに適した方法で位相調整されるので、系統電圧に逆相分が重畳されている場合でも、系統対抗分生成部8は、位相が適切に調整された系統指令値信号を出力することができる。

【0071】

図6〜8は、本実施形態において行ったシミュレーション結果を説明するための図である。

【0072】

まず、系統対抗分生成部8が出力する系統指令値信号Yu,Yv,Ywを、電力系統Bの系統電圧に精度よく追従させることができるかの検証を行った。そのため、位相調整量θ0=0としてシミュレーションを行っている。図6は、このシミュレーションにおける連系点電圧(系統電圧に相当する。)と系統対抗分(系統指令値信号に相当する。)の波形を、相毎に示している。同図(a)はU相のものであり、同図(b)はV相のものであり、同図(c)はW相のものである。シミュレーション開始から0.2秒後に瞬低をおこし、更に逆相分を印加した。同図(a)〜(c)に示すように、各相とも系統対抗分が連系点電圧に高速に精度よく追従している。

【0073】

次に、位相を調整できるかを検証した。図7は、位相を進めた場合のシミュレーションにおける連系点電圧と系統対抗分の波形を、相毎に示している。当該シミュレーションは、位相調整量θ0=30度とした以外は上記シミュレーションと同じ条件で行っている。また、図8は、位相を遅らせた場合のシミュレーションにおける連系点電圧と系統対抗分の波形を、相毎に示している。当該シミュレーションは、位相調整量θ0=−30度とした以外は上記シミュレーションと同じ条件で行っている。図7および図8に示すように、系統対抗分が連系点電圧に高速に精度よく追従し、かつ、位相の調整を適切に行っている。つまり、系統電圧に逆相分が重畳された状態でも、系統指令値信号の位相を適切に調整することができる。

【0074】

上記第1実施形態においては、複素係数バンドパスフィルタを用いて正相分信号および逆相分信号を抽出する場合について説明したが、複素係数ノッチフィルタ(帯域阻止型の複素係数フィルタ)を用いて正相分信号および逆相分信号を抽出するようにしてもよい。以下に、複素係数ノッチフィルタを用いる場合を第2実施形態として説明する。

【0075】

第2実施形態に係る系統対抗分生成部の内部構成を説明するためのブロック図は、図2に示す第1実施形態の系統対抗分生成部8のものと共通する。第2実施形態においては、図2に示す正相分抽出部82および逆相分抽出部83が複素係数ノッチフィルタを備えている。正相分抽出部82は、複素係数ノッチフィルタが逆相分の通過を抑制することで正相分を抽出し、逆相分抽出部83は、複素係数ノッチフィルタが正相分の通過を抑制することで逆相分を抽出する。

【0076】

正相分抽出部82および逆相分抽出部83が備える複素係数ノッチフィルタは、z変換表現による伝達関数H(z)が下記(14)式で表される複素係数の1次IIRフィルタで構成されている。下記(14)式において、Ωdは阻止帯域の正規化中心角周波数(−π<Ωd<π)であり、rは阻止帯域の帯域幅を決めるパラメータ(0<r<1)であり、jは虚数単位、exp()は自然対数の底eの指数関数である。

【0077】

【数10】

【0078】

図9は、上記(14)式の演算処理を示すブロック図である。図9は、図3に示すブロック図に対して、出力データy[k]を入力データu[k]から減算した値を新しく出力データe[k]として出力する回路を追加したものである。出力データはe[k]となるので、以下では、y[k]を単にデータy[k]と記載する。図9に示すブロック図の詳細説明は省略する。

【0079】

図10は、複素係数ノッチフィルタの複素演算処理を行う回路構成を示す図である。図10は、図4に示すブロック図に対して、実数部の乗算器12eの後段に加算器12nを追加し、当該加算器12nで入力データの実数部ur[k]からデータy[k]の実数部yr[k]を減算して出力データの実数部er[k]を出力する構成としている。また、虚数部の乗算器12fの後段に加算器12oを追加し、当該加算器12oで入力データの虚数部uj[k]からデータy[k]の虚数部yj[k]を減算して出力データの虚数部ej[k]を出力する構成としている。図10に示す回路の演算処理の詳細説明は省略する。

【0080】

乗算器12eより出力されるデータyr[k]を入力データur[k]から減算した値が、出力データer[k]として出力される。出力データer[k]は、α軸電圧信号Vαから正規化角周波数Ωdに対応する成分のみを抑制したものとなる。また、乗算器12fより出力されるデータyj[k]を入力データuj[k]から減算した値が、出力データej[k]として出力される。出力データej[k]は、β軸電圧信号Vβから正規化角周波数Ωdに対応する成分のみを抑制したものとなる。

【0081】

正相分抽出部82が備える複素係数ノッチフィルタの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数「−ω0」を正規化した「−ωd」があらかじめ設定されている。正相分抽出部82は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k]として複素係数ノッチフィルタに入力し、出力データer[k]およびej[k]を正相分信号Yαp,Yβpとして出力する。

【0082】

図11(a)は、正相分抽出部82が備える複素係数ノッチフィルタの周波数特性を示す図である。阻止帯域の中心角周波数を系統電圧の基本波の逆相分の角周波数「−ω0」としているので、その他の角周波数の信号(正相分)を好適に通過させて、正相分のみを抽出することができる。

【0083】

逆相分抽出部83が備える複素係数ノッチフィルタの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波(正相分)の角周波数ω0を正規化したωdがあらかじめ設定されている。逆相分抽出部83は、α軸電圧信号Vαおよびβ軸電圧信号Vβを入力データur[k]およびuj[k]として複素係数ノッチフィルタに入力し、出力データer[k]およびej[k]を逆相分信号Yαn,Yβnとして出力する。

【0084】

図11(b)は、逆相分抽出部83が備える複素係数ノッチフィルタの周波数特性を示す図である。阻止帯域の中心角周波数を系統電圧の基本波(正相分)の角周波数ω0としているので、その他の角周波数の信号(逆相分)を好適に通過させて、基本波の逆相分のみを抽出することができる。

【0085】

なお、正相分抽出部82および逆相分抽出部83が備える複素係数ノッチフィルタは、上記(14)式に示す伝達関数H(z)のものに限定されない。例えば、複素係数の2次以上のIIRフィルタなどで構成された複素係数ノッチフィルタであってもよい。

【0086】

本実施形態においても、正相分信号Yαp,Yβpと逆相分信号Yαn,Yβnとをそれぞれ抽出することができる。そして、正相分位相調整部84および逆相分位相調整部85で、それぞれに適した方法で位相調整されるので、第1実施形態と同様の効果を奏することができる。

【0087】

第2実施形態においては、正相分抽出部82が基本波の逆相分の通過を抑制することで正相分を抽出し、逆相分抽出部83が基本波(正相分)の通過を抑制することで逆相分を抽出する。したがって、α軸電圧信号Vαおよびβ軸電圧信号Vβに高調波成分が含まれていた場合、正相分抽出部82および逆相分抽出部83は、高調波成分も通過させてしまう。高調波成分が含まれている場合に当該高調波成分の通過も抑制することで、基本波の正相分または逆相分をより精度よく抽出する場合を、第3実施形態として、以下に説明する。

【0088】

図12は、第3実施形態に係る正相分抽出部の内部構成を説明するためのブロック図である。

【0089】

図12に示す正相分抽出部82’は、多段に接続された4つの複素係数ノッチフィルタ82a〜82dを備えている点で、第2実施形態に係る正相分抽出部82(図2参照)と異なる。複素係数ノッチフィルタ82aは、第2実施形態に係る正相分抽出部82が備える複素係数ノッチフィルタと同じものであり、基本波の逆相分を抑制するためのものである。複素係数ノッチフィルタ82aの阻止帯域を決定する正規化角周波数Ωdとして、系統電圧の基本波の逆相分の角周波数「−ω0」を正規化した「−ωd」があらかじめ設定されている。複素係数ノッチフィルタ82b〜82dは、それぞれ5次、7次、11次高調波(正相分)を抑制するためのものである。複素係数ノッチフィルタ82b〜82dの阻止帯域を決定する正規化角周波数Ωdとして、それぞれ「−5ωd」、「7ωd」、「−11ωd」があらかじめ設定されている。

【0090】

図13(a)は、正相分抽出部82’の周波数特性を示す図である。同図(a)によると、基本波の逆相分(角周波数「−ω0」)、5次高調波成分(角周波数「−5ω0」)、7次高調波成分(角周波数「7ω0」)、11次高調波成分(角周波数「−11ω0」)が抑制され、その他の成分が通過される。正相分抽出部82’では、複素係数ノッチフィルタ82a〜82dによって、基本波の逆相分だけではなく、5次、7次、11次高調波(正相分)も抑制されるので、基本波の正相分のみをより好適に通過させることができる。

【0091】

一般的に、電力系統Bに重畳されている高調波は、5次、7次、11次高調波が多いので、本実施形態においては、これらを抑制するようにしている。なお、正相分抽出部82’は、抑制する必要がある高調波の次数に応じて設計すればよい。例えば、高調波としては5次高調波のみを抑制したい場合は、複素係数ノッチフィルタ82aおよび82bのみを備えていればよく、さらに13次高調波も抑制したい場合には、阻止帯域を決定する正規化角周波数Ωdとして「13ωd」を設定した複素係数ノッチフィルタをさらに備えるようにすればよい。

【0092】

同様に、第3実施形態に係る逆相分抽出部(図示しないが、説明上、「逆相分抽出部83’」とする。)は、第2実施形態に係る逆相分抽出部83が備える複素係数ノッチフィルタと、それぞれ5次、7次、11次高調波(正相分)を抑制するための複素係数ノッチフィルタ(図12に示す複素係数ノッチフィルタ82b〜82d)とを備えている。

【0093】

図13(b)は、逆相分抽出部83’の周波数特性を示す図である。同図(b)によると、基本波の正相分(角周波数「ω0」)、5次高調波成分(角周波数「−5ω0」)、7次高調波成分(角周波数「7ω0」)、11次高調波成分(角周波数「−11ω0」)が抑制され、その他の成分が通過される。逆相分抽出部83’では、基本波の正相分だけではなく、5次、7次、11次高調波(正相分)も抑制されるので、基本波の逆相分のみをより好適に通過させることができる。

【0094】

第3実施形態は、電力系統Bに高調波が重畳されている場合でも、基本波の正相分または逆相分を精度よく抽出することができる。

【0095】

上記第1ないし第3実施形態においては、正相分抽出部82(82’)および逆相分抽出部83(83’)がどちらも複素係数バンドパスフィルタまたは複素係数ノッチフィルタを用いる場合について説明したが、これに限られない。例えば、正相分抽出部82が複素係数バンドパスフィルタを用いて正相分信号を通過させることで抽出し、逆相分抽出部83(83’)が複素係数ノッチフィルタを用いて正相分信号の通過を抑制することで逆相分信号を抽出するようにしてもよい。また、正相分抽出部82(82’)が複素係数ノッチフィルタを用いて逆相分信号の通過を抑制することで正相分信号を抽出し、逆相分抽出部83が複素係数バンドパスフィルタを用いて逆相分信号を通過させることで抽出するようにしてもよい。

【0096】

上記第1ないし第3実施形態においては、正相分抽出部82(82’)および逆相分抽出部83(83’)で用いられる正規化角周波数Ωdをあらかじめ設定しておく場合について説明したが、これに限られない。信号処理のサンプリング周期が固定サンプリング周期の場合、系統電圧の基本波の角周波数を周波数検出装置などで検出して、検出された角周波数を正規化して用いるようにしてもよい。

【0097】

上記第1ないし第3実施形態においては、基本波の正相分および逆相分のみを抽出して位相の調整を行っているが、高調波成分も位相の調整をするようにしてもよい。すなわち、電力系統Bに含まれる高調波成分が無視できない場合は、当該高調波成分(例えば、5,7,11次高調波成分)を抽出して位相の調整を行った上で、基本波成分に重畳させるようにすればよい。その際、高調波成分の逆相分も無視できない場合は、基本波成分の場合と同様に、正相分の信号と逆相分の信号とをそれぞれ抽出して、それぞれ位相を調整するようにすればよい。

【0098】

上記第1ないし第3実施形態においては、本発明に係る位相調整装置を系統対抗分生成部に用いた場合について説明したが、これに限られない。例えば、電流制御部71(図1参照)に入力される電流信号I(Iu,Iv,Iw)の位相を調整する場合や、電流制御部71から出力される補正値信号Xu,Xv,Xwの位相を調整する場合にも、本発明に係る位相調整装置を用いることができる。

【0099】

上記第1ないし第3実施形態においては、本発明に係る位相調整装置を系統連系インバータシステムに用いた場合について説明したが、これに限られない。本発明に係る位相調整装置は、三相交流に基づく信号を用いるあらゆる装置や構成において、当該信号の位相を調整する場合に用いることができる。例えば、高調波補償装置、電力用アクティブフィルタ、不平衡補償装置、静止型無効電力補償装置(SVC、SVG)、無停電電源装置(UPS)、力率補償装置、周波数変換装置などの三相交流を扱う装置にも、本発明に係る位相調整装置を用いることができる。

【0100】

本発明に係る位相調整装置、系統対抗分生成装置、系統連系インバータシステム、および、位相調整方法は、上述した実施形態に限定されるものではない。本発明に係る位相調整装置、系統対抗分生成装置、系統連系インバータシステム、および、位相調整方法の各部の具体的な構成は、種々に設計変更自在である。

【符号の説明】

【0101】

A 系統連系インバータシステム

1 直流電源

2 インバータ回路

3 フィルタ回路

4 変圧回路

5 電流センサ

6 電圧センサ

7 制御回路

71 電流制御部

72 PWM信号生成部

8 系統対抗分生成部

81 三相/二相変換部

82,82' 正相分抽出部

82a,82b,82c,82d 複素係数ノッチフィルタ

83 逆相分抽出部

84 正相分位相調整部

85 逆相分位相調整部

86 振幅調整部

87 二相/三相変換部

B 電力系統

【特許請求の範囲】

【請求項1】

三相交流に基づく3つの信号の位相を調整する位相調整装置であって、

前記3つの信号を第1の信号および第2の信号に変換する三相二相変換手段と、

前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号とを、それぞれ抽出する正相分抽出手段と、

前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とを、それぞれ抽出する逆相分抽出手段と、

前記正相分抽出手段によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する正相分位相調整手段と、

前記逆相分抽出手段によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する逆相分位相調整手段と、

位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する加算手段と、

前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する二相三相変換手段と、

を備えており、

前記正相分抽出手段および前記逆相分抽出手段は、それぞれ複素係数フィルタを用いて各信号を抽出する、

ことを特徴とする位相調整装置。

【請求項2】

前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域通過型の複素係数フィルタである、請求項1に記載の位相調整装置。

【請求項3】

前記複素係数フィルタのz変換表現による伝達関数H(z)は、通過帯域の正規化中心角周波数をΩd(−π<Ωd<π)、通過帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数1】

である、請求項2に記載の位相調整装置。

【請求項4】

前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域阻止型の複素係数フィルタである、請求項1に記載の位相調整装置。

【請求項5】

前記複素係数フィルタのz変換表現による伝達関数H(z)は、阻止帯域の正規化中心角周波数をΩd(−π<Ωd<π)、阻止帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数2】

である、請求項4に記載の位相調整装置。

【請求項6】

前記正相分抽出手段または前記逆相分抽出手段は、複数の複素係数フィルタを多段に接続したフィルタを用いる、請求項4または5に記載の位相調整装置。

【請求項7】

前記正相分位相調整手段は、前記第1の正相分信号をXα、前記第2の正相分信号をXβ、位相調整量をθ0とすると、位相調整後の第1の正相分信号X’αおよび第2の正相分信号X’βを、下記(1)式に示す行列式によって算出し、

前記逆相分位相調整手段は、前記第1の逆相分信号をYα、前記第2の逆相分信号をYβ、位相調整量をθ0とすると、位相調整後の第1の逆相分信号Y’αおよび第2の逆相分信号Y’βを、下記(2)式に示す行列式によって算出する、

請求項1ないし6のいずれかに記載の位相調整装置。

【数3】

【請求項8】

前記第1の調整後信号および前記第2の調整後信号の振幅を調整する振幅調整手段をさらに備えている、請求項1ないし7のいずれかに記載の位相調整装置。

【請求項9】

請求項1ないし8のいずれかに記載の位相調整装置によって、電圧検出手段により検出された三相電力系統の各相の電圧信号の位相を調整して出力することを特徴とする系統対抗分生成装置。

【請求項10】

請求項9に記載の系統対抗分生成装置から出力される位相調整後の各相の電圧信号に基づいてPWM信号を生成して出力する制御回路と、

前記制御回路から入力されるPWM信号に基づいて、直流電力を交流電力に変換するインバータ回路と、

を備えていることを特徴とする系統連系インバータシステム。

【請求項11】

三相交流に基づく3つの信号の位相を調整する位相調整方法であって、

前記3つの信号を第1の信号および第2の信号に変換する第1の工程と、

前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とをそれぞれ抽出する第2の工程と、

前記第2の工程によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する第3の工程と、

前記第2の工程によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する第4の工程と、

位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する第5の工程と、

前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する第6の工程と、

を備えており、

前記第2の工程は、複素係数フィルタを用いて各信号を抽出する、

ことを特徴とする位相調整方法。

【請求項1】

三相交流に基づく3つの信号の位相を調整する位相調整装置であって、

前記3つの信号を第1の信号および第2の信号に変換する三相二相変換手段と、

前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号とを、それぞれ抽出する正相分抽出手段と、

前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とを、それぞれ抽出する逆相分抽出手段と、

前記正相分抽出手段によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する正相分位相調整手段と、

前記逆相分抽出手段によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する逆相分位相調整手段と、

位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する加算手段と、

前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する二相三相変換手段と、

を備えており、

前記正相分抽出手段および前記逆相分抽出手段は、それぞれ複素係数フィルタを用いて各信号を抽出する、

ことを特徴とする位相調整装置。

【請求項2】

前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域通過型の複素係数フィルタである、請求項1に記載の位相調整装置。

【請求項3】

前記複素係数フィルタのz変換表現による伝達関数H(z)は、通過帯域の正規化中心角周波数をΩd(−π<Ωd<π)、通過帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数1】

である、請求項2に記載の位相調整装置。

【請求項4】

前記正相分抽出手段または前記逆相分抽出手段が用いる複素係数フィルタは、帯域阻止型の複素係数フィルタである、請求項1に記載の位相調整装置。

【請求項5】

前記複素係数フィルタのz変換表現による伝達関数H(z)は、阻止帯域の正規化中心角周波数をΩd(−π<Ωd<π)、阻止帯域の帯域幅を決めるパラメータをr(0<r<1)、虚数単位をj、自然対数の底eの指数関数をexp()とした場合、

【数2】

である、請求項4に記載の位相調整装置。

【請求項6】

前記正相分抽出手段または前記逆相分抽出手段は、複数の複素係数フィルタを多段に接続したフィルタを用いる、請求項4または5に記載の位相調整装置。

【請求項7】

前記正相分位相調整手段は、前記第1の正相分信号をXα、前記第2の正相分信号をXβ、位相調整量をθ0とすると、位相調整後の第1の正相分信号X’αおよび第2の正相分信号X’βを、下記(1)式に示す行列式によって算出し、

前記逆相分位相調整手段は、前記第1の逆相分信号をYα、前記第2の逆相分信号をYβ、位相調整量をθ0とすると、位相調整後の第1の逆相分信号Y’αおよび第2の逆相分信号Y’βを、下記(2)式に示す行列式によって算出する、

請求項1ないし6のいずれかに記載の位相調整装置。

【数3】

【請求項8】

前記第1の調整後信号および前記第2の調整後信号の振幅を調整する振幅調整手段をさらに備えている、請求項1ないし7のいずれかに記載の位相調整装置。

【請求項9】

請求項1ないし8のいずれかに記載の位相調整装置によって、電圧検出手段により検出された三相電力系統の各相の電圧信号の位相を調整して出力することを特徴とする系統対抗分生成装置。

【請求項10】

請求項9に記載の系統対抗分生成装置から出力される位相調整後の各相の電圧信号に基づいてPWM信号を生成して出力する制御回路と、

前記制御回路から入力されるPWM信号に基づいて、直流電力を交流電力に変換するインバータ回路と、

を備えていることを特徴とする系統連系インバータシステム。

【請求項11】

三相交流に基づく3つの信号の位相を調整する位相調整方法であって、

前記3つの信号を第1の信号および第2の信号に変換する第1の工程と、

前記第1の信号に含まれる正相分の信号である第1の正相分信号と、前記第1の信号に含まれる逆相分の信号である第1の逆相分信号と、前記第2の信号に含まれる正相分の信号である第2の正相分信号と、前記第2の信号に含まれる逆相分の信号である第2の逆相分信号とをそれぞれ抽出する第2の工程と、

前記第2の工程によって抽出された前記第1の正相分信号および前記第2の正相分信号の位相を調整する第3の工程と、

前記第2の工程によって抽出された前記第1の逆相分信号および前記第2の逆相分信号の位相を調整する第4の工程と、

位相調整後の第1の正相分信号と位相調整後の第1の逆相分信号とを加算した第1の調整後信号と、位相調整後の第2の正相分信号と位相調整後の第2の逆相分信号とを加算した第2の調整後信号とを、それぞれ生成する第5の工程と、

前記第1の調整後信号および前記第2の調整後信号を3つの調整後信号に変換する第6の工程と、

を備えており、

前記第2の工程は、複素係数フィルタを用いて各信号を抽出する、

ことを特徴とする位相調整方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図6】

【図7】

【図8】

【公開番号】特開2013−85338(P2013−85338A)

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願番号】特願2011−222458(P2011−222458)

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

【公開日】平成25年5月9日(2013.5.9)

【国際特許分類】

【出願日】平成23年10月7日(2011.10.7)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

[ Back to top ]