低インピーダンス損失線路

【課題】数百[kHz]から1[GHz]を超える帯域まで非常に低いインピーダンス値と透過係数値を有する、コンデンサでは実現不可能な理想電源の機能を伝送線路構造で実現する。

【解決手段】

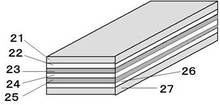

低インピーダンス損失線路は、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔24と、第1の陰極箔21と、第2の陰極箔27と、陽極箔24の両面の誘電体酸化皮膜上に形成される第1の導電性ポリマー層23および第2の導電性ポリマー層25と、第1の導電性ポリマー層23に第1の陰極箔21を貼付するための第1の導電性ポリマーペースト層22と、第2の導電性ポリマー層25に第2の陰極箔27を貼付するための第2の導電性ポリマーペースト層26から形成され、第1の陰極箔21および第2の陰極箔27を電極とする平行板線路を形成している。

【解決手段】

低インピーダンス損失線路は、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔24と、第1の陰極箔21と、第2の陰極箔27と、陽極箔24の両面の誘電体酸化皮膜上に形成される第1の導電性ポリマー層23および第2の導電性ポリマー層25と、第1の導電性ポリマー層23に第1の陰極箔21を貼付するための第1の導電性ポリマーペースト層22と、第2の導電性ポリマー層25に第2の陰極箔27を貼付するための第2の導電性ポリマーペースト層26から形成され、第1の陰極箔21および第2の陰極箔27を電極とする平行板線路を形成している。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、回路または回路部品に関し、特に、高速スイッチング素子を使用する、情報技術装置やディジタルデータ通信機器の直流電源分配回路、並びに高周波DC−DCコンバータ等の電力変換器に使用し、小型軽量化が可能で、変換効率、信号品位(シグナルインテグリティ)、および電磁環境適合性(EMC)を向上させることが出来る低インピーダンス損失線路に関する。

【背景技術】

【0002】

近年、コンピュータを初めとするディジタル回路システムの高性能、小型化の要求が強い。ディジタル回路システムを構成するトランジスタの高速化は、高性能化や小型化に効果があるが、電磁ノイズや消費電力が増えると考えられて来た。

【0003】

IECにおいては、情報技術装置やマルチメディア機器を対象に新たなEMI規格であるCISPR32の制定に向けた作業が進んでいる。ここでは、装置または機器からの放射妨害波について320[MHz]から6[GHz]まで、電源ラインおよび通信線による伝導妨害波について150[kHz]から30[MHz]までが規制の対象となる。許容値は従来の情報技術装置向けのCISPR22と同様であるが、適用対象がディジタル家電を含むマルチメディア機器まで拡大される。

【0004】

一方、半導体技術の先端を進む半導体集積回路においてはトランジスタの高速化が進んでいる。非特許文献1によると、2007年のテクノロジノードにおける高性能MPUのPチャネル型電界効果トランジスタの最小上昇時間(ゲートディレー)は0.64[ps](ピコ秒)であり、電源電圧は1.1[V]である。

【0005】

電磁気学によると、回路の状態には活性状態(exited states)、定常状態(stationary states)および、実用上は定常状態と見なせる準定常状態(quasi

stationary states)が存在する。活性状態とは、回路上の電界と磁界が変化または振動している状態であり交流回路はその一例である。振動する電界と磁界は電磁波となって絶縁体中を進行する。該絶縁体が真空空間の場合は、電磁波は光速で進行する。

【0006】

定常状態とは、回路上の電界と磁界が静止している状態であり直流回路はその一例である。準定常状態とは、電界と磁界が電磁波となって回路上を進行するが、電磁波の波長が回路長に対して非常に長く回路内での電磁波の挙動が強弱振動だけと見なしても通常の界路設計においてほぼ不都合が生じないと見なされる状態である。低周波アナログ回路や、およそ1[ns]以上の立ち上がり時間を有するトランジスタと10[cm]以下の長さの配線で構成される回路は、実用上、準定常状態と見なすことの出来る回路の一例であるとされて来た。

【0007】

電磁気学によると、活性状態にある回路の電流はアンペールの法則として定義され次式で示される。

【0008】

【数1】

【0009】

電磁気学によると、電位Vは、電界の及ばない無限遠から導線の一点までの電界の積分値と定義されるが実用的にはグランド面から導線の一点までの電界の積分値として、また、電界Eは電位Vの傾きとしてそれぞれ次式から求められる。

【0010】

【数2】

【0011】

マックスウエルは、磁界に関する理論と電界に関する理論を融合したマックスウエルの方程式を1873年に発表し、続いてこの式をダランベールの波動方程式の形式に変形し、ベクトル波動方程式を導出した。マックスウエルは、1862年頃から主張していた、電磁波と光はともに光速で伝搬することをこの式を用いて理論的に証明し、線形電磁波理論(以下電磁波理論)を完成させ、これにより電磁気学が完成した。ヘルツは、1887年に、実験によって電磁波の存在を実証し、マックスウエルの電磁波理論の正しさを証明した。

【0012】

電磁気学によると、時間的に変化する電界と磁界は相互に作用しつつ横波となって空間または誘電体中を伝搬する。真空中を伝搬する電磁波の速度は光速である。伝搬する電磁波はポインチングベクトル理論に従って電力を伝搬する。空間を伝搬する電磁波は、周期および極性が一致し振幅ベクトルが進行方向に対して直交する電界波と磁界波とから構成される。この状態の電磁波はTEM(transverse electromagnetic)波と呼ばれる。電磁気学によると、時間的に変化する電界と磁界は相互に作用しつつ横波となって空間または誘電体中を伝搬する。真空中を伝搬する電磁波の速度は光速である。伝搬する電磁波はポインチングベクトル理論に従って電力を伝搬する。空間を伝搬する電磁波は、周期および極性が一致し振幅ベクトルが進行方向に対して直交する電界波と磁界波とから構成される。この状態の電磁波はTEM(transverse electromagnetic)波と呼ばれる。TEM波を構成する電界波の振幅を磁界波の振幅で割った値は波動インピーダンス(surge

impedanceまたはwave impedance)と呼ばれる。

【0013】

電磁気学によると、電磁波は空間だけでなく媒体中も進行する。損失のない誘電体中を進行する電磁波の速度は、光速に対して比誘電率の平方根だけ遅くなり、波長は比誘電率の平方根だけ短くなる。後者は、波長圧縮と呼ばれる。

【0014】

電磁気学によると、損失のある媒体中を進行する電磁波は、次式で示される減衰定数γに従い、進行に伴って振幅が減少し位相が変化する。

【0015】

【数3】

【0016】

式(3)において、γの実数項であるαは減衰定数、γの虚数項であるβは位相定数と呼ばれる。αは、nep/m(ネパー/メートル)の単位で表される。1

[nep/m]は、1メートル進行して振幅がexp-1または0.368倍に減衰することを意味する。

【0017】

電磁気学によると、式(3)中のγ 2を変形して得られる次式の括弧の項は、損失のある誘電体に関する複素誘電率と定義され、虚数部(σ/ε0ω)を実数部(εr)で割った値を誘電体損失の正接と呼び、tanδで表す。但し、tanδは、電磁気学上、深い意味を持たない。

【0018】

【数4】

【0019】

電磁波が導体中を進行する場合は、導体中では電磁波に作用する電荷は存在せず導電率σは ωεに比べて非常に大きいので、γは次式で表される。次式中における減衰定数α の逆数であるδは、表皮厚さと呼ばれる。

【0020】

【数5】

【0021】

電磁気学によると、導体中を進行する電磁波の電界と磁界の比である固有インピーダンスZ0は、損失のある媒体中の固有インピーダンスにおいて導電率σがωεに比べて非常に大きいとして、次式で与えられる。

【0022】

【数6】

【0023】

回路上の電界と磁界が変化または振動している活性状態または準定常状態においては電磁波理論が回路を支配し、この場合は導体中を電磁波が進むことは困難である。しかし回路上の電界と磁界が静止している定常状態においては、導体中を電荷の移動による電流が流れることが出来る。

【0024】

物理学によると、導体中には無尽蔵に近い自由電子すなわち電荷が存在する。直流電源に静的負荷が接続されている場合は導体中の電荷の移動による電流が流れるが、一般に、電荷の移動軸方向にはわずかな電界しか印加されないので、電荷の平均移動速度は極めて遅い。

【0025】

例えば、1平方ミリメートルの断面を有する銅線中を導体中の電荷の速度(dq/dt)で定義される10アンペアの電流が進行しているときの電流の進行速度は、物理学に従って計算すると常温で0.368[mm/s]となる。導体中の電荷は、遅いながらも移動は可能であるので、導体の他端で定常的に電荷が消費される際に導体の一端から同量の電荷が定常的に供給されれば、導体の他端に接続される抵抗器等の定常負荷へのエネルギー供給が支障なく行われる。

【0026】

伝送線路上の電気信号の進行を扱うのが電気通信工学である。電気通信工学によると、直流的に絶縁された2本の導体間に電気信号を与えると、電気信号は電流波と電圧波となって伝送線路を進行するとしている。

【0027】

電気通信工学では、交流回路理論と同様に、電流を導体中の電荷の平均速度(dq/dt)すなわち導体電流としている。しかし、電磁気学の基礎を成すマックスウエルの方程式においては、導体電流は、時間の関数ではない電流密度Jに対応させている。

【0028】

交流回路理論や電気通信工学が電流をdq/dtと定義しているのは以下の理由によると考えられる。交流回路理論を支える重要な法則の一つであるキルヒホッフの法則が発表されたのが1845年で、マックスウエルが電磁波の存在を理論的に証明しヘルツによって実験で電磁波の存在が確認される42年前である。また、電気通信工学を支える重要な理論の一つである電信方程式が開発されたのが1874年で、同様に電磁波の存在が確認される13年前である。従って、交流回路理論および電気通信工学が実用化された当時は、回路の作用を電磁波の作用とする考え方がそもそも存在していなかった。さらに、その後も理論の修正が行われなかった。

【0029】

電気通信工学の基礎を成す電信方程式において、導体電流が光速で流れることが出来るとしている根拠となっているのはダランベールの波動方程式である。ダランベールの波動方程式では、波動の主体をスカラー量のラプラシアンとするベクトル関数で表現し、波動の主体を特定していない。導体電流が導体間電圧とともに波となることが、電気回路を支配する電磁気学と整合していなので、電圧と電流に関する回路方程式をダランベールの波動方程式に対比させて得られる電信方程式は、電磁気学とは無関係であり、また電磁気学に整合していないことになる。

【0030】

電流の定義が電磁気学に整合していないとなると、線路の電圧や、インピーダンス、電磁波との関係、さらには伝送損失に関しても電磁気学と矛盾する事態が生じる可能性がある。電気通信工学にはこのような問題が内在するが、歴史が古く伝送線路設計への豊富な適用実績を背景に、従来通りの連続波を対象とする伝送線路設計では電磁気学との矛盾が顕在化しないよう、工夫が施されている。

【0031】

スイッチング波またはディジタル波のような間欠波を対象とする伝送線路設計においても電気通信工学に基づくと効率的であると言う考え方が支配的である。しかし電気通信工学のディジタル回路への実用実績が少ないため、電磁気学と対比しつつ慎重に設計や解析を行わないと、電磁気学との前記矛盾が顕在化する可能性がある。

【0032】

電磁気学によれば、絶縁された2本の導体で構成される伝送線路に印加された電磁波は、TEMモードとなって準光速で進行する。絶縁が真空であれば進行速度は高速となる。このとき伝送線路で観測される電流や電圧は、それぞれ式(1)および式(2)から求められ、実態は伝送線路の導体ではなくて絶縁体中を進む電界波と磁界波である。電気通信工学によると、伝送線路上のTEM波を構成する電界波の振幅を磁界波の振幅で割った値が、特性インピーダンスである。

【0033】

電磁気学と電気通信工学によると、伝送線路上を進行する信号の挙動は、伝送線路の特性インピーダンスと伝搬定数によって決まる。平板導体や絶縁体の材料特性は、伝送線路の特性インピーダンスに対して実用上ほとんど影響を及ぼさない。

【0034】

電気通信工学によると、直径aの2本の導線の中心間を距離dだけ離して平行に配置した構造の、レッヘル線路の特性インピーダンスは次式から求めることが出来る。

【0035】

【数7】

【0036】

電気通信工学によると、実用的なマイクロストリップ線路ならびに平行板線路の特性インピーダンスは次式から求めることが出来る。

【0037】

【数8】

【0038】

電気通信工学によると、既知の特性インピーダンスZ0を有する伝送線路を通して未知の特性インピーダンスZ1を有する伝送線路に電磁波を注入したときの、

前記二つの伝送線路の接続点における反射係数S11は、次式で表される。

【0039】

【数9】

【0040】

電気通信工学によると、反射係数がS11である、線路間の透過係数S21Γは、次式で表される。

【0041】

【数10】

【0042】

電気通信工学によると減衰定数α1を超える損失線路の透過係数S21αは、次式で表される。

【0043】

【数11】

【0044】

電磁気学によると、実用的な伝送線路の減衰定数は、電磁波が損失のある誘電体内を進行するときの減衰と、電磁波が誘電体内を進行する過程でその一部が導体内に侵入して熱になる導体損と、伝送線路外に漏れ出る放射損との和となると考えることが出来る。

【0045】

高速ディジタルデータ通信機器の配線設計は電気通信工学に従って行われている。しかし、電気通信工学は正弦波等の連続波を扱う伝送線路設計には適するが、前述のようにディジタル信号のような間欠波を扱う伝送線路設計には、電磁気学との矛盾があり適さない。

【0046】

高速ディジタルデータ通信機器や高周波電力変換器おける直流電源は、回路に電荷を供給すると考えられている。

【0047】

電磁気学によると、マックスウエルは、単位(試験)点電荷に働く力の原因は、単位点電荷の存在する場所における電界にあるとし、クーロンの法則を修正した。この事実はあまり知られていない。

【0048】

修正された電磁気学によると、電界に関する静電(electrostatic)エネルギーwEは、次式で表される。

【0049】

【数12】

【0050】

このように、静電エネルギーwEは電荷が持っているのではなくて電界Eと電束密度Dの積または電界Eとして媒質に蓄積していることになる。

【0051】

なお、電圧Vが印加された容量Cのコンデンサに蓄積されている静電エネルギーwCは、電極距離をd、電極面積をSとすると、次式で表される。

【0052】

【数13】

【0053】

電磁気学によると磁界に関する静磁気(magnetostatic)エネルギーwHは磁界と磁束密度の積として媒質に蓄積しているとされ、次式で表される。

【0054】

【数14】

【0055】

電流Iが印加された誘導Lのリアクトルに蓄積されている静磁気エネルギーwLは、リアクトルの磁路長をl 、磁路の断面積をSとすると、次式で表される。

【0056】

【数15】

【0057】

非特許文献4および非特許文献5に示される孤立電磁波コンセプトによると、半導体集積回路内のトランジスタは、スイッチングの瞬間に、非線形波動またはソリトンの一種である孤立電磁波を励起する。ディジタル回路システムを構成する回路モジュール内のトランジスタも同様である。

【0058】

トランジスタのスイッチング動作時の孤立電磁波の励起メカニズムは、1834年にJohn Scott Russell がソリトンを発見する際に行った種々の実験の内の水を貯めた水門(ゲート)を急に開くことによって生じたソリトンの発生メカニズムや、ソリトンの一種であると確認されている津波の生成過程に極めて類似している。

【0059】

前記孤立電磁波コンセプトによると、トランジスタがオフからオンにスイッチングする瞬間に、トランジスタの電位が前記直流電源の電圧を電源線路と信号線路の特性インピーダンス分割した値になる。従って、電源線路には電圧を分割電圧まで下げる極性の孤立電磁波が、信号線路には電圧を分割電圧まで上げる極性の孤立電磁波がそれぞれ同時に励起され、電磁波理論に従い、互いにその振幅ベクトルが直交する孤立電界波と孤立磁界波を伴って伝送線路上を進行する。

【0060】

図1は、インバータに関する電磁波等価回路の一例である。

【0061】

図1において、特性インピーダンスZ0の伝送線路の途中にインバータ1が接続されており、特性インピーダンスZ0の伝送線路5は直流電源4とインバータ1との間に接続されて電源線路を構成し、特性インピーダンスZ0の伝送線路6はインバータ1と整合終端抵抗7との間に接続されて信号線路を構成している。インバータ1は、PチャネルMOS

FET2とNチャネルMOS FET3によるコンプリメンタリー構成である。

【0062】

図1において、インバータ1のオン状態とは、PチャネルMOS FET2がオンでNチャネルMOS FET3がオフの状態であり、インバータ1のオフ状態はその逆である。伝送線路を進行するTEM波に関する磁界と電流の関係および電界と電位の関係は、電磁気学においてそれぞれアンペアの法則および電位の定義として示される。

【0063】

図2は、線路上の電源側の電位波形と電界波形の一例である。図3は、線路上の抵抗側の電位波形と電界波形の一例である。

【0064】

図2は、インバータ1がオン時の伝送線路6上の電位波形9と、電磁気学に示される電位の定義から逆算して求められる伝送線路6上を進む電界波形8とを示す。図3は、インバータ1がオン時の伝送線路5上の電位波形11と、電磁気学に示される電位の定義から逆算して求められる電源側の伝送線路5上を進む電界波形10とを示す。

【0065】

図2および図3に示すように、インバータ1のスイッチングによって生じる電界の波形は、トランジスタの立ち上がり波形の最大傾斜部の接線を立ち上がり波形と見なして求める立ち上がり時間と円周率との積の逆数として求められる周波数で定義される実効周波数(significant frequency)を有する正弦波の半波形に近似している。実効周波数の考え方を引用すると、前記近似の確かさ(accuracy)は、92%以上と見込まれる。従って、設計だけに限ると実用上、実効周波数で行うことが出来る。

【0066】

図1から図3において、インバータ1がオンすると、図1中のB点とC点の電位は等しくE/2[V]となる。インバータ1によって励起された、お互い逆極性を有する伝送線路6上を進む孤立電界波8と伝送線路5上を進む孤立電界波10は、それぞれインバータ1に対して反対方向に進む。伝送線路6上を進む孤立電界波8は、伝送線路6の電位を0[V]からE/2[V]に上昇させつつ進み、整合終端抵抗7に向かう。一方、伝送線路5上を進む孤立電界波10は、伝送線路5の電位をE[V]からE/2[V]に降下させつつ直流電源4に向かって、それぞれ伝送線路を構成する絶縁体中を準光速で進行する。

【0067】

前記孤立電磁波コンセプトによると、伝送線路上を進行する孤立電磁波の波長は次式で定義される。

【0068】

【数16】

【0069】

従来の電源デカップリング回路または回路部品については、下記の特許文献や非特許文献に記載されている。その要点は後述される。

【特許文献1】特開2002−260965(P2002−260965A)

【特許文献2】特開2005−294449(P2005−294499A)

【特許文献3】特開2007−42732(P2007−42732A)

【特許文献4】特開2002−164760(P2002−164760A)

【特許文献5】特開2004−048650(P2004−048650A)

【非特許文献1】Hirokazu Tohya and Noritaka Toya著 「A NovelDesign Methodology of the On - Chip Power Distribution Network Enhancing thePerformance and Suppressing EMI of the SoC」、IEEE International Symposium onCircuits and Systems 2007、 pp. 889-892、 May 2007.

【非特許文献2】遠矢弘和、遠矢紀尚 著 「SoCの性能とEMCを大きく改善するオンチップ電源分配回路の新しい設計法」、電子情報通信学会 信学技報、Vol.107、No.149、 EE2007-20、pp.73-78、2007年7月.

【非特許文献3】Stephan Kirchmeyerand Knud Reuter著 「Scientific importance, propertiesand growing applications of poly(3,4-ethylendioxythiophene)、The Royal Societyof Chemistry、Journal of Materials Chemistry.,2005、pp. 2077-2088、2005.

【発明の開示】

【発明が解決しようとする課題】

【0070】

解決しようとする問題点の第1は、特許文献1に関する。特許文献1は、簡便な製造工程で、良好な特性を有する固体電解コンデンサを得ることができる固体電解コンデンサの製造方法を提供するために、固体電解質層に関する詳細な製法を開示している。しかし、改良の目的がESRの低減であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0071】

解決しようとする問題点の第2は、特許文献2に関する。特許文献2は、静電容量及び耐圧の向上と、小型大容量化を可能とした固体電解コンデンサの製造方法を提供するために、固体電解質層に関する詳細な製法を開示している。しかし、改良の目的が静電容量及び耐圧の向上と、小型大容量化であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0072】

解決しようとする問題点の第3は、特許文献3に関する。特許文献3は、大容量、低ESR、高信頼性である固体電解コンデンサを提供するために、セパレータを含む固体電解質層に関する詳細な製法を開示している。しかし、改良の目的が大容量、低ESR、高信頼性であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0073】

解決しようとする問題点の第4は、特許文献4に関する。特許文献4は、10KHzから1GHz間での帯域で使用する分布定数型ノイズフィルタの形成法を示している。該分布定数型ノイズフィルタの長さは、電子部品から発生する高周波の1/4波長以上の長さとなるように設定するとしているが、たとえば100[MHz]の高調波すなわち正弦波の1/4波長は大気中で75[cm]、この文献で絶縁体として使用している酸化アルミニウムの場合は、比誘電率が約8.5であるので26[cm]となり、通常の電子・電気機器に使用するには長すぎる。また、線路の入力インピーダンス特性は、反射係数(S11)の測定値または同等の電磁界シミュレーション値から求めるべきところを透過係数(S21)から求める理論的な誤りを犯しているのでデータの信頼性が無い。従って、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。さらに極性を有しているため使用に際して注意が必要であった。

【0074】

解決しようとする問題点の第5は、特許文献5に関する。特許文献7は、高速化、高周波数化に適した平行平板線路型素子を提供するために、電極の構造を詳細に示しているが、使用する材料の物理定数や固体電解質層に関する製法が示されていない。従って期待する透過係数(S21)の特性の裏付けが無い。開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0075】

非特許文献1および非特許文献2は本特許の理論的な根拠を成す重要文献であるがすでに詳述した。非特許文献3も本特許の理論的な根拠の一つである。非特許文献3は、ナノサイズの粒子にしたポリ(3,4−エチレンジオキシチオフェン)とポリスチレン・スルホン酸の錯体の例が示されている。このように薬品メーカからナノサイズの固体電解質材料が供給されれば、これを使用する部品メーカ等での化学重合反応工程が不要になる。非特許文献3のような化学メーカの努力により、100 [S/m]以上の導電率を有するナノサイズの固体電解質材料の商品化は間近となっている。

【0076】

電磁気学の定義に従うと、ディジタル信号処理回路の多くは準定常回路に該当すると考えられ、設計には交流回路理論が使用されている。準定常状態の回路は電磁波理論が支配しているが、回路を定常と見なして設計や解析しても実用上の誤差が少ないということを意味する。ディジタル信号処理回路のトランジスタのスイッチング速度が向上すると電磁ノイズが増加し、その対策は非常に難しいとされている。スイッチング周波数が高くなると小型軽量化が計られることはよく知られているが、電磁ノイズの増加が、ディジタル回路システムの高周波化を妨げている大きな要因の一つとなっている。

【0077】

定常回路を扱う交流回路理論では、電磁波である電磁ノイズの対策は不可能であることは自明である。従って、トランジスタの高速化に伴って発生する電磁ノイズ問題を解決するためには、ディジタル回路システムを構成する配線の設計において、配線の長さにかかわらず電磁波理論を適用する必要があることになる。

【0078】

電気・電子回路には、多くのコンデンサが使用されている。コンデンサは、1875年にドイツ人のクライスト(Ewald George von Kleist)

によって発明された後、原理的な変更がなされないままで電気電子機器に使用されてきた化石のような存在であるが、最近のディジタル化に伴って機器での使用数が増加し続けている。例えばPCのマザーボードにおいては、600個から1000個またはそれ以上のコンデンサが使用され、半導体集積回路パッケージやチップ上にも多くのコンデンサが搭載または形成されており、使用数は増える傾向にある。

【0079】

一般に、コンデンサの機能は、交流回路理論に従って電荷の蓄積とされている。また、直流電源は交流回路に電荷を供給すると考えられている。特に半導体メーカは、コンデンサからの電荷の供給が半導体集積回路の安定動作に必須であると考えている。従って、コンデンサは、電荷蓄積または放出性能を高めるために、おおむね絶縁体に対向する電極の形状は正方形または円形であって、対向する電極の全面または中心部に一対の回路接続用端子が備えられている。

【0080】

一方で、電気・電子回路に使用されているコンデンサの多くは、ディジタル信号処理回路が発生する電磁ノイズを電源分配回路でデカップリング(減結合)するためにも使用されている。以上の理由から、ディジタル回路システムにおいては、コンデンサのほとんどが電源分配回路に搭載され、回路に並列に接続されている。

【0081】

ところで、コンデンサの機能を電荷の蓄積とする考え方は、前述のようにマックスウエルによって否定され、完成された電磁気学においては、コンデンサの機能は電束密度または電界の蓄積と修正されている。従って、交流回路理論を学んだ回路設計技術者が信じる、コンデンサからの電荷の供給が半導体集積回路の安定動作に必須であるという考え方は、全くの誤りであることが判る。

【0082】

次に、コンデンサに期待されているデカップリング効果について検証を試みる。ここで言うデカップリング効果とは高域の電磁ノイズを遮断し電源供給に必要な直流または低周波域を透過させる効果であるので、デカップリングをロウパスフィルタリングと言うことが出来る。すなわち、コンデンサを回路に並列に接続すると、周波数が高くなるにつれてコンデンサのインピーダンスが小さくなるので、キルヒホッフの法則に従い、並列コンデンサを挟む閉回路間の独立性が高まるが、低周波ではコンデンサの作用は無視できるほどになり、並列コンデンサを挟む閉回路間の一体性が高まる。

【0083】

電気通信工学によると、線路に並列に接続されたときのコンデンサのインピーダンスは、測定系がZ0の特性インピーダンスを有するネットワークアナライザでS21を測定することによって次式から求められるとされている。

【0084】

【数17】

【0085】

これは、コンデンサを線路に並列に接続する場合は、式(11)における線路長zがゼロとなり、透過係数S21と反射係数S11が比例関係となるためである。なお、測定されるS21の値は周波数が高くなると1よりかなり小さくなる。またZ0は通常50[Ω]である。この場合は、式(17)は簡略化できて、ZC=25S21となる。

【0086】

式(17)にS21の測定値を代入することによって、市販されているコンデンサのインピーダンスの周波数特性を求めるとV字型の特性曲線となる。すなわち、セラミックコンデンサ等の比較的静電容量が小さいコンデンサにおいては、直列共振点と呼ばれるインピーダンスが最小となる周波数までは周波数に比例してインピーダンス値が減少し、直列共振周波数以上ではインピーダンスが周波数に比例して増加する特性となる。

【0087】

このような特性になる理由は、従来、コンデンサにはリード線、端子、および電極があり、この部分を流れる電流は導体電流であるのでこの部分が等価直列インダクタンス(ESL)として作用し、周波数が高くなるほど電流が流れにくくなるためであるとされている。さらに前記直列共振点のインピーダンスは誘電体損失やリード線、端子、および電極の抵抗等で構成される等価直列抵抗(ESR)によって決まると考えられている。

【0088】

しかし、デカップリングコンデンサの周波数特性についての上記解釈は、電磁気学に照らすと誤りであることが判る。すなわち、デカップリングコンデンサは電磁波の回路と定義されている交流回路での使用が想定されているにもかかわらず、デカップリングコンデンサの周波数特性についての上記解釈は、主に静電磁界における電磁気学の理論に基づいているし、オームの法則は電磁気学とは関係無い。

【0089】

デカップリングコンデンサは電磁波の回路と定義されている交流回路での使用が想定されているのであれば、回路または線路におけるインピーダンスは、電磁波の進行を想定した特性インピーダンスで無ければならない。しかし、コンデンサは線路から見たときの長さがゼロであるので、コンデンサ部の電磁波はTEMモードでは無い。従って、コンデンサの特性インピーダンスは理論上存在しないことになる。

【0090】

長年続けられてきたコンデンサに対する、直列共振点と呼ばれるインピーダンスが最小となる周波数以上におけるインピーダンス特性を改善するための各種改良は、以上から、そのほとんどが的を射ないものであったと考えることが出来る。すなわち、ESLを小さくするためにサイズを出来るだけ小さくする。リード線、端子、および電極には導電性の高い材料を使用する。誘電体損を出来るだけ小さくする等である。最近、等価直列抵抗(ESR)が小さすぎるとQファクタが大きくなりかえって電磁ノイズが増えることがあるという理由で、リード線、端子、および電極には導電性が比較的低い材料を使用し誘電体損をやや大きくしたコンデンサも現れているが、デカップリング機能向上の観点からは、これも的を射ない方法と位置づけられる。

【0091】

さらに、コンデンサの使用法についても誤りがある。コンデンサを多数並列に接続することによって回路のインピーダンスが低くなると言う考え方があり、広く信じられている。この考え方はキルヒホッフの法則が成り立つ場合に有効であるが、キルヒホッフの法則が成り立たない数メガヘルツ以上では無効である。数メガヘルツ以上の信号を扱う電磁波の進行を想定すべき回路において、回路インピーダンスを低くする方法は、伝送線路の特性インピーダンスを低くする以外に無い。

【0092】

コンデンサは、線路長がゼロであるので、線路に多数のコンデンサを並列に接続しても、線路の特性インピーダンスを低くすることは出来ない。しかし、伝送線路の特性インピーダンスと透過係数は独立であるので、電磁波の透過を減らすことは出来る。コンデンサの場合は、線路長がゼロすなわち線路ではないために、インピーダンスと透過係数が比例関係にあったのであるが、このこのような考え方で求められるインピーダンスは、数メガヘルツ以上の信号を扱うデカップリング回路においては意味のない指標である。

【0093】

従って、コンデンサの前記V字型のインピーダンス特性は、デカップリング機能の周波数上限を示すためのものであると考えるのが正しい。すなわち、コンデンサの並列使用は、たとえば非特許文献2に従って、電束密度または電界の蓄積の機能に期待して、集中要素モデルが採用できる低周波領域に限る必要があるということになる。これは、電源分配回路のデカップリングに適する部品が、現在において存在しないことを意味する。このことが、電磁ノイズ問題に改善の兆しが見られない最大の理由の一つであることは容易に推定できる。

【0094】

アナログ回路は、回路状態の変化が比較的緩やかで始まりと終わりが明確でないことが多い。従って、特に低周波アナログ回路の設計においては、マックスウエルが確立した電磁波理論の代わりに、定常状態の回路を扱う交流回路理論を適用しても、実用上、問題が生じることはほとんど無かった。

【0095】

一方、クロック回路やディジタル信号処理回路は、アナログ回路と異なり、状態の変化の期間が短く変化の始まりと終わりは明確である。ディジタル信号処理回路の状態の変化は非常に急激であり、急激な電界または磁界の変化は、電磁気学に従い大きなレベルの電磁波を励起する。ディジタル信号処理回路における電界または磁界の変化は一般に間歇的である。さらに、周波数制御型のディジタル信号処理回路においては、スイッチングの周期は不定である。

【0096】

以上のようにアナログ回路とディジタル信号処理回路は、電磁気学の観点からは大きく異なっている。しかし、クロック回路やディジタル信号処理回路で構成される半導体集積回路の設計や解析には、従来からアナログ回路と同様、交流回路理論が使用されて来た。この原因の一つは、スイッチング波がひずみ波の一種とみなされて来たことに因る。

【0097】

フーリエ変換法によると、ひずみ波は正弦波である多数の高調波から構成されているとされる。これらの高調波は始まりと終わりが無い多数の正弦波である。そうであるとすれば、回路上の信号を高調波毎に解析してその結果を加算すれば、クロック回路やディジタル信号処理回路の解析が可能となる。このように、フーリエ変換法は、クロック回路やディジタル信号処理回路の設計や解析に従来のアナログ回路に関する手法が適用出来るという、利便性の高い道を開いている。

【0098】

フーリエ変換法(Fourier transform)と呼ばれ、1812年に提出されアカデミー大賞を受賞した「熱の解析的理論」の中でフランス人のJoseph

Fourierによって最初に使用された。

フーリエ変換法は数学の一手法であり、汎用性はあるが、上位理論である電磁気学との整合性を確認した上で電気電子回路の設計や解析に採用されている訳ではない。

【0099】

従って、クロック回路やディジタル信号処理回路の設計や解析にフーリエ変換法を適用しているのは、前述の電気通信工学においてダランベールの波動方程式のみに依存して導体電流と導体間電圧が光速でと進行するとしているのと同様、物理学の観点からは誤用と考えるべきである。

【0100】

スイッチング波形をひずみ波として扱うと、損失を有する損失線路をスイッチング波が進行した場合に、観測結果と解析結果との間で齟齬が生じる。たとえばデューティが1/10で繰り返し周波数が1[GHz]のスイッチング波をフーリエ変換すると振幅の1/10の値の直流成分と1[GHz]を基本波とする高調波とに分解できる。直流電流はほとんど流さないCMOS回路を使用する半導体集積回路内のある長さの配線または伝送線路が、1[GHz]の振幅を1/2に低下させる損失を有しているとすると、配線または伝送線路の終端でのスイッチング波の振幅は、解析結果ではほぼ1/2以下に低下する。

【0101】

しかし、電磁気学に従うと、スイッチング波の定常振幅は直流電源から供給される静電エネルギーによって維持される。静電エネルギーは波動エネルギーではないので配線または伝送線路の損失の作用は受けない。従って、伝送線路の終端で観測されるスイッチング波の振幅は減衰しないはずである。

【0102】

この事実は、スイッチング波をひずみ波として扱うことが誤りであることを示している。また、この事実は、フーリエ変換法に基づいて生じる群速度の概念に従う、ディジタル信号配線における信号品位(シグナルインテグリティ)に関する従来の理論には修正が必要であることを意味する。すなわち、この事実は、クロック回路やディジタル信号処理回路の技術の今後の発展のためには、従来の回路理論に代わる理論が必要であることを示唆している。

【0103】

ディジタル信号処理回路を誤り無く高い性能で動作させるためには、ディジタル信号処理回路に直流電源を分配する電源分配回路での充分なデカップリングが必要である。前記電源分配回路でのデカップリングが不充分であると、ディジタル信号処理回路の設計や解析において、ディジタル信号処理回路内だけでなくディジタル回路システム内、さらにはディジタル回路システムの外部の電源分配回路もやバッテリ、商用電源ネットワークまでを想定することも必要となる。これでは、設計や解析が事実上不可能になってしまう。

【0104】

しかし、従来のようにスイッチング波形を歪み波として扱うと、ディジタル回路システム内の多くのトランジスタに接続されている前記電源分配回路にはトランジスタの数の歪み波が関係し、それぞれの歪み波には膨大な数の高調波が含まれていることになる。このような状態にある前記電源分配回路のデカップリング回路の設計や解析を行うことは、高性能コンピュータを用いても不可能である。

【0105】

本発明は、上記問題を根本的に解決する手段を提供することを目的の一つとしている。

【課題を解決するための手段】

【0106】

上記課題を解決するため、請求項1記載の発明は、低インピーダンス損失線路に係り、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔と、第1の陰極箔と、第2の陰極箔と、前記陽極箔の両面の誘電体酸化皮膜上に形成される導電性ポリマー層と、前記導電性ポリマー層に前記第1の陰極箔、および前記第2の陰極箔を貼付するための導電性ポリマーペースト層から形成され、前記第1の陰極箔および前記第2の陰極箔を電極とする平行板伝送線路構造であることを特徴としている。

【0107】

また、請求項2記載の発明は、低インピーダンス損失線路に係り、請求項1記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、少なくとも10[MHz]から10[GHz]の帯域において、前記電源線路を除くスイッチング信号が進行する全ての線路の特性インピーダンスに対して1/100以下または0.5[Ω] 以下の特性インピーダンスと、10[nep/m](ネパー/メートル)以上の減衰定数を有することを特徴としている。

【0108】

また、請求項3記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項2記載の低インピーダンス損失線路において、前記導電性ポリマー層が、100[S/m]以上の導電率を有し、前記導電性ポリマーペースト層が、10[S/m]以上の導電率を有することを特徴としている。

【0109】

また、請求項4記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項3記載の低インピーダンス損失線路において、前記弁作用金属が、アルミニウム、タンタル、ニオブ、チタン、ジルコニウム、またはそれらの合金であることを特徴している。

【0110】

また、請求項5記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項4記載の低インピーダンス損失線路において、前記導電性ポリマー層が、導電性モノマーを溶解した酸化剤の水溶液中に前記陽極箔を浸漬することによって形成されることを特徴としている。

【0111】

また、請求項6記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項5記載の低インピーダンス損失線路において、前記導電性ポリマー層が、前記陽極箔をナノサイズの粒子からなる導電性ポリマーを溶解したエタノールまたはブタノール溶液中に浸漬することによって形成されることを特徴としている。

【0112】

また、請求項7記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項6記載の低インピーダンス損失線路において、前記モノマーが、3,4−エチレンジオキシチオフェン、ピロール、フラン、多環状スルフィド、またはそれらの置換誘導体であることを特徴としている。

【0113】

また、請求項8記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項7記載の低インピーダンス損失線路において、前記酸化剤が、ブタノールまたはエタノールに溶解したパラトルエンスルホン酸第二鉄、エチレングリコールに溶解したパラトルエンスルホン酸第二鉄、過ヨウ素酸、またはヨウ素酸であることを特徴としている。

【0114】

また、請求項9記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項8記載の低インピーダンス損失線路において、前記酸化剤の溶液が、アエロジルを添加して40〜180

[mpa.s]の粘度と、0.5 [wt %]から5.0 [wt %]の範囲の水分含有率を有していることを特徴としている。

【0115】

また、請求項10記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項9記載の低インピーダンス損失線路において、前記導電性ポリマー層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)または、前記いずれかの一つ以上を含む錯体で形成されることを特徴としている。

【0116】

また、請求項11記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項10記載の低インピーダンス損失線路において、前記導電性ポリマーペースト層が、バインダー機能を有するポリチオフェンペーストまたはポリピロールペーストであることを特徴としている。

【0117】

また、請求項12記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項11記載の低インピーダンス損失線路において、前記第1の導電性ポリマーペースト層および前記第2の導電性ポリマーペースト層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはカーボングラファイト、または二酸化マンガン、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)、またはシリコン、またはゲルマニウム、またはシリコンゲルマニウム合金のいずれか1つ以上を重量比で50%以上含み、ポリエチレン、エポキシ樹脂、フェノール樹脂のいずれかのバインダーに混合されて形成されることを特徴としている。

【0118】

また、請求項13記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項12記載の低インピーダンス損失線路において、前記誘電体酸化皮膜が、前記電解質の形成工程の前、後、または前後に、化成液に5分から120分間浸漬して化成または修復化成されることを特徴としている。

【0119】

また、請求項14記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項13記載の低インピーダンス損失線路において、前記化成液が、リン酸二水素アンモニウム、リン酸水素二アンモニウム等のリン酸系の化成液、ホウ酸アンモニウム等のホウ酸系の化成液、アジピン酸アンモニウム等のアジピン酸系の化成液であることを特徴としている。

【0120】

また、請求項15記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項14記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、スイッチング素子またはスイッチング回路ブロックと信号線路と電源線路から構成されるスイッチング回路システムの電源線路の全て、または前記電源線路の前記スイッチング素子またはスイッチング回路ブロックの近傍の一部に使用され、前記第1の陰極箔が前記電源線路を構成する非グランド導体に対して直列に挿入され、前記第2の陰極箔が前記漸減線路を構成するグランド導体に対して並列に接続されて使用されることを特徴としている。

【発明の効果】

【0121】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、スイッチング素子によって励起される電磁波の漏洩が大幅に抑圧されるために、スイッチング素子が使用されている機器の電磁環境適合性(EMC)を大幅に向上させることが可能となる。

【0122】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、スイッチング素子によって励起される電磁波の漏洩が大幅に抑圧されるために、アナログ回路とディジタル回路の混在設計が容易になる。

【0123】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、高速スイッチング素子を使用する情報技術装置、ディジタルデータ通信機器、並びに高周波DC−DCコンバータの直流電源分配回路に使用し、小型軽量化、低コスト化、高変換効率化、高信号品位(シグナルインテグリティ)化、および高電磁環境適合性(EMC)化を両立させることが可能となる。

【発明を実施するための最良の形態】

【0124】

以下、本発明に係る 最良の実施形態について、図面を参照して詳細に説明する。

【0125】

(実施の形態1)

図4は、試作した低インピーダンス損失線路の構造の一例である。図5は、試作した低インピーダンス損失線路のS21特性の一例である。図6は、試作した低インピーダンス損失線路部品の構造の一例である。図7は、試作した低インピーダンス損失線路部品のS21特性の一例である。本実施例における低インピーダンス損失線路および低インピーダンス損失線路部品はいずれも公知である。

【0126】

図6において、本実施例の低インピーダンス損失線路部品は2個の陽極端子18と4個の陰極端子19を有している。低インピーダンス損失線路は銀ペースト層12、陽極箔13、絶縁層14、固体電解質層15、およびカーボンペースト層16で構成されており、全体が気密封止樹脂17で覆われている。図6の右側の1個の陽極端子18および2個の陰極端子19が、陽極箔13および銀ペースト層12の一端にそれぞれ接続され、図6の左側の1個の陽極端子18および2個の陰極端子19が、陽極箔13および銀ペースト層12損失線路の他端にそれぞれ接続されている。

【0127】

図4において、本実施例の低インピーダンス損失線路は、線路部の幅が1[mm]で実効長さが4[mm] 、8[mm] 、16[mm]、および24[mm]を有するエッチング処理が施されたアルミニウム薄膜が陽極箔13として使用されている。アルミニウム薄膜のエッチング部に化成処理によって形成された約15[nm]の前後厚さの酸化アルミニウム被膜が絶縁層14に相当している。アルミニウム薄膜のエッチング部分に化学重合によって付着させたポリピロールが固体電解質層15に相当し、厚さは約2.5[μm]である。カーボンペーストがポリピロールの上に約30[μm]の厚さに塗布され、その上に熱硬化性銀ペーストによって銀ペースト層12が形成されている。

【0128】

電磁界シミュレーション結果によると、本実施例の低インピーダンス損失線路の特性インピーダンスは20−30[mΩ]と推定されている。これは、低インピーダンス損失線路を構成する絶縁体5のみをTEM波が進行する場合に比べて3桁ほど大きい値である。TEM波の一部は絶縁体5から固有インピーダンスで決まる比率で半導体9に進入する。半導体中に進入する電磁波は急速に減衰する。

【0129】

半導体として使用するポリピロールの導電率を3500[S/m]、絶縁体である酸化アルミニウムの厚さを15[nm]、比誘電率を8.5、ポリピロールの塗布厚さを2.5[μm]、比誘電率を1とし、酸化アルミニウムの比誘電率を8.5とする。低インピーダンス損失線路の幅は1[mm]、導体の厚さは100[μm]である。試作結果から、低インピーダンス損失線路の1mm2当たりの静電容量は0.7[μF]である。

【0130】

低インピーダンス損失線路の特性インピーダンスは、ポリピロールの塗布厚さまでTEM波が侵入していると考えると式(8)から32[mΩ]となる。この値は、伝送線路中のポインチングベクトルから求めた電磁界シミュレーション値とほぼ一致する。この値を特性インピーダンスとすれば、50Ωの線路にこの特性インピーダンスを有する低インピーダンス損失線路を接続したときの接続部の透過係数S21αは、式(11)から0.051すなわち−26dBとなる。

【0131】

低インピーダンス損失線路を構成する酸化アルミニウムとポリピロールをTEM波が進行しているときのポリピロールへの透過係数S21Γは、式(10)のZ1に式(6)から得られるポリピロールの固有インピーダンス、Z0に低インピーダンス損失線路の特性インピーダンス値を代入することによって求められる。

【0132】

低インピーダンス損失線路を構成する酸化アルミニウムとポリピロールをTEM波が進行しているときの透過係数S21αは、式(5)から得られるポリピロールの減衰定数にポリピロールへの透過係数を掛けた値をαとして、式(11)に代入すると、低インピーダンス損失線路の長さz毎に求めることが出来る。

【0133】

低インピーダンス損失線路の低周波帯域の特性である静電容量値による50[Ω]の測定系の透過係数S21Cは、式(17)を変形して、次式から求められる。

【0134】

【数18】

【0135】

式(18)において、ZCは、静電容量の交流インピーダンス値に、電極の導電率、ここでは半導体であるポリピロールの導電率に従う低周波でのESR値を加えた値と考えることが出来る。ESRは、次式から求められる。

【0136】

【数19】

【0137】

概略の低インピーダンス損失線路の透過係数S21Aは、次式から求めることが出来る。

【0138】

【数20】

【0139】

式(20)から求められる本実施例の低インピーダンス損失線路の透過係数S21Aは、以下の通りであり、測定結果に近い値となっている。

【0140】

線路長が4[mm]の場合:100[kHz] で−37[dB]、1[MHz]で−53[dB]、10

[MHz]で−73[dB]、100[MHz]で−91[dB]、1[GHz]で−101 [dB]。線路長が8[mm]の場合:100[kHz] で−41[dB]、1[MHz]で−59[dB]、10

[MHz]で−79[dB]、100[MHz]で−97[dB]、1[GHz]で−116 [dB]。線路長が16[mm]の場合:100[kHz] で−46[dB]、1[MHz]で−66

[dB]、10 [MHz]で−86[dB]、100[MHz]で−119[dB]、1[GHz]で−200 [dB]、線路長が24[mm]の場合:100[kHz]

で−50[dB]、1[MHz]で−69[dB]、10 [MHz]で−96[dB]、100[MHz]で−164[dB]、1[GHz]で−287[dB] 。

【0141】

低インピーダンス損失線路部品は低インピーダンス損失線路の両端にボード搭載用の端子が備えられている。このために、高周波帯域で端子間に電磁波のバイパスが形成されて透過係数が劣化する。この電磁波のバイパスは、静電容量を流れる変位電流または電束電流によると考えることが出来る。本実施例の低インピーダンス損失線路部品の実測値から端子間距離1[m]当たりのバイパス容量を求めると5×10−17[F/m]となる。

【0142】

端子間の静電容量のインピーダンスをZTとすると、直列に接続されている静電容量の透過係数S21Tは、次式から求めることが出来る。

【0143】

【数21】

【0144】

概略の低インピーダンス損失線路部品の透過係数S21Bは、次式から求めることが出来る。

【0145】

【数22】

【0146】

式(22)から求められる本実施例の低インピーダンス損失線路部品の透過係数S21Bは、以下の通りであり、測定結果に近い値となっている。

【0147】

線路長が4[mm]の場合:100[kHz] で−37[dB]、1[MHz]で−53[dB]、10 [MHz]で−70[dB]、100[MHz]で−62[dB]、1[GHz]で−42

[dB]。線路長が8[mm]の場合:100[kHz] で−41[dB]、1[MHz]で−59[dB]、10 [MHz]で−76[dB]、100[MHz]で−68[dB]、1[GHz]で−48

[dB]。線路長が16[mm]の場合:100[kHz] で−46[dB]、1[MHz]で−65[dB]、10 [MHz]で−83[dB]、100[MHz]で−74[dB]、1[GHz]で−54

[dB]、線路長が24[mm]の場合:100[kHz] で−50[dB]、1[MHz]で−69[dB]、10 [MHz]で−91[dB]、100[MHz]で−78[dB]、1[GHz]で−58[dB]

。

【0148】

以上の計算結果は、図5、図7と同様に、10[MHz] 以下では低インピーダンス損失線路と低インピーダンス損失線路部品の透過特性の差はほとんど無く、10[MHz]を超えると、低インピーダンス損失線路部品では端子間のバイパスによる透過特性の劣化現象が見られ、劣化度は端子間の距離にほぼ比例している。以上から、上記計算式は実用的であると判断できる。

【0149】

(実施の形態2)

図8は、低インピーダンス損失線路の一例である。

【0150】

図8において、低インピーダンス損失線路は、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔24と、第1の陰極箔21と、第2の陰極箔27と、陽極箔24の両面の誘電体酸化皮膜上に形成される第1の導電性ポリマー層23および第2の導電性ポリマー層25と、第1の導電性ポリマー層23に第1の陰極箔21を貼付するための第1の導電性ポリマーペースト層22と、第2の導電性ポリマー層25に第2の陰極箔27を貼付するための第2の導電性ポリマーペースト層26から形成され、第1の陰極箔21および第2の陰極箔27を電極とする平行板線路を形成している。

【0151】

図8において、低インピーダンス損失線路は整流作用を有している。従って、陰極箔27にグランド線またはグランド板が接続され陰極箔21に正の電圧を有する電源線が接続された場合は陽極箔24と陰極箔27で構成される線路が機能を発揮し、陽極箔24と陰極箔21で構成される線路は短絡に近い状態となり機能しない。一方、陰極箔21にグランド線またはグランド板が接続され陰極箔27に正の電圧を有する電源線が接続された場合は陽極箔24と陰極箔21で構成される線路が機能を発揮し、陽極箔24と陰極箔27で構成される線路は短絡に近い状態となり機能しない。

【0152】

図8において、低インピーダンス損失線路の幅を1[mm]、長さを12[mm]、導電性ポリマーおよび導電性ポリマーペーストの導電率を1000[S/m]、導電性ポリマーペーストの塗布厚さを20[μm]とする。陽極箔をアルミニウムとして、誘電体酸化皮膜であるアルミナの比誘電率を8.5、厚さ30[nm]とし、陽極箔のエッチングによる面積拡大率を実施の形態1の場合の3割減の153とする。低インピーダンス損失線路の端子間のバイパス容量を10−18[F/m]とする。このときの1mm2当たりのESRは、式(19)から1.7[mΩ]となる。

【0153】

本実施の形態における低インピーダンス損失線路の特性インピーダンスは、実施の形態1に従い、30[mΩ]と推定される。また、透過係数S21Bは、以下のように推定される。

【0154】

線路長が3[mm]の場合:100[kHz]で−34[dB]、1[MHz]で−49[dB]、10 [MHz]で−64[dB]、100[MHz]で−70[dB]、230[MHz]で−71[dB]、1[GHz]で−67

[dB]。線路長が6[mm]の場合:100[kHz]で−38 [dB]、1[MHz]で−55[dB]、10 [MHz]で−70[dB]、100[MHz]で−76[dB]、230[MHz]で−76[dB]、1[GHz]で−73

[dB]。線路長が12[mm]の場合:100[kHz]で−43[dB]、1[MHz]で−61[dB]、10 [MHz]で−76[dB]、100[MHz]で−82[dB]、230[MHz]で−82[dB]、1[GHz]で−80

[dB]、線路長が24[mm]の場合:100[kHz]で−48[dB]、1[MHz]で−67[dB]、10 [MHz]で−82[dB]、100[MHz]で−91[dB]、230[MHz]で−95[dB]、1[GHz]で−92[dB]

。

【0155】

(実施の形態3)

図9は、低インピーダンス損失線路を使用するディジタル基本回路の等価回路の一例である。

【0156】

図9において、低インピーダンス損失線を使用するディジタル基本回路の等価回路は、直流電源31、インバータ35および40、インバータル35を構成するPチャネルMOS FET36およびNチャネルMOS FET37、オンチップインターコネクト上の電源線路34およびボード上の電源線路33、低インピーダンス損失線路32、信号線路38、ならびに整合終端抵抗39から構成されている。

【0157】

図9において、電源線路34と信号線路38の特性インピーダンスが150[Ω]、電源線路33の特性インピーダンスが50[Ω]、低インピーダンス損失線路32の特性インピーダンスが実施の形態3で設計した値の30[mΩ]と仮定する。インバータ35のオン状態とオフ状態の定義は前述と同様であり、伝送線路上の電界と伝送線路の電位との関係は電磁気学に従う。

【0158】

インバータ35がオフからオンに変化する時の信号線路38の電位波形と、信号線路6上を進む孤立電界波形、並びに電源線路33、34の電位波形と電源線路33、34上を進む孤立電界波形は、前述と同様である。従って、図9の回路の動作説明には図2と図3の波形を使用する。

【0159】

図9において、インバータ35がオフからオンに変化したときの孤立電界波の伝送線路上の進行の様子と伝送線路の電位変化は図2、図3で説明した通りである。

【0160】

図9において、電源線路34上を進行する孤立電磁波は電源線路33との接続部で一部が反射し、低インピーダンス損失線路32との接続部ではほぼ全てが、信号線路38上に励起された孤立電磁波と同極性で反射し、電源線路33、34および信号線路38の電位をE/2[V]からほぼE[V]に上昇させつつ進行し、整合終端抵抗39で消滅する。

【0161】

電源線路13の長さが孤立電磁波の波長に対して充分短ければ、インバータ35がオンした後のD点の電位は、電源線路5上を孤立電磁波が進行するときの遅延時間だけ上昇時間が長くなることを除けば、通信を行うのにほぼ充分な値となる。

【0162】

図9において、低インピーダンス損失線路32の特性インピーダンスは30[mΩ]と、通信を行うのにほぼ充分な値であるが、電源線路33、34を進行する孤立電磁波の一部が低インピーダンス損失線路32に侵入する。

【0163】

放射電力Pを有する線形電磁波がアンテナから放射されたときのr[m]の距離での電界強度Eは、IEC CISPR16−2−3に示されている次式から求めることが出来る。

【0164】

【数23】

【0165】

例えば家庭内使用を目的とするクラスB情報技術装置から10[m]の距離での妨害波電界強度の許容値は、VCCI(CISPR22)で決められており、30[MHz]から230[MHz]で30[dBμV/m]、230[MHz]から1[GHz]で37[dBμV/m]である。式(23)から、例えば230[MHz]での許容放射電力値を求めると、2[nW]となる。

【0166】

実施の形態3で設計した低インピーダンス損失線路を使用し、図9のインバータ35の代わりに20個の電源端子が設けられており100[W]の消費電力を有する半導体集積回路を想定すると、1個の電源端子で5[W]の電力を分担していることになる。

【0167】

次に、導体集積回路の2個の電源端子毎に、実施の形態2で設計した12[mm]の長さの低インピーダンス損失線路が使用されている場合について、電源ポートから漏洩する不要電磁波の放射電力量を試算する。

【0168】

図9において、インバータ35によって励起された孤立電界波8が信号線路38の電位を0[V]からE/2 [V]まで上昇させるエネルギーと、電源線路34に向かう孤立電界波が電源線路の電位をE[V]からE/2 [V] まで降下させるエネルギーの比は、1:3である。従って電源線路34上の電力は7.5[W]となる。電源線路34から電源線路33への電力透過率は0.87となるので、電源線路33を透過する電力は6.5[W]となる。

【0169】

低インピーダンス損失線路32に、実施の形態2で設計した6[mm]の長さの低インピーダンス損失線路が使用されているときの、230[MHz]における透過係数は−76dBである。図7に示したチップセラミックコンデンサの230[MHz]における透過係数よりも約46dB(約1/200)小さい。このときの、低インピーダンス損失線路32を透過する電力は0.86[mW]となる。

【0170】

4.6[mW]のうちの0.1%が大気中に放射され、放射するまでの過程で、孤立電磁波が多くの箇所で反射を繰り返すことによってその0.1%のエネルギーが230[MHz]から1[GHz]の間の1つの周波数に存在すると仮定した場合の電磁エネルギーは0.86[nW]である。この値はクラスB情報技術装置の放射電力許容値2[nW]を充分満たす。

【産業上の利用可能性】

【0171】

本発明はスイッチング回路を内蔵する半導体集積回路並びに、半導体集積回路を内蔵する情報技術機器、マルチメディア機器、電力変換機器の高性能化、設計容易化と設計期間の短縮化、小型軽量化、低消費電力化、低コスト化、電磁干渉問題の解消又は低減、電磁のノイズによる誤動作の低減、および品質・信頼性向上を実現することが出来る。

【図面の簡単な説明】

【0172】

【図1】図1は、インバータに関する電磁波等価回路の一例である。

【図2】図2は、線路上の電源側の電位波形と電界波形の一例である。

【図3】図3は、線路上の抵抗側の電位波形と電界波形の一例である。

【図4】図4は、試作した低インピーダンス損失線路の構造の一例である。

【図5】図5は、試作した低インピーダンス損失線路のS21特性の一例である。

【図6】図6は、試作した低インピーダンス損失線路部品の構造の一例である。

【図7】図7は、試作した低インピーダンス損失線路部品のS21特性の一例である。

【図8】図8は、低インピーダンス損失線路の一例である。

【図9】図9は、低インピーダンス損失線を使用するディジタル基本回路の等価回路の一例である。

【符号の説明】

【0173】

1、35、40

インバータ

2、36 PチャネルMOS FET

3、37 NチャネルMOS FET

4、31 直流電源

5、33、34 電源線路

6、38 信号線路

7、39 整合終端抵抗

8 信号線路上の孤立電界波

9 信号線路の電位波形

10 電源線路上の孤立電界波

11 電源側の線路の電位波形

12 銀ペースト層

13 陽極箔

14 絶縁体層

15 固体電解質層

16 カーボンペースト層

17 気密封止樹脂

18 陽極端子

19 陰極端子

21 第1の陰極箔

22 第1の導電性ポリマーペースト層

23 第1の導電性ポリマー層

24 陽極箔

25 第2の導電性ポリマー層

26 第2の導電性ポリマーペースト層

27 第2の陰極箔

32 低インピーダンス損失線路

【技術分野】

【0001】

本発明は、回路または回路部品に関し、特に、高速スイッチング素子を使用する、情報技術装置やディジタルデータ通信機器の直流電源分配回路、並びに高周波DC−DCコンバータ等の電力変換器に使用し、小型軽量化が可能で、変換効率、信号品位(シグナルインテグリティ)、および電磁環境適合性(EMC)を向上させることが出来る低インピーダンス損失線路に関する。

【背景技術】

【0002】

近年、コンピュータを初めとするディジタル回路システムの高性能、小型化の要求が強い。ディジタル回路システムを構成するトランジスタの高速化は、高性能化や小型化に効果があるが、電磁ノイズや消費電力が増えると考えられて来た。

【0003】

IECにおいては、情報技術装置やマルチメディア機器を対象に新たなEMI規格であるCISPR32の制定に向けた作業が進んでいる。ここでは、装置または機器からの放射妨害波について320[MHz]から6[GHz]まで、電源ラインおよび通信線による伝導妨害波について150[kHz]から30[MHz]までが規制の対象となる。許容値は従来の情報技術装置向けのCISPR22と同様であるが、適用対象がディジタル家電を含むマルチメディア機器まで拡大される。

【0004】

一方、半導体技術の先端を進む半導体集積回路においてはトランジスタの高速化が進んでいる。非特許文献1によると、2007年のテクノロジノードにおける高性能MPUのPチャネル型電界効果トランジスタの最小上昇時間(ゲートディレー)は0.64[ps](ピコ秒)であり、電源電圧は1.1[V]である。

【0005】

電磁気学によると、回路の状態には活性状態(exited states)、定常状態(stationary states)および、実用上は定常状態と見なせる準定常状態(quasi

stationary states)が存在する。活性状態とは、回路上の電界と磁界が変化または振動している状態であり交流回路はその一例である。振動する電界と磁界は電磁波となって絶縁体中を進行する。該絶縁体が真空空間の場合は、電磁波は光速で進行する。

【0006】

定常状態とは、回路上の電界と磁界が静止している状態であり直流回路はその一例である。準定常状態とは、電界と磁界が電磁波となって回路上を進行するが、電磁波の波長が回路長に対して非常に長く回路内での電磁波の挙動が強弱振動だけと見なしても通常の界路設計においてほぼ不都合が生じないと見なされる状態である。低周波アナログ回路や、およそ1[ns]以上の立ち上がり時間を有するトランジスタと10[cm]以下の長さの配線で構成される回路は、実用上、準定常状態と見なすことの出来る回路の一例であるとされて来た。

【0007】

電磁気学によると、活性状態にある回路の電流はアンペールの法則として定義され次式で示される。

【0008】

【数1】

【0009】

電磁気学によると、電位Vは、電界の及ばない無限遠から導線の一点までの電界の積分値と定義されるが実用的にはグランド面から導線の一点までの電界の積分値として、また、電界Eは電位Vの傾きとしてそれぞれ次式から求められる。

【0010】

【数2】

【0011】

マックスウエルは、磁界に関する理論と電界に関する理論を融合したマックスウエルの方程式を1873年に発表し、続いてこの式をダランベールの波動方程式の形式に変形し、ベクトル波動方程式を導出した。マックスウエルは、1862年頃から主張していた、電磁波と光はともに光速で伝搬することをこの式を用いて理論的に証明し、線形電磁波理論(以下電磁波理論)を完成させ、これにより電磁気学が完成した。ヘルツは、1887年に、実験によって電磁波の存在を実証し、マックスウエルの電磁波理論の正しさを証明した。

【0012】

電磁気学によると、時間的に変化する電界と磁界は相互に作用しつつ横波となって空間または誘電体中を伝搬する。真空中を伝搬する電磁波の速度は光速である。伝搬する電磁波はポインチングベクトル理論に従って電力を伝搬する。空間を伝搬する電磁波は、周期および極性が一致し振幅ベクトルが進行方向に対して直交する電界波と磁界波とから構成される。この状態の電磁波はTEM(transverse electromagnetic)波と呼ばれる。電磁気学によると、時間的に変化する電界と磁界は相互に作用しつつ横波となって空間または誘電体中を伝搬する。真空中を伝搬する電磁波の速度は光速である。伝搬する電磁波はポインチングベクトル理論に従って電力を伝搬する。空間を伝搬する電磁波は、周期および極性が一致し振幅ベクトルが進行方向に対して直交する電界波と磁界波とから構成される。この状態の電磁波はTEM(transverse electromagnetic)波と呼ばれる。TEM波を構成する電界波の振幅を磁界波の振幅で割った値は波動インピーダンス(surge

impedanceまたはwave impedance)と呼ばれる。

【0013】

電磁気学によると、電磁波は空間だけでなく媒体中も進行する。損失のない誘電体中を進行する電磁波の速度は、光速に対して比誘電率の平方根だけ遅くなり、波長は比誘電率の平方根だけ短くなる。後者は、波長圧縮と呼ばれる。

【0014】

電磁気学によると、損失のある媒体中を進行する電磁波は、次式で示される減衰定数γに従い、進行に伴って振幅が減少し位相が変化する。

【0015】

【数3】

【0016】

式(3)において、γの実数項であるαは減衰定数、γの虚数項であるβは位相定数と呼ばれる。αは、nep/m(ネパー/メートル)の単位で表される。1

[nep/m]は、1メートル進行して振幅がexp-1または0.368倍に減衰することを意味する。

【0017】

電磁気学によると、式(3)中のγ 2を変形して得られる次式の括弧の項は、損失のある誘電体に関する複素誘電率と定義され、虚数部(σ/ε0ω)を実数部(εr)で割った値を誘電体損失の正接と呼び、tanδで表す。但し、tanδは、電磁気学上、深い意味を持たない。

【0018】

【数4】

【0019】

電磁波が導体中を進行する場合は、導体中では電磁波に作用する電荷は存在せず導電率σは ωεに比べて非常に大きいので、γは次式で表される。次式中における減衰定数α の逆数であるδは、表皮厚さと呼ばれる。

【0020】

【数5】

【0021】

電磁気学によると、導体中を進行する電磁波の電界と磁界の比である固有インピーダンスZ0は、損失のある媒体中の固有インピーダンスにおいて導電率σがωεに比べて非常に大きいとして、次式で与えられる。

【0022】

【数6】

【0023】

回路上の電界と磁界が変化または振動している活性状態または準定常状態においては電磁波理論が回路を支配し、この場合は導体中を電磁波が進むことは困難である。しかし回路上の電界と磁界が静止している定常状態においては、導体中を電荷の移動による電流が流れることが出来る。

【0024】

物理学によると、導体中には無尽蔵に近い自由電子すなわち電荷が存在する。直流電源に静的負荷が接続されている場合は導体中の電荷の移動による電流が流れるが、一般に、電荷の移動軸方向にはわずかな電界しか印加されないので、電荷の平均移動速度は極めて遅い。

【0025】

例えば、1平方ミリメートルの断面を有する銅線中を導体中の電荷の速度(dq/dt)で定義される10アンペアの電流が進行しているときの電流の進行速度は、物理学に従って計算すると常温で0.368[mm/s]となる。導体中の電荷は、遅いながらも移動は可能であるので、導体の他端で定常的に電荷が消費される際に導体の一端から同量の電荷が定常的に供給されれば、導体の他端に接続される抵抗器等の定常負荷へのエネルギー供給が支障なく行われる。

【0026】

伝送線路上の電気信号の進行を扱うのが電気通信工学である。電気通信工学によると、直流的に絶縁された2本の導体間に電気信号を与えると、電気信号は電流波と電圧波となって伝送線路を進行するとしている。

【0027】

電気通信工学では、交流回路理論と同様に、電流を導体中の電荷の平均速度(dq/dt)すなわち導体電流としている。しかし、電磁気学の基礎を成すマックスウエルの方程式においては、導体電流は、時間の関数ではない電流密度Jに対応させている。

【0028】

交流回路理論や電気通信工学が電流をdq/dtと定義しているのは以下の理由によると考えられる。交流回路理論を支える重要な法則の一つであるキルヒホッフの法則が発表されたのが1845年で、マックスウエルが電磁波の存在を理論的に証明しヘルツによって実験で電磁波の存在が確認される42年前である。また、電気通信工学を支える重要な理論の一つである電信方程式が開発されたのが1874年で、同様に電磁波の存在が確認される13年前である。従って、交流回路理論および電気通信工学が実用化された当時は、回路の作用を電磁波の作用とする考え方がそもそも存在していなかった。さらに、その後も理論の修正が行われなかった。

【0029】

電気通信工学の基礎を成す電信方程式において、導体電流が光速で流れることが出来るとしている根拠となっているのはダランベールの波動方程式である。ダランベールの波動方程式では、波動の主体をスカラー量のラプラシアンとするベクトル関数で表現し、波動の主体を特定していない。導体電流が導体間電圧とともに波となることが、電気回路を支配する電磁気学と整合していなので、電圧と電流に関する回路方程式をダランベールの波動方程式に対比させて得られる電信方程式は、電磁気学とは無関係であり、また電磁気学に整合していないことになる。

【0030】

電流の定義が電磁気学に整合していないとなると、線路の電圧や、インピーダンス、電磁波との関係、さらには伝送損失に関しても電磁気学と矛盾する事態が生じる可能性がある。電気通信工学にはこのような問題が内在するが、歴史が古く伝送線路設計への豊富な適用実績を背景に、従来通りの連続波を対象とする伝送線路設計では電磁気学との矛盾が顕在化しないよう、工夫が施されている。

【0031】

スイッチング波またはディジタル波のような間欠波を対象とする伝送線路設計においても電気通信工学に基づくと効率的であると言う考え方が支配的である。しかし電気通信工学のディジタル回路への実用実績が少ないため、電磁気学と対比しつつ慎重に設計や解析を行わないと、電磁気学との前記矛盾が顕在化する可能性がある。

【0032】

電磁気学によれば、絶縁された2本の導体で構成される伝送線路に印加された電磁波は、TEMモードとなって準光速で進行する。絶縁が真空であれば進行速度は高速となる。このとき伝送線路で観測される電流や電圧は、それぞれ式(1)および式(2)から求められ、実態は伝送線路の導体ではなくて絶縁体中を進む電界波と磁界波である。電気通信工学によると、伝送線路上のTEM波を構成する電界波の振幅を磁界波の振幅で割った値が、特性インピーダンスである。

【0033】

電磁気学と電気通信工学によると、伝送線路上を進行する信号の挙動は、伝送線路の特性インピーダンスと伝搬定数によって決まる。平板導体や絶縁体の材料特性は、伝送線路の特性インピーダンスに対して実用上ほとんど影響を及ぼさない。

【0034】

電気通信工学によると、直径aの2本の導線の中心間を距離dだけ離して平行に配置した構造の、レッヘル線路の特性インピーダンスは次式から求めることが出来る。

【0035】

【数7】

【0036】

電気通信工学によると、実用的なマイクロストリップ線路ならびに平行板線路の特性インピーダンスは次式から求めることが出来る。

【0037】

【数8】

【0038】

電気通信工学によると、既知の特性インピーダンスZ0を有する伝送線路を通して未知の特性インピーダンスZ1を有する伝送線路に電磁波を注入したときの、

前記二つの伝送線路の接続点における反射係数S11は、次式で表される。

【0039】

【数9】

【0040】

電気通信工学によると、反射係数がS11である、線路間の透過係数S21Γは、次式で表される。

【0041】

【数10】

【0042】

電気通信工学によると減衰定数α1を超える損失線路の透過係数S21αは、次式で表される。

【0043】

【数11】

【0044】

電磁気学によると、実用的な伝送線路の減衰定数は、電磁波が損失のある誘電体内を進行するときの減衰と、電磁波が誘電体内を進行する過程でその一部が導体内に侵入して熱になる導体損と、伝送線路外に漏れ出る放射損との和となると考えることが出来る。

【0045】

高速ディジタルデータ通信機器の配線設計は電気通信工学に従って行われている。しかし、電気通信工学は正弦波等の連続波を扱う伝送線路設計には適するが、前述のようにディジタル信号のような間欠波を扱う伝送線路設計には、電磁気学との矛盾があり適さない。

【0046】

高速ディジタルデータ通信機器や高周波電力変換器おける直流電源は、回路に電荷を供給すると考えられている。

【0047】

電磁気学によると、マックスウエルは、単位(試験)点電荷に働く力の原因は、単位点電荷の存在する場所における電界にあるとし、クーロンの法則を修正した。この事実はあまり知られていない。

【0048】

修正された電磁気学によると、電界に関する静電(electrostatic)エネルギーwEは、次式で表される。

【0049】

【数12】

【0050】

このように、静電エネルギーwEは電荷が持っているのではなくて電界Eと電束密度Dの積または電界Eとして媒質に蓄積していることになる。

【0051】

なお、電圧Vが印加された容量Cのコンデンサに蓄積されている静電エネルギーwCは、電極距離をd、電極面積をSとすると、次式で表される。

【0052】

【数13】

【0053】

電磁気学によると磁界に関する静磁気(magnetostatic)エネルギーwHは磁界と磁束密度の積として媒質に蓄積しているとされ、次式で表される。

【0054】

【数14】

【0055】

電流Iが印加された誘導Lのリアクトルに蓄積されている静磁気エネルギーwLは、リアクトルの磁路長をl 、磁路の断面積をSとすると、次式で表される。

【0056】

【数15】

【0057】

非特許文献4および非特許文献5に示される孤立電磁波コンセプトによると、半導体集積回路内のトランジスタは、スイッチングの瞬間に、非線形波動またはソリトンの一種である孤立電磁波を励起する。ディジタル回路システムを構成する回路モジュール内のトランジスタも同様である。

【0058】

トランジスタのスイッチング動作時の孤立電磁波の励起メカニズムは、1834年にJohn Scott Russell がソリトンを発見する際に行った種々の実験の内の水を貯めた水門(ゲート)を急に開くことによって生じたソリトンの発生メカニズムや、ソリトンの一種であると確認されている津波の生成過程に極めて類似している。

【0059】

前記孤立電磁波コンセプトによると、トランジスタがオフからオンにスイッチングする瞬間に、トランジスタの電位が前記直流電源の電圧を電源線路と信号線路の特性インピーダンス分割した値になる。従って、電源線路には電圧を分割電圧まで下げる極性の孤立電磁波が、信号線路には電圧を分割電圧まで上げる極性の孤立電磁波がそれぞれ同時に励起され、電磁波理論に従い、互いにその振幅ベクトルが直交する孤立電界波と孤立磁界波を伴って伝送線路上を進行する。

【0060】

図1は、インバータに関する電磁波等価回路の一例である。

【0061】

図1において、特性インピーダンスZ0の伝送線路の途中にインバータ1が接続されており、特性インピーダンスZ0の伝送線路5は直流電源4とインバータ1との間に接続されて電源線路を構成し、特性インピーダンスZ0の伝送線路6はインバータ1と整合終端抵抗7との間に接続されて信号線路を構成している。インバータ1は、PチャネルMOS

FET2とNチャネルMOS FET3によるコンプリメンタリー構成である。

【0062】

図1において、インバータ1のオン状態とは、PチャネルMOS FET2がオンでNチャネルMOS FET3がオフの状態であり、インバータ1のオフ状態はその逆である。伝送線路を進行するTEM波に関する磁界と電流の関係および電界と電位の関係は、電磁気学においてそれぞれアンペアの法則および電位の定義として示される。

【0063】

図2は、線路上の電源側の電位波形と電界波形の一例である。図3は、線路上の抵抗側の電位波形と電界波形の一例である。

【0064】

図2は、インバータ1がオン時の伝送線路6上の電位波形9と、電磁気学に示される電位の定義から逆算して求められる伝送線路6上を進む電界波形8とを示す。図3は、インバータ1がオン時の伝送線路5上の電位波形11と、電磁気学に示される電位の定義から逆算して求められる電源側の伝送線路5上を進む電界波形10とを示す。

【0065】

図2および図3に示すように、インバータ1のスイッチングによって生じる電界の波形は、トランジスタの立ち上がり波形の最大傾斜部の接線を立ち上がり波形と見なして求める立ち上がり時間と円周率との積の逆数として求められる周波数で定義される実効周波数(significant frequency)を有する正弦波の半波形に近似している。実効周波数の考え方を引用すると、前記近似の確かさ(accuracy)は、92%以上と見込まれる。従って、設計だけに限ると実用上、実効周波数で行うことが出来る。

【0066】

図1から図3において、インバータ1がオンすると、図1中のB点とC点の電位は等しくE/2[V]となる。インバータ1によって励起された、お互い逆極性を有する伝送線路6上を進む孤立電界波8と伝送線路5上を進む孤立電界波10は、それぞれインバータ1に対して反対方向に進む。伝送線路6上を進む孤立電界波8は、伝送線路6の電位を0[V]からE/2[V]に上昇させつつ進み、整合終端抵抗7に向かう。一方、伝送線路5上を進む孤立電界波10は、伝送線路5の電位をE[V]からE/2[V]に降下させつつ直流電源4に向かって、それぞれ伝送線路を構成する絶縁体中を準光速で進行する。

【0067】

前記孤立電磁波コンセプトによると、伝送線路上を進行する孤立電磁波の波長は次式で定義される。

【0068】

【数16】

【0069】

従来の電源デカップリング回路または回路部品については、下記の特許文献や非特許文献に記載されている。その要点は後述される。

【特許文献1】特開2002−260965(P2002−260965A)

【特許文献2】特開2005−294449(P2005−294499A)

【特許文献3】特開2007−42732(P2007−42732A)

【特許文献4】特開2002−164760(P2002−164760A)

【特許文献5】特開2004−048650(P2004−048650A)

【非特許文献1】Hirokazu Tohya and Noritaka Toya著 「A NovelDesign Methodology of the On - Chip Power Distribution Network Enhancing thePerformance and Suppressing EMI of the SoC」、IEEE International Symposium onCircuits and Systems 2007、 pp. 889-892、 May 2007.

【非特許文献2】遠矢弘和、遠矢紀尚 著 「SoCの性能とEMCを大きく改善するオンチップ電源分配回路の新しい設計法」、電子情報通信学会 信学技報、Vol.107、No.149、 EE2007-20、pp.73-78、2007年7月.

【非特許文献3】Stephan Kirchmeyerand Knud Reuter著 「Scientific importance, propertiesand growing applications of poly(3,4-ethylendioxythiophene)、The Royal Societyof Chemistry、Journal of Materials Chemistry.,2005、pp. 2077-2088、2005.

【発明の開示】

【発明が解決しようとする課題】

【0070】

解決しようとする問題点の第1は、特許文献1に関する。特許文献1は、簡便な製造工程で、良好な特性を有する固体電解コンデンサを得ることができる固体電解コンデンサの製造方法を提供するために、固体電解質層に関する詳細な製法を開示している。しかし、改良の目的がESRの低減であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0071】

解決しようとする問題点の第2は、特許文献2に関する。特許文献2は、静電容量及び耐圧の向上と、小型大容量化を可能とした固体電解コンデンサの製造方法を提供するために、固体電解質層に関する詳細な製法を開示している。しかし、改良の目的が静電容量及び耐圧の向上と、小型大容量化であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0072】

解決しようとする問題点の第3は、特許文献3に関する。特許文献3は、大容量、低ESR、高信頼性である固体電解コンデンサを提供するために、セパレータを含む固体電解質層に関する詳細な製法を開示している。しかし、改良の目的が大容量、低ESR、高信頼性であり、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0073】

解決しようとする問題点の第4は、特許文献4に関する。特許文献4は、10KHzから1GHz間での帯域で使用する分布定数型ノイズフィルタの形成法を示している。該分布定数型ノイズフィルタの長さは、電子部品から発生する高周波の1/4波長以上の長さとなるように設定するとしているが、たとえば100[MHz]の高調波すなわち正弦波の1/4波長は大気中で75[cm]、この文献で絶縁体として使用している酸化アルミニウムの場合は、比誘電率が約8.5であるので26[cm]となり、通常の電子・電気機器に使用するには長すぎる。また、線路の入力インピーダンス特性は、反射係数(S11)の測定値または同等の電磁界シミュレーション値から求めるべきところを透過係数(S21)から求める理論的な誤りを犯しているのでデータの信頼性が無い。従って、開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。さらに極性を有しているため使用に際して注意が必要であった。

【0074】

解決しようとする問題点の第5は、特許文献5に関する。特許文献7は、高速化、高周波数化に適した平行平板線路型素子を提供するために、電極の構造を詳細に示しているが、使用する材料の物理定数や固体電解質層に関する製法が示されていない。従って期待する透過係数(S21)の特性の裏付けが無い。開示されている技術によって、コンデンサに期待されている理想電源の機能に近づけることは不可能であった。

【0075】

非特許文献1および非特許文献2は本特許の理論的な根拠を成す重要文献であるがすでに詳述した。非特許文献3も本特許の理論的な根拠の一つである。非特許文献3は、ナノサイズの粒子にしたポリ(3,4−エチレンジオキシチオフェン)とポリスチレン・スルホン酸の錯体の例が示されている。このように薬品メーカからナノサイズの固体電解質材料が供給されれば、これを使用する部品メーカ等での化学重合反応工程が不要になる。非特許文献3のような化学メーカの努力により、100 [S/m]以上の導電率を有するナノサイズの固体電解質材料の商品化は間近となっている。

【0076】

電磁気学の定義に従うと、ディジタル信号処理回路の多くは準定常回路に該当すると考えられ、設計には交流回路理論が使用されている。準定常状態の回路は電磁波理論が支配しているが、回路を定常と見なして設計や解析しても実用上の誤差が少ないということを意味する。ディジタル信号処理回路のトランジスタのスイッチング速度が向上すると電磁ノイズが増加し、その対策は非常に難しいとされている。スイッチング周波数が高くなると小型軽量化が計られることはよく知られているが、電磁ノイズの増加が、ディジタル回路システムの高周波化を妨げている大きな要因の一つとなっている。

【0077】

定常回路を扱う交流回路理論では、電磁波である電磁ノイズの対策は不可能であることは自明である。従って、トランジスタの高速化に伴って発生する電磁ノイズ問題を解決するためには、ディジタル回路システムを構成する配線の設計において、配線の長さにかかわらず電磁波理論を適用する必要があることになる。

【0078】

電気・電子回路には、多くのコンデンサが使用されている。コンデンサは、1875年にドイツ人のクライスト(Ewald George von Kleist)

によって発明された後、原理的な変更がなされないままで電気電子機器に使用されてきた化石のような存在であるが、最近のディジタル化に伴って機器での使用数が増加し続けている。例えばPCのマザーボードにおいては、600個から1000個またはそれ以上のコンデンサが使用され、半導体集積回路パッケージやチップ上にも多くのコンデンサが搭載または形成されており、使用数は増える傾向にある。

【0079】

一般に、コンデンサの機能は、交流回路理論に従って電荷の蓄積とされている。また、直流電源は交流回路に電荷を供給すると考えられている。特に半導体メーカは、コンデンサからの電荷の供給が半導体集積回路の安定動作に必須であると考えている。従って、コンデンサは、電荷蓄積または放出性能を高めるために、おおむね絶縁体に対向する電極の形状は正方形または円形であって、対向する電極の全面または中心部に一対の回路接続用端子が備えられている。

【0080】

一方で、電気・電子回路に使用されているコンデンサの多くは、ディジタル信号処理回路が発生する電磁ノイズを電源分配回路でデカップリング(減結合)するためにも使用されている。以上の理由から、ディジタル回路システムにおいては、コンデンサのほとんどが電源分配回路に搭載され、回路に並列に接続されている。

【0081】

ところで、コンデンサの機能を電荷の蓄積とする考え方は、前述のようにマックスウエルによって否定され、完成された電磁気学においては、コンデンサの機能は電束密度または電界の蓄積と修正されている。従って、交流回路理論を学んだ回路設計技術者が信じる、コンデンサからの電荷の供給が半導体集積回路の安定動作に必須であるという考え方は、全くの誤りであることが判る。

【0082】

次に、コンデンサに期待されているデカップリング効果について検証を試みる。ここで言うデカップリング効果とは高域の電磁ノイズを遮断し電源供給に必要な直流または低周波域を透過させる効果であるので、デカップリングをロウパスフィルタリングと言うことが出来る。すなわち、コンデンサを回路に並列に接続すると、周波数が高くなるにつれてコンデンサのインピーダンスが小さくなるので、キルヒホッフの法則に従い、並列コンデンサを挟む閉回路間の独立性が高まるが、低周波ではコンデンサの作用は無視できるほどになり、並列コンデンサを挟む閉回路間の一体性が高まる。

【0083】

電気通信工学によると、線路に並列に接続されたときのコンデンサのインピーダンスは、測定系がZ0の特性インピーダンスを有するネットワークアナライザでS21を測定することによって次式から求められるとされている。

【0084】

【数17】

【0085】

これは、コンデンサを線路に並列に接続する場合は、式(11)における線路長zがゼロとなり、透過係数S21と反射係数S11が比例関係となるためである。なお、測定されるS21の値は周波数が高くなると1よりかなり小さくなる。またZ0は通常50[Ω]である。この場合は、式(17)は簡略化できて、ZC=25S21となる。

【0086】

式(17)にS21の測定値を代入することによって、市販されているコンデンサのインピーダンスの周波数特性を求めるとV字型の特性曲線となる。すなわち、セラミックコンデンサ等の比較的静電容量が小さいコンデンサにおいては、直列共振点と呼ばれるインピーダンスが最小となる周波数までは周波数に比例してインピーダンス値が減少し、直列共振周波数以上ではインピーダンスが周波数に比例して増加する特性となる。

【0087】

このような特性になる理由は、従来、コンデンサにはリード線、端子、および電極があり、この部分を流れる電流は導体電流であるのでこの部分が等価直列インダクタンス(ESL)として作用し、周波数が高くなるほど電流が流れにくくなるためであるとされている。さらに前記直列共振点のインピーダンスは誘電体損失やリード線、端子、および電極の抵抗等で構成される等価直列抵抗(ESR)によって決まると考えられている。

【0088】

しかし、デカップリングコンデンサの周波数特性についての上記解釈は、電磁気学に照らすと誤りであることが判る。すなわち、デカップリングコンデンサは電磁波の回路と定義されている交流回路での使用が想定されているにもかかわらず、デカップリングコンデンサの周波数特性についての上記解釈は、主に静電磁界における電磁気学の理論に基づいているし、オームの法則は電磁気学とは関係無い。

【0089】

デカップリングコンデンサは電磁波の回路と定義されている交流回路での使用が想定されているのであれば、回路または線路におけるインピーダンスは、電磁波の進行を想定した特性インピーダンスで無ければならない。しかし、コンデンサは線路から見たときの長さがゼロであるので、コンデンサ部の電磁波はTEMモードでは無い。従って、コンデンサの特性インピーダンスは理論上存在しないことになる。

【0090】

長年続けられてきたコンデンサに対する、直列共振点と呼ばれるインピーダンスが最小となる周波数以上におけるインピーダンス特性を改善するための各種改良は、以上から、そのほとんどが的を射ないものであったと考えることが出来る。すなわち、ESLを小さくするためにサイズを出来るだけ小さくする。リード線、端子、および電極には導電性の高い材料を使用する。誘電体損を出来るだけ小さくする等である。最近、等価直列抵抗(ESR)が小さすぎるとQファクタが大きくなりかえって電磁ノイズが増えることがあるという理由で、リード線、端子、および電極には導電性が比較的低い材料を使用し誘電体損をやや大きくしたコンデンサも現れているが、デカップリング機能向上の観点からは、これも的を射ない方法と位置づけられる。

【0091】

さらに、コンデンサの使用法についても誤りがある。コンデンサを多数並列に接続することによって回路のインピーダンスが低くなると言う考え方があり、広く信じられている。この考え方はキルヒホッフの法則が成り立つ場合に有効であるが、キルヒホッフの法則が成り立たない数メガヘルツ以上では無効である。数メガヘルツ以上の信号を扱う電磁波の進行を想定すべき回路において、回路インピーダンスを低くする方法は、伝送線路の特性インピーダンスを低くする以外に無い。

【0092】

コンデンサは、線路長がゼロであるので、線路に多数のコンデンサを並列に接続しても、線路の特性インピーダンスを低くすることは出来ない。しかし、伝送線路の特性インピーダンスと透過係数は独立であるので、電磁波の透過を減らすことは出来る。コンデンサの場合は、線路長がゼロすなわち線路ではないために、インピーダンスと透過係数が比例関係にあったのであるが、このこのような考え方で求められるインピーダンスは、数メガヘルツ以上の信号を扱うデカップリング回路においては意味のない指標である。

【0093】

従って、コンデンサの前記V字型のインピーダンス特性は、デカップリング機能の周波数上限を示すためのものであると考えるのが正しい。すなわち、コンデンサの並列使用は、たとえば非特許文献2に従って、電束密度または電界の蓄積の機能に期待して、集中要素モデルが採用できる低周波領域に限る必要があるということになる。これは、電源分配回路のデカップリングに適する部品が、現在において存在しないことを意味する。このことが、電磁ノイズ問題に改善の兆しが見られない最大の理由の一つであることは容易に推定できる。

【0094】

アナログ回路は、回路状態の変化が比較的緩やかで始まりと終わりが明確でないことが多い。従って、特に低周波アナログ回路の設計においては、マックスウエルが確立した電磁波理論の代わりに、定常状態の回路を扱う交流回路理論を適用しても、実用上、問題が生じることはほとんど無かった。

【0095】

一方、クロック回路やディジタル信号処理回路は、アナログ回路と異なり、状態の変化の期間が短く変化の始まりと終わりは明確である。ディジタル信号処理回路の状態の変化は非常に急激であり、急激な電界または磁界の変化は、電磁気学に従い大きなレベルの電磁波を励起する。ディジタル信号処理回路における電界または磁界の変化は一般に間歇的である。さらに、周波数制御型のディジタル信号処理回路においては、スイッチングの周期は不定である。

【0096】

以上のようにアナログ回路とディジタル信号処理回路は、電磁気学の観点からは大きく異なっている。しかし、クロック回路やディジタル信号処理回路で構成される半導体集積回路の設計や解析には、従来からアナログ回路と同様、交流回路理論が使用されて来た。この原因の一つは、スイッチング波がひずみ波の一種とみなされて来たことに因る。

【0097】

フーリエ変換法によると、ひずみ波は正弦波である多数の高調波から構成されているとされる。これらの高調波は始まりと終わりが無い多数の正弦波である。そうであるとすれば、回路上の信号を高調波毎に解析してその結果を加算すれば、クロック回路やディジタル信号処理回路の解析が可能となる。このように、フーリエ変換法は、クロック回路やディジタル信号処理回路の設計や解析に従来のアナログ回路に関する手法が適用出来るという、利便性の高い道を開いている。

【0098】

フーリエ変換法(Fourier transform)と呼ばれ、1812年に提出されアカデミー大賞を受賞した「熱の解析的理論」の中でフランス人のJoseph

Fourierによって最初に使用された。

フーリエ変換法は数学の一手法であり、汎用性はあるが、上位理論である電磁気学との整合性を確認した上で電気電子回路の設計や解析に採用されている訳ではない。

【0099】

従って、クロック回路やディジタル信号処理回路の設計や解析にフーリエ変換法を適用しているのは、前述の電気通信工学においてダランベールの波動方程式のみに依存して導体電流と導体間電圧が光速でと進行するとしているのと同様、物理学の観点からは誤用と考えるべきである。

【0100】

スイッチング波形をひずみ波として扱うと、損失を有する損失線路をスイッチング波が進行した場合に、観測結果と解析結果との間で齟齬が生じる。たとえばデューティが1/10で繰り返し周波数が1[GHz]のスイッチング波をフーリエ変換すると振幅の1/10の値の直流成分と1[GHz]を基本波とする高調波とに分解できる。直流電流はほとんど流さないCMOS回路を使用する半導体集積回路内のある長さの配線または伝送線路が、1[GHz]の振幅を1/2に低下させる損失を有しているとすると、配線または伝送線路の終端でのスイッチング波の振幅は、解析結果ではほぼ1/2以下に低下する。

【0101】

しかし、電磁気学に従うと、スイッチング波の定常振幅は直流電源から供給される静電エネルギーによって維持される。静電エネルギーは波動エネルギーではないので配線または伝送線路の損失の作用は受けない。従って、伝送線路の終端で観測されるスイッチング波の振幅は減衰しないはずである。

【0102】

この事実は、スイッチング波をひずみ波として扱うことが誤りであることを示している。また、この事実は、フーリエ変換法に基づいて生じる群速度の概念に従う、ディジタル信号配線における信号品位(シグナルインテグリティ)に関する従来の理論には修正が必要であることを意味する。すなわち、この事実は、クロック回路やディジタル信号処理回路の技術の今後の発展のためには、従来の回路理論に代わる理論が必要であることを示唆している。

【0103】

ディジタル信号処理回路を誤り無く高い性能で動作させるためには、ディジタル信号処理回路に直流電源を分配する電源分配回路での充分なデカップリングが必要である。前記電源分配回路でのデカップリングが不充分であると、ディジタル信号処理回路の設計や解析において、ディジタル信号処理回路内だけでなくディジタル回路システム内、さらにはディジタル回路システムの外部の電源分配回路もやバッテリ、商用電源ネットワークまでを想定することも必要となる。これでは、設計や解析が事実上不可能になってしまう。

【0104】

しかし、従来のようにスイッチング波形を歪み波として扱うと、ディジタル回路システム内の多くのトランジスタに接続されている前記電源分配回路にはトランジスタの数の歪み波が関係し、それぞれの歪み波には膨大な数の高調波が含まれていることになる。このような状態にある前記電源分配回路のデカップリング回路の設計や解析を行うことは、高性能コンピュータを用いても不可能である。

【0105】

本発明は、上記問題を根本的に解決する手段を提供することを目的の一つとしている。

【課題を解決するための手段】

【0106】

上記課題を解決するため、請求項1記載の発明は、低インピーダンス損失線路に係り、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔と、第1の陰極箔と、第2の陰極箔と、前記陽極箔の両面の誘電体酸化皮膜上に形成される導電性ポリマー層と、前記導電性ポリマー層に前記第1の陰極箔、および前記第2の陰極箔を貼付するための導電性ポリマーペースト層から形成され、前記第1の陰極箔および前記第2の陰極箔を電極とする平行板伝送線路構造であることを特徴としている。

【0107】

また、請求項2記載の発明は、低インピーダンス損失線路に係り、請求項1記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、少なくとも10[MHz]から10[GHz]の帯域において、前記電源線路を除くスイッチング信号が進行する全ての線路の特性インピーダンスに対して1/100以下または0.5[Ω] 以下の特性インピーダンスと、10[nep/m](ネパー/メートル)以上の減衰定数を有することを特徴としている。

【0108】

また、請求項3記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項2記載の低インピーダンス損失線路において、前記導電性ポリマー層が、100[S/m]以上の導電率を有し、前記導電性ポリマーペースト層が、10[S/m]以上の導電率を有することを特徴としている。

【0109】

また、請求項4記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項3記載の低インピーダンス損失線路において、前記弁作用金属が、アルミニウム、タンタル、ニオブ、チタン、ジルコニウム、またはそれらの合金であることを特徴している。

【0110】

また、請求項5記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項4記載の低インピーダンス損失線路において、前記導電性ポリマー層が、導電性モノマーを溶解した酸化剤の水溶液中に前記陽極箔を浸漬することによって形成されることを特徴としている。

【0111】

また、請求項6記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項5記載の低インピーダンス損失線路において、前記導電性ポリマー層が、前記陽極箔をナノサイズの粒子からなる導電性ポリマーを溶解したエタノールまたはブタノール溶液中に浸漬することによって形成されることを特徴としている。

【0112】

また、請求項7記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項6記載の低インピーダンス損失線路において、前記モノマーが、3,4−エチレンジオキシチオフェン、ピロール、フラン、多環状スルフィド、またはそれらの置換誘導体であることを特徴としている。

【0113】

また、請求項8記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項7記載の低インピーダンス損失線路において、前記酸化剤が、ブタノールまたはエタノールに溶解したパラトルエンスルホン酸第二鉄、エチレングリコールに溶解したパラトルエンスルホン酸第二鉄、過ヨウ素酸、またはヨウ素酸であることを特徴としている。

【0114】

また、請求項9記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項8記載の低インピーダンス損失線路において、前記酸化剤の溶液が、アエロジルを添加して40〜180

[mpa.s]の粘度と、0.5 [wt %]から5.0 [wt %]の範囲の水分含有率を有していることを特徴としている。

【0115】

また、請求項10記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項9記載の低インピーダンス損失線路において、前記導電性ポリマー層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)または、前記いずれかの一つ以上を含む錯体で形成されることを特徴としている。

【0116】

また、請求項11記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項10記載の低インピーダンス損失線路において、前記導電性ポリマーペースト層が、バインダー機能を有するポリチオフェンペーストまたはポリピロールペーストであることを特徴としている。

【0117】

また、請求項12記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項11記載の低インピーダンス損失線路において、前記第1の導電性ポリマーペースト層および前記第2の導電性ポリマーペースト層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはカーボングラファイト、または二酸化マンガン、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)、またはシリコン、またはゲルマニウム、またはシリコンゲルマニウム合金のいずれか1つ以上を重量比で50%以上含み、ポリエチレン、エポキシ樹脂、フェノール樹脂のいずれかのバインダーに混合されて形成されることを特徴としている。

【0118】

また、請求項13記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項12記載の低インピーダンス損失線路において、前記誘電体酸化皮膜が、前記電解質の形成工程の前、後、または前後に、化成液に5分から120分間浸漬して化成または修復化成されることを特徴としている。

【0119】

また、請求項14記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項13記載の低インピーダンス損失線路において、前記化成液が、リン酸二水素アンモニウム、リン酸水素二アンモニウム等のリン酸系の化成液、ホウ酸アンモニウム等のホウ酸系の化成液、アジピン酸アンモニウム等のアジピン酸系の化成液であることを特徴としている。

【0120】

また、請求項15記載の発明は、低インピーダンス損失線路に係り、請求項1から請求項14記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、スイッチング素子またはスイッチング回路ブロックと信号線路と電源線路から構成されるスイッチング回路システムの電源線路の全て、または前記電源線路の前記スイッチング素子またはスイッチング回路ブロックの近傍の一部に使用され、前記第1の陰極箔が前記電源線路を構成する非グランド導体に対して直列に挿入され、前記第2の陰極箔が前記漸減線路を構成するグランド導体に対して並列に接続されて使用されることを特徴としている。

【発明の効果】

【0121】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、スイッチング素子によって励起される電磁波の漏洩が大幅に抑圧されるために、スイッチング素子が使用されている機器の電磁環境適合性(EMC)を大幅に向上させることが可能となる。

【0122】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、スイッチング素子によって励起される電磁波の漏洩が大幅に抑圧されるために、アナログ回路とディジタル回路の混在設計が容易になる。

【0123】

本発明をスイッチング回路、ディジタル回路またはこれらに使用する印刷配線基板に適用すると、高速スイッチング素子を使用する情報技術装置、ディジタルデータ通信機器、並びに高周波DC−DCコンバータの直流電源分配回路に使用し、小型軽量化、低コスト化、高変換効率化、高信号品位(シグナルインテグリティ)化、および高電磁環境適合性(EMC)化を両立させることが可能となる。

【発明を実施するための最良の形態】

【0124】

以下、本発明に係る 最良の実施形態について、図面を参照して詳細に説明する。

【0125】

(実施の形態1)

図4は、試作した低インピーダンス損失線路の構造の一例である。図5は、試作した低インピーダンス損失線路のS21特性の一例である。図6は、試作した低インピーダンス損失線路部品の構造の一例である。図7は、試作した低インピーダンス損失線路部品のS21特性の一例である。本実施例における低インピーダンス損失線路および低インピーダンス損失線路部品はいずれも公知である。

【0126】

図6において、本実施例の低インピーダンス損失線路部品は2個の陽極端子18と4個の陰極端子19を有している。低インピーダンス損失線路は銀ペースト層12、陽極箔13、絶縁層14、固体電解質層15、およびカーボンペースト層16で構成されており、全体が気密封止樹脂17で覆われている。図6の右側の1個の陽極端子18および2個の陰極端子19が、陽極箔13および銀ペースト層12の一端にそれぞれ接続され、図6の左側の1個の陽極端子18および2個の陰極端子19が、陽極箔13および銀ペースト層12損失線路の他端にそれぞれ接続されている。

【0127】

図4において、本実施例の低インピーダンス損失線路は、線路部の幅が1[mm]で実効長さが4[mm] 、8[mm] 、16[mm]、および24[mm]を有するエッチング処理が施されたアルミニウム薄膜が陽極箔13として使用されている。アルミニウム薄膜のエッチング部に化成処理によって形成された約15[nm]の前後厚さの酸化アルミニウム被膜が絶縁層14に相当している。アルミニウム薄膜のエッチング部分に化学重合によって付着させたポリピロールが固体電解質層15に相当し、厚さは約2.5[μm]である。カーボンペーストがポリピロールの上に約30[μm]の厚さに塗布され、その上に熱硬化性銀ペーストによって銀ペースト層12が形成されている。

【0128】

電磁界シミュレーション結果によると、本実施例の低インピーダンス損失線路の特性インピーダンスは20−30[mΩ]と推定されている。これは、低インピーダンス損失線路を構成する絶縁体5のみをTEM波が進行する場合に比べて3桁ほど大きい値である。TEM波の一部は絶縁体5から固有インピーダンスで決まる比率で半導体9に進入する。半導体中に進入する電磁波は急速に減衰する。

【0129】

半導体として使用するポリピロールの導電率を3500[S/m]、絶縁体である酸化アルミニウムの厚さを15[nm]、比誘電率を8.5、ポリピロールの塗布厚さを2.5[μm]、比誘電率を1とし、酸化アルミニウムの比誘電率を8.5とする。低インピーダンス損失線路の幅は1[mm]、導体の厚さは100[μm]である。試作結果から、低インピーダンス損失線路の1mm2当たりの静電容量は0.7[μF]である。

【0130】

低インピーダンス損失線路の特性インピーダンスは、ポリピロールの塗布厚さまでTEM波が侵入していると考えると式(8)から32[mΩ]となる。この値は、伝送線路中のポインチングベクトルから求めた電磁界シミュレーション値とほぼ一致する。この値を特性インピーダンスとすれば、50Ωの線路にこの特性インピーダンスを有する低インピーダンス損失線路を接続したときの接続部の透過係数S21αは、式(11)から0.051すなわち−26dBとなる。

【0131】

低インピーダンス損失線路を構成する酸化アルミニウムとポリピロールをTEM波が進行しているときのポリピロールへの透過係数S21Γは、式(10)のZ1に式(6)から得られるポリピロールの固有インピーダンス、Z0に低インピーダンス損失線路の特性インピーダンス値を代入することによって求められる。

【0132】

低インピーダンス損失線路を構成する酸化アルミニウムとポリピロールをTEM波が進行しているときの透過係数S21αは、式(5)から得られるポリピロールの減衰定数にポリピロールへの透過係数を掛けた値をαとして、式(11)に代入すると、低インピーダンス損失線路の長さz毎に求めることが出来る。

【0133】

低インピーダンス損失線路の低周波帯域の特性である静電容量値による50[Ω]の測定系の透過係数S21Cは、式(17)を変形して、次式から求められる。

【0134】

【数18】

【0135】

式(18)において、ZCは、静電容量の交流インピーダンス値に、電極の導電率、ここでは半導体であるポリピロールの導電率に従う低周波でのESR値を加えた値と考えることが出来る。ESRは、次式から求められる。

【0136】

【数19】

【0137】

概略の低インピーダンス損失線路の透過係数S21Aは、次式から求めることが出来る。

【0138】

【数20】

【0139】

式(20)から求められる本実施例の低インピーダンス損失線路の透過係数S21Aは、以下の通りであり、測定結果に近い値となっている。

【0140】

線路長が4[mm]の場合:100[kHz] で−37[dB]、1[MHz]で−53[dB]、10

[MHz]で−73[dB]、100[MHz]で−91[dB]、1[GHz]で−101 [dB]。線路長が8[mm]の場合:100[kHz] で−41[dB]、1[MHz]で−59[dB]、10

[MHz]で−79[dB]、100[MHz]で−97[dB]、1[GHz]で−116 [dB]。線路長が16[mm]の場合:100[kHz] で−46[dB]、1[MHz]で−66

[dB]、10 [MHz]で−86[dB]、100[MHz]で−119[dB]、1[GHz]で−200 [dB]、線路長が24[mm]の場合:100[kHz]

で−50[dB]、1[MHz]で−69[dB]、10 [MHz]で−96[dB]、100[MHz]で−164[dB]、1[GHz]で−287[dB] 。

【0141】

低インピーダンス損失線路部品は低インピーダンス損失線路の両端にボード搭載用の端子が備えられている。このために、高周波帯域で端子間に電磁波のバイパスが形成されて透過係数が劣化する。この電磁波のバイパスは、静電容量を流れる変位電流または電束電流によると考えることが出来る。本実施例の低インピーダンス損失線路部品の実測値から端子間距離1[m]当たりのバイパス容量を求めると5×10−17[F/m]となる。

【0142】

端子間の静電容量のインピーダンスをZTとすると、直列に接続されている静電容量の透過係数S21Tは、次式から求めることが出来る。

【0143】

【数21】

【0144】

概略の低インピーダンス損失線路部品の透過係数S21Bは、次式から求めることが出来る。

【0145】

【数22】

【0146】

式(22)から求められる本実施例の低インピーダンス損失線路部品の透過係数S21Bは、以下の通りであり、測定結果に近い値となっている。

【0147】

線路長が4[mm]の場合:100[kHz] で−37[dB]、1[MHz]で−53[dB]、10 [MHz]で−70[dB]、100[MHz]で−62[dB]、1[GHz]で−42

[dB]。線路長が8[mm]の場合:100[kHz] で−41[dB]、1[MHz]で−59[dB]、10 [MHz]で−76[dB]、100[MHz]で−68[dB]、1[GHz]で−48

[dB]。線路長が16[mm]の場合:100[kHz] で−46[dB]、1[MHz]で−65[dB]、10 [MHz]で−83[dB]、100[MHz]で−74[dB]、1[GHz]で−54

[dB]、線路長が24[mm]の場合:100[kHz] で−50[dB]、1[MHz]で−69[dB]、10 [MHz]で−91[dB]、100[MHz]で−78[dB]、1[GHz]で−58[dB]

。

【0148】

以上の計算結果は、図5、図7と同様に、10[MHz] 以下では低インピーダンス損失線路と低インピーダンス損失線路部品の透過特性の差はほとんど無く、10[MHz]を超えると、低インピーダンス損失線路部品では端子間のバイパスによる透過特性の劣化現象が見られ、劣化度は端子間の距離にほぼ比例している。以上から、上記計算式は実用的であると判断できる。

【0149】

(実施の形態2)

図8は、低インピーダンス損失線路の一例である。

【0150】

図8において、低インピーダンス損失線路は、弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔24と、第1の陰極箔21と、第2の陰極箔27と、陽極箔24の両面の誘電体酸化皮膜上に形成される第1の導電性ポリマー層23および第2の導電性ポリマー層25と、第1の導電性ポリマー層23に第1の陰極箔21を貼付するための第1の導電性ポリマーペースト層22と、第2の導電性ポリマー層25に第2の陰極箔27を貼付するための第2の導電性ポリマーペースト層26から形成され、第1の陰極箔21および第2の陰極箔27を電極とする平行板線路を形成している。

【0151】

図8において、低インピーダンス損失線路は整流作用を有している。従って、陰極箔27にグランド線またはグランド板が接続され陰極箔21に正の電圧を有する電源線が接続された場合は陽極箔24と陰極箔27で構成される線路が機能を発揮し、陽極箔24と陰極箔21で構成される線路は短絡に近い状態となり機能しない。一方、陰極箔21にグランド線またはグランド板が接続され陰極箔27に正の電圧を有する電源線が接続された場合は陽極箔24と陰極箔21で構成される線路が機能を発揮し、陽極箔24と陰極箔27で構成される線路は短絡に近い状態となり機能しない。

【0152】

図8において、低インピーダンス損失線路の幅を1[mm]、長さを12[mm]、導電性ポリマーおよび導電性ポリマーペーストの導電率を1000[S/m]、導電性ポリマーペーストの塗布厚さを20[μm]とする。陽極箔をアルミニウムとして、誘電体酸化皮膜であるアルミナの比誘電率を8.5、厚さ30[nm]とし、陽極箔のエッチングによる面積拡大率を実施の形態1の場合の3割減の153とする。低インピーダンス損失線路の端子間のバイパス容量を10−18[F/m]とする。このときの1mm2当たりのESRは、式(19)から1.7[mΩ]となる。

【0153】

本実施の形態における低インピーダンス損失線路の特性インピーダンスは、実施の形態1に従い、30[mΩ]と推定される。また、透過係数S21Bは、以下のように推定される。

【0154】

線路長が3[mm]の場合:100[kHz]で−34[dB]、1[MHz]で−49[dB]、10 [MHz]で−64[dB]、100[MHz]で−70[dB]、230[MHz]で−71[dB]、1[GHz]で−67

[dB]。線路長が6[mm]の場合:100[kHz]で−38 [dB]、1[MHz]で−55[dB]、10 [MHz]で−70[dB]、100[MHz]で−76[dB]、230[MHz]で−76[dB]、1[GHz]で−73

[dB]。線路長が12[mm]の場合:100[kHz]で−43[dB]、1[MHz]で−61[dB]、10 [MHz]で−76[dB]、100[MHz]で−82[dB]、230[MHz]で−82[dB]、1[GHz]で−80

[dB]、線路長が24[mm]の場合:100[kHz]で−48[dB]、1[MHz]で−67[dB]、10 [MHz]で−82[dB]、100[MHz]で−91[dB]、230[MHz]で−95[dB]、1[GHz]で−92[dB]

。

【0155】

(実施の形態3)

図9は、低インピーダンス損失線路を使用するディジタル基本回路の等価回路の一例である。

【0156】

図9において、低インピーダンス損失線を使用するディジタル基本回路の等価回路は、直流電源31、インバータ35および40、インバータル35を構成するPチャネルMOS FET36およびNチャネルMOS FET37、オンチップインターコネクト上の電源線路34およびボード上の電源線路33、低インピーダンス損失線路32、信号線路38、ならびに整合終端抵抗39から構成されている。

【0157】

図9において、電源線路34と信号線路38の特性インピーダンスが150[Ω]、電源線路33の特性インピーダンスが50[Ω]、低インピーダンス損失線路32の特性インピーダンスが実施の形態3で設計した値の30[mΩ]と仮定する。インバータ35のオン状態とオフ状態の定義は前述と同様であり、伝送線路上の電界と伝送線路の電位との関係は電磁気学に従う。

【0158】

インバータ35がオフからオンに変化する時の信号線路38の電位波形と、信号線路6上を進む孤立電界波形、並びに電源線路33、34の電位波形と電源線路33、34上を進む孤立電界波形は、前述と同様である。従って、図9の回路の動作説明には図2と図3の波形を使用する。

【0159】

図9において、インバータ35がオフからオンに変化したときの孤立電界波の伝送線路上の進行の様子と伝送線路の電位変化は図2、図3で説明した通りである。

【0160】

図9において、電源線路34上を進行する孤立電磁波は電源線路33との接続部で一部が反射し、低インピーダンス損失線路32との接続部ではほぼ全てが、信号線路38上に励起された孤立電磁波と同極性で反射し、電源線路33、34および信号線路38の電位をE/2[V]からほぼE[V]に上昇させつつ進行し、整合終端抵抗39で消滅する。

【0161】

電源線路13の長さが孤立電磁波の波長に対して充分短ければ、インバータ35がオンした後のD点の電位は、電源線路5上を孤立電磁波が進行するときの遅延時間だけ上昇時間が長くなることを除けば、通信を行うのにほぼ充分な値となる。

【0162】

図9において、低インピーダンス損失線路32の特性インピーダンスは30[mΩ]と、通信を行うのにほぼ充分な値であるが、電源線路33、34を進行する孤立電磁波の一部が低インピーダンス損失線路32に侵入する。

【0163】

放射電力Pを有する線形電磁波がアンテナから放射されたときのr[m]の距離での電界強度Eは、IEC CISPR16−2−3に示されている次式から求めることが出来る。

【0164】

【数23】

【0165】

例えば家庭内使用を目的とするクラスB情報技術装置から10[m]の距離での妨害波電界強度の許容値は、VCCI(CISPR22)で決められており、30[MHz]から230[MHz]で30[dBμV/m]、230[MHz]から1[GHz]で37[dBμV/m]である。式(23)から、例えば230[MHz]での許容放射電力値を求めると、2[nW]となる。

【0166】

実施の形態3で設計した低インピーダンス損失線路を使用し、図9のインバータ35の代わりに20個の電源端子が設けられており100[W]の消費電力を有する半導体集積回路を想定すると、1個の電源端子で5[W]の電力を分担していることになる。

【0167】

次に、導体集積回路の2個の電源端子毎に、実施の形態2で設計した12[mm]の長さの低インピーダンス損失線路が使用されている場合について、電源ポートから漏洩する不要電磁波の放射電力量を試算する。

【0168】

図9において、インバータ35によって励起された孤立電界波8が信号線路38の電位を0[V]からE/2 [V]まで上昇させるエネルギーと、電源線路34に向かう孤立電界波が電源線路の電位をE[V]からE/2 [V] まで降下させるエネルギーの比は、1:3である。従って電源線路34上の電力は7.5[W]となる。電源線路34から電源線路33への電力透過率は0.87となるので、電源線路33を透過する電力は6.5[W]となる。

【0169】

低インピーダンス損失線路32に、実施の形態2で設計した6[mm]の長さの低インピーダンス損失線路が使用されているときの、230[MHz]における透過係数は−76dBである。図7に示したチップセラミックコンデンサの230[MHz]における透過係数よりも約46dB(約1/200)小さい。このときの、低インピーダンス損失線路32を透過する電力は0.86[mW]となる。

【0170】

4.6[mW]のうちの0.1%が大気中に放射され、放射するまでの過程で、孤立電磁波が多くの箇所で反射を繰り返すことによってその0.1%のエネルギーが230[MHz]から1[GHz]の間の1つの周波数に存在すると仮定した場合の電磁エネルギーは0.86[nW]である。この値はクラスB情報技術装置の放射電力許容値2[nW]を充分満たす。

【産業上の利用可能性】

【0171】

本発明はスイッチング回路を内蔵する半導体集積回路並びに、半導体集積回路を内蔵する情報技術機器、マルチメディア機器、電力変換機器の高性能化、設計容易化と設計期間の短縮化、小型軽量化、低消費電力化、低コスト化、電磁干渉問題の解消又は低減、電磁のノイズによる誤動作の低減、および品質・信頼性向上を実現することが出来る。

【図面の簡単な説明】

【0172】

【図1】図1は、インバータに関する電磁波等価回路の一例である。

【図2】図2は、線路上の電源側の電位波形と電界波形の一例である。

【図3】図3は、線路上の抵抗側の電位波形と電界波形の一例である。

【図4】図4は、試作した低インピーダンス損失線路の構造の一例である。

【図5】図5は、試作した低インピーダンス損失線路のS21特性の一例である。

【図6】図6は、試作した低インピーダンス損失線路部品の構造の一例である。

【図7】図7は、試作した低インピーダンス損失線路部品のS21特性の一例である。

【図8】図8は、低インピーダンス損失線路の一例である。

【図9】図9は、低インピーダンス損失線を使用するディジタル基本回路の等価回路の一例である。

【符号の説明】

【0173】

1、35、40

インバータ

2、36 PチャネルMOS FET

3、37 NチャネルMOS FET

4、31 直流電源

5、33、34 電源線路

6、38 信号線路

7、39 整合終端抵抗

8 信号線路上の孤立電界波

9 信号線路の電位波形

10 電源線路上の孤立電界波

11 電源側の線路の電位波形

12 銀ペースト層

13 陽極箔

14 絶縁体層

15 固体電解質層

16 カーボンペースト層

17 気密封止樹脂

18 陽極端子

19 陰極端子

21 第1の陰極箔

22 第1の導電性ポリマーペースト層

23 第1の導電性ポリマー層

24 陽極箔

25 第2の導電性ポリマー層

26 第2の導電性ポリマーペースト層

27 第2の陰極箔

32 低インピーダンス損失線路

【特許請求の範囲】

【請求項1】

弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔と、第1の陰極箔と、第2の陰極箔と、前記陽極箔の両面の誘電体酸化皮膜上に形成される導電性ポリマー層と、前記導電性ポリマー層に前記第1の陰極箔、および前記第2の陰極箔を貼付するための導電性ポリマーペースト層から形成され、前記第1の陰極箔および前記第2の陰極箔を電極とする平行板伝送線路構造であることを特徴とする、低インピーダンス損失線路

【請求項2】

請求項1記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、少なくとも10[MHz]から10[GHz]の帯域において、前記電源線路を除くスイッチング信号が進行する全ての線路の特性インピーダンスに対して1/100以下または0.5[Ω] 以下の特性インピーダンスと、10[nep/m](ネパー/メートル)以上の減衰定数を有することを特徴とする、低インピーダンス損失線路

【請求項3】

請求項1から請求項2記載の低インピーダンス損失線路において、前記導電性ポリマー層が、100[S/m]以上の導電率を有し、前記導電性ポリマーペースト層が、10[S/m]以上の導電率を有することを特徴とする、低インピーダンス損失線路

【請求項4】

請求項1から請求項3記載の低インピーダンス損失線路において、前記弁作用金属が、アルミニウム、タンタル、ニオブ、チタン、ジルコニウム、またはそれらの合金であることを特徴とする、低インピーダンス損失線路

【請求項5】

請求項1から請求項4記載の低インピーダンス損失線路において、前記導電性ポリマー層が、導電性モノマーを溶解した酸化剤の水溶液中に前記陽極箔を浸漬することによって形成されることを特徴とする、低インピーダンス損失線路

【請求項6】

請求項1から請求項5記載の低インピーダンス損失線路において、前記導電性ポリマー層が、前記陽極箔をナノサイズの粒子からなる導電性ポリマーを溶解したエタノールまたはブタノール溶液中に浸漬することによって形成されることを特徴とする、低インピーダンス損失線路

【請求項7】

請求項1から請求項6記載の低インピーダンス損失線路において、前記モノマーが、3,4−エチレンジオキシチオフェン、ピロール、フラン、多環状スルフィド、またはそれらの置換誘導体であることを特徴とする、低インピーダンス損失線路

【請求項8】

請求項1から請求項7記載の低インピーダンス損失線路において、前記酸化剤が、ブタノールまたはエタノールに溶解したパラトルエンスルホン酸第二鉄、エチレングリコールに溶解したパラトルエンスルホン酸第二鉄、過ヨウ素酸、またはヨウ素酸であることを特徴とする、低インピーダンス損失線路

【請求項9】

請求項1から請求項8記載の低インピーダンス損失線路において、前記酸化剤の溶液が、アエロジルを添加して40〜180

[mpa.s]の粘度と、0.5 [wt %]から5.0 [wt %]の範囲の水分含有率を有していることを特徴とする、低インピーダンス損失線路

【請求項10】

請求項1から請求項9記載の低インピーダンス損失線路において、前記導電性ポリマー層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)または、前記いずれかの一つ以上を含む錯体で形成されることを特徴とする、低インピーダンス損失線路

【請求項11】

請求項1から請求項10記載の低インピーダンス損失線路において、前記導電性ポリマーペースト層が、バインダー機能を有するポリチオフェンペーストまたはポリピロールペーストであることを特徴とする、低インピーダンス損失線路

【請求項12】

請求項1から請求項11記載の低インピーダンス損失線路において、前記第1の導電性ポリマーペースト層および前記第2の導電性ポリマーペースト層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはカーボングラファイト、または二酸化マンガン、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)、またはシリコン、またはゲルマニウム、またはシリコンゲルマニウム合金のいずれか1つ以上を重量比で50%以上含み、ポリエチレン、エポキシ樹脂、フェノール樹脂のいずれかのバインダーに混合されて形成されることを特徴とする、低インピーダンス損失線路

【請求項13】

請求項1から請求項12記載の低インピーダンス損失線路において、前記誘電体酸化皮膜が、前記電解質の形成工程の前、後、または前後に、化成液に5分から120分間浸漬して化成または修復化成されることを特徴とする、低インピーダンス損失線路

【請求項14】

請求項1から請求項13記載の低インピーダンス損失線路において、前記化成液が、リン酸二水素アンモニウム、リン酸水素二アンモニウム等のリン酸系の化成液、ホウ酸アンモニウム等のホウ酸系の化成液、アジピン酸アンモニウム等のアジピン酸系の化成液であることを特徴とする、低インピーダンス損失線路

【請求項15】

請求項1から請求項14記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、スイッチング素子またはスイッチング回路ブロックと信号線路と電源線路から構成されるスイッチング回路システムの電源線路の全て、または前記電源線路の前記スイッチング素子またはスイッチング回路ブロックの近傍の一部に使用され、前記第1の陰極箔が前記電源線路を構成する非グランド導体に対して直列に挿入され、前記第2の陰極箔が前記漸減線路を構成するグランド導体に対して並列に接続されて使用されることを特徴とする、低インピーダンス損失線路

【請求項1】

弁作用金属から成り両面にエッチング部が形成され該エッチング部の表面に誘電体酸化皮膜が形成された陽極箔と、第1の陰極箔と、第2の陰極箔と、前記陽極箔の両面の誘電体酸化皮膜上に形成される導電性ポリマー層と、前記導電性ポリマー層に前記第1の陰極箔、および前記第2の陰極箔を貼付するための導電性ポリマーペースト層から形成され、前記第1の陰極箔および前記第2の陰極箔を電極とする平行板伝送線路構造であることを特徴とする、低インピーダンス損失線路

【請求項2】

請求項1記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、少なくとも10[MHz]から10[GHz]の帯域において、前記電源線路を除くスイッチング信号が進行する全ての線路の特性インピーダンスに対して1/100以下または0.5[Ω] 以下の特性インピーダンスと、10[nep/m](ネパー/メートル)以上の減衰定数を有することを特徴とする、低インピーダンス損失線路

【請求項3】

請求項1から請求項2記載の低インピーダンス損失線路において、前記導電性ポリマー層が、100[S/m]以上の導電率を有し、前記導電性ポリマーペースト層が、10[S/m]以上の導電率を有することを特徴とする、低インピーダンス損失線路

【請求項4】

請求項1から請求項3記載の低インピーダンス損失線路において、前記弁作用金属が、アルミニウム、タンタル、ニオブ、チタン、ジルコニウム、またはそれらの合金であることを特徴とする、低インピーダンス損失線路

【請求項5】

請求項1から請求項4記載の低インピーダンス損失線路において、前記導電性ポリマー層が、導電性モノマーを溶解した酸化剤の水溶液中に前記陽極箔を浸漬することによって形成されることを特徴とする、低インピーダンス損失線路

【請求項6】

請求項1から請求項5記載の低インピーダンス損失線路において、前記導電性ポリマー層が、前記陽極箔をナノサイズの粒子からなる導電性ポリマーを溶解したエタノールまたはブタノール溶液中に浸漬することによって形成されることを特徴とする、低インピーダンス損失線路

【請求項7】

請求項1から請求項6記載の低インピーダンス損失線路において、前記モノマーが、3,4−エチレンジオキシチオフェン、ピロール、フラン、多環状スルフィド、またはそれらの置換誘導体であることを特徴とする、低インピーダンス損失線路

【請求項8】

請求項1から請求項7記載の低インピーダンス損失線路において、前記酸化剤が、ブタノールまたはエタノールに溶解したパラトルエンスルホン酸第二鉄、エチレングリコールに溶解したパラトルエンスルホン酸第二鉄、過ヨウ素酸、またはヨウ素酸であることを特徴とする、低インピーダンス損失線路

【請求項9】

請求項1から請求項8記載の低インピーダンス損失線路において、前記酸化剤の溶液が、アエロジルを添加して40〜180

[mpa.s]の粘度と、0.5 [wt %]から5.0 [wt %]の範囲の水分含有率を有していることを特徴とする、低インピーダンス損失線路

【請求項10】

請求項1から請求項9記載の低インピーダンス損失線路において、前記導電性ポリマー層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)または、前記いずれかの一つ以上を含む錯体で形成されることを特徴とする、低インピーダンス損失線路

【請求項11】

請求項1から請求項10記載の低インピーダンス損失線路において、前記導電性ポリマーペースト層が、バインダー機能を有するポリチオフェンペーストまたはポリピロールペーストであることを特徴とする、低インピーダンス損失線路

【請求項12】

請求項1から請求項11記載の低インピーダンス損失線路において、前記第1の導電性ポリマーペースト層および前記第2の導電性ポリマーペースト層が、ポリ(p−フェニレン)(22.7°)、またはポリ(p−フェニレンスルフィド)、またはカーボングラファイト、または二酸化マンガン、またはポリアセチレン、またはポリ(3,4−エチレンジオキシチオフェン)、またはポリピロール、またはポリフェニレンビニレン、またはテトラチアフルバレン−テトラキノジメタン(TTF−TCNQ)、またはシリコン、またはゲルマニウム、またはシリコンゲルマニウム合金のいずれか1つ以上を重量比で50%以上含み、ポリエチレン、エポキシ樹脂、フェノール樹脂のいずれかのバインダーに混合されて形成されることを特徴とする、低インピーダンス損失線路

【請求項13】

請求項1から請求項12記載の低インピーダンス損失線路において、前記誘電体酸化皮膜が、前記電解質の形成工程の前、後、または前後に、化成液に5分から120分間浸漬して化成または修復化成されることを特徴とする、低インピーダンス損失線路

【請求項14】

請求項1から請求項13記載の低インピーダンス損失線路において、前記化成液が、リン酸二水素アンモニウム、リン酸水素二アンモニウム等のリン酸系の化成液、ホウ酸アンモニウム等のホウ酸系の化成液、アジピン酸アンモニウム等のアジピン酸系の化成液であることを特徴とする、低インピーダンス損失線路

【請求項15】

請求項1から請求項14記載の低インピーダンス損失線路において、該低インピーダンス損失線路が、スイッチング素子またはスイッチング回路ブロックと信号線路と電源線路から構成されるスイッチング回路システムの電源線路の全て、または前記電源線路の前記スイッチング素子またはスイッチング回路ブロックの近傍の一部に使用され、前記第1の陰極箔が前記電源線路を構成する非グランド導体に対して直列に挿入され、前記第2の陰極箔が前記漸減線路を構成するグランド導体に対して並列に接続されて使用されることを特徴とする、低インピーダンス損失線路

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【公開番号】特開2010−45471(P2010−45471A)

【公開日】平成22年2月25日(2010.2.25)

【国際特許分類】

【出願番号】特願2008−206585(P2008−206585)

【出願日】平成20年8月11日(2008.8.11)

【出願人】(706001123)株式会社アイキャスト (37)

【Fターム(参考)】

【公開日】平成22年2月25日(2010.2.25)

【国際特許分類】

【出願日】平成20年8月11日(2008.8.11)

【出願人】(706001123)株式会社アイキャスト (37)

【Fターム(参考)】

[ Back to top ]