半導体素子

【課題】 Agのマイグレーションによるリークを抑制する。

【解決手段】 半導体素子は、第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、共晶層を介して前記キャップ層と結合する支持基板とを有する。

【解決手段】 半導体素子は、第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、共晶層を介して前記キャップ層と結合する支持基板とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、半導体素子に関する。

【背景技術】

【0002】

近年、半導体発光素子の高出力化に伴い、光取り出し構造形成などの点から放熱支持基板に半導体膜を貼付・支持させた構造のデバイスが用いられている。高出力を実現するためには半導体膜と支持基板との間に高反射率の電極として、Ag又はAg合金からなる反射電極が形成されている。

【0003】

Agは反射率が高いが、Agイオンのマイグレーション即ち移動を起こしやすく、特に通電時や温度変化などによってマイグレーションを起こしやすい事が知られている。Agイオンのマイグレーションが起こると、リークなどの素子の特性、信頼性に影響を与える現象が発生する。

【0004】

Agイオンのマイグレーションを防止するために、Ptなどの高融点金属や、ITOなどの金属酸化物からなる拡散防止層を形成することが広く行われている。例えば、窒化物半導体側に透光性電極としてITOなどの金属酸化物などを形成し、その上にAg系反射電極層、次いで、拡散防止層として高融点金属又は金属窒化物などを含む層を形成することが知られている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−192782号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

拡散防止層として、Ptなどの金属膜を使用した場合には、成膜時の応力や、放熱支持基板への貼り付けなどの工程において、高温処理されるため、当該熱処理時に熱ひずみの影響を受けて、拡散防止層にクラックが入るなどの欠陥が生じやすい。

【0007】

また、拡散防止層として酸化膜などを使用した場合には、熱処理時における熱ひずみの影響は受けにくいものの、成膜時にピンホールが生じ、そこを通じてAgが移動してしまう現象が起こり、拡散防止の性能が金属膜に比べて劣ってしまう。

【0008】

本発明の目的は、Agのマイグレーションによるリークを抑制することが可能な半導体素子を提供することである。

【課題を解決するための手段】

【0009】

本発明の一観点によれば、半導体素子は、第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、共晶層を介して前記キャップ層と結合する支持基板とを有する。

【発明の効果】

【0010】

本発明によれば、Agのマイグレーションによるリークを抑制することが可能な半導体素子を提供することができる。

【図面の簡単な説明】

【0011】

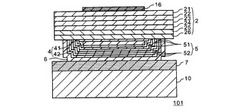

【図1】本発明の実施例による窒化物半導体発光素子(LED素子)101の素子構造を表す概略断面図である。

【図2】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図3】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図4】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図5】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図6】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図7】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図8】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図9】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図10】クラック発生評価実験に用いた比較例1によるキャップ層53の構造を表す概略断面図である。

【図11】クラック発生評価実験に用いた比較例2によるキャップ層55の構造を表す概略断面図である。

【図12】本発明の実施例を適用したフリップチップタイプの窒化物半導体発光素子(LED素子)の素子構造を表す概略断面図である。

【図13】本発明の実施例を適用したジャンクションダウンタイプの窒化物半導体発光素子(LED素子)の素子構造を表す概略断面図である。

【発明を実施するための形態】

【0012】

図1は、本発明の実施例による窒化物半導体発光素子(LED素子)101の素子構造を表す概略断面図である。

【0013】

窒化物半導体発光素子(LED素子)101は、例えば、アンドープのGaN層21、Si等をドープしたn型GaN層22、GaN/InGaNを含む歪緩和層23、GaN/InGaN多層膜からなる多重量子井戸構造を有する活性層24、p型AlGaN層(クラッド層)25及びp型GaN層(コンタクト層)26を含むGaN系半導体層(発光部)2、GaN系半導体層(発光部)2の一方の主面上に形成されるNi層41及びAg層42からなる反射電極層4、反射電極層4を覆い、Agの拡散防止層としての酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層からなるキャップ層5、GaN系半導体層(発光部)2の他方の主面上に形成されるn側電極(配線電極)16、例えばPt/Ti/Ni/Au/Pt/AuSnからなる共晶材を含む共晶層7とAu層6との共晶合金層、該共晶合金層を介してキャップ層5と結合するシリコン(Si)支持基板10を含んで構成される。

【0014】

図1に示すように、本発明の実施例では、Ag層42を含む反射電極層4をキャップ層5で覆うことにより、Agの拡散を防止している。本実施例では、キャップ層5を酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとし、これを2セット以上形成することにより構成している。

【0015】

酸化物透明導電層51は、例えば、ITOなどの透明導電膜からなり、結晶子の大きさが小さい微結晶又は非晶質(結晶性の低い)膜であることが、熱ひずみを緩和するという観点から好ましい。なお、本明細書において、「結晶子」とは、単結晶とみなせる最大の集まりのことであり、「結晶子の大きさが小さい微結晶」とは、結晶子の大きさがX線回析法(Scherrer法)で測定した場合に、500Å以下である結晶を指す。

【0016】

例えば、ITOの場合は結晶の配向方向は〈100〉または〈111〉に配向しやすく、さらに、膜厚が厚くなるとそれらの方向への配向性が強くなる。また、配向方向はスパッタ膜では〈100〉方向が顕著であり、EB膜では〈111〉方向が顕著である。膜厚100〜1000Åの間ではこれらの方向性が明確でない(X線回折でシャープなピークを示さない)結晶性の低い領域となるので、熱ひずみの緩和に適していると考えられる。

【0017】

酸化物透明導電層51の成長温度は結晶子の大きさが小さい微結晶または非晶質(結晶性の低いもの)となる200℃以下とするのが好ましい。例えば、ITOの結晶子の大きさは200℃以下で成膜したスパッタ膜の場合、概ね500Å程度となり、より低温で成膜するとさらにサイズが小さくなっていく傾向が見られる。

【0018】

酸化物透明導電層51の材料として、ITO以外に、ZnO、AZO、IZOなどの酸化物透明導電性膜を用いることができる。酸化物透明導電性膜の材料によって微結晶〜非晶質となる温度や成膜条件は異なるため、結晶子の大きさが小さい微結晶または非晶質となるように設定する必要がある。

【0019】

酸化物透明導電層51は1層あたりの膜厚は、100Å以上あることが好ましく、100〜1000Åの範囲であることがより好ましい。膜厚が100Å未満では金属層52の熱ひずみを緩和するには薄すぎる。また、膜厚が1000Åよりも厚くなると、酸化物透明導電層51の結晶性が上がり、熱ひずみを緩和する力が弱くなる。さらに、透明導電性膜の欠点であるピンホールなどの欠陥が出やすくなる。透明導電性膜は初期核生成時にはランダム配向しており膜厚が厚くなっていくときに方向性がそろった結晶粒となっていく傾向がある。本実施例では、酸化物透明導電層51を100〜1000Åの結晶性の低い非晶質または微結晶(結晶子が500Å以下)とすることで熱ひずみの緩和を起こしやすくしている。

【0020】

以上のように、酸化物透明導電層51は、熱処理により発生する熱ひずみを緩和する機能を有するが、ピンホールを有する場合があり、このピンホールを伝って、Agのマイグレーションが起こることが考えられる。そのため、本実施例では、酸化物透明導電層51を覆って金属層(第2キャップ層)52を形成して、拡散防止機能を向上させている。

【0021】

金属層52の材料としては、TiW以外に、Ti、Pt、TiNなどの金属、合金または金属窒化物を用いることが可能である。金属層52の膜厚は、酸化物透明導電層51の膜厚以上であることが好ましい。膜厚の上限は酸化物透明導電層51の厚さの2倍程度であれば、十分であると考えられる。これは結晶性の低い酸化物透明導電層51は表面平坦性が高くないためその平坦性を緩和できれば十分なためである。

【0022】

酸化物透明導電層51及び金属層52の成膜方法としてはスパッタ、EB蒸着などが使用可能である、スパッタで成膜した場合の方が、膜の密着性、カバレッジ性能が高く、Agの拡散防止機能に優れている。

【0023】

これらの酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとして、図1に示すように、例えば、3セット分成膜する。キャップ層5の総厚は、反射電極層4の膜厚より厚くなることが好ましく、1.5倍以上の総厚となることがより好ましい。積層のセット数は、キャップ層5の総厚が反射電極層4の膜厚より厚くなればよいため、1セット以上であれば良いが、2セット以上形成することが好ましい。

【0024】

これは、酸化物透明導電層(第1キャップ層)51にピンホールが生じたとしても、2層以上の酸化物透明導電層51を重ねることにより、ピンホールの位置が重なることをほとんどなくすことができ、ピンホールを伝ってAgのマイグレーションが起こることを防ぐと考えられるからである。

【0025】

キャップ層5の構成は、必ず酸化物透明導電層51が反射電極層4に接することが好ましい。これは反射電極層4の端面に一番ひずみがかかりやすいため、熱ひずみの緩和の働きをする酸化物透明導電層51を最下面に配置して、反射電極層4と接するようにすることでその効果を高くするためである。

【0026】

また、酸化物透明導電層51を反射電極層4の反射面に近い第1層目とすることで反射電極層4の周りに反射電極層4よりは接触抵抗の高い部分が形成され、通常の通電時は電気が流れないが高電圧印加時に通電パスとなりうる領域を形成することができる。これにより瞬時の高電圧印加時の信頼性(静電耐圧)を向上させることができる。

【0027】

なお、本発明者らが、人体モデル(Human Body Model:HBM)実験方法により、本実施例によるLED素子101の静電耐圧を実際に測定したところ、1kV以上の静電耐圧を有するものが75%得られた。これに対して、TiWのみのキャップ層構成だった場合には、1kV以上の静電耐圧を有するものは得られなかった。

【0028】

以上のように、キャップ層5を酸化物透明導電層51と金属、合金または金属窒化物からなる金属層52の積層構造とすることにより金属層52にかかる熱ひずみの緩和を透明導電膜51が行うことで、キャップ層5のクラックなどの欠陥が入りにくくなり、Agのマイグレーションが抑えられる。よって、素子の特性、信頼性が向上する。

【0029】

以下、図2〜図9を参照して、本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明する。

【0030】

まず図2に示すように、サファイア基板(成長基板)1を準備し、サーマルクリーニングを行い、MOCVDにより、GaNバッファ層20を、例えば、500℃で低温成長した後、基板温度を1000℃に昇温して、結晶化させる。その後、GaNバッファ層20上に、GaN系半導体層2を成長させる。例えば、サファイア基板1をMOCVD装置に投入後、バッファ層20を成長した後に、アンドープのGaN層21、Si等をドープしたn型GaN層22を成長温度1000℃で成長させる。その後、成長温度730℃でGaN/InGaNを含む歪緩和層23を成長させる。続いて、活性層24として、例えば、GaN/InGaN多層膜からなる多重量子井戸構造を成長温度700℃で成長させる。さらに、活性層24上にp型AlGaN層(クラッド層)25及びp型GaN層(コンタクト層)26を順次成長させる。なお、バッファ層20及びGaN系半導体層2の膜厚は、例えば、6μm程度である。なお、成長基板はサファイアに限らず、GaNやSiC基板などでもよい。

【0031】

続いて、図3に示すように、反射電極層4を成膜する。例えば、Ni層41を約5Å、Ag層42を約3000Åの順に電子ビーム(EB)蒸着にて成膜を行う。次に、発光パターンの大きさにレジストマスクを形成し、{硝酸:水:酢酸:リン酸}={1:1:8:10}の割合で調整したエッチャントで25℃、20秒間、反射電極層4をエッチングして、図4に示す状態にする。その後、酸素が含まれるガスの雰囲気で、400度で2分加熱処理する。Ni層41は、Ag層42のp型GaN層26への密着性を向上させるとともに、透明電極の機能を有し、Ag層42は反射電極としての機能を有する。

【0032】

次に、図5に示すように、酸化物透明導電層(第1キャップ層)51及び該酸化物透明導電層(第1キャップ層)51を覆う金属層(第2キャップ層)52の積層からなるキャップ層5を、反射電極層4を覆うように形成する。

【0033】

酸化物透明導電層(第1キャップ層)51は、例えば、ITO等の透明導電性膜からなり、常温のスパッタ装置で、反射電極層4を覆って成膜する。酸素分圧は2.5×10−2Pa、パワーは100Wとする。膜厚は、1000Å程度である。なお、酸化物透明導電層(ITO)51は、結晶子の大きさが小さい微結晶または非晶質(結晶性の低い)膜である。

【0034】

金属層(第2キャップ層)52は、例えば、TiW等の金属膜等からなり、常温のスパッタ装置で、酸化物透明導電層(第1キャップ層)51を覆って成膜する。アルゴン分圧は1Pa、パワーは300Wとする。膜厚は、1000Å程度である。

【0035】

続いて、図6に示すように、酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとし、それをさらに、2セット繰り返して積層し、合計3セットの積層からなるキャップ層5を形成する。なお、キャップ層5の総厚は、6000Å程度である。キャップ層5の積層を覆って、膜厚2000Å程度のAuからなる共晶(Au)層6を成膜する。

【0036】

次に、表面にPt/Ti/Ni/Au/Pt/AuSnからなる共晶材を含む共晶層7を成膜したSi基板10を準備し、図7に示すように、Au層6と共晶層7とを張り合わせて、真空中、6kNの圧力、温度330〜350℃で熱圧着(共晶)させる。

【0037】

次に、図8に示すように、サファイア基板1の裏面(サファイア基板側)よりエキシマレーザを照射して、バッファ層20を分解させ、サファイア基板1とGaN系半導体層2とを分離し、図9に示す状態とする。レーザーリフトオフにより発生したGaを熱水などで除去し、その後塩酸で表面処理する。表面処理には窒化物半導体をエッチングできるものであればよく、リン酸、硫酸、KOH、NaOHなどの酸やアルカリなどの薬剤を用いることができる。また、表面処理はArプラズマや塩素系プラズマを用いたドライエッチングや、研磨などで行ってもよい。

【0038】

その後、既存のフォトリソグラフィ技術によりGaN系半導体層2をパターニングする。具体的には、GaN系半導体層2表面にフォトレジストを塗布、露光、現像し、ドライエッチングにてGaN系半導体層2の不要な一部(露出部分)を除去して、隣接するGaN系半導体層2間にストリート部を形成する。その後、フォトレジストをリムーバで除去する。

【0039】

次に、n側電極(配線電極)16として、Ti/Al/Ti/Pt/Auを順に成膜し、図1に示す状態とする。なお、n側電極16に用いられる電極構成としては接触抵抗が、1×10−4Ωcm2以下となること望ましく、それに見合う電極構成であればそのほかの材料でもよい。n側電極16は、例えば、GaN系半導体層2の主面の全面積の5〜15%程度の面積を有するストライプ等の平面形状を有する。

【0040】

以上により、窒化物半導体発光素子101が完成する。一枚の基板から複数の素子を製造する場合は、スクライブ後ブレイキングして素子分離を行う。

【0041】

なお、青色GaNの発光素子を白色化するには発光素子を封止充填する樹脂に黄色の蛍光体を入れる。

【0042】

本発明者らは、本実施例による窒化物半導体発光素子101を、図6に示す状態まで実際に作製した段階でのクラックの発生評価を行った。また、比較例1及び比較例2として図10及び図11に示すものを実際に作製し、クラックの発生評価を行った。

【0043】

クラックの発生評価に用いた本実施例による半導体素子は、図6に示すように、成長基板1上に、GaN系半導体層(発光部)2を形成し、その上に反射電極層4を成膜し、該反射電極層4を覆うように、キャップ層5(酸化物透明導電層51及び金属層52の積層を3セット)及び共晶(Au)層6を成膜した段階のものである。

【0044】

比較例1による半導体素子は、図10に示すように、本実施例によるキャップ層5の代わりに、膜厚6000ÅのTiW膜単層からなるキャップ層53を成膜し、その上に共晶(Au)層6を成膜した段階のものであり、比較例2による半導体素子は、図11に示すように、本実施例によるキャップ層5の代わりに、膜厚1000ÅのPt膜54と膜厚1000ÅのTiW膜52との積層を1セットとし、それを3セット成膜したものからなるキャップ層55を成膜し、その上に共晶(Au)層6を成膜した段階のものである。

【0045】

クラックの発生の評価は、キャップ層形成後、硝酸の中で1分放置し、Agの侵食(クラック部分から硝酸が入り込み、AgがエッチングされてAgのラインが後退)があった場合は成膜時の応力によるクラック発生があると判断することにより行った。この評価方法では、比較例1や比較例2では、ほぼ全周囲において侵食の発生が観察されたが、本実施例による半導体素子では、Agの侵食がほとんど観察されなかった。したがって、比較例1及び比較例2ではクラックが発生したが、本実施例では、クラックが発生しなかったものと考えられる。

【0046】

また、支持基板10と貼りあわせた後(図7に示す状態)に、クラック発生を写真観察により判断した。この写真観察では、もとのAgのラインよりAgがはみでていたらクラックが発生したと判断した。この場合にも、比較例1及び比較例2では、図10及び図11に示すように、キャップ層53、55のエッジ部分でクラックCRが観察されたが、本実施例によるキャップ層5のエッジ部分にはクラックは観察されなかった。

【0047】

なお、その後の工程によるクラックの発生は、Agがクラックよりマイグレーションし、リークになるとPL発光強度が減少したり、p−nジャンクション部分にAgが析出してきたりすることで判断が可能である。

【0048】

以上、本発明の実施例によれば、反射電極層4を覆うキャップ層5を酸化物透明導電層51と金属、合金または金属窒化物からなる金属層52の積層構造とした。これにより、金属層52にかかる熱ひずみの緩和を透明導電膜51が行うことができる。よって、キャップ層5のクラックなどの欠陥が入りにくくなり、Agのマイグレーションが抑えられ、素子の特性、信頼性を向上させることができる。

【0049】

さらに、酸化物透明導電層51を100〜1000Åの結晶性の低い非晶質または微結晶(結晶子が500Å以下)とすることで熱ひずみの緩和を起こしやすくすることができる。

【0050】

また、本発明の実施例によれば、酸化物透明導電層51を反射電極層4と接する第1層目とすることで、反射電極層4の周りに反射電極層4よりも接触抵抗の高い領域が形成される。よって、通常の通電時には電気が流れないが、高電圧印加時に通電パスとなりうる領域を形成することが可能なる。これにより、瞬時の高電圧印加時の信頼性(静電耐圧)を向上させることができる。

【0051】

また、上述の実施例では、成長基板1としてサファイア基板を用いたが、これ以外にもGaN基板やSiC基板などを成長基板として用いることができる。また、半導体層2の材料はGaNに限らず、AlGaInPや、ZnO等でもよい。

【0052】

以上、実施例、及び変形例に沿って本発明を説明したが、本発明はこれらに限定されるものではない。種々の変更、改良、組み合わせ等が可能なことは当業者には自明であろう。

【0053】

例えば、本発明の実施例はAg層42が反射電極層4に含まれれば、図12に示す成長基板1を除去しないフリップチップタイプや、図13に示す成長基板1としてGaNやSiCなどの透明導電性基板を用いたジャンクションダウンタイプにも適用可能である。

【符号の説明】

【0054】

1…サファイア基板、2…GaN系半導体層(発光部)、4…反射電極層、5…キャップ層、6…、7…、10…シリコン(Si)基板、16…n側電極(配線電極)、20…バッファ層、21…アンドープGaN層、22…Siドープn型GaN層、23…歪緩和層、24…活性層、25…p型AlGaN層(クラッド層)、26…p型GaN層(コンタクト層)、41…Ni層、42…Ag層、51…酸化物透明導電層(第1キャップ層)、52…金属層(第2キャップ層)、53、55…キャップ層、54…Pt層、101…窒化物半導体発光素子(LED素子)

【技術分野】

【0001】

本発明は、半導体素子に関する。

【背景技術】

【0002】

近年、半導体発光素子の高出力化に伴い、光取り出し構造形成などの点から放熱支持基板に半導体膜を貼付・支持させた構造のデバイスが用いられている。高出力を実現するためには半導体膜と支持基板との間に高反射率の電極として、Ag又はAg合金からなる反射電極が形成されている。

【0003】

Agは反射率が高いが、Agイオンのマイグレーション即ち移動を起こしやすく、特に通電時や温度変化などによってマイグレーションを起こしやすい事が知られている。Agイオンのマイグレーションが起こると、リークなどの素子の特性、信頼性に影響を与える現象が発生する。

【0004】

Agイオンのマイグレーションを防止するために、Ptなどの高融点金属や、ITOなどの金属酸化物からなる拡散防止層を形成することが広く行われている。例えば、窒化物半導体側に透光性電極としてITOなどの金属酸化物などを形成し、その上にAg系反射電極層、次いで、拡散防止層として高融点金属又は金属窒化物などを含む層を形成することが知られている(例えば、特許文献1参照)。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】特開2008−192782号公報

【発明の概要】

【発明が解決しようとする課題】

【0006】

拡散防止層として、Ptなどの金属膜を使用した場合には、成膜時の応力や、放熱支持基板への貼り付けなどの工程において、高温処理されるため、当該熱処理時に熱ひずみの影響を受けて、拡散防止層にクラックが入るなどの欠陥が生じやすい。

【0007】

また、拡散防止層として酸化膜などを使用した場合には、熱処理時における熱ひずみの影響は受けにくいものの、成膜時にピンホールが生じ、そこを通じてAgが移動してしまう現象が起こり、拡散防止の性能が金属膜に比べて劣ってしまう。

【0008】

本発明の目的は、Agのマイグレーションによるリークを抑制することが可能な半導体素子を提供することである。

【課題を解決するための手段】

【0009】

本発明の一観点によれば、半導体素子は、第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、共晶層を介して前記キャップ層と結合する支持基板とを有する。

【発明の効果】

【0010】

本発明によれば、Agのマイグレーションによるリークを抑制することが可能な半導体素子を提供することができる。

【図面の簡単な説明】

【0011】

【図1】本発明の実施例による窒化物半導体発光素子(LED素子)101の素子構造を表す概略断面図である。

【図2】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図3】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図4】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図5】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図6】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図7】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図8】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図9】本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明するための概略断面図である。

【図10】クラック発生評価実験に用いた比較例1によるキャップ層53の構造を表す概略断面図である。

【図11】クラック発生評価実験に用いた比較例2によるキャップ層55の構造を表す概略断面図である。

【図12】本発明の実施例を適用したフリップチップタイプの窒化物半導体発光素子(LED素子)の素子構造を表す概略断面図である。

【図13】本発明の実施例を適用したジャンクションダウンタイプの窒化物半導体発光素子(LED素子)の素子構造を表す概略断面図である。

【発明を実施するための形態】

【0012】

図1は、本発明の実施例による窒化物半導体発光素子(LED素子)101の素子構造を表す概略断面図である。

【0013】

窒化物半導体発光素子(LED素子)101は、例えば、アンドープのGaN層21、Si等をドープしたn型GaN層22、GaN/InGaNを含む歪緩和層23、GaN/InGaN多層膜からなる多重量子井戸構造を有する活性層24、p型AlGaN層(クラッド層)25及びp型GaN層(コンタクト層)26を含むGaN系半導体層(発光部)2、GaN系半導体層(発光部)2の一方の主面上に形成されるNi層41及びAg層42からなる反射電極層4、反射電極層4を覆い、Agの拡散防止層としての酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層からなるキャップ層5、GaN系半導体層(発光部)2の他方の主面上に形成されるn側電極(配線電極)16、例えばPt/Ti/Ni/Au/Pt/AuSnからなる共晶材を含む共晶層7とAu層6との共晶合金層、該共晶合金層を介してキャップ層5と結合するシリコン(Si)支持基板10を含んで構成される。

【0014】

図1に示すように、本発明の実施例では、Ag層42を含む反射電極層4をキャップ層5で覆うことにより、Agの拡散を防止している。本実施例では、キャップ層5を酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとし、これを2セット以上形成することにより構成している。

【0015】

酸化物透明導電層51は、例えば、ITOなどの透明導電膜からなり、結晶子の大きさが小さい微結晶又は非晶質(結晶性の低い)膜であることが、熱ひずみを緩和するという観点から好ましい。なお、本明細書において、「結晶子」とは、単結晶とみなせる最大の集まりのことであり、「結晶子の大きさが小さい微結晶」とは、結晶子の大きさがX線回析法(Scherrer法)で測定した場合に、500Å以下である結晶を指す。

【0016】

例えば、ITOの場合は結晶の配向方向は〈100〉または〈111〉に配向しやすく、さらに、膜厚が厚くなるとそれらの方向への配向性が強くなる。また、配向方向はスパッタ膜では〈100〉方向が顕著であり、EB膜では〈111〉方向が顕著である。膜厚100〜1000Åの間ではこれらの方向性が明確でない(X線回折でシャープなピークを示さない)結晶性の低い領域となるので、熱ひずみの緩和に適していると考えられる。

【0017】

酸化物透明導電層51の成長温度は結晶子の大きさが小さい微結晶または非晶質(結晶性の低いもの)となる200℃以下とするのが好ましい。例えば、ITOの結晶子の大きさは200℃以下で成膜したスパッタ膜の場合、概ね500Å程度となり、より低温で成膜するとさらにサイズが小さくなっていく傾向が見られる。

【0018】

酸化物透明導電層51の材料として、ITO以外に、ZnO、AZO、IZOなどの酸化物透明導電性膜を用いることができる。酸化物透明導電性膜の材料によって微結晶〜非晶質となる温度や成膜条件は異なるため、結晶子の大きさが小さい微結晶または非晶質となるように設定する必要がある。

【0019】

酸化物透明導電層51は1層あたりの膜厚は、100Å以上あることが好ましく、100〜1000Åの範囲であることがより好ましい。膜厚が100Å未満では金属層52の熱ひずみを緩和するには薄すぎる。また、膜厚が1000Åよりも厚くなると、酸化物透明導電層51の結晶性が上がり、熱ひずみを緩和する力が弱くなる。さらに、透明導電性膜の欠点であるピンホールなどの欠陥が出やすくなる。透明導電性膜は初期核生成時にはランダム配向しており膜厚が厚くなっていくときに方向性がそろった結晶粒となっていく傾向がある。本実施例では、酸化物透明導電層51を100〜1000Åの結晶性の低い非晶質または微結晶(結晶子が500Å以下)とすることで熱ひずみの緩和を起こしやすくしている。

【0020】

以上のように、酸化物透明導電層51は、熱処理により発生する熱ひずみを緩和する機能を有するが、ピンホールを有する場合があり、このピンホールを伝って、Agのマイグレーションが起こることが考えられる。そのため、本実施例では、酸化物透明導電層51を覆って金属層(第2キャップ層)52を形成して、拡散防止機能を向上させている。

【0021】

金属層52の材料としては、TiW以外に、Ti、Pt、TiNなどの金属、合金または金属窒化物を用いることが可能である。金属層52の膜厚は、酸化物透明導電層51の膜厚以上であることが好ましい。膜厚の上限は酸化物透明導電層51の厚さの2倍程度であれば、十分であると考えられる。これは結晶性の低い酸化物透明導電層51は表面平坦性が高くないためその平坦性を緩和できれば十分なためである。

【0022】

酸化物透明導電層51及び金属層52の成膜方法としてはスパッタ、EB蒸着などが使用可能である、スパッタで成膜した場合の方が、膜の密着性、カバレッジ性能が高く、Agの拡散防止機能に優れている。

【0023】

これらの酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとして、図1に示すように、例えば、3セット分成膜する。キャップ層5の総厚は、反射電極層4の膜厚より厚くなることが好ましく、1.5倍以上の総厚となることがより好ましい。積層のセット数は、キャップ層5の総厚が反射電極層4の膜厚より厚くなればよいため、1セット以上であれば良いが、2セット以上形成することが好ましい。

【0024】

これは、酸化物透明導電層(第1キャップ層)51にピンホールが生じたとしても、2層以上の酸化物透明導電層51を重ねることにより、ピンホールの位置が重なることをほとんどなくすことができ、ピンホールを伝ってAgのマイグレーションが起こることを防ぐと考えられるからである。

【0025】

キャップ層5の構成は、必ず酸化物透明導電層51が反射電極層4に接することが好ましい。これは反射電極層4の端面に一番ひずみがかかりやすいため、熱ひずみの緩和の働きをする酸化物透明導電層51を最下面に配置して、反射電極層4と接するようにすることでその効果を高くするためである。

【0026】

また、酸化物透明導電層51を反射電極層4の反射面に近い第1層目とすることで反射電極層4の周りに反射電極層4よりは接触抵抗の高い部分が形成され、通常の通電時は電気が流れないが高電圧印加時に通電パスとなりうる領域を形成することができる。これにより瞬時の高電圧印加時の信頼性(静電耐圧)を向上させることができる。

【0027】

なお、本発明者らが、人体モデル(Human Body Model:HBM)実験方法により、本実施例によるLED素子101の静電耐圧を実際に測定したところ、1kV以上の静電耐圧を有するものが75%得られた。これに対して、TiWのみのキャップ層構成だった場合には、1kV以上の静電耐圧を有するものは得られなかった。

【0028】

以上のように、キャップ層5を酸化物透明導電層51と金属、合金または金属窒化物からなる金属層52の積層構造とすることにより金属層52にかかる熱ひずみの緩和を透明導電膜51が行うことで、キャップ層5のクラックなどの欠陥が入りにくくなり、Agのマイグレーションが抑えられる。よって、素子の特性、信頼性が向上する。

【0029】

以下、図2〜図9を参照して、本発明の実施例による窒化物半導体発光素子(LED素子)101の製造方法を説明する。

【0030】

まず図2に示すように、サファイア基板(成長基板)1を準備し、サーマルクリーニングを行い、MOCVDにより、GaNバッファ層20を、例えば、500℃で低温成長した後、基板温度を1000℃に昇温して、結晶化させる。その後、GaNバッファ層20上に、GaN系半導体層2を成長させる。例えば、サファイア基板1をMOCVD装置に投入後、バッファ層20を成長した後に、アンドープのGaN層21、Si等をドープしたn型GaN層22を成長温度1000℃で成長させる。その後、成長温度730℃でGaN/InGaNを含む歪緩和層23を成長させる。続いて、活性層24として、例えば、GaN/InGaN多層膜からなる多重量子井戸構造を成長温度700℃で成長させる。さらに、活性層24上にp型AlGaN層(クラッド層)25及びp型GaN層(コンタクト層)26を順次成長させる。なお、バッファ層20及びGaN系半導体層2の膜厚は、例えば、6μm程度である。なお、成長基板はサファイアに限らず、GaNやSiC基板などでもよい。

【0031】

続いて、図3に示すように、反射電極層4を成膜する。例えば、Ni層41を約5Å、Ag層42を約3000Åの順に電子ビーム(EB)蒸着にて成膜を行う。次に、発光パターンの大きさにレジストマスクを形成し、{硝酸:水:酢酸:リン酸}={1:1:8:10}の割合で調整したエッチャントで25℃、20秒間、反射電極層4をエッチングして、図4に示す状態にする。その後、酸素が含まれるガスの雰囲気で、400度で2分加熱処理する。Ni層41は、Ag層42のp型GaN層26への密着性を向上させるとともに、透明電極の機能を有し、Ag層42は反射電極としての機能を有する。

【0032】

次に、図5に示すように、酸化物透明導電層(第1キャップ層)51及び該酸化物透明導電層(第1キャップ層)51を覆う金属層(第2キャップ層)52の積層からなるキャップ層5を、反射電極層4を覆うように形成する。

【0033】

酸化物透明導電層(第1キャップ層)51は、例えば、ITO等の透明導電性膜からなり、常温のスパッタ装置で、反射電極層4を覆って成膜する。酸素分圧は2.5×10−2Pa、パワーは100Wとする。膜厚は、1000Å程度である。なお、酸化物透明導電層(ITO)51は、結晶子の大きさが小さい微結晶または非晶質(結晶性の低い)膜である。

【0034】

金属層(第2キャップ層)52は、例えば、TiW等の金属膜等からなり、常温のスパッタ装置で、酸化物透明導電層(第1キャップ層)51を覆って成膜する。アルゴン分圧は1Pa、パワーは300Wとする。膜厚は、1000Å程度である。

【0035】

続いて、図6に示すように、酸化物透明導電層(第1キャップ層)51及び金属層(第2キャップ層)52の積層を1セットとし、それをさらに、2セット繰り返して積層し、合計3セットの積層からなるキャップ層5を形成する。なお、キャップ層5の総厚は、6000Å程度である。キャップ層5の積層を覆って、膜厚2000Å程度のAuからなる共晶(Au)層6を成膜する。

【0036】

次に、表面にPt/Ti/Ni/Au/Pt/AuSnからなる共晶材を含む共晶層7を成膜したSi基板10を準備し、図7に示すように、Au層6と共晶層7とを張り合わせて、真空中、6kNの圧力、温度330〜350℃で熱圧着(共晶)させる。

【0037】

次に、図8に示すように、サファイア基板1の裏面(サファイア基板側)よりエキシマレーザを照射して、バッファ層20を分解させ、サファイア基板1とGaN系半導体層2とを分離し、図9に示す状態とする。レーザーリフトオフにより発生したGaを熱水などで除去し、その後塩酸で表面処理する。表面処理には窒化物半導体をエッチングできるものであればよく、リン酸、硫酸、KOH、NaOHなどの酸やアルカリなどの薬剤を用いることができる。また、表面処理はArプラズマや塩素系プラズマを用いたドライエッチングや、研磨などで行ってもよい。

【0038】

その後、既存のフォトリソグラフィ技術によりGaN系半導体層2をパターニングする。具体的には、GaN系半導体層2表面にフォトレジストを塗布、露光、現像し、ドライエッチングにてGaN系半導体層2の不要な一部(露出部分)を除去して、隣接するGaN系半導体層2間にストリート部を形成する。その後、フォトレジストをリムーバで除去する。

【0039】

次に、n側電極(配線電極)16として、Ti/Al/Ti/Pt/Auを順に成膜し、図1に示す状態とする。なお、n側電極16に用いられる電極構成としては接触抵抗が、1×10−4Ωcm2以下となること望ましく、それに見合う電極構成であればそのほかの材料でもよい。n側電極16は、例えば、GaN系半導体層2の主面の全面積の5〜15%程度の面積を有するストライプ等の平面形状を有する。

【0040】

以上により、窒化物半導体発光素子101が完成する。一枚の基板から複数の素子を製造する場合は、スクライブ後ブレイキングして素子分離を行う。

【0041】

なお、青色GaNの発光素子を白色化するには発光素子を封止充填する樹脂に黄色の蛍光体を入れる。

【0042】

本発明者らは、本実施例による窒化物半導体発光素子101を、図6に示す状態まで実際に作製した段階でのクラックの発生評価を行った。また、比較例1及び比較例2として図10及び図11に示すものを実際に作製し、クラックの発生評価を行った。

【0043】

クラックの発生評価に用いた本実施例による半導体素子は、図6に示すように、成長基板1上に、GaN系半導体層(発光部)2を形成し、その上に反射電極層4を成膜し、該反射電極層4を覆うように、キャップ層5(酸化物透明導電層51及び金属層52の積層を3セット)及び共晶(Au)層6を成膜した段階のものである。

【0044】

比較例1による半導体素子は、図10に示すように、本実施例によるキャップ層5の代わりに、膜厚6000ÅのTiW膜単層からなるキャップ層53を成膜し、その上に共晶(Au)層6を成膜した段階のものであり、比較例2による半導体素子は、図11に示すように、本実施例によるキャップ層5の代わりに、膜厚1000ÅのPt膜54と膜厚1000ÅのTiW膜52との積層を1セットとし、それを3セット成膜したものからなるキャップ層55を成膜し、その上に共晶(Au)層6を成膜した段階のものである。

【0045】

クラックの発生の評価は、キャップ層形成後、硝酸の中で1分放置し、Agの侵食(クラック部分から硝酸が入り込み、AgがエッチングされてAgのラインが後退)があった場合は成膜時の応力によるクラック発生があると判断することにより行った。この評価方法では、比較例1や比較例2では、ほぼ全周囲において侵食の発生が観察されたが、本実施例による半導体素子では、Agの侵食がほとんど観察されなかった。したがって、比較例1及び比較例2ではクラックが発生したが、本実施例では、クラックが発生しなかったものと考えられる。

【0046】

また、支持基板10と貼りあわせた後(図7に示す状態)に、クラック発生を写真観察により判断した。この写真観察では、もとのAgのラインよりAgがはみでていたらクラックが発生したと判断した。この場合にも、比較例1及び比較例2では、図10及び図11に示すように、キャップ層53、55のエッジ部分でクラックCRが観察されたが、本実施例によるキャップ層5のエッジ部分にはクラックは観察されなかった。

【0047】

なお、その後の工程によるクラックの発生は、Agがクラックよりマイグレーションし、リークになるとPL発光強度が減少したり、p−nジャンクション部分にAgが析出してきたりすることで判断が可能である。

【0048】

以上、本発明の実施例によれば、反射電極層4を覆うキャップ層5を酸化物透明導電層51と金属、合金または金属窒化物からなる金属層52の積層構造とした。これにより、金属層52にかかる熱ひずみの緩和を透明導電膜51が行うことができる。よって、キャップ層5のクラックなどの欠陥が入りにくくなり、Agのマイグレーションが抑えられ、素子の特性、信頼性を向上させることができる。

【0049】

さらに、酸化物透明導電層51を100〜1000Åの結晶性の低い非晶質または微結晶(結晶子が500Å以下)とすることで熱ひずみの緩和を起こしやすくすることができる。

【0050】

また、本発明の実施例によれば、酸化物透明導電層51を反射電極層4と接する第1層目とすることで、反射電極層4の周りに反射電極層4よりも接触抵抗の高い領域が形成される。よって、通常の通電時には電気が流れないが、高電圧印加時に通電パスとなりうる領域を形成することが可能なる。これにより、瞬時の高電圧印加時の信頼性(静電耐圧)を向上させることができる。

【0051】

また、上述の実施例では、成長基板1としてサファイア基板を用いたが、これ以外にもGaN基板やSiC基板などを成長基板として用いることができる。また、半導体層2の材料はGaNに限らず、AlGaInPや、ZnO等でもよい。

【0052】

以上、実施例、及び変形例に沿って本発明を説明したが、本発明はこれらに限定されるものではない。種々の変更、改良、組み合わせ等が可能なことは当業者には自明であろう。

【0053】

例えば、本発明の実施例はAg層42が反射電極層4に含まれれば、図12に示す成長基板1を除去しないフリップチップタイプや、図13に示す成長基板1としてGaNやSiCなどの透明導電性基板を用いたジャンクションダウンタイプにも適用可能である。

【符号の説明】

【0054】

1…サファイア基板、2…GaN系半導体層(発光部)、4…反射電極層、5…キャップ層、6…、7…、10…シリコン(Si)基板、16…n側電極(配線電極)、20…バッファ層、21…アンドープGaN層、22…Siドープn型GaN層、23…歪緩和層、24…活性層、25…p型AlGaN層(クラッド層)、26…p型GaN層(コンタクト層)、41…Ni層、42…Ag層、51…酸化物透明導電層(第1キャップ層)、52…金属層(第2キャップ層)、53、55…キャップ層、54…Pt層、101…窒化物半導体発光素子(LED素子)

【特許請求の範囲】

【請求項1】

第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、

前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、

前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、

前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、

共晶層を介して前記キャップ層と結合する支持基板と

を有する半導体素子。

【請求項2】

前記第1キャップ層の厚さは100Åよりも厚く、1000Å以下である請求項1記載の半導体素子。

【請求項3】

前記透明導電膜は、結晶子の大きさが500Å以下の非晶質又は微結晶である請求項1又は2記載の半導体素子。

【請求項4】

前記金属層は、金属、合金又は金属窒化物からなる請求項1〜3のいずれか1項に記載の半導体素子。

【請求項1】

第1導電型の第1の半導体層と、該第1の半導体層の上に形成される活性層と、該活性層の上に形成される第2導電型の第2の半導体層とを含む半導体積層構造と、

前記第1の半導体層又は前記第2の半導体層の一方に接して形成される配線電極層と、

前記第1の半導体層又は前記第2の半導体層の前記配線電極層が形成されていない他方に接して形成されるAgを含む反射電極層と、

前記反射電極層を覆って形成される透明導電膜からなる第1キャップ層と、該第1キャップ層を覆って形成され、金属、合金又は金属窒化物からなる第2キャップ層との積層を少なくとも2セット以上含むキャップ層と、

共晶層を介して前記キャップ層と結合する支持基板と

を有する半導体素子。

【請求項2】

前記第1キャップ層の厚さは100Åよりも厚く、1000Å以下である請求項1記載の半導体素子。

【請求項3】

前記透明導電膜は、結晶子の大きさが500Å以下の非晶質又は微結晶である請求項1又は2記載の半導体素子。

【請求項4】

前記金属層は、金属、合金又は金属窒化物からなる請求項1〜3のいずれか1項に記載の半導体素子。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【公開番号】特開2013−115341(P2013−115341A)

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願番号】特願2011−262177(P2011−262177)

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

【公開日】平成25年6月10日(2013.6.10)

【国際特許分類】

【出願日】平成23年11月30日(2011.11.30)

【出願人】(000002303)スタンレー電気株式会社 (2,684)

【Fターム(参考)】

[ Back to top ]