回路装置

【課題】素子から出力される信号の絶対的な量がより容易に把握できるようにする。

【解決手段】電源103より供給される電圧が印加された第1素子101より出力される信号量を検出する第1検出回路104と、電源103より供給される電圧が印加された第2素子102より出力される信号量を検出する第2検出回路105と、第1検出回路104が検出した信号量と第2検出回路105が検出した信号量との差分に対応する信号を出力する差分回路106とを備える。

【解決手段】電源103より供給される電圧が印加された第1素子101より出力される信号量を検出する第1検出回路104と、電源103より供給される電圧が印加された第2素子102より出力される信号量を検出する第2検出回路105と、第1検出回路104が検出した信号量と第2検出回路105が検出した信号量との差分に対応する信号を出力する差分回路106とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、MEMSや圧電素子などの素子を駆動するための回路装置に関するものである。

【背景技術】

【0002】

近年、MEMS(Micro Electro Mechanical System)技術を用いて作製された各種センサやスイッチなどが、盛んに研究開発されている。MEMS技術を用いて作製された各種センサやスイッチなどの素子を使用する場合の従来例について、図13を用いて説明する。これらの素子は、駆動用電源1301より素子1302に対して電圧を供給して素子1302を動作させ、素子1302より出力される信号を検出回路1303で検出している。

【0003】

以下、MEMS技術を用いて作製された静電アクチュエータを例に、より詳細に説明する(特許文献1参照)。図14は、静電アクチュエータの構成を示す構成図である。静電アクチュエータは、基板1401の上に支持部1402により支持された梁部1403を備え、基板1401に形成された固定電極1404に対向し、梁部1403に可動電極1405を備えている。また、固定電極1404の可動電極1405との対向面には、絶縁膜1406が形成されている。また、固定電極1404および可動電極1405には、マトリクススイッチ1407およびスイッチ1408を介し、駆動用電源1409および検出回路1410が接続されている。

【0004】

図14では、スイッチ1408は、駆動用電源1409に接続され、固定電極1404に駆動用電源1409が接続され、可動電極1405は0ボルトに接続されている。このように接続して固定電極1404に駆動用電源1409から電圧を印加すると、静電引力によって可動電極1405が固定電極1404の側に引き寄せられる。引き寄せられる可動電極1405は、最終的に図15に示すように、絶縁膜1406に接触して動作を停止する。

【0005】

ここで、可動電極1405の固定電極1404との対向面の面積をS、可動電極1405と固定電極1404との間の空間の誘電率をε、可動電極1405と固定電極1404との間の距離、すなわち絶縁膜1406の膜厚をdとすると、図15に示す静電アクチュエータの静電容量C1は、「C1=εS/d・・・(1)」により計算できる。

【0006】

次に、可動電極1405が絶縁膜1406に接触した状態で、スイッチ1408を検出回路1410に切り替えれば、絶縁膜1406に蓄積された電荷量を検出回路によって検出することができる。このようにして検出した電荷量が一定値を超えた場合、マトリクススイッチ1407の接続状態を変更し、可動電極1405に駆動用電源1409を接続して電圧を印加し、固定電極1404を0Vに接続する。この接続切り替えにより、絶縁膜1406に対する電荷の蓄積が解消される。この接続切り替えは、蓄積された電荷によって可動電極1405絶縁膜1406から離れなくなる現象(特許文献1中でスティクションと表現している)を防ぐ効果がある。なお、特許文献1では、絶縁膜1406に蓄積される電荷量を低減させるために、駆動用の電圧として正あるいは負のバイポーラ電圧を推奨している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−242607号公報

【特許文献2】特許第4373345号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述した技術では、入力信号に対して素子から出力される信号の絶対的な量を把握(測定)することが容易ではないという問題があった。例えば、MEMS素子では、上述のことにより、検出できる信号量により可動部の変位を正確に把握することが困難である。前述したアクチュエータの場合、可動電極1405を絶縁膜1406に接触させて使用しており、固定電極1404と可動電極1405との距離dは常に一定の値となり、可動電極1405を中空に浮かせた状態に適用することができない。

【0009】

また、可動電極を中空に浮かせた状態で使用する例として、MEMS技術を用いて作製したMEMSミラーがある(特許文献2参照)。この技術では、MEMSミラーを駆動するための駆動電圧とMEMSミラーの傾斜角度との関係を求めるために、MEMSミラーを微小面積に分割して各々の静電容量を検出し、検出した静電容量の和を計算することで可動するミラーと固定電極(駆動電極)との間の静電容量を求め、傾斜角を求めるようにしている。この技術によれば、可動部の変位を正確に把握することを可能としている。

【0010】

しかし特許文献2の方法では、MEMSミラーを微小面積に分割し、分割した面積毎に静電容量を検出する必要があるため、手間がかかるという問題があった。なお、特許文献2では、微小面積毎の静電容量を具体的に検出する方法については記載されていないため、MEMSミラーと駆動電極との距離を求める方法が不明である。

【0011】

本発明は、以上のような問題点を解消するためになされたものであり、素子から出力される信号の絶対的な量がより容易に把握できるようにすることを目的とする。

【課題を解決するための手段】

【0012】

本発明に係る回路装置は、入力信号に対して既知の信号量を出力する第1素子と、入力信号に対して未知の信号量を出力する第2素子と、第1素子および第2素子に同じ入力信号を供給する電源と、電源より供給される電圧が印加された第1素子より出力される信号量を検出する第1検出回路と、電源より供給される電圧が印加された第2素子より出力される信号量を検出する第2検出回路と、第1検出回路が検出した信号量と第2検出回路が検出した信号量との差分に対応する信号を出力する差分回路とを少なくとも備える。

【0013】

上記回路装置において、第1素子より第1検出回路に出力される信号の切り替えを行う第1スイッチと、第2素子より第2検出回路に出力される信号の切り替えを行う第2スイッチとを備えるようにしてもよい。

【0014】

上記回路装置において、第1素子および第2素子は、同一の構造を有するものであってもよい。

【0015】

上記回路装置において、電源は、周期的に変化する電圧を供給するものであればよい。

【0016】

上記回路装置において、例えば、第1素子は、容量素子から構成され、第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されている。

【発明の効果】

【0017】

以上説明したように、本発明によれば、入力信号に対して既知の信号量を出力する第1素子の出力と、入力信号に対して未知の信号量を出力する第2素子の出力との差分を取るようにしたので、素子から出力される信号の絶対的な量がより容易に把握できるようになるという優れた効果が得られる。

【図面の簡単な説明】

【0018】

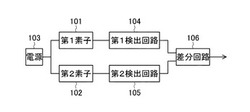

【図1】図1は、本発明の実施の形態1における回路装置の構成を示す構成図である。

【図2】図2は、本発明の実施例1における回路装置の構成を示す回路図である。

【図3】図3は、実施例1における静電アクチュエータ202の構成を示す構成図である。

【図4】図4は、実施例1における回路装置の動作を説明するためのタイミングチャートである。

【図5】図5は、固定電極224と可動電極225との距離dと信号量Voutとの関係を示す特性図である。

【図6】図6は、本発明の実施例2における回路装置の構成を示す回路図である。

【図7】図7は、第1素子601の回路構成例を示す回路図である。

【図8】図8は、本発明の実施例3における回路装置の構成を示す回路図である。

【図9】図9は、本発明の実施例4における回路装置の構成を示す回路図である。

【図10】図10は、第1スイッチ907,第2スイッチ908,第3スイッチ931,第4スイッチ932の回路構成例を示す回路図である。

【図11】図11は、本発明の実施例5における回路装置の構成を示す回路図である。

【図12】図12は、本発明の実施の形態2における回路装置の構成を示す構成図である。

【図13】図13は、MEMS技術を用いて作製された素子の構成例を示す構成図である。

【図14】図14は、静電アクチュエータの構成を示す構成図である。

【図15】図15は、静電アクチュエータの構成を示す構成図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態について図を参照して説明する。

【0020】

[実施の形態1]

はじめに、本発明の実施の形態1について説明する。図1は、本発明の実施の形態1における回路装置の構成を示す構成図である。この回路装置は、入力信号に対して既知の信号量を出力する第1素子101と、入力信号に対して未知の信号量を出力する第2素子102と、第1素子101および第2素子102に同じ入力信号を供給する電源103と、電源103より供給される電圧が印加された第1素子101より出力される信号量を検出する第1検出回路104と、電源103より供給される電圧が印加された第2素子102より出力される信号量を検出する第2検出回路105と、第1検出回路104が検出した信号量と第2検出回路105が検出した信号量との差分に対応する信号を出力する差分回路106とを備える。

【0021】

この回路装置によれば、第1素子101は、入力信号に対して既知の信号量を出力するため、第1検出回路104より出力される信号量は、既知の値となる。一方、第2素子102は、入力信号に対して出力される信号量は不明であるが、第2検出回路105より出力される信号量は、差分回路106で第1検出回路104より出力される信号量との差分が取られる。この結果、第2検出回路105より出力される信号量は、差分回路106より出力される差分値と、既知である第1検出回路104より出力される信号量とにより、求めることができる。また、本実施の形態1によれば、第2素子102より複数の信号を取り出すことが必要ではない。このように、本実施の形態1によれば、第2素子102から出力される信号の絶対的な量がより容易に把握できるようになる。

【0022】

以下、実施例を用いてより詳細な説明をする。

【0023】

[実施例1]

はじめに、実施例1について説明する。図2は、実施例1における回路装置の構成を示す回路図である。この回路装置は、半導体容量素子(第1素子)201と、MEMS技術を用いて作製した静電アクチュエータ(第2素子)202と、パルス電圧P1を出力する電源203とを備える。静電アクチュエータ202は、図3に示すように、基板221の上に支持部212により支持された梁部223を備え、基板221に形成された固定電極224に対向し、梁部223に可動電極225を備えている。可動電極225が、端子210に接続されている。ここで、半導体容量素子201の容量値は、静電アクチュエータ202の容量値より小さい値であることが望ましい。

【0024】

また、この回路装置は、半導体容量素子201より出力される信号量を検出する第1検出回路204と、静電アクチュエータ202より出力される信号量を検出する第2検出回路205と、第1検出回路204が検出した信号量と第2検出回路205が検出した信号量との差分に対応する信号を出力する差分回路206とを備える。第1検出回路204は、入力側のNMOSFETと、半導体容量と、定電流源に接続するPMOSFETとで構成されている。第2検出回路205も同様の構成であり、各FETのゲート長,ゲート幅などの物理的なパラメータや、半導体容量値、定電流源の電流値は、両者において同じ値とする。また、差分回路206は、抵抗素子およびオペアンプ回路から構成されている。

【0025】

上述した構成に加え、実施例1では、半導体容量素子201と第1検出回路204との間に第1スイッチ207を備え、静電アクチュエータ202と第2検出回路205との間に第2スイッチ208を備えている。

【0026】

以下、実施例1の回路装置の動作について、図4を用いて説明する。図4は、P1,S1,S2,D1,D2,Voutのタイミングチャートであり、横軸は経過時間、縦軸は電圧値を示している。まず、P1は、電源203からの出力であり、周期が一定のパルス電圧である。また、S1は、第1スイッチ207および第2スイッチ208のオンおよびオフを切り替える(ゲート電極に入力される)信号である。また、S2は、第1検出回路204および第2検出回路205の入力側のNMOSFETのゲート電極に入力する信号である。また、D1は、第1検出回路204で検出される信号量であり、D2は、第2検出回路205で検出される信号量である。また、Voutは、差分回路206からの出力である。

【0027】

図4に示すように、P1の電圧値があるタイミングで0Vになった時(a)、S1(第1スイッチ207および第2スイッチ208)をONする(b)。S1がONになることで、半導体容量素子201に蓄積された電荷が、第1スイッチ207を介して第1検出回路204の半導体容量に移動する。同様に、静電アクチュエータ202に蓄積された電荷が、第2スイッチ208を介して第2検出回路205の半導体容量に移動する。これらの結果、第1検出回路204および第2検出回路205では、各電荷量を信号量D1および信号量D2として検出して出力する(d)。なお、D1およびD2は電圧値である。

【0028】

次に、差分回路206で、D1とD2の差分を計算し、信号量Voutを電圧値として出力する(e)。この後、S2をONし、第1検出回路204および第2検出回路205のNMOSFETをオン状態とし、第1検出回路204および第2検出回路205の半導体容量に蓄積されている電荷量を、NMOSFETを介してグランド電極に移動させて蓄積されている電荷量を0にする(c)。

【0029】

なお、電源203から出力される電圧は、パルス電圧以外に、三角波、正弦波などのように周期的に電圧が変化するものであれば如何なる電圧であっても問題ない。また、実施例1において、D1,D2,Voutは電圧値としたが、電圧値以外に、電流、電荷、容量、あるいはインダクタンス、抵抗といった信号量を用いても問題ないことは明らかである。

【0030】

上述した実施の形態1によれば、以下に示すように、静電アクチュエータ202の電極間の距離を、Voutの変化として検出することができる。まず、静電アクチュエータ202の固定電極224と可動電極225との距離をdとする。また、固定電極224と可動電極225との間に蓄積される静電容量をC1とする。また、可動電極225の固定電極224との対向面の面積Sを100μm2とする。また、固定電極224と可動電極225との間の空間の誘電率εを8.85418782×10-12F/mとする。また、固定電極224と可動電極225との距離dが、0.22μmから0.44μmまで変化した場合を考える。

【0031】

このとき、固定電極224と可動電極225との間に蓄積される静電容量C1は、「C1=εS/d・・・(1)」に基づいて変化し、信号量Voutも変化する。図5に、信号量Voutと距離dとの関係を示す。図5に示すように、距離dの変化を、信号量Voutの変化として検出することができる。従って、Voutにより、静電アクチュエータ202における可動電極225の位置を検出することが可能である。

【0032】

なお、実施例1において、電源203から出力されるパルス電圧P1の電圧値やパルスの幅の調整を行うためのフィードバック回路を新たに設け、このフィードバック回路にVoutを入力し、フィードバック回路がVoutをもとに電源203から出力されるパルス電圧P1の電圧値やパルスの幅の調整することで、静電アクチュエータ202の可動電極225を所望の位置に駆動できることは言うまでも無い。フィードバック回路が、実施例1の回路装置を構成している半導体装置と同一の半導体基板上にモノリシックに形成されていてもよい。また、これらが、ディスクリートに構成されていてもよい。例えば、フィードバック回路がパーソナルコンピュータ等の演算機能を持つ計算機であってもよいことは言うまでも無い。

【0033】

また、実施例1のように、第2素子を静電アクチュエータなどの機械的な可動構造部を持つ素子とした場合、一般的に可動構造部の共振周波数は高くとも数百kHz程度であることが知られている。一方、電源は、例えば数MHzの周波数で動作させることが可能である。従って、第2素子の可動構造部の共振周波数よりも早い周期で変化する電圧を電源から供給することで、差分回路による信号量の出力要する時間を短縮することができる。また、第2素子の機械的な動作に影響を与えることなく差分回路による信号量が検出できるという利点がある。

【0034】

ここで、実施例1の静電アクチュエータ202として、図13,図14を用いて説明した静電アクチュエータを用いてもよいことは言うまでもない。実施例1によれば、固定電極を絶縁膜に接触させる必要がなく、可動電極を中空に浮いた状態でも使用できるという利点がある。また、特許文献1では、絶縁膜に蓄積される電荷量を低減させるために駆動用の電圧として正あるいは負のバイポーラ電圧を推奨しているが、本発明では絶縁膜に蓄積される電荷量を低減させる必要がないため、第2素子に供給する電圧が正あるいは負のバイポーラ電圧である必要はない。

【0035】

また、実施例1の静電アクチュエータの代わりに、特許文献2のMEMSミラーを用いてもよいことは言うまでもない。この場合、MEMSミラーを微小面積に分割することなく、MEMSミラーを駆動させる駆動電極(固定電極)とMEMSミラーとの間の静電容量を検出すればよいので、ミラーを微小面積に分割した面積毎に静電容量を検出する必要はなく、手間を省くことができる。このように、本発明は、第2素子として、静電アクチュエータに限らず、MEMS技術を用いて作製されたスイッチ、圧力センサ、加速度センサ、イオンセンサなどの様々な素子に適用可能である。

【0036】

また、第2素子が、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路と同一の半導体基板上に形成した構造であっても問題ない。また、第2素子が、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路と別の半導体基板上に形成した構造であっても問題ない。

【0037】

さらに、電源、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路は、同じ半導体基板上に形成されていてもよい。また、電源、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路が別の半導体基板上に形成されていても問題ないことは言うまでもない。

【0038】

[実施例2]

次に、実施例2について説明する。図6は、実施例2における回路装置の構成を示す回路図である。この回路装置は、第1素子601と、静電アクチュエータ(第2素子)202と、電源203と、第1検出回路604と、第2検出回路605と、差分回路206と、第1スイッチ207と、第2スイッチ208を備えている。本実施例では、まず、第1素子601を図7に示す回路構成とした。また、実施例1の第1検出回路204を構成している容量素子を図7に示す回路構成の回路641とした第1検出回路604とし、実施例1の第2検出回路205を構成している容量素子を図7に示す回路構成の回路651とした第2検出回路605としている。他の構成は、実施例1と同様である。

【0039】

図7に示す回路構成は、電源701,NOT回路702,AND回路703,およびNMOSFET704から構成され、容量C1,C2,C3,C4,C5,C6,C6,C7,C8を選択して切り替え可能としている。この結果、実施例2によれば、静電アクチュエータ202の特性に応じて第1素子601の値を適切かつ簡単に設定することが可能になるという利点がある。同様に、第1検出回路604および第2検出回路605の出力(信号量)を、静電アクチュエータ202の特性に応じて適切かつ簡単に設定することが可能になるという利点がある。

【0040】

[実施例3]

次に,実施例3について説明する。図8は、実施例3における回路装置の構成を示す回路図である。この回路装置は、半導体容量素子(第1素子)201と、静電アクチュエータ(第2素子)202と、第1検出回路204と、第2検出回路205と、差分回路206と、第1スイッチ207と、第2スイッチ208を備えている。これらの構成は、実施例1と同様である。

【0041】

実施例3では、図2を用いて説明した実施例1の電源203と半導体容量素子201および静電アクチュエータ202と電源203との間のダイオードを、PMOSFET831,PMOSFET832としている。また、PMOSFET831およびPMOSFET832に各々電源を供給する電源803を用いている。このように構成することで、半導体容量素子201と第1検出回路204との間の信号量と、静電アクチュエータ202と第2検出回路205との間の信号量との間の影響を低減することができる。また、ダイオードを用いる場合に比較して、実施例3によれば、消費電力を低減できるようになる。

【0042】

[実施例4]

次に、実施例4について説明する。図9は、実施例4における回路装置の構成を示す回路図である。この回路装置は、実施例3の回路装置の第1スイッチ207,第2スイッチ208,PMOSFET831,およびPMOSFET832を、図10に示す回路構成とした第1スイッチ907,第2スイッチ908,第3スイッチ931,第4スイッチ932に変更している。

【0043】

図10に示すスイッチは、NMOSFET1001,PMOSFET1002,NMOSFET1003,PMOSFET1004,NOT回路1005,NOT回路1006,NOT回路1007,抵抗素子1008,およびダイオード素子1009を組み合わせたCMOSスイッチである。

【0044】

このようにCMOSスイッチより構成することで、単体のMOSFETスイッチを用いる場合と比較し、オン状態における抵抗値を下げることが可能となり、消費電力を低減できるメリットがある。また、図10に示すような回路構成のCMOSとすることで、第1スイッチ907および第2スイッチ908が、ONまたはOFFのどちらかのみの状態を取るため、単体のMOSFETスイッチを用いる場合と比較し、スイッチとしての動作をより安定させることが可能である。

【0045】

[実施例5]

次に、実施例5について説明する。図11は、実施例5における回路装置の構成を示す回路図である。この回路装置は、実施例4における回路装置の半導体容量素子201,第1検出回路204の容量素子,第2検出回路205の容量素子を、図7に示す回路構成とした第1素子601,回路641,回路651に変更し、第1検出回路204および第2検出回路205を、第1検出回路604および第2検出回路605としている。他の構成は、実施例4と同様である。

【0046】

実施例5によれば、まず、実施例2と同様に、静電アクチュエータ202の特性に応じ、第1素子601の値を適切かつ簡単に設定することが可能になるという利点がある。また、第1検出回路604および第2検出回路605の出力(信号量)を、静電アクチュエータ202の特性に応じて適切かつ簡単に設定することが可能になるという利点がある。また、実施例5によれば、実施例4と同様に、CMOSスイッチの回路構成を用いることで、消費電流を減らすことができる。

【0047】

[実施の形態2]

次に、本発明の実施の形態2について説明する。図12は、本発明の実施の形態2における回路装置の構成を示す構成図である。この回路装置は、入力信号に対して未知の信号量を出力する素子1201と、素子1201に入力信号を供給する電源1202と、電源1202より供給される電圧が印加された素子1201より出力される信号量を検出する検出回路1203と、入力信号が未入力の素子1201より出力される信号量を検出回路1203で検出した初期信号量が記憶されている記憶部1204と、検出回路1203が検出した信号量と記憶部1204より出力される初期信号量との差分に対応する信号を出力する差分回路1205とを少なくとも備える。なお、記憶部1204には、様々な記憶方法による手段を組み合わせ可能な範囲で適用可能であることは言うまでもない。

【0048】

素子1201,電源1202,検出回路1203,および差分回路1205は、前述した実施の形態1における第2素子102,電源103,第2検出回路105,および差分回路106と同様である。

【0049】

この回路装置では、差分回路1205において、電源1202より供給される電圧が印加された素子1201より出力される信号量より初期信号量が差し引かれる。ここで、初期信号量は、検出回路1203で検出される入力信号が未入力の素子1201より出力される信号量である。従って、差分回路1205から出力される信号量は、電源1202より供給される入力信号(電圧)のみに対応する絶対的なものとなる。また、本実施の形態2によれば、素子1201より複数の信号を取り出すことが必要ではない。このように、本実施の形態2によれば、素子1201から出力される信号の絶対的な量がより容易に把握できるようになる。

【0050】

なお、本発明は以上に説明した実施の形態に限定されるものではなく、本発明の技術的思想内で、当分野において通常の知識を有する者(当業者)により、多くの組み合わせおよび変形が実施可能であることは明白である。例えば、上述では、第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されているものとしたが、これに限るものではない。第2素子は、例えば圧電素子から構成されていてもよいことは、当業者であれば容易に理解できる。また、上述では、第1素子は、容量素子から構成し、検出回路においても容量素子を用いるようにしたが、これに限るものではなく、インダクタンスおよび抵抗なおどの半導体素子であってもよく、第2素子と同様の構成のMEMS素子であってもよい。いずれにしても、第1素子は、入力信号に対して既知の信号量を出力するものであればよい。

【符号の説明】

【0051】

101…第1素子、102…第2素子、103…電源、104…第1検出回路、105…第2検出回路、106…差分回路、1201…素子、1202…電源、1203…検出回路、1204…記憶部、1205…差分回路。

【技術分野】

【0001】

本発明は、MEMSや圧電素子などの素子を駆動するための回路装置に関するものである。

【背景技術】

【0002】

近年、MEMS(Micro Electro Mechanical System)技術を用いて作製された各種センサやスイッチなどが、盛んに研究開発されている。MEMS技術を用いて作製された各種センサやスイッチなどの素子を使用する場合の従来例について、図13を用いて説明する。これらの素子は、駆動用電源1301より素子1302に対して電圧を供給して素子1302を動作させ、素子1302より出力される信号を検出回路1303で検出している。

【0003】

以下、MEMS技術を用いて作製された静電アクチュエータを例に、より詳細に説明する(特許文献1参照)。図14は、静電アクチュエータの構成を示す構成図である。静電アクチュエータは、基板1401の上に支持部1402により支持された梁部1403を備え、基板1401に形成された固定電極1404に対向し、梁部1403に可動電極1405を備えている。また、固定電極1404の可動電極1405との対向面には、絶縁膜1406が形成されている。また、固定電極1404および可動電極1405には、マトリクススイッチ1407およびスイッチ1408を介し、駆動用電源1409および検出回路1410が接続されている。

【0004】

図14では、スイッチ1408は、駆動用電源1409に接続され、固定電極1404に駆動用電源1409が接続され、可動電極1405は0ボルトに接続されている。このように接続して固定電極1404に駆動用電源1409から電圧を印加すると、静電引力によって可動電極1405が固定電極1404の側に引き寄せられる。引き寄せられる可動電極1405は、最終的に図15に示すように、絶縁膜1406に接触して動作を停止する。

【0005】

ここで、可動電極1405の固定電極1404との対向面の面積をS、可動電極1405と固定電極1404との間の空間の誘電率をε、可動電極1405と固定電極1404との間の距離、すなわち絶縁膜1406の膜厚をdとすると、図15に示す静電アクチュエータの静電容量C1は、「C1=εS/d・・・(1)」により計算できる。

【0006】

次に、可動電極1405が絶縁膜1406に接触した状態で、スイッチ1408を検出回路1410に切り替えれば、絶縁膜1406に蓄積された電荷量を検出回路によって検出することができる。このようにして検出した電荷量が一定値を超えた場合、マトリクススイッチ1407の接続状態を変更し、可動電極1405に駆動用電源1409を接続して電圧を印加し、固定電極1404を0Vに接続する。この接続切り替えにより、絶縁膜1406に対する電荷の蓄積が解消される。この接続切り替えは、蓄積された電荷によって可動電極1405絶縁膜1406から離れなくなる現象(特許文献1中でスティクションと表現している)を防ぐ効果がある。なお、特許文献1では、絶縁膜1406に蓄積される電荷量を低減させるために、駆動用の電圧として正あるいは負のバイポーラ電圧を推奨している。

【先行技術文献】

【特許文献】

【0007】

【特許文献1】特開2007−242607号公報

【特許文献2】特許第4373345号公報

【発明の概要】

【発明が解決しようとする課題】

【0008】

しかしながら、上述した技術では、入力信号に対して素子から出力される信号の絶対的な量を把握(測定)することが容易ではないという問題があった。例えば、MEMS素子では、上述のことにより、検出できる信号量により可動部の変位を正確に把握することが困難である。前述したアクチュエータの場合、可動電極1405を絶縁膜1406に接触させて使用しており、固定電極1404と可動電極1405との距離dは常に一定の値となり、可動電極1405を中空に浮かせた状態に適用することができない。

【0009】

また、可動電極を中空に浮かせた状態で使用する例として、MEMS技術を用いて作製したMEMSミラーがある(特許文献2参照)。この技術では、MEMSミラーを駆動するための駆動電圧とMEMSミラーの傾斜角度との関係を求めるために、MEMSミラーを微小面積に分割して各々の静電容量を検出し、検出した静電容量の和を計算することで可動するミラーと固定電極(駆動電極)との間の静電容量を求め、傾斜角を求めるようにしている。この技術によれば、可動部の変位を正確に把握することを可能としている。

【0010】

しかし特許文献2の方法では、MEMSミラーを微小面積に分割し、分割した面積毎に静電容量を検出する必要があるため、手間がかかるという問題があった。なお、特許文献2では、微小面積毎の静電容量を具体的に検出する方法については記載されていないため、MEMSミラーと駆動電極との距離を求める方法が不明である。

【0011】

本発明は、以上のような問題点を解消するためになされたものであり、素子から出力される信号の絶対的な量がより容易に把握できるようにすることを目的とする。

【課題を解決するための手段】

【0012】

本発明に係る回路装置は、入力信号に対して既知の信号量を出力する第1素子と、入力信号に対して未知の信号量を出力する第2素子と、第1素子および第2素子に同じ入力信号を供給する電源と、電源より供給される電圧が印加された第1素子より出力される信号量を検出する第1検出回路と、電源より供給される電圧が印加された第2素子より出力される信号量を検出する第2検出回路と、第1検出回路が検出した信号量と第2検出回路が検出した信号量との差分に対応する信号を出力する差分回路とを少なくとも備える。

【0013】

上記回路装置において、第1素子より第1検出回路に出力される信号の切り替えを行う第1スイッチと、第2素子より第2検出回路に出力される信号の切り替えを行う第2スイッチとを備えるようにしてもよい。

【0014】

上記回路装置において、第1素子および第2素子は、同一の構造を有するものであってもよい。

【0015】

上記回路装置において、電源は、周期的に変化する電圧を供給するものであればよい。

【0016】

上記回路装置において、例えば、第1素子は、容量素子から構成され、第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されている。

【発明の効果】

【0017】

以上説明したように、本発明によれば、入力信号に対して既知の信号量を出力する第1素子の出力と、入力信号に対して未知の信号量を出力する第2素子の出力との差分を取るようにしたので、素子から出力される信号の絶対的な量がより容易に把握できるようになるという優れた効果が得られる。

【図面の簡単な説明】

【0018】

【図1】図1は、本発明の実施の形態1における回路装置の構成を示す構成図である。

【図2】図2は、本発明の実施例1における回路装置の構成を示す回路図である。

【図3】図3は、実施例1における静電アクチュエータ202の構成を示す構成図である。

【図4】図4は、実施例1における回路装置の動作を説明するためのタイミングチャートである。

【図5】図5は、固定電極224と可動電極225との距離dと信号量Voutとの関係を示す特性図である。

【図6】図6は、本発明の実施例2における回路装置の構成を示す回路図である。

【図7】図7は、第1素子601の回路構成例を示す回路図である。

【図8】図8は、本発明の実施例3における回路装置の構成を示す回路図である。

【図9】図9は、本発明の実施例4における回路装置の構成を示す回路図である。

【図10】図10は、第1スイッチ907,第2スイッチ908,第3スイッチ931,第4スイッチ932の回路構成例を示す回路図である。

【図11】図11は、本発明の実施例5における回路装置の構成を示す回路図である。

【図12】図12は、本発明の実施の形態2における回路装置の構成を示す構成図である。

【図13】図13は、MEMS技術を用いて作製された素子の構成例を示す構成図である。

【図14】図14は、静電アクチュエータの構成を示す構成図である。

【図15】図15は、静電アクチュエータの構成を示す構成図である。

【発明を実施するための形態】

【0019】

以下、本発明の実施の形態について図を参照して説明する。

【0020】

[実施の形態1]

はじめに、本発明の実施の形態1について説明する。図1は、本発明の実施の形態1における回路装置の構成を示す構成図である。この回路装置は、入力信号に対して既知の信号量を出力する第1素子101と、入力信号に対して未知の信号量を出力する第2素子102と、第1素子101および第2素子102に同じ入力信号を供給する電源103と、電源103より供給される電圧が印加された第1素子101より出力される信号量を検出する第1検出回路104と、電源103より供給される電圧が印加された第2素子102より出力される信号量を検出する第2検出回路105と、第1検出回路104が検出した信号量と第2検出回路105が検出した信号量との差分に対応する信号を出力する差分回路106とを備える。

【0021】

この回路装置によれば、第1素子101は、入力信号に対して既知の信号量を出力するため、第1検出回路104より出力される信号量は、既知の値となる。一方、第2素子102は、入力信号に対して出力される信号量は不明であるが、第2検出回路105より出力される信号量は、差分回路106で第1検出回路104より出力される信号量との差分が取られる。この結果、第2検出回路105より出力される信号量は、差分回路106より出力される差分値と、既知である第1検出回路104より出力される信号量とにより、求めることができる。また、本実施の形態1によれば、第2素子102より複数の信号を取り出すことが必要ではない。このように、本実施の形態1によれば、第2素子102から出力される信号の絶対的な量がより容易に把握できるようになる。

【0022】

以下、実施例を用いてより詳細な説明をする。

【0023】

[実施例1]

はじめに、実施例1について説明する。図2は、実施例1における回路装置の構成を示す回路図である。この回路装置は、半導体容量素子(第1素子)201と、MEMS技術を用いて作製した静電アクチュエータ(第2素子)202と、パルス電圧P1を出力する電源203とを備える。静電アクチュエータ202は、図3に示すように、基板221の上に支持部212により支持された梁部223を備え、基板221に形成された固定電極224に対向し、梁部223に可動電極225を備えている。可動電極225が、端子210に接続されている。ここで、半導体容量素子201の容量値は、静電アクチュエータ202の容量値より小さい値であることが望ましい。

【0024】

また、この回路装置は、半導体容量素子201より出力される信号量を検出する第1検出回路204と、静電アクチュエータ202より出力される信号量を検出する第2検出回路205と、第1検出回路204が検出した信号量と第2検出回路205が検出した信号量との差分に対応する信号を出力する差分回路206とを備える。第1検出回路204は、入力側のNMOSFETと、半導体容量と、定電流源に接続するPMOSFETとで構成されている。第2検出回路205も同様の構成であり、各FETのゲート長,ゲート幅などの物理的なパラメータや、半導体容量値、定電流源の電流値は、両者において同じ値とする。また、差分回路206は、抵抗素子およびオペアンプ回路から構成されている。

【0025】

上述した構成に加え、実施例1では、半導体容量素子201と第1検出回路204との間に第1スイッチ207を備え、静電アクチュエータ202と第2検出回路205との間に第2スイッチ208を備えている。

【0026】

以下、実施例1の回路装置の動作について、図4を用いて説明する。図4は、P1,S1,S2,D1,D2,Voutのタイミングチャートであり、横軸は経過時間、縦軸は電圧値を示している。まず、P1は、電源203からの出力であり、周期が一定のパルス電圧である。また、S1は、第1スイッチ207および第2スイッチ208のオンおよびオフを切り替える(ゲート電極に入力される)信号である。また、S2は、第1検出回路204および第2検出回路205の入力側のNMOSFETのゲート電極に入力する信号である。また、D1は、第1検出回路204で検出される信号量であり、D2は、第2検出回路205で検出される信号量である。また、Voutは、差分回路206からの出力である。

【0027】

図4に示すように、P1の電圧値があるタイミングで0Vになった時(a)、S1(第1スイッチ207および第2スイッチ208)をONする(b)。S1がONになることで、半導体容量素子201に蓄積された電荷が、第1スイッチ207を介して第1検出回路204の半導体容量に移動する。同様に、静電アクチュエータ202に蓄積された電荷が、第2スイッチ208を介して第2検出回路205の半導体容量に移動する。これらの結果、第1検出回路204および第2検出回路205では、各電荷量を信号量D1および信号量D2として検出して出力する(d)。なお、D1およびD2は電圧値である。

【0028】

次に、差分回路206で、D1とD2の差分を計算し、信号量Voutを電圧値として出力する(e)。この後、S2をONし、第1検出回路204および第2検出回路205のNMOSFETをオン状態とし、第1検出回路204および第2検出回路205の半導体容量に蓄積されている電荷量を、NMOSFETを介してグランド電極に移動させて蓄積されている電荷量を0にする(c)。

【0029】

なお、電源203から出力される電圧は、パルス電圧以外に、三角波、正弦波などのように周期的に電圧が変化するものであれば如何なる電圧であっても問題ない。また、実施例1において、D1,D2,Voutは電圧値としたが、電圧値以外に、電流、電荷、容量、あるいはインダクタンス、抵抗といった信号量を用いても問題ないことは明らかである。

【0030】

上述した実施の形態1によれば、以下に示すように、静電アクチュエータ202の電極間の距離を、Voutの変化として検出することができる。まず、静電アクチュエータ202の固定電極224と可動電極225との距離をdとする。また、固定電極224と可動電極225との間に蓄積される静電容量をC1とする。また、可動電極225の固定電極224との対向面の面積Sを100μm2とする。また、固定電極224と可動電極225との間の空間の誘電率εを8.85418782×10-12F/mとする。また、固定電極224と可動電極225との距離dが、0.22μmから0.44μmまで変化した場合を考える。

【0031】

このとき、固定電極224と可動電極225との間に蓄積される静電容量C1は、「C1=εS/d・・・(1)」に基づいて変化し、信号量Voutも変化する。図5に、信号量Voutと距離dとの関係を示す。図5に示すように、距離dの変化を、信号量Voutの変化として検出することができる。従って、Voutにより、静電アクチュエータ202における可動電極225の位置を検出することが可能である。

【0032】

なお、実施例1において、電源203から出力されるパルス電圧P1の電圧値やパルスの幅の調整を行うためのフィードバック回路を新たに設け、このフィードバック回路にVoutを入力し、フィードバック回路がVoutをもとに電源203から出力されるパルス電圧P1の電圧値やパルスの幅の調整することで、静電アクチュエータ202の可動電極225を所望の位置に駆動できることは言うまでも無い。フィードバック回路が、実施例1の回路装置を構成している半導体装置と同一の半導体基板上にモノリシックに形成されていてもよい。また、これらが、ディスクリートに構成されていてもよい。例えば、フィードバック回路がパーソナルコンピュータ等の演算機能を持つ計算機であってもよいことは言うまでも無い。

【0033】

また、実施例1のように、第2素子を静電アクチュエータなどの機械的な可動構造部を持つ素子とした場合、一般的に可動構造部の共振周波数は高くとも数百kHz程度であることが知られている。一方、電源は、例えば数MHzの周波数で動作させることが可能である。従って、第2素子の可動構造部の共振周波数よりも早い周期で変化する電圧を電源から供給することで、差分回路による信号量の出力要する時間を短縮することができる。また、第2素子の機械的な動作に影響を与えることなく差分回路による信号量が検出できるという利点がある。

【0034】

ここで、実施例1の静電アクチュエータ202として、図13,図14を用いて説明した静電アクチュエータを用いてもよいことは言うまでもない。実施例1によれば、固定電極を絶縁膜に接触させる必要がなく、可動電極を中空に浮いた状態でも使用できるという利点がある。また、特許文献1では、絶縁膜に蓄積される電荷量を低減させるために駆動用の電圧として正あるいは負のバイポーラ電圧を推奨しているが、本発明では絶縁膜に蓄積される電荷量を低減させる必要がないため、第2素子に供給する電圧が正あるいは負のバイポーラ電圧である必要はない。

【0035】

また、実施例1の静電アクチュエータの代わりに、特許文献2のMEMSミラーを用いてもよいことは言うまでもない。この場合、MEMSミラーを微小面積に分割することなく、MEMSミラーを駆動させる駆動電極(固定電極)とMEMSミラーとの間の静電容量を検出すればよいので、ミラーを微小面積に分割した面積毎に静電容量を検出する必要はなく、手間を省くことができる。このように、本発明は、第2素子として、静電アクチュエータに限らず、MEMS技術を用いて作製されたスイッチ、圧力センサ、加速度センサ、イオンセンサなどの様々な素子に適用可能である。

【0036】

また、第2素子が、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路と同一の半導体基板上に形成した構造であっても問題ない。また、第2素子が、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路と別の半導体基板上に形成した構造であっても問題ない。

【0037】

さらに、電源、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路は、同じ半導体基板上に形成されていてもよい。また、電源、第1素子、第1および第2のスイッチ、第1および第2の検出回路、差分回路が別の半導体基板上に形成されていても問題ないことは言うまでもない。

【0038】

[実施例2]

次に、実施例2について説明する。図6は、実施例2における回路装置の構成を示す回路図である。この回路装置は、第1素子601と、静電アクチュエータ(第2素子)202と、電源203と、第1検出回路604と、第2検出回路605と、差分回路206と、第1スイッチ207と、第2スイッチ208を備えている。本実施例では、まず、第1素子601を図7に示す回路構成とした。また、実施例1の第1検出回路204を構成している容量素子を図7に示す回路構成の回路641とした第1検出回路604とし、実施例1の第2検出回路205を構成している容量素子を図7に示す回路構成の回路651とした第2検出回路605としている。他の構成は、実施例1と同様である。

【0039】

図7に示す回路構成は、電源701,NOT回路702,AND回路703,およびNMOSFET704から構成され、容量C1,C2,C3,C4,C5,C6,C6,C7,C8を選択して切り替え可能としている。この結果、実施例2によれば、静電アクチュエータ202の特性に応じて第1素子601の値を適切かつ簡単に設定することが可能になるという利点がある。同様に、第1検出回路604および第2検出回路605の出力(信号量)を、静電アクチュエータ202の特性に応じて適切かつ簡単に設定することが可能になるという利点がある。

【0040】

[実施例3]

次に,実施例3について説明する。図8は、実施例3における回路装置の構成を示す回路図である。この回路装置は、半導体容量素子(第1素子)201と、静電アクチュエータ(第2素子)202と、第1検出回路204と、第2検出回路205と、差分回路206と、第1スイッチ207と、第2スイッチ208を備えている。これらの構成は、実施例1と同様である。

【0041】

実施例3では、図2を用いて説明した実施例1の電源203と半導体容量素子201および静電アクチュエータ202と電源203との間のダイオードを、PMOSFET831,PMOSFET832としている。また、PMOSFET831およびPMOSFET832に各々電源を供給する電源803を用いている。このように構成することで、半導体容量素子201と第1検出回路204との間の信号量と、静電アクチュエータ202と第2検出回路205との間の信号量との間の影響を低減することができる。また、ダイオードを用いる場合に比較して、実施例3によれば、消費電力を低減できるようになる。

【0042】

[実施例4]

次に、実施例4について説明する。図9は、実施例4における回路装置の構成を示す回路図である。この回路装置は、実施例3の回路装置の第1スイッチ207,第2スイッチ208,PMOSFET831,およびPMOSFET832を、図10に示す回路構成とした第1スイッチ907,第2スイッチ908,第3スイッチ931,第4スイッチ932に変更している。

【0043】

図10に示すスイッチは、NMOSFET1001,PMOSFET1002,NMOSFET1003,PMOSFET1004,NOT回路1005,NOT回路1006,NOT回路1007,抵抗素子1008,およびダイオード素子1009を組み合わせたCMOSスイッチである。

【0044】

このようにCMOSスイッチより構成することで、単体のMOSFETスイッチを用いる場合と比較し、オン状態における抵抗値を下げることが可能となり、消費電力を低減できるメリットがある。また、図10に示すような回路構成のCMOSとすることで、第1スイッチ907および第2スイッチ908が、ONまたはOFFのどちらかのみの状態を取るため、単体のMOSFETスイッチを用いる場合と比較し、スイッチとしての動作をより安定させることが可能である。

【0045】

[実施例5]

次に、実施例5について説明する。図11は、実施例5における回路装置の構成を示す回路図である。この回路装置は、実施例4における回路装置の半導体容量素子201,第1検出回路204の容量素子,第2検出回路205の容量素子を、図7に示す回路構成とした第1素子601,回路641,回路651に変更し、第1検出回路204および第2検出回路205を、第1検出回路604および第2検出回路605としている。他の構成は、実施例4と同様である。

【0046】

実施例5によれば、まず、実施例2と同様に、静電アクチュエータ202の特性に応じ、第1素子601の値を適切かつ簡単に設定することが可能になるという利点がある。また、第1検出回路604および第2検出回路605の出力(信号量)を、静電アクチュエータ202の特性に応じて適切かつ簡単に設定することが可能になるという利点がある。また、実施例5によれば、実施例4と同様に、CMOSスイッチの回路構成を用いることで、消費電流を減らすことができる。

【0047】

[実施の形態2]

次に、本発明の実施の形態2について説明する。図12は、本発明の実施の形態2における回路装置の構成を示す構成図である。この回路装置は、入力信号に対して未知の信号量を出力する素子1201と、素子1201に入力信号を供給する電源1202と、電源1202より供給される電圧が印加された素子1201より出力される信号量を検出する検出回路1203と、入力信号が未入力の素子1201より出力される信号量を検出回路1203で検出した初期信号量が記憶されている記憶部1204と、検出回路1203が検出した信号量と記憶部1204より出力される初期信号量との差分に対応する信号を出力する差分回路1205とを少なくとも備える。なお、記憶部1204には、様々な記憶方法による手段を組み合わせ可能な範囲で適用可能であることは言うまでもない。

【0048】

素子1201,電源1202,検出回路1203,および差分回路1205は、前述した実施の形態1における第2素子102,電源103,第2検出回路105,および差分回路106と同様である。

【0049】

この回路装置では、差分回路1205において、電源1202より供給される電圧が印加された素子1201より出力される信号量より初期信号量が差し引かれる。ここで、初期信号量は、検出回路1203で検出される入力信号が未入力の素子1201より出力される信号量である。従って、差分回路1205から出力される信号量は、電源1202より供給される入力信号(電圧)のみに対応する絶対的なものとなる。また、本実施の形態2によれば、素子1201より複数の信号を取り出すことが必要ではない。このように、本実施の形態2によれば、素子1201から出力される信号の絶対的な量がより容易に把握できるようになる。

【0050】

なお、本発明は以上に説明した実施の形態に限定されるものではなく、本発明の技術的思想内で、当分野において通常の知識を有する者(当業者)により、多くの組み合わせおよび変形が実施可能であることは明白である。例えば、上述では、第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されているものとしたが、これに限るものではない。第2素子は、例えば圧電素子から構成されていてもよいことは、当業者であれば容易に理解できる。また、上述では、第1素子は、容量素子から構成し、検出回路においても容量素子を用いるようにしたが、これに限るものではなく、インダクタンスおよび抵抗なおどの半導体素子であってもよく、第2素子と同様の構成のMEMS素子であってもよい。いずれにしても、第1素子は、入力信号に対して既知の信号量を出力するものであればよい。

【符号の説明】

【0051】

101…第1素子、102…第2素子、103…電源、104…第1検出回路、105…第2検出回路、106…差分回路、1201…素子、1202…電源、1203…検出回路、1204…記憶部、1205…差分回路。

【特許請求の範囲】

【請求項1】

入力信号に対して既知の信号量を出力する第1素子と、

入力信号に対して未知の信号量を出力する第2素子と、

前記第1素子および前記第2素子に同じ入力信号を供給する電源と、

前記電源より供給される電圧が印加された前記第1素子より出力される信号量を検出する第1検出回路と、

前記電源より供給される電圧が印加された前記第2素子より出力される信号量を検出する第2検出回路と、

前記第1検出回路が検出した信号量と前記第2検出回路が検出した信号量との差分に対応する信号を出力する差分回路と

を少なくとも備えることを特徴とする回路装置。

【請求項2】

請求項1記載の回路装置において、

前記第1素子より前記第1検出回路に出力される信号の切り替えを行う第1スイッチと、

前記第2素子より前記第2検出回路に出力される信号の切り替えを行う第2スイッチと

を備えることを特徴とする回路装置。

【請求項3】

請求項1または2記載の回路装置において、

前記第1素子および前記第2素子は、同一の構造を有することを特徴とする回路装置。

【請求項4】

請求項1〜3のいずれか1項に記載の回路装置において、

前記電源は、周期的に変化する電圧を供給することを特徴とする回路装置。

【請求項5】

請求項1〜4のいずれか1項に記載の回路装置において、

前記第1素子は、容量素子から構成され、

前記第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されていることを特徴とする回路装置。

【請求項6】

入力信号に対して未知の信号量を出力する素子と、

前記素子に入力信号を供給する電源と、

前記電源より供給される電圧が印加された前記素子より出力される信号量を検出する検出回路と、

入力信号が未入力の前記素子より出力される信号量を前記検出回路で検出した初期信号量が記憶されている記憶手段と、

前記検出回路が検出した信号量と前記記憶手段より出力される前記初期信号量との差分に対応する信号を出力する差分回路と

を少なくとも備えることを特徴とする回路装置。

【請求項1】

入力信号に対して既知の信号量を出力する第1素子と、

入力信号に対して未知の信号量を出力する第2素子と、

前記第1素子および前記第2素子に同じ入力信号を供給する電源と、

前記電源より供給される電圧が印加された前記第1素子より出力される信号量を検出する第1検出回路と、

前記電源より供給される電圧が印加された前記第2素子より出力される信号量を検出する第2検出回路と、

前記第1検出回路が検出した信号量と前記第2検出回路が検出した信号量との差分に対応する信号を出力する差分回路と

を少なくとも備えることを特徴とする回路装置。

【請求項2】

請求項1記載の回路装置において、

前記第1素子より前記第1検出回路に出力される信号の切り替えを行う第1スイッチと、

前記第2素子より前記第2検出回路に出力される信号の切り替えを行う第2スイッチと

を備えることを特徴とする回路装置。

【請求項3】

請求項1または2記載の回路装置において、

前記第1素子および前記第2素子は、同一の構造を有することを特徴とする回路装置。

【請求項4】

請求項1〜3のいずれか1項に記載の回路装置において、

前記電源は、周期的に変化する電圧を供給することを特徴とする回路装置。

【請求項5】

請求項1〜4のいずれか1項に記載の回路装置において、

前記第1素子は、容量素子から構成され、

前記第2素子は、対向して配置されて互いの距離が可変とされた2つの電極から構成されていることを特徴とする回路装置。

【請求項6】

入力信号に対して未知の信号量を出力する素子と、

前記素子に入力信号を供給する電源と、

前記電源より供給される電圧が印加された前記素子より出力される信号量を検出する検出回路と、

入力信号が未入力の前記素子より出力される信号量を前記検出回路で検出した初期信号量が記憶されている記憶手段と、

前記検出回路が検出した信号量と前記記憶手段より出力される前記初期信号量との差分に対応する信号を出力する差分回路と

を少なくとも備えることを特徴とする回路装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【公開番号】特開2012−152880(P2012−152880A)

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願番号】特願2011−16249(P2011−16249)

【出願日】平成23年1月28日(2011.1.28)

【出願人】(000102739)エヌ・ティ・ティ・アドバンステクノロジ株式会社 (265)

【出願人】(504137912)国立大学法人 東京大学 (1,942)

【Fターム(参考)】

【公開日】平成24年8月16日(2012.8.16)

【国際特許分類】

【出願日】平成23年1月28日(2011.1.28)

【出願人】(000102739)エヌ・ティ・ティ・アドバンステクノロジ株式会社 (265)

【出願人】(504137912)国立大学法人 東京大学 (1,942)

【Fターム(参考)】

[ Back to top ]