固体撮像装置、固体撮像装置の制御方法、および撮像装置

【課題】複数枚のチップを接続した構成の固体撮像装置において、それぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と、第2の基板に配置され、光電変換素子で発生した信号をアナログの読み出し信号として出力する読み出し回路とを具備する画素が複数配置された画素部と、読み出し信号に対して信号処理を行う信号処理回路とを備え、信号処理回路を構成する回路要素を区分基準に基づいて第1の基板側または第2の基板側に区分し、第1信号処理回路に区分された回路要素を第1の基板内に配置し、第2信号処理回路に区分された回路要素を第2の基板内に配置する。

【解決手段】第1の基板と第2の基板とが接続部によって電気的に接続された固体撮像装置であって、第1の基板に配置された光電変換素子と、第2の基板に配置され、光電変換素子で発生した信号をアナログの読み出し信号として出力する読み出し回路とを具備する画素が複数配置された画素部と、読み出し信号に対して信号処理を行う信号処理回路とを備え、信号処理回路を構成する回路要素を区分基準に基づいて第1の基板側または第2の基板側に区分し、第1信号処理回路に区分された回路要素を第1の基板内に配置し、第2信号処理回路に区分された回路要素を第2の基板内に配置する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、固体撮像装置、固体撮像装置の制御方法、および撮像装置に関する。

【背景技術】

【0002】

近年、ビデオカメラや電子スチルカメラなどの撮像装置が広く一般に普及している。これらの撮像装置(以下、「カメラ」という)には、CCD(Charge Coupled Device:電荷結合素子)型の固体撮像装置や、増幅型の固体撮像装置が使用されている。増幅型の固体撮像装置では、画素がマトリクス状に複数配置されている。そして、増幅型の固体撮像装置では、各画素の受光部である光電変換部で生成、蓄積された信号電荷を、画素内に設けられた増幅部に導き、増幅部によって増幅された信号を画素からの出力信号として出力する。

【0003】

増幅型の固体撮像装置には、例えば、増幅部に接合型電界効果トランジスタを用いた固体撮像装置や、増幅部にCMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)トランジスタを用いたCMOS型固体撮像装置などがある。

【0004】

また、従来から、一般的なCMOS型固体撮像装置(以下、「固体撮像装置」ともいう)では、二次元のマトリクス状に配列された各画素の光電変換部で生成、蓄積された信号電荷を、行毎に順次読み出す方式が採用されている。この読み出し方式の場合、各画素の光電変換部における露光のタイミングは、信号電荷の読み出しの開始と終了によって決まり、画素の行毎に露光のタイミングが異なる。このため、このようなCMOS型固体撮像装置を用いて速い動きの被写体を撮像すると、被写体が歪んで撮像されてしまうことがある。

【0005】

この被写体の歪みをなくすための露光方法として、全ての画素を同じタイミングで露光させることによって、信号電荷の生成、蓄積の同時刻性を実現する同時撮像機能(以下、「グローバルシャッタ機能」という)が提案されている。そして、グローバルシャッタ機能を有するCMOS型固体撮像装置の用途も多くなってきている。

【0006】

グローバルシャッタ機能を有するCMOS型固体撮像装置では、通常、光電変換部が生成した信号電荷を、読み出しが終了するまで蓄えておく必要があることから、遮光性を持った蓄積容量部を有することが必要となる。従来のグローバルシャッタ機能を有するCMOS型固体撮像装置では、全ての画素を同時に露光した後、各光電変換部で生成された信号電荷を、全ての画素同時に、各蓄積容量部に転送して一旦蓄積しておき、蓄積容量部に蓄積された信号電荷を、所定の読み出しタイミングで順次画素信号に変換するようにしている。

【0007】

しかし、従来のグローバルシャッタ機能を有するCMOS型固体撮像装置では、光電変換部と蓄積容量部とを、基板の同一平面上に配置しなければならず、固体撮像装置のチップ面積の増大を避けることができない。さらに、蓄積容量部に蓄積された信号電荷を読み出すまでの待機期間中に、光や蓄積容量部のリークに起因するノイズによって、信号の品質が劣化してしまうという問題がある。

【0008】

このような問題を解決するための技術として、例えば、特許文献1のように、光電変換部が形成された第1の基板と、複数のMOSトランジスタが形成された第2の基板とを、別々に作製し、これらの基板を張り合わせて1つの固体撮像装置とすることによって、固体撮像装置のチップ面積(実装面積)の増大を防ぐ方法が開示されている。特許文献1で開示された技術では、別々に作製した第1の基板と第2の基板とを、接続電極によって電気的に接続している。

【0009】

また、CMOS型固体撮像装置は、CCD型固体撮像装置と異なり、単一電源で駆動することが可能である。また、CCD型固体撮像装置では、専用の製造プロセスを必要とするのに対し、CMOS型固体撮像装置は、他のLSIと同じ製造プロセスを用いて製造することができることからSOC(System On Chip)への対応が容易である。このため、固体撮像装置に信号処理回路を搭載することによって、多機能化を実現したCMOS型固体撮像装置が提案されている。

【0010】

多機能化を実現したCMOS型固体撮像装置として、例えば、特許文献2では、アナログデジタル変換を行うAD変換器を、信号処理回路として搭載したCMOS型固体撮像装置が開示されている。特許文献2で開示されたCMOS型固体撮像装置では、画素列毎にAD変換器を搭載している。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−219339号公報

【特許文献2】特開2005−323331号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1で開示された技術では、従来のグローバルシャッタ機能を有する画素を、2つの基板に分けて構成している。このため、第1の基板のチップ面積の増大を避けることができる。また、第1の基板と第2の基板とを張り合わせた構成にすることによって、蓄積容量部に蓄積された信号電荷を読み出すまでの待機期間中の光に起因するノイズによる信号品質の劣化を避けることができる。

【0013】

図8は、特許文献1で開示された技術を適用し、さらに、特許文献2で開示された信号処理回路を搭載した従来の固体撮像装置の基板の接続構成を示した概観図である。図8(a)には、固体撮像装置800の第1の基板と第2の基板の接続構成の側面図を示し、図8(b)には、固体撮像装置800の第1の基板と第2の基板の接続構成の平面図を示している。

【0014】

図8(a)に示したように、固体撮像装置800では、第1の基板に形成された画素部11と、第2の基板に形成された画素部12とを基板間接続部13を介して接続している。より具体的には、画素部11に光電変換部を形成し、画素部12に蓄積容量部を形成している。また、基板間接続部13内では、例えば、バンプによって画素部11の光電変換部と画素部12の蓄積容量部とを接続している。このようにして、固体撮像装置800では、バンプを介して接続された画素部11と画素部12との構成によって、固体撮像装置800の画素アレイ部40の領域を積層構成で形成している。

【0015】

ところで、固体撮像装置内に配置された各画素から読み出した画素信号を正確に出力するには、それぞれの信号処理回路によるノイズ除去などの信号処理を施す必要がある。しかしながら、特許文献1には、信号処理するための構成については、その技術や具体例が開示されていない。すなわち、特許文献1からは、画素部の光電変換部によって生成された信号電荷を増幅した画素信号を信号処理回路に読み出し、さらに信号処理回路で信号処理を行うための具体的な構成を導き出すことができない。

【0016】

そこで、仮に、図8に示した固体撮像装置800のように、画素信号を読み出す読出し回路を第2の基板内に設ける場合を考える。固体撮像装置800では、第1の基板の画素部11の領域に相当する第2の基板の領域に、画素部11の光電変換部で生成した信号電荷を蓄積する蓄積容量部を形成する信号保持領域を設け、さらに、固体撮像装置800の周辺の読出し回路(図8に示した固体撮像装置制御信号発生回路10、垂直読出し制御回路20、水平読出し制御回路30、カラム信号処理回路60、出力回路80)を、第2の基板内に形成している。このようにすると、図8を見てわかるように、固体撮像装置800における第2の基板のチップ面積は、第1の基板に比べ大幅に大きくなってしまう。

【0017】

これにより、特許文献1で開示された技術では、第1の基板と第2の基板とを接続した後の固体撮像装置800のチップ面積は、第2の基板と同様の大きな面積となり、固体撮像装置800の実装面積は、1枚の基板で製造された固体撮像装置の実装面積よりも大幅に小さくすることができないという問題がある。

【0018】

また、近年では、画素列毎に搭載したAD変換器(図8に示したカラム信号処理回路60)などの信号処理回路を、より多機能化したり、高速化したりする例が増加し、信号処理回路の回路面積も増大が進んでいる。このため、上述したような構成では、第1の基板と第2の基板とのチップ面積の差がさらに大きくなる。

【0019】

また、第1の基板と第2の基板とを張り合わせる方法としては、それぞれの半導体製造工程を終えた後に、第1の基板を生成したウエハと第2の基板を生成したウエハとをウエハの状態で張り合わせる方法などがある。この場合には、第1の基板を生成したウエハと第2の基板を生成したウエハとを張り合わせた後にダイシングを行うことになるため、第1の基板と第2の基板のチップ面積とは同じ面積になる。このため、上述したように、第1の基板と第2の基板とのチップ面積に差があると、いずれかの基板に、回路が形成されていない領域(以下、「調整領域」という)が発生し、固体撮像装置のチップ面積増大に繋がってしまう。例えば、図8に示した固体撮像装置800においては、第1の基板のチップ面積も第2の基板のチップ面積と同じ面積になるため、第1の基板に余分な調整領域が発生し、固体撮像装置800のチップ面積が増大してしまう。このため、特許文献1で開示された技術を適用した固体撮像装置では、チップコストが高くなってしまうという問題がある。

【0020】

本発明は、上記の課題認識に基づいてなされたものであり、複数枚のチップを接続することによって構成される固体撮像装置において、固体撮像装置が形成されるそれぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供することを目的としている。

【課題を解決するための手段】

【0021】

上記の課題を解決するため、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0022】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0023】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0024】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0025】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理ステップと、を含む。

【0026】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0027】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0028】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0029】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0030】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0031】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0032】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0033】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0034】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理ステップと、を含む。

【0035】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0036】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0037】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0038】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【図面の簡単な説明】

【0039】

【図1】本発明の実施形態によるデジタルカメラの概略構成を示したブロック図である。

【図2】本発明の第1の実施形態による固体撮像装置の概略構成を示したブロック図である。

【図3】本第1の実施形態の固体撮像装置の画素アレイ部内の単位画素の概略構成を示した回路図である。

【図4】本第1の実施形態の固体撮像装置内のカラム信号処理回路の概略構成を示した回路図である。

【図5】本第1の実施形態の固体撮像装置の各構成要素の各基板への配置の一例を示したレイアウト図である。

【図6】本第1の実施形態の固体撮像装置の各構成要素の各基板への配置の別の一例を示したレイアウト図である。

【図7】本発明の第2の実施形態による固体撮像装置内のカラム信号処理回路の概略構成を示した回路図である。

【図8】従来の固体撮像装置の基板の接続構成を示した概観図である。

【発明を実施するための形態】

【0040】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の説明は、例示のために特定の詳細な内容が含まれている。しかし、当業者であれば、以下に説明する詳細な内容に様々な変更を加えた場合であっても、本発明の範囲を超えないことは理解できるであろう。従って、以下に説明する本発明の例示的な実施形態は、権利を請求された発明に対して、一般性を失わせることなく、また、何ら限定をすることもなく、述べられたものである。

【0041】

図1は、本実施形態によるデジタルカメラ(例えば、デジタル一眼レフレックスカメラシステム)の概略構成を示したブロック図である。ここに示した各構成要素は、ハードウェア的には、コンピュータのCPUやメモリをはじめとする素子で実現することができ、ソフトウェア的にはコンピュータプログラムなどによって実現されるものであるが、ここでは、これらの連携によって実現される機能ブロックとして示している。従って、これらの機能ブロックは、ハードウェア、ソフトウェアの組合せによって、様々な形式で実現できるということは、当業者には理解できるであろう。

【0042】

図1に示したデジタルカメラ7は、レンズユニット部2、固体撮像装置1、画像信号処理装置3、記録装置4、カメラ制御装置5、表示装置6から構成される。なお、図1に示したデジタルカメラ7は、固体撮像装置1を遮光するためのメカニカルシャッタを搭載せず、全画素同時に露光するグローバル露光を行うデジタルカメラである。

【0043】

レンズユニット部2は、カメラ制御装置5によってズーム、フォーカス、絞りなどが駆動制御され、被写体像を固体撮像装置1に結像させる。

固体撮像装置1は、カメラ制御装置5によって駆動・制御され、レンズユニット部2を介して固体撮像装置1内に入射した被写体光を画像信号に変換するMOS型固体撮像装置である。なお、この固体撮像装置1に関する詳細な説明は、後述する。

【0044】

画像信号処理装置3は固体撮像装置1から出力された画像信号に対して、信号の増幅、画像データへの変換および各種の補正、画像データの圧縮などの処理を行う。画像信号処理装置3は、各処理における画像データの一時記憶手段として図示しないメモリを利用する。

記録装置4は、半導体メモリなどの着脱可能な記録媒体であり、画像データの記録または読み出しを行う。

表示装置6は、固体撮像装置1に結像され、画像信号処理装置3によって処理された画像データ、または記録装置4から読み出された画像データに基づく画像を表示する液晶などの表示装置である。

カメラ制御装置5は、デジタルカメラ7の全体の制御を行う制御装置である。

【0045】

<第1の実施形態>

次に、デジタルカメラ7に搭載した第1の実施形態の固体撮像装置1について説明する。図2は、本第1の実施形態による固体撮像装置1の概略構成を示したブロック図である。図2において、固体撮像装置1は、固体撮像装置制御信号発生回路10、垂直読出し制御回路20、水平読出し制御回路30、複数の単位画素50で構成された画素アレイ部40、参照電圧生成部100、カラム信号処理回路60、出力回路80から構成される。

【0046】

なお、図2に示した固体撮像装置1では、複数の単位画素50が、7行7列に2次元的に配置された画素アレイ部40の例を示している。また、図2に示した固体撮像装置1では、参照電圧生成部100と、カラム信号処理回路60とを、信号処理回路として構成している。

【0047】

固体撮像装置制御信号発生回路10は、垂直読出し制御回路20、水平読出し制御回路30、カラム信号処理回路60、および参照電圧生成部100を制御する。

垂直読出し制御回路20は、固体撮像装置制御信号発生回路10からの制御に応じて、画素アレイ部40内のそれぞれの単位画素50を制御し、各単位画素50の画素信号を垂直信号線90に出力させる。垂直読出し制御回路20は、単位画素50を制御するための制御信号を、画素アレイ部40に配置された単位画素50の行毎に出力する。

【0048】

画素アレイ部40内のそれぞれの単位画素50は、入射した被写体光を画素信号に変換し、垂直読出し制御回路20から入力された制御信号に応じて、入射した被写体光に応じた画素信号を、垂直信号線90に出力する。なお、この単位画素50に関する詳細な説明は、後述する。

【0049】

カラム信号処理回路60は、画素アレイ部40の各列に配置され、固体撮像装置制御信号発生回路10からの制御に応じて、各列の単位画素50からそれぞれ垂直信号線90に出力された画素信号に対して、ノイズ抑圧やアナログデジタル変換などの信号処理を行う。また、カラム信号処理回路60は、水平読出し制御回路30からの制御に応じて、画素信号に対して信号処理を行った出力信号を、水平信号線70に出力する。以下の説明においては、カラム信号処理回路60が、参照電圧生成部100から入力されたランプ波を用いてアナログデジタル変換を行うシングルスロープ型AD変換器で構成されているものとして説明する。なお、カラム信号処理回路60に関する詳細な説明は、後述する。

【0050】

参照電圧生成部100は、固体撮像装置制御信号発生回路10からの制御に応じて、時間の経過とともに増加または減少する一定の傾きをもったランプ波(参照電圧)を生成する。参照電圧生成部100は、生成したランプ波を、それぞれのカラム信号処理回路60に出力する。参照電圧生成部100が生成したランプ波は、画素アレイ部40の各列に配置されたカラム信号処理回路60、すなわち、シングルスロープ型AD変換器がアナログデジタル変換する際に用いられる。

【0051】

水平読出し制御回路30は、固体撮像装置制御信号発生回路10からの制御に応じて、各列に配置されたカラム信号処理回路60から出力されるアナログデジタル変換後の出力信号を、水平信号線70に順次読み出す。水平信号線70に読み出された信号は、出力回路80を介して固体撮像装置1の外部に出力される。

【0052】

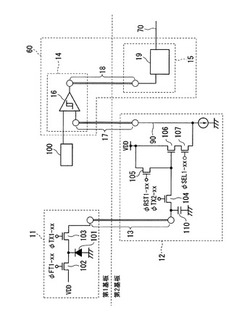

次に、本第1の実施形態の固体撮像装置1内の画素アレイ部40に備えた単位画素50について説明する。図3は、本第1の実施形態の固体撮像装置1の画素アレイ部40内の単位画素50の概略構成を示した回路図である。図3では、1つの単位画素50を示している。単位画素50は、入射した被写体光を画素信号に変換し、垂直信号線90に出力する。図3に示した単位画素50の概略構成は、従来の固体撮像装置における単位画素の構成と同様の構成である。ただし、本第1の実施形態の固体撮像装置1においては、図3に示したように、それぞれの単位画素50内の各構成要素を、第1の基板の画素部11と第2の基板の画素部12とに分けて配置している。

【0053】

図3において、単位画素50は、第1の基板の画素部11に形成された光電変換部101、光電変換部リセットトランジスタ102、および第1の転送トランジスタ103と、第2の基板の画素部12に形成された第2の転送トランジスタ104、画素リセットトランジスタ105、増幅トランジスタ106、選択トランジスタ107、および電荷蓄積部110とから構成される。また、第1の基板の画素部11と第2の基板の画素部12とは、基板間接続部13によって接続される。

【0054】

基板間接続部13は、第1の基板と第2の基板とを電気的に接続するための接続部である。基板間接続部13は、例えば、蒸着法、めっき法で作製されるバンプなどを用いる。なお、第1の基板と第2の基板との間に存在する空間には、接着剤などの絶縁部材を充填させてもよい。第1の基板と第2の基板とは、基板間接続部13を介して信号の送受信を行う。図3に示した単位画素50では、第1の基板の画素部11内の第1の転送トランジスタ103と、第2の基板の画素部12内の第2の転送トランジスタ104および電荷蓄積部110とが、基板間接続部13を介して接続されている。

【0055】

光電変換部101は、入射した光を光電変換して信号電荷を発生させ、光電変換信号として蓄積する。第1の転送トランジスタ103は、垂直読出し制御回路20から入力された制御信号φTX1−xxに応じて、光電変換部101に蓄積された光電変換信号を、基板間接続部13を介して電荷蓄積部110に転送する。電荷蓄積部110は、光電変換信号を保持(蓄積)する容量である。第1の転送トランジスタ103によって転送された光電変換信号は、電荷蓄積部110に蓄積される。

【0056】

なお、上述した制御信号の信号名「制御信号φTX1−xx」の内、制御信号の名称「制御信号φTX1」の後の「−」に続く「xx」の部分は、画素アレイ部40内に配置されている単位画素50の行番号を表す部分である。以下の説明においては、上述した制御信号φTX1も含め、画素アレイ部40内に配置されている単位画素50の行番号の数字を、それぞれの制御信号の「xx」の部分に記述する。なお、「xx」の部分に行番号の数字を記述せず、そのまま“xx”と記述した場合には、今回の説明におけるこの制御信号は、画素アレイ部40の特定の行の制御信号ではなく、画素アレイ部40の行毎に異なる制御信号であり、適宜行番号を当てはめて考えることができる制御信号であることを表す。

【0057】

第2の転送トランジスタ104は、垂直読出し制御回路20から入力された制御信号φTX2−xxに応じて、電荷蓄積部110に保持(蓄積)された光電変換信号を、増幅トランジスタ106のゲート端子に転送する。増幅トランジスタ106は、ゲート端子に転送された光電変換信号に応じた信号電圧を出力する。選択トランジスタ107は、垂直読出し制御回路20から入力された制御信号φSEL1−xxに応じて、増幅トランジスタ106が出力した信号電圧を、単位画素50が出力する画素信号として垂直信号線90に出力する。

【0058】

光電変換部リセットトランジスタ102は、垂直読出し制御回路20から入力された制御信号φFT1−xxに応じて、光電変換部101を電源電圧VDDにリセットする。画素リセットトランジスタ105は、垂直読出し制御回路20から入力された制御信号φRST1−xxに応じて、単位画素50内の信号を電源電圧VDDにリセットする。

【0059】

固体撮像装置1では、垂直読出し制御回路20が、全ての単位画素50を同時に制御することによって、グローバルシャッタ機能を実現している。より具体的には、垂直読出し制御回路20は、全ての単位画素50の制御信号φFT1−xxを同時に出力して、全ての単位画素50の光電変換部101による光電変換を同時に開始させる。そして、予め定められた露光時間が経過した後、垂直読出し制御回路20は、全ての単位画素50の制御信号φTX1−xxを同時に出力して、全ての単位画素50の光電変換部101が蓄積した光電変換信号を同時に、電荷蓄積部110に転送して保持させる。

【0060】

その後、固体撮像装置1では、垂直読出し制御回路20が、単位画素50を行毎に順次制御することによって、それぞれの単位画素50が光電変換した画素信号を、垂直信号線90に出力する。より具体的には、垂直読出し制御回路20は、単位画素50の行毎に制御信号φTX2−xx、制御信号φRST1−xx、制御信号φSEL1−xxを制御し、それぞれの電荷蓄積部110に保持された光電変換信号を、画素信号として垂直信号線90に順次出力(読み出し)させる。単位画素50では、それぞれの単位画素50が読み出されるまでに発生する、リークなどに起因するノイズによる信号の品質の劣化を、電荷蓄積部110を第2の基板に設けることによって抑圧している。

【0061】

次に、本第1の実施形態の固体撮像装置1内のカラム信号処理回路60について説明する。図4は、本第1の実施形態の固体撮像装置1内のカラム信号処理回路60の概略構成を示した回路図である。図4では、画素アレイ部40の1つの列に配置されたカラム信号処理回路60(シングルスロープ型AD変換器)を示している。また、図4には、図3に示した単位画素50を併せて示している。さらに、図4には、シングルスロープ型AD変換器にランプ波を出力する参照電圧生成部100も併せて示している。

【0062】

カラム信号処理回路60は、単位画素50が垂直信号線90に出力した画素信号に対して、アナログデジタル変換を行い、変換したデジタルの出力信号を水平信号線70に出力する。図4に示したカラム信号処理回路60の概略構成は、従来の固体撮像装置におけるカラム信号処理回路の構成と同様の構成である。ただし、本第1の実施形態の固体撮像装置1においては、図4に示したように、それぞれのカラム信号処理回路60内の各構成要素を、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置している。

【0063】

図4において、カラム信号処理回路60は、第1の基板のカラム信号処理部14に形成された比較器16と、第2の基板のカラム信号処理部15に形成されたカウンタ&ラッチ部19とから構成される。また、垂直信号線90と第1の基板のカラム信号処理部14とは、図3に示した単位画素50における第1の基板の画素部11と第2の基板の画素部12との接続と同様に、基板間接続部17によって接続され、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とは、基板間接続部18によって接続される。なお、参照電圧生成部100は、第1の基板に配置する。

【0064】

図4に示したように、カラム信号処理回路60では、アナログの動作を行う比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、デジタルの動作を行うカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。

【0065】

基板間接続部17および基板間接続部18は、図3に示した基板間接続部13と同様に、第1の基板と第2の基板とを電気的に接続するための接続部であるため、詳細な説明は省略する。図4に示したカラム信号処理回路60では、画素信号として垂直信号線90に出力された、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧が、第1の基板のカラム信号処理部14内の比較器16の一方の入力端子に、基板間接続部17を介して印加(入力)される。また、参照電圧生成部100が生成したランプ波が、第1の基板のカラム信号処理部14内の比較器16の他方の入力端子に印加(入力)される。また、第1の基板のカラム信号処理部14内の比較器16による比較結果を表す信号(以下、「比較結果信号」という)が、第2の基板のカラム信号処理部15内のカウンタ&ラッチ部19に、基板間接続部18を介して入力される。

【0066】

参照電圧生成部100は、固体撮像装置制御信号発生回路10からの制御に応じて、固体撮像装置制御信号発生回路10から入力されるクロック信号に同期した一定の傾きを持ったランプ波(参照電圧)を、例えば、デジタルアナログ変換器を用いて生成する。参照電圧生成部100は、生成したランプ波を、比較器16に印加(出力)する。

【0067】

比較器16は、基板間接続部17を介して印加された画素信号のレベルと、参照電圧生成部100から印加されたランプ波のレベルとを比較する。例えば、比較器16は、画素信号のレベルとランプ波のレベルとの大小関係を比較する。そして、比較器16は、ランプ波のレベルと画素信号のレベルとが一致したことを表す比較結果信号を、カウンタ&ラッチ部19に出力する。

【0068】

カウンタ&ラッチ部19は、固体撮像装置制御信号発生回路10からの制御に応じて、固体撮像装置制御信号発生回路10から入力されるクロック信号のカウントを開始する。カウンタ&ラッチ部19が、カウントを開始するタイミングは、参照電圧生成部100がランプ波を出力するタイミングと同期したタイミングである。そして、カウンタ&ラッチ部19は、基板間接続部18を介して比較器16から比較結果信号が入力されたタイミングで、クロック信号のカウントを停止し、現在のカウント値を、単位画素50から出力された画素信号のレベルを表すデジタル信号、すなわち、アナログデジタル変換した結果のデジタル信号として、水平信号線70に出力する。

【0069】

このような動作によって、カラム信号処理回路60(シングルスロープ型AD変換器)は、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧をアナログデジタル変換処理することができる。これにより、固体撮像装置1は、入射した被写体光に応じたデジタル信号を、画像信号として出力することができる。

【0070】

また、カラム信号処理回路60を、図4に示したように、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置することによって、図8に示した従来の固体撮像装置800よりもチップ面積を有効活用することができ、固体撮像装置1の実装面積を縮小することができる。

【0071】

ここで、本第1の実施形態の固体撮像装置1の各構成要素の配置について説明する。図5は、本第1の実施形態の固体撮像装置1の各構成要素の各基板への配置の一例を示したレイアウト図である。図5は、固体撮像装置1に入射する被写体光の入射面側から見た各構成要素の配置を示している。なお、固体撮像装置1を形成する場合、図5(a)に示した第1の基板は、図5(b)に示した第2の基板の上側に重ねて形成、すなわち、第1の基板と第2の基板とを積層構成にする。

【0072】

図5に示したように、固体撮像装置1では、画素アレイ部40の画素部11と、カラム信号処理回路60のカラム信号処理部14と、参照電圧生成部100とを、第1の基板に配置する。また、固体撮像装置1では、画素アレイ部40の画素部12と、カラム信号処理回路60のカラム信号処理部15と、固体撮像装置制御信号発生回路10と、垂直読出し制御回路20と、水平読出し制御回路30と、出力回路80とを、第2の基板に配置する。

【0073】

図5に示した固体撮像装置1の各構成要素の各基板への配置の一例では、参照電圧生成部100を、出力回路80の直上に配置している。このように、固体撮像装置1の各構成要素を配置することにより、第1の基板と第2の基板とのチップ面積を、ほぼ同じ面積にすることができ、第1の基板において、回路が形成されていない調整領域を少なくすることができる。

【0074】

上記に述べたように、本第1の実施形態における固体撮像装置1では、画素アレイ部40内のそれぞれの単位画素50およびカラム信号処理回路60を、第1の基板と第2の基板とに分けて形成することによって、図5をみてわかるように、第1の基板と第2の基板との大きさの差を少なくすることができる。これにより、第1の基板内の調整領域を少なくすることができ、従来の固体撮像装置よりもチップ面積を有効に活用することができる。このことにより、固体撮像装置1の実装面積を縮小することができる。

【0075】

また、本第1の実施形態における固体撮像装置1では、信号処理回路の構成要素において、アナログの動作を行う比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、デジタルの動作を行うカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。すなわち、本第1の実施形態における固体撮像装置1では、信号処理回路の各構成要素がアナログの動作を行うか、デジタルの動作を行うかという基準に基づいて、各構成要素を、第1の基板または第2の基板のいずれかの基板に配置している。これにより、少なくとも一方の基板を、好適な半導体プロセス技術が適用された製造工程で作製することができる。例えば、第1の基板をアナログ回路に適した半導体プロセスで作製することができる。また、例えば、第2の基板をデジタル回路に適した半導体プロセスで作製することができる。このように、少なくとも一方の基板を好適な半導体プロセスで作製することができるように、信号処理回路の構成要素をそれぞれの基板に分けて配置することによって、固体撮像装置1のチップコストの低減と製造工程の削減とを図ることができる。なお、この場合には、カラム信号処理回路60内における動作速度など、他の要因も考慮して配置する回路を決定することが望ましい。

【0076】

なお、本第1の実施形態における固体撮像装置1では、図5に示した配置の一例において、出力回路80の直上に参照電圧生成部100を配置した例を示した。しかし、第1の基板と第2の基板とに配置する回路の面積がほぼ同じ面積になるように配置すれば、各基板への固体撮像装置1の各構成要素の配置は、図5に示した本第1の実施形態の構成に限定されるものではない。例えば、固体撮像装置1の各構成要素を、図6に示したように各基板に配置することもできる。

【0077】

図6は、本第1の実施形態の固体撮像装置1の各構成要素の各基板への配置の別の一例を示したレイアウト図である。図6に示した配置の一例でも、図5に示した配置の一例と同様に、固体撮像装置1に入射する被写体光の入射面側から見た各構成要素の配置を示している。なお、固体撮像装置1を形成する場合も、図5に示した配置の一例と同様に、図6(a)に示した第1の基板と、図6(b)に示した第2の基板とを積層構成にする。

【0078】

図6に示した固体撮像装置1の各構成要素の各基板への配置の別の一例でも、図5に示した配置の一例と同様に、画素アレイ部40の画素部11と、カラム信号処理回路60のカラム信号処理部14と、参照電圧生成部100とを、第1の基板に配置する。また、画素アレイ部40の画素部12と、カラム信号処理回路60のカラム信号処理部15と、固体撮像装置制御信号発生回路10と、垂直読出し制御回路20と、水平読出し制御回路30と、出力回路80とを、第2の基板に配置する。

【0079】

図6に示した配置の別の一例では、参照電圧生成部100を、垂直読出し制御回路20の直上に配置している。このように、第1の基板と第2の基板とに配置された画素アレイ部40以外の回路の配置は、第1の基板と第2の基板とに配置される回路の面積がほぼ同じ面積になる配置であれば、図5に示した配置の一例と同様に、第1の基板の調整領域を少なくし、チップ面積を有効に活用することができるという効果を得ることができる。そして、図5に示した配置の一例と同様に、固体撮像装置1の実装面積を縮小することができるという効果や、固体撮像装置1のチップコストの低減と製造工程の削減とを図ることができるという効果を得ることができる。

【0080】

<第2の実施形態>

次に、デジタルカメラ7に搭載した第2の実施形態の固体撮像装置について説明する。なお、本第2の実施形態の固体撮像装置は、図2に示した第1の実施形態の固体撮像装置1内のカラム信号処理回路60が異なる回路構成となっているのみであり、その他の構成要素は、第1の実施形態の固体撮像装置1と同様である。従って、本第2の実施形態の固体撮像装置の構成要素において、図2に示した第1の実施形態の固体撮像装置1と同様の構成要素には、同一の符号を付加して詳細な説明は省略する。

【0081】

図7は、本第2の実施形態による固体撮像装置内のカラム信号処理回路62の概略構成を示した回路図である。カラム信号処理回路62は、図4に示したカラム信号処理回路60と同様に、画素アレイ部40の各列に配置され、固体撮像装置制御信号発生回路10からの制御に応じて、各列の単位画素50からそれぞれ垂直信号線90に出力された画素信号に対して、ノイズ抑圧やアナログデジタル変換などの信号処理を行う。また、カラム信号処理回路62は、図4に示したカラム信号処理回路60と同様に、水平読出し制御回路30からの制御に応じて、画素信号に対して信号処理を行った出力信号を、水平信号線70に出力する。以下の説明においては、図4に示したカラム信号処理回路60と同様に、カラム信号処理回路62が、参照電圧生成部100から入力されたランプ波を用いてアナログデジタル変換を行うシングルスロープ型AD変換器で構成されているものとして説明する。

【0082】

図7では、図4に示したカラム信号処理回路60と同様に、画素アレイ部40の1つの列に配置されたカラム信号処理回路62(シングルスロープ型AD変換器)を示している。また、図7には、図4に示したカラム信号処理回路60と同様に、図3に示した単位画素50と、参照電圧生成部100とを併せて示している。図7に示したように、カラム信号処理回路62においても、カラム信号処理回路62内の各構成要素を、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置する。

【0083】

図7において、カラム信号処理回路62は、第1の基板のカラム信号処理部14に形成された比較器16およびレベルシフタ21と、第2の基板のカラム信号処理部15に形成されたカウンタ&ラッチ部19とから構成される。また、垂直信号線90と第1の基板のカラム信号処理部14とは、図4に示したカラム信号処理回路60と同様に、基板間接続部17によって接続され、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とは、基板間接続部18によって接続される。なお、参照電圧生成部100も、第1の基板に配置する。

【0084】

カラム信号処理回路62において、第1の基板に配置された比較器16を含むシングルスロープ型AD変換器の構成要素は、比較的高い電源電圧で駆動される。また、カラム信号処理回路62において、第2の基板に配置されたカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素は、比較的低い電源電圧で駆動される。また、参照電圧生成部100も、比較的高い電源電圧で駆動される。このため、図7に示したように、カラム信号処理回路62では、比較的高い電源電圧で駆動される比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、比較的低い電源電圧で駆動されるカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。そして、カラム信号処理回路62では、図4に示したカラム信号処理回路60に加えて、比較器16が出力する比較結果信号の信号レベルを下げるためのレベルシフタ21を備えている。

【0085】

なお、比較器16、カウンタ&ラッチ部19、および参照電圧生成部100の動作は、駆動する電源電圧が異なる以外は、図4に示したカラム信号処理回路60に備えた比較器16、カウンタ&ラッチ部19、および参照電圧生成部100の動作と同様であるため、詳細な説明は省略する。

【0086】

図7に示したカラム信号処理回路62では、図4に示したカラム信号処理回路60と同様に、画素信号として垂直信号線90に出力された、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧が、第1の基板のカラム信号処理部14内の比較器16の一方の入力端子に、基板間接続部17を介して印加(入力)される。また、カラム信号処理回路62では、図4に示したカラム信号処理回路60と同様に、参照電圧生成部100が生成したランプ波が、第1の基板のカラム信号処理部14内の比較器16の他方の入力端子に印加(入力)される。

【0087】

カラム信号処理回路62では、第1の基板のカラム信号処理部14内の比較器16による比較結果である比較結果信号が、第1の基板のカラム信号処理部14内のレベルシフタ21に出力される。レベルシフタ21は、比較器16から入力された、比較的高い電圧である比較結果信号の出力レベルを、第2の基板で使用される比較的低い電圧の比較結果信号に変換する。そして、レベルシフタ21は、出力レベルを変換した比較結果信号を、基板間接続部18を介して、第2の基板のカラム信号処理部15内のカウンタ&ラッチ部19に出力する。

【0088】

カウンタ&ラッチ部19は、出力レベルが変換された比較結果信号が入力されたタイミングで停止した現在のカウント値を、単位画素50から出力された画素信号のレベルをアナログデジタル変換した結果のデジタル信号として、水平信号線70に出力する。

【0089】

このような動作によって、カラム信号処理回路62(シングルスロープ型AD変換器)は、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧をアナログデジタル変換処理することができる。これにより、本第2の実施形態の固体撮像装置1でも、第1の実施形態の固体撮像装置1と同様に、入射した被写体光に応じたデジタル信号を、画像信号として出力することができる。

【0090】

また、カラム信号処理回路62を、図7に示したように、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置することによって、回路が形成されていない調整領域を少なくし、チップ面積を有効活用することができる。そして、本第2の実施形態の固体撮像装置1でも、第1の実施形態の固体撮像装置1と同様に、固体撮像装置1の実装面積を縮小することができる。なお、本第2の実施形態の固体撮像装置1における各構成要素の各基板への配置は、図5および図6に示した配置の例と同様に考えることができるため、詳細な説明は省略する。

【0091】

上記に述べたように、本第2の実施形態における固体撮像装置1でも、画素アレイ部40内のそれぞれの単位画素50およびカラム信号処理回路62を、第1の基板と第2の基板とに分けて形成することによって、第1の実施形態の固体撮像装置1と同様に、第1の基板と第2の基板との大きさの差を少なくすることができる。これにより、第1の基板内の調整領域を少なくすることができ、従来の固体撮像装置よりもチップ面積を有効に活用し、第1の実施形態の固体撮像装置1と同様に、固体撮像装置1の実装面積を縮小することができる。

【0092】

また、本第2の実施形態における固体撮像装置1では、信号処理回路の構成要素において、比較的高い電源電圧で駆動される比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、比較的低い電源電圧で駆動されるカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。また、第1の基板に配置されたシングルスロープ型AD変換器の構成要素と、第2の基板に配置されたシングルスロープ型AD変換器の構成要素との間の信号レベルを合わせるため、レベルシフタ21を配置している。すなわち、本第2の実施形態における固体撮像装置1では、信号処理回路の各構成要素を駆動する電源電圧が比較的高いか低いかという基準に基づいて、各構成要素を、第1の基板または第2の基板のいずれかの基板に配置している。これにより、例えば、第2の基板のカラム信号処理部15内に配置するカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を形成する際に、耐圧電圧が低い微細な半導体プロセス技術を適用することができる。このことにより、固体撮像装置1の実装面積をさらに縮小することができ、固体撮像装置1のチップコストの低減を図ることができる。なお、この場合にも、カラム信号処理回路60内における動作速度など、他の要因も考慮して配置する回路を決定することが望ましい。

【0093】

上記に述べたように、本発明を実施するための形態によれば、予め定めた基準に基づいて、固体撮像装置の信号処理回路の各構成要素を、第1の基板と第2の基板とに分けて形成する。これにより、固体撮像装置を形成する第1の基板と第2の基板との大きさの差を少なくすることができる。このことにより、固体撮像装置の製造やチップに係るコストの削減を図ることができる。

【0094】

さらに、本発明を実施するための形態によれば、固体撮像装置を形成する第1の基板と第2の基板とを別々に作製することできるため、第1の基板と第2の基板とのそれぞれに適した半導体プロセスを使用することができる。これにより、固体撮像装置のコスト低減を図ることができる。

【0095】

また、本発明を実施するための形態によれば、ノイズ抑圧やアナログデジタル変換などの信号処理を行う信号処理回路を、第1の基板と第2の基板とに分けて形成するため、小さなチップ面積(実装面積)で信号処理回路を実現することができ、高品質な画像を得ることができる固体撮像装置を実現することができる。

【0096】

なお、本発明のある態様に係る固体撮像装置は、本実施形態においては、例えば、固体撮像装置1に対応し、撮像装置は、例えば、デジタルカメラ7に対応し、接続部は、例えば、基板間接続部13と、基板間接続部17と、基板間接続部18に対応する。また、本発明のある態様に係る光電変換素子は、本実施形態においては、例えば、光電変換部101に対応し、読み出し回路は、例えば、第2の転送トランジスタ104と、増幅トランジスタ106と、選択トランジスタ107とに対応し、信号処理回路は、例えば、カラム信号処理回路60と、参照電圧生成部100とに対応する。

【0097】

また、本発明のある態様に係る画素部は、本実施形態においては、例えば、画素アレイ部40、または画素部11および画素部12に対応し、画素は、例えば、単位画素50に対応し、第1信号処理回路に区分された回路要素は、例えば、比較器16およびレベルシフタ21、またはカラム信号処理部14に対応し、第2信号処理回路に区分された回路要素は、例えば、カウンタ&ラッチ部19、またはカラム信号処理部15に対応する。

【0098】

また、本発明のある態様に係る比較器は、本実施形態においては、例えば、比較器16に対応し、カウンタおよびラッチは、例えば、カウンタ&ラッチ部19に対応し、レベルシフタは、例えば、レベルシフタ21に対応し、参照電圧生成部は、例えば、参照電圧生成部100に対応する。

【0099】

また、本発明のある態様に係る読み出しトランジスタは、本実施形態においては、例えば、第2の転送トランジスタ104と、増幅トランジスタ106と、選択トランジスタ107に対応する。

【0100】

なお、本発明における具体的な構成は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更をすることができる。例えば、本発明を実施するための形態においては、シングルスロープ型AD変換器を用いて信号処理回路を構成した場合について説明したが、シングルスロープ型AD変換器の代わりに、パイプライン型AD変換器、デルタシグマ型AD変換器、または時間変換型AD変換器を用いて信号処理回路を構成することもできる。また、例えば、AD変換器のみではなく、他の信号処理回路やカラム信号処理回路であっても、それぞれの回路の動作や電源電圧に応じて第1の基板と第2の基板とに分割して配置することができれば、本発明を実施するための形態と同様に、チップ面積を有効に活用することができる。このことにより、少なくとも一方の基板を、好適な半導体プロセス技術が適用された製造工程で作製することができ、固体撮像装置の実装面積を縮小することができるという効果や、固体撮像装置のチップコストの低減と製造工程の削減とを図ることができるという効果を得ることができる。

【0101】

また、本発明における回路構成および駆動方法の具体的な構成は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更をすることができる。例えば、画素や信号処理回路の構成要素および駆動方法が変わった場合においても、固体撮像装置、単位画素、信号処理回路、またはカラム信号処理回路内の構成要素や回路構成に応じて駆動方法を変更することによって対応することができる。

【0102】

また、画素の行方向および列方向の配置は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において画素を配置する行方向および列方向の数を変更することができる。

【0103】

以上、本発明を実施するための形態をもとに説明したが、各構成要素や各処理プロセスの任意の組み合わせ、本発明の表現をコンピュータプログラムプロダクトなどに変換したものもまた、本発明の態様として有効である。ここで、コンピュータプログラムプロダクトとは、プログラムコードが記録された記録媒体(DVD媒体、ハードディスク媒体、メモリ媒体など)、プログラムコードが記録されたコンピュータ、プログラムコードが記録されたインターネットシステム(例えば、サーバとクライアント端末を含むシステム)など、プログラムコードが記録された記録媒体、装置、機器やシステムをいう。この場合、上述した各構成要素や各処理プロセスは各モジュールで実装され、その実装されたモジュールからなるプログラムコードはコンピュータプログラムプロダクト内に記録される。

【0104】

例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0105】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0106】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0107】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0108】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0109】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0110】

また、例えば、図1に示したデジタルカメラ7の各構成要素による処理を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、当該記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより、デジタルカメラ7に係る上述した種々の処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものであってもよい。また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、フラッシュメモリ等の書き込み可能な不揮発性メモリ、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。

【0111】

さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムが送信された場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリ(例えばDRAM(Dynamic Random Access Memory))のように、一定時間プログラムを保持しているものも含むものとする。また、上記プログラムは、このプログラムを記憶装置等に格納したコンピュータシステムから、伝送媒体を介して、あるいは、伝送媒体中の伝送波により他のコンピュータシステムに伝送されてもよい。ここで、プログラムを伝送する「伝送媒体」は、インターネット等のネットワーク(通信網)や電話回線等の通信回線(通信線)のように情報を伝送する機能を有する媒体のことをいう。また、上記プログラムは、前述した機能の一部を実現するためのものであっても良い。さらに、前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるもの、いわゆる差分ファイル(差分プログラム)であっても良い。

【0112】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲においての種々の変更も含まれる。

【0113】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする固体撮像装置であってもよい。

【0114】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0115】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0116】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする撮像装置であってもよい。

【0117】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0118】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0119】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする固体撮像装置であってもよい。

【0120】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0121】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0122】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする撮像装置であってもよい。

【0123】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0124】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0125】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の代替物、変形、等価物による変更を行うこともできる。従って、本発明の範囲は、上記の説明を参照して決められるものではなく、請求項によって決められるべきであり、均等物の全ての範囲も含まれる。また、上述した特徴は、いずれも、好ましいか否かを問わず、他の特徴と組み合わせてもよい。また、請求項において、明示的に断らない限り、各構成要素は1またはそれ以上の数量である。また、請求項において「〜のための手段」のような語句を用いて明示的に記載する場合を除いて、請求項が、ミーンズ・プラス・ファンクションの限定を含むものと解してはならない。

【0126】

また、本発明の実施形態に係る固体撮像装置は、2枚の基板が接続部により接続されていてもよいし、3枚以上の基板が接続部で接続されていてもよい。3枚以上の基板が接続部で接続される固体撮像装置の場合、そのうちの2枚が請求項に係る第1の基板と第2の基板に相当する。

【符号の説明】

【0127】

1・・・固体撮像装置

2・・・レンズユニット部

3・・・画像信号処理装置

4・・・記録装置

5・・・カメラ制御装置

6・・・表示装置

7・・・デジタルカメラ

10・・・固体撮像装置制御信号発生回路

20・・・垂直読出し制御回路

30・・・水平読出し制御回路

40・・・画素アレイ部

50・・・単位画素

11・・・画素部

12・・・画素部

101・・・光電変換部

102・・・光電変換部リセットトランジスタ

103・・・第1の転送トランジスタ

104・・・第2の転送トランジスタ

105・・・画素リセットトランジスタ

106・・・増幅トランジスタ

107・・・選択トランジスタ

110・・・電荷蓄積部

13・・・基板間接続部

60,62・・・カラム信号処理回路

14・・・カラム信号処理部

15・・・カラム信号処理部

16・・・比較器

17・・・基板間接続部

18・・・基板間接続部

19・・・カウンタ&ラッチ部

21・・・レベルシフタ

70・・・水平信号線

80・・・出力回路

90・・・垂直信号線

100・・・参照電圧生成部

800・・・固体撮像装置

【技術分野】

【0001】

本発明は、固体撮像装置、固体撮像装置の制御方法、および撮像装置に関する。

【背景技術】

【0002】

近年、ビデオカメラや電子スチルカメラなどの撮像装置が広く一般に普及している。これらの撮像装置(以下、「カメラ」という)には、CCD(Charge Coupled Device:電荷結合素子)型の固体撮像装置や、増幅型の固体撮像装置が使用されている。増幅型の固体撮像装置では、画素がマトリクス状に複数配置されている。そして、増幅型の固体撮像装置では、各画素の受光部である光電変換部で生成、蓄積された信号電荷を、画素内に設けられた増幅部に導き、増幅部によって増幅された信号を画素からの出力信号として出力する。

【0003】

増幅型の固体撮像装置には、例えば、増幅部に接合型電界効果トランジスタを用いた固体撮像装置や、増幅部にCMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)トランジスタを用いたCMOS型固体撮像装置などがある。

【0004】

また、従来から、一般的なCMOS型固体撮像装置(以下、「固体撮像装置」ともいう)では、二次元のマトリクス状に配列された各画素の光電変換部で生成、蓄積された信号電荷を、行毎に順次読み出す方式が採用されている。この読み出し方式の場合、各画素の光電変換部における露光のタイミングは、信号電荷の読み出しの開始と終了によって決まり、画素の行毎に露光のタイミングが異なる。このため、このようなCMOS型固体撮像装置を用いて速い動きの被写体を撮像すると、被写体が歪んで撮像されてしまうことがある。

【0005】

この被写体の歪みをなくすための露光方法として、全ての画素を同じタイミングで露光させることによって、信号電荷の生成、蓄積の同時刻性を実現する同時撮像機能(以下、「グローバルシャッタ機能」という)が提案されている。そして、グローバルシャッタ機能を有するCMOS型固体撮像装置の用途も多くなってきている。

【0006】

グローバルシャッタ機能を有するCMOS型固体撮像装置では、通常、光電変換部が生成した信号電荷を、読み出しが終了するまで蓄えておく必要があることから、遮光性を持った蓄積容量部を有することが必要となる。従来のグローバルシャッタ機能を有するCMOS型固体撮像装置では、全ての画素を同時に露光した後、各光電変換部で生成された信号電荷を、全ての画素同時に、各蓄積容量部に転送して一旦蓄積しておき、蓄積容量部に蓄積された信号電荷を、所定の読み出しタイミングで順次画素信号に変換するようにしている。

【0007】

しかし、従来のグローバルシャッタ機能を有するCMOS型固体撮像装置では、光電変換部と蓄積容量部とを、基板の同一平面上に配置しなければならず、固体撮像装置のチップ面積の増大を避けることができない。さらに、蓄積容量部に蓄積された信号電荷を読み出すまでの待機期間中に、光や蓄積容量部のリークに起因するノイズによって、信号の品質が劣化してしまうという問題がある。

【0008】

このような問題を解決するための技術として、例えば、特許文献1のように、光電変換部が形成された第1の基板と、複数のMOSトランジスタが形成された第2の基板とを、別々に作製し、これらの基板を張り合わせて1つの固体撮像装置とすることによって、固体撮像装置のチップ面積(実装面積)の増大を防ぐ方法が開示されている。特許文献1で開示された技術では、別々に作製した第1の基板と第2の基板とを、接続電極によって電気的に接続している。

【0009】

また、CMOS型固体撮像装置は、CCD型固体撮像装置と異なり、単一電源で駆動することが可能である。また、CCD型固体撮像装置では、専用の製造プロセスを必要とするのに対し、CMOS型固体撮像装置は、他のLSIと同じ製造プロセスを用いて製造することができることからSOC(System On Chip)への対応が容易である。このため、固体撮像装置に信号処理回路を搭載することによって、多機能化を実現したCMOS型固体撮像装置が提案されている。

【0010】

多機能化を実現したCMOS型固体撮像装置として、例えば、特許文献2では、アナログデジタル変換を行うAD変換器を、信号処理回路として搭載したCMOS型固体撮像装置が開示されている。特許文献2で開示されたCMOS型固体撮像装置では、画素列毎にAD変換器を搭載している。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特開2010−219339号公報

【特許文献2】特開2005−323331号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

特許文献1で開示された技術では、従来のグローバルシャッタ機能を有する画素を、2つの基板に分けて構成している。このため、第1の基板のチップ面積の増大を避けることができる。また、第1の基板と第2の基板とを張り合わせた構成にすることによって、蓄積容量部に蓄積された信号電荷を読み出すまでの待機期間中の光に起因するノイズによる信号品質の劣化を避けることができる。

【0013】

図8は、特許文献1で開示された技術を適用し、さらに、特許文献2で開示された信号処理回路を搭載した従来の固体撮像装置の基板の接続構成を示した概観図である。図8(a)には、固体撮像装置800の第1の基板と第2の基板の接続構成の側面図を示し、図8(b)には、固体撮像装置800の第1の基板と第2の基板の接続構成の平面図を示している。

【0014】

図8(a)に示したように、固体撮像装置800では、第1の基板に形成された画素部11と、第2の基板に形成された画素部12とを基板間接続部13を介して接続している。より具体的には、画素部11に光電変換部を形成し、画素部12に蓄積容量部を形成している。また、基板間接続部13内では、例えば、バンプによって画素部11の光電変換部と画素部12の蓄積容量部とを接続している。このようにして、固体撮像装置800では、バンプを介して接続された画素部11と画素部12との構成によって、固体撮像装置800の画素アレイ部40の領域を積層構成で形成している。

【0015】

ところで、固体撮像装置内に配置された各画素から読み出した画素信号を正確に出力するには、それぞれの信号処理回路によるノイズ除去などの信号処理を施す必要がある。しかしながら、特許文献1には、信号処理するための構成については、その技術や具体例が開示されていない。すなわち、特許文献1からは、画素部の光電変換部によって生成された信号電荷を増幅した画素信号を信号処理回路に読み出し、さらに信号処理回路で信号処理を行うための具体的な構成を導き出すことができない。

【0016】

そこで、仮に、図8に示した固体撮像装置800のように、画素信号を読み出す読出し回路を第2の基板内に設ける場合を考える。固体撮像装置800では、第1の基板の画素部11の領域に相当する第2の基板の領域に、画素部11の光電変換部で生成した信号電荷を蓄積する蓄積容量部を形成する信号保持領域を設け、さらに、固体撮像装置800の周辺の読出し回路(図8に示した固体撮像装置制御信号発生回路10、垂直読出し制御回路20、水平読出し制御回路30、カラム信号処理回路60、出力回路80)を、第2の基板内に形成している。このようにすると、図8を見てわかるように、固体撮像装置800における第2の基板のチップ面積は、第1の基板に比べ大幅に大きくなってしまう。

【0017】

これにより、特許文献1で開示された技術では、第1の基板と第2の基板とを接続した後の固体撮像装置800のチップ面積は、第2の基板と同様の大きな面積となり、固体撮像装置800の実装面積は、1枚の基板で製造された固体撮像装置の実装面積よりも大幅に小さくすることができないという問題がある。

【0018】

また、近年では、画素列毎に搭載したAD変換器(図8に示したカラム信号処理回路60)などの信号処理回路を、より多機能化したり、高速化したりする例が増加し、信号処理回路の回路面積も増大が進んでいる。このため、上述したような構成では、第1の基板と第2の基板とのチップ面積の差がさらに大きくなる。

【0019】

また、第1の基板と第2の基板とを張り合わせる方法としては、それぞれの半導体製造工程を終えた後に、第1の基板を生成したウエハと第2の基板を生成したウエハとをウエハの状態で張り合わせる方法などがある。この場合には、第1の基板を生成したウエハと第2の基板を生成したウエハとを張り合わせた後にダイシングを行うことになるため、第1の基板と第2の基板のチップ面積とは同じ面積になる。このため、上述したように、第1の基板と第2の基板とのチップ面積に差があると、いずれかの基板に、回路が形成されていない領域(以下、「調整領域」という)が発生し、固体撮像装置のチップ面積増大に繋がってしまう。例えば、図8に示した固体撮像装置800においては、第1の基板のチップ面積も第2の基板のチップ面積と同じ面積になるため、第1の基板に余分な調整領域が発生し、固体撮像装置800のチップ面積が増大してしまう。このため、特許文献1で開示された技術を適用した固体撮像装置では、チップコストが高くなってしまうという問題がある。

【0020】

本発明は、上記の課題認識に基づいてなされたものであり、複数枚のチップを接続することによって構成される固体撮像装置において、固体撮像装置が形成されるそれぞれのチップの大きさの差を少なくすることによって、固体撮像装置のチップ面積(実装面積)の縮小化と、コストの削減を図ることができる固体撮像装置、固体撮像装置の制御方法、および撮像装置を提供することを目的としている。

【課題を解決するための手段】

【0021】

上記の課題を解決するため、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0022】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0023】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0024】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0025】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理ステップと、を含む。

【0026】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0027】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0028】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0029】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0030】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0031】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0032】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【0033】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0034】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理ステップと、を含む。

【0035】

また、本発明のある態様に係る固体撮像装置の制御方法は、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の制御方法であって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しステップと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理ステップと、を含む。

【0036】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、を備え、前記信号処理回路は、当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する。

【0037】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置され、前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備える。

【0038】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続部によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素部と、前記読み出し信号に対して信号処理を行う信号処理回路と、を備え、前記信号処理回路は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備える。

【図面の簡単な説明】

【0039】

【図1】本発明の実施形態によるデジタルカメラの概略構成を示したブロック図である。

【図2】本発明の第1の実施形態による固体撮像装置の概略構成を示したブロック図である。

【図3】本第1の実施形態の固体撮像装置の画素アレイ部内の単位画素の概略構成を示した回路図である。

【図4】本第1の実施形態の固体撮像装置内のカラム信号処理回路の概略構成を示した回路図である。

【図5】本第1の実施形態の固体撮像装置の各構成要素の各基板への配置の一例を示したレイアウト図である。

【図6】本第1の実施形態の固体撮像装置の各構成要素の各基板への配置の別の一例を示したレイアウト図である。

【図7】本発明の第2の実施形態による固体撮像装置内のカラム信号処理回路の概略構成を示した回路図である。

【図8】従来の固体撮像装置の基板の接続構成を示した概観図である。

【発明を実施するための形態】

【0040】

以下、本発明の実施形態について、図面を参照して説明する。なお、以下の説明は、例示のために特定の詳細な内容が含まれている。しかし、当業者であれば、以下に説明する詳細な内容に様々な変更を加えた場合であっても、本発明の範囲を超えないことは理解できるであろう。従って、以下に説明する本発明の例示的な実施形態は、権利を請求された発明に対して、一般性を失わせることなく、また、何ら限定をすることもなく、述べられたものである。

【0041】

図1は、本実施形態によるデジタルカメラ(例えば、デジタル一眼レフレックスカメラシステム)の概略構成を示したブロック図である。ここに示した各構成要素は、ハードウェア的には、コンピュータのCPUやメモリをはじめとする素子で実現することができ、ソフトウェア的にはコンピュータプログラムなどによって実現されるものであるが、ここでは、これらの連携によって実現される機能ブロックとして示している。従って、これらの機能ブロックは、ハードウェア、ソフトウェアの組合せによって、様々な形式で実現できるということは、当業者には理解できるであろう。

【0042】

図1に示したデジタルカメラ7は、レンズユニット部2、固体撮像装置1、画像信号処理装置3、記録装置4、カメラ制御装置5、表示装置6から構成される。なお、図1に示したデジタルカメラ7は、固体撮像装置1を遮光するためのメカニカルシャッタを搭載せず、全画素同時に露光するグローバル露光を行うデジタルカメラである。

【0043】

レンズユニット部2は、カメラ制御装置5によってズーム、フォーカス、絞りなどが駆動制御され、被写体像を固体撮像装置1に結像させる。

固体撮像装置1は、カメラ制御装置5によって駆動・制御され、レンズユニット部2を介して固体撮像装置1内に入射した被写体光を画像信号に変換するMOS型固体撮像装置である。なお、この固体撮像装置1に関する詳細な説明は、後述する。

【0044】

画像信号処理装置3は固体撮像装置1から出力された画像信号に対して、信号の増幅、画像データへの変換および各種の補正、画像データの圧縮などの処理を行う。画像信号処理装置3は、各処理における画像データの一時記憶手段として図示しないメモリを利用する。

記録装置4は、半導体メモリなどの着脱可能な記録媒体であり、画像データの記録または読み出しを行う。

表示装置6は、固体撮像装置1に結像され、画像信号処理装置3によって処理された画像データ、または記録装置4から読み出された画像データに基づく画像を表示する液晶などの表示装置である。

カメラ制御装置5は、デジタルカメラ7の全体の制御を行う制御装置である。

【0045】

<第1の実施形態>

次に、デジタルカメラ7に搭載した第1の実施形態の固体撮像装置1について説明する。図2は、本第1の実施形態による固体撮像装置1の概略構成を示したブロック図である。図2において、固体撮像装置1は、固体撮像装置制御信号発生回路10、垂直読出し制御回路20、水平読出し制御回路30、複数の単位画素50で構成された画素アレイ部40、参照電圧生成部100、カラム信号処理回路60、出力回路80から構成される。

【0046】

なお、図2に示した固体撮像装置1では、複数の単位画素50が、7行7列に2次元的に配置された画素アレイ部40の例を示している。また、図2に示した固体撮像装置1では、参照電圧生成部100と、カラム信号処理回路60とを、信号処理回路として構成している。

【0047】

固体撮像装置制御信号発生回路10は、垂直読出し制御回路20、水平読出し制御回路30、カラム信号処理回路60、および参照電圧生成部100を制御する。

垂直読出し制御回路20は、固体撮像装置制御信号発生回路10からの制御に応じて、画素アレイ部40内のそれぞれの単位画素50を制御し、各単位画素50の画素信号を垂直信号線90に出力させる。垂直読出し制御回路20は、単位画素50を制御するための制御信号を、画素アレイ部40に配置された単位画素50の行毎に出力する。

【0048】

画素アレイ部40内のそれぞれの単位画素50は、入射した被写体光を画素信号に変換し、垂直読出し制御回路20から入力された制御信号に応じて、入射した被写体光に応じた画素信号を、垂直信号線90に出力する。なお、この単位画素50に関する詳細な説明は、後述する。

【0049】

カラム信号処理回路60は、画素アレイ部40の各列に配置され、固体撮像装置制御信号発生回路10からの制御に応じて、各列の単位画素50からそれぞれ垂直信号線90に出力された画素信号に対して、ノイズ抑圧やアナログデジタル変換などの信号処理を行う。また、カラム信号処理回路60は、水平読出し制御回路30からの制御に応じて、画素信号に対して信号処理を行った出力信号を、水平信号線70に出力する。以下の説明においては、カラム信号処理回路60が、参照電圧生成部100から入力されたランプ波を用いてアナログデジタル変換を行うシングルスロープ型AD変換器で構成されているものとして説明する。なお、カラム信号処理回路60に関する詳細な説明は、後述する。

【0050】

参照電圧生成部100は、固体撮像装置制御信号発生回路10からの制御に応じて、時間の経過とともに増加または減少する一定の傾きをもったランプ波(参照電圧)を生成する。参照電圧生成部100は、生成したランプ波を、それぞれのカラム信号処理回路60に出力する。参照電圧生成部100が生成したランプ波は、画素アレイ部40の各列に配置されたカラム信号処理回路60、すなわち、シングルスロープ型AD変換器がアナログデジタル変換する際に用いられる。

【0051】

水平読出し制御回路30は、固体撮像装置制御信号発生回路10からの制御に応じて、各列に配置されたカラム信号処理回路60から出力されるアナログデジタル変換後の出力信号を、水平信号線70に順次読み出す。水平信号線70に読み出された信号は、出力回路80を介して固体撮像装置1の外部に出力される。

【0052】

次に、本第1の実施形態の固体撮像装置1内の画素アレイ部40に備えた単位画素50について説明する。図3は、本第1の実施形態の固体撮像装置1の画素アレイ部40内の単位画素50の概略構成を示した回路図である。図3では、1つの単位画素50を示している。単位画素50は、入射した被写体光を画素信号に変換し、垂直信号線90に出力する。図3に示した単位画素50の概略構成は、従来の固体撮像装置における単位画素の構成と同様の構成である。ただし、本第1の実施形態の固体撮像装置1においては、図3に示したように、それぞれの単位画素50内の各構成要素を、第1の基板の画素部11と第2の基板の画素部12とに分けて配置している。

【0053】

図3において、単位画素50は、第1の基板の画素部11に形成された光電変換部101、光電変換部リセットトランジスタ102、および第1の転送トランジスタ103と、第2の基板の画素部12に形成された第2の転送トランジスタ104、画素リセットトランジスタ105、増幅トランジスタ106、選択トランジスタ107、および電荷蓄積部110とから構成される。また、第1の基板の画素部11と第2の基板の画素部12とは、基板間接続部13によって接続される。

【0054】

基板間接続部13は、第1の基板と第2の基板とを電気的に接続するための接続部である。基板間接続部13は、例えば、蒸着法、めっき法で作製されるバンプなどを用いる。なお、第1の基板と第2の基板との間に存在する空間には、接着剤などの絶縁部材を充填させてもよい。第1の基板と第2の基板とは、基板間接続部13を介して信号の送受信を行う。図3に示した単位画素50では、第1の基板の画素部11内の第1の転送トランジスタ103と、第2の基板の画素部12内の第2の転送トランジスタ104および電荷蓄積部110とが、基板間接続部13を介して接続されている。

【0055】

光電変換部101は、入射した光を光電変換して信号電荷を発生させ、光電変換信号として蓄積する。第1の転送トランジスタ103は、垂直読出し制御回路20から入力された制御信号φTX1−xxに応じて、光電変換部101に蓄積された光電変換信号を、基板間接続部13を介して電荷蓄積部110に転送する。電荷蓄積部110は、光電変換信号を保持(蓄積)する容量である。第1の転送トランジスタ103によって転送された光電変換信号は、電荷蓄積部110に蓄積される。

【0056】

なお、上述した制御信号の信号名「制御信号φTX1−xx」の内、制御信号の名称「制御信号φTX1」の後の「−」に続く「xx」の部分は、画素アレイ部40内に配置されている単位画素50の行番号を表す部分である。以下の説明においては、上述した制御信号φTX1も含め、画素アレイ部40内に配置されている単位画素50の行番号の数字を、それぞれの制御信号の「xx」の部分に記述する。なお、「xx」の部分に行番号の数字を記述せず、そのまま“xx”と記述した場合には、今回の説明におけるこの制御信号は、画素アレイ部40の特定の行の制御信号ではなく、画素アレイ部40の行毎に異なる制御信号であり、適宜行番号を当てはめて考えることができる制御信号であることを表す。

【0057】

第2の転送トランジスタ104は、垂直読出し制御回路20から入力された制御信号φTX2−xxに応じて、電荷蓄積部110に保持(蓄積)された光電変換信号を、増幅トランジスタ106のゲート端子に転送する。増幅トランジスタ106は、ゲート端子に転送された光電変換信号に応じた信号電圧を出力する。選択トランジスタ107は、垂直読出し制御回路20から入力された制御信号φSEL1−xxに応じて、増幅トランジスタ106が出力した信号電圧を、単位画素50が出力する画素信号として垂直信号線90に出力する。

【0058】

光電変換部リセットトランジスタ102は、垂直読出し制御回路20から入力された制御信号φFT1−xxに応じて、光電変換部101を電源電圧VDDにリセットする。画素リセットトランジスタ105は、垂直読出し制御回路20から入力された制御信号φRST1−xxに応じて、単位画素50内の信号を電源電圧VDDにリセットする。

【0059】

固体撮像装置1では、垂直読出し制御回路20が、全ての単位画素50を同時に制御することによって、グローバルシャッタ機能を実現している。より具体的には、垂直読出し制御回路20は、全ての単位画素50の制御信号φFT1−xxを同時に出力して、全ての単位画素50の光電変換部101による光電変換を同時に開始させる。そして、予め定められた露光時間が経過した後、垂直読出し制御回路20は、全ての単位画素50の制御信号φTX1−xxを同時に出力して、全ての単位画素50の光電変換部101が蓄積した光電変換信号を同時に、電荷蓄積部110に転送して保持させる。

【0060】

その後、固体撮像装置1では、垂直読出し制御回路20が、単位画素50を行毎に順次制御することによって、それぞれの単位画素50が光電変換した画素信号を、垂直信号線90に出力する。より具体的には、垂直読出し制御回路20は、単位画素50の行毎に制御信号φTX2−xx、制御信号φRST1−xx、制御信号φSEL1−xxを制御し、それぞれの電荷蓄積部110に保持された光電変換信号を、画素信号として垂直信号線90に順次出力(読み出し)させる。単位画素50では、それぞれの単位画素50が読み出されるまでに発生する、リークなどに起因するノイズによる信号の品質の劣化を、電荷蓄積部110を第2の基板に設けることによって抑圧している。

【0061】

次に、本第1の実施形態の固体撮像装置1内のカラム信号処理回路60について説明する。図4は、本第1の実施形態の固体撮像装置1内のカラム信号処理回路60の概略構成を示した回路図である。図4では、画素アレイ部40の1つの列に配置されたカラム信号処理回路60(シングルスロープ型AD変換器)を示している。また、図4には、図3に示した単位画素50を併せて示している。さらに、図4には、シングルスロープ型AD変換器にランプ波を出力する参照電圧生成部100も併せて示している。

【0062】

カラム信号処理回路60は、単位画素50が垂直信号線90に出力した画素信号に対して、アナログデジタル変換を行い、変換したデジタルの出力信号を水平信号線70に出力する。図4に示したカラム信号処理回路60の概略構成は、従来の固体撮像装置におけるカラム信号処理回路の構成と同様の構成である。ただし、本第1の実施形態の固体撮像装置1においては、図4に示したように、それぞれのカラム信号処理回路60内の各構成要素を、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置している。

【0063】

図4において、カラム信号処理回路60は、第1の基板のカラム信号処理部14に形成された比較器16と、第2の基板のカラム信号処理部15に形成されたカウンタ&ラッチ部19とから構成される。また、垂直信号線90と第1の基板のカラム信号処理部14とは、図3に示した単位画素50における第1の基板の画素部11と第2の基板の画素部12との接続と同様に、基板間接続部17によって接続され、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とは、基板間接続部18によって接続される。なお、参照電圧生成部100は、第1の基板に配置する。

【0064】

図4に示したように、カラム信号処理回路60では、アナログの動作を行う比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、デジタルの動作を行うカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。

【0065】

基板間接続部17および基板間接続部18は、図3に示した基板間接続部13と同様に、第1の基板と第2の基板とを電気的に接続するための接続部であるため、詳細な説明は省略する。図4に示したカラム信号処理回路60では、画素信号として垂直信号線90に出力された、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧が、第1の基板のカラム信号処理部14内の比較器16の一方の入力端子に、基板間接続部17を介して印加(入力)される。また、参照電圧生成部100が生成したランプ波が、第1の基板のカラム信号処理部14内の比較器16の他方の入力端子に印加(入力)される。また、第1の基板のカラム信号処理部14内の比較器16による比較結果を表す信号(以下、「比較結果信号」という)が、第2の基板のカラム信号処理部15内のカウンタ&ラッチ部19に、基板間接続部18を介して入力される。

【0066】

参照電圧生成部100は、固体撮像装置制御信号発生回路10からの制御に応じて、固体撮像装置制御信号発生回路10から入力されるクロック信号に同期した一定の傾きを持ったランプ波(参照電圧)を、例えば、デジタルアナログ変換器を用いて生成する。参照電圧生成部100は、生成したランプ波を、比較器16に印加(出力)する。

【0067】

比較器16は、基板間接続部17を介して印加された画素信号のレベルと、参照電圧生成部100から印加されたランプ波のレベルとを比較する。例えば、比較器16は、画素信号のレベルとランプ波のレベルとの大小関係を比較する。そして、比較器16は、ランプ波のレベルと画素信号のレベルとが一致したことを表す比較結果信号を、カウンタ&ラッチ部19に出力する。

【0068】

カウンタ&ラッチ部19は、固体撮像装置制御信号発生回路10からの制御に応じて、固体撮像装置制御信号発生回路10から入力されるクロック信号のカウントを開始する。カウンタ&ラッチ部19が、カウントを開始するタイミングは、参照電圧生成部100がランプ波を出力するタイミングと同期したタイミングである。そして、カウンタ&ラッチ部19は、基板間接続部18を介して比較器16から比較結果信号が入力されたタイミングで、クロック信号のカウントを停止し、現在のカウント値を、単位画素50から出力された画素信号のレベルを表すデジタル信号、すなわち、アナログデジタル変換した結果のデジタル信号として、水平信号線70に出力する。

【0069】

このような動作によって、カラム信号処理回路60(シングルスロープ型AD変換器)は、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧をアナログデジタル変換処理することができる。これにより、固体撮像装置1は、入射した被写体光に応じたデジタル信号を、画像信号として出力することができる。

【0070】

また、カラム信号処理回路60を、図4に示したように、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置することによって、図8に示した従来の固体撮像装置800よりもチップ面積を有効活用することができ、固体撮像装置1の実装面積を縮小することができる。

【0071】

ここで、本第1の実施形態の固体撮像装置1の各構成要素の配置について説明する。図5は、本第1の実施形態の固体撮像装置1の各構成要素の各基板への配置の一例を示したレイアウト図である。図5は、固体撮像装置1に入射する被写体光の入射面側から見た各構成要素の配置を示している。なお、固体撮像装置1を形成する場合、図5(a)に示した第1の基板は、図5(b)に示した第2の基板の上側に重ねて形成、すなわち、第1の基板と第2の基板とを積層構成にする。

【0072】

図5に示したように、固体撮像装置1では、画素アレイ部40の画素部11と、カラム信号処理回路60のカラム信号処理部14と、参照電圧生成部100とを、第1の基板に配置する。また、固体撮像装置1では、画素アレイ部40の画素部12と、カラム信号処理回路60のカラム信号処理部15と、固体撮像装置制御信号発生回路10と、垂直読出し制御回路20と、水平読出し制御回路30と、出力回路80とを、第2の基板に配置する。

【0073】

図5に示した固体撮像装置1の各構成要素の各基板への配置の一例では、参照電圧生成部100を、出力回路80の直上に配置している。このように、固体撮像装置1の各構成要素を配置することにより、第1の基板と第2の基板とのチップ面積を、ほぼ同じ面積にすることができ、第1の基板において、回路が形成されていない調整領域を少なくすることができる。

【0074】

上記に述べたように、本第1の実施形態における固体撮像装置1では、画素アレイ部40内のそれぞれの単位画素50およびカラム信号処理回路60を、第1の基板と第2の基板とに分けて形成することによって、図5をみてわかるように、第1の基板と第2の基板との大きさの差を少なくすることができる。これにより、第1の基板内の調整領域を少なくすることができ、従来の固体撮像装置よりもチップ面積を有効に活用することができる。このことにより、固体撮像装置1の実装面積を縮小することができる。

【0075】

また、本第1の実施形態における固体撮像装置1では、信号処理回路の構成要素において、アナログの動作を行う比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、デジタルの動作を行うカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。すなわち、本第1の実施形態における固体撮像装置1では、信号処理回路の各構成要素がアナログの動作を行うか、デジタルの動作を行うかという基準に基づいて、各構成要素を、第1の基板または第2の基板のいずれかの基板に配置している。これにより、少なくとも一方の基板を、好適な半導体プロセス技術が適用された製造工程で作製することができる。例えば、第1の基板をアナログ回路に適した半導体プロセスで作製することができる。また、例えば、第2の基板をデジタル回路に適した半導体プロセスで作製することができる。このように、少なくとも一方の基板を好適な半導体プロセスで作製することができるように、信号処理回路の構成要素をそれぞれの基板に分けて配置することによって、固体撮像装置1のチップコストの低減と製造工程の削減とを図ることができる。なお、この場合には、カラム信号処理回路60内における動作速度など、他の要因も考慮して配置する回路を決定することが望ましい。

【0076】

なお、本第1の実施形態における固体撮像装置1では、図5に示した配置の一例において、出力回路80の直上に参照電圧生成部100を配置した例を示した。しかし、第1の基板と第2の基板とに配置する回路の面積がほぼ同じ面積になるように配置すれば、各基板への固体撮像装置1の各構成要素の配置は、図5に示した本第1の実施形態の構成に限定されるものではない。例えば、固体撮像装置1の各構成要素を、図6に示したように各基板に配置することもできる。

【0077】

図6は、本第1の実施形態の固体撮像装置1の各構成要素の各基板への配置の別の一例を示したレイアウト図である。図6に示した配置の一例でも、図5に示した配置の一例と同様に、固体撮像装置1に入射する被写体光の入射面側から見た各構成要素の配置を示している。なお、固体撮像装置1を形成する場合も、図5に示した配置の一例と同様に、図6(a)に示した第1の基板と、図6(b)に示した第2の基板とを積層構成にする。

【0078】

図6に示した固体撮像装置1の各構成要素の各基板への配置の別の一例でも、図5に示した配置の一例と同様に、画素アレイ部40の画素部11と、カラム信号処理回路60のカラム信号処理部14と、参照電圧生成部100とを、第1の基板に配置する。また、画素アレイ部40の画素部12と、カラム信号処理回路60のカラム信号処理部15と、固体撮像装置制御信号発生回路10と、垂直読出し制御回路20と、水平読出し制御回路30と、出力回路80とを、第2の基板に配置する。

【0079】

図6に示した配置の別の一例では、参照電圧生成部100を、垂直読出し制御回路20の直上に配置している。このように、第1の基板と第2の基板とに配置された画素アレイ部40以外の回路の配置は、第1の基板と第2の基板とに配置される回路の面積がほぼ同じ面積になる配置であれば、図5に示した配置の一例と同様に、第1の基板の調整領域を少なくし、チップ面積を有効に活用することができるという効果を得ることができる。そして、図5に示した配置の一例と同様に、固体撮像装置1の実装面積を縮小することができるという効果や、固体撮像装置1のチップコストの低減と製造工程の削減とを図ることができるという効果を得ることができる。

【0080】

<第2の実施形態>

次に、デジタルカメラ7に搭載した第2の実施形態の固体撮像装置について説明する。なお、本第2の実施形態の固体撮像装置は、図2に示した第1の実施形態の固体撮像装置1内のカラム信号処理回路60が異なる回路構成となっているのみであり、その他の構成要素は、第1の実施形態の固体撮像装置1と同様である。従って、本第2の実施形態の固体撮像装置の構成要素において、図2に示した第1の実施形態の固体撮像装置1と同様の構成要素には、同一の符号を付加して詳細な説明は省略する。

【0081】

図7は、本第2の実施形態による固体撮像装置内のカラム信号処理回路62の概略構成を示した回路図である。カラム信号処理回路62は、図4に示したカラム信号処理回路60と同様に、画素アレイ部40の各列に配置され、固体撮像装置制御信号発生回路10からの制御に応じて、各列の単位画素50からそれぞれ垂直信号線90に出力された画素信号に対して、ノイズ抑圧やアナログデジタル変換などの信号処理を行う。また、カラム信号処理回路62は、図4に示したカラム信号処理回路60と同様に、水平読出し制御回路30からの制御に応じて、画素信号に対して信号処理を行った出力信号を、水平信号線70に出力する。以下の説明においては、図4に示したカラム信号処理回路60と同様に、カラム信号処理回路62が、参照電圧生成部100から入力されたランプ波を用いてアナログデジタル変換を行うシングルスロープ型AD変換器で構成されているものとして説明する。

【0082】

図7では、図4に示したカラム信号処理回路60と同様に、画素アレイ部40の1つの列に配置されたカラム信号処理回路62(シングルスロープ型AD変換器)を示している。また、図7には、図4に示したカラム信号処理回路60と同様に、図3に示した単位画素50と、参照電圧生成部100とを併せて示している。図7に示したように、カラム信号処理回路62においても、カラム信号処理回路62内の各構成要素を、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置する。

【0083】

図7において、カラム信号処理回路62は、第1の基板のカラム信号処理部14に形成された比較器16およびレベルシフタ21と、第2の基板のカラム信号処理部15に形成されたカウンタ&ラッチ部19とから構成される。また、垂直信号線90と第1の基板のカラム信号処理部14とは、図4に示したカラム信号処理回路60と同様に、基板間接続部17によって接続され、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とは、基板間接続部18によって接続される。なお、参照電圧生成部100も、第1の基板に配置する。

【0084】

カラム信号処理回路62において、第1の基板に配置された比較器16を含むシングルスロープ型AD変換器の構成要素は、比較的高い電源電圧で駆動される。また、カラム信号処理回路62において、第2の基板に配置されたカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素は、比較的低い電源電圧で駆動される。また、参照電圧生成部100も、比較的高い電源電圧で駆動される。このため、図7に示したように、カラム信号処理回路62では、比較的高い電源電圧で駆動される比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、比較的低い電源電圧で駆動されるカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。そして、カラム信号処理回路62では、図4に示したカラム信号処理回路60に加えて、比較器16が出力する比較結果信号の信号レベルを下げるためのレベルシフタ21を備えている。

【0085】

なお、比較器16、カウンタ&ラッチ部19、および参照電圧生成部100の動作は、駆動する電源電圧が異なる以外は、図4に示したカラム信号処理回路60に備えた比較器16、カウンタ&ラッチ部19、および参照電圧生成部100の動作と同様であるため、詳細な説明は省略する。

【0086】

図7に示したカラム信号処理回路62では、図4に示したカラム信号処理回路60と同様に、画素信号として垂直信号線90に出力された、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧が、第1の基板のカラム信号処理部14内の比較器16の一方の入力端子に、基板間接続部17を介して印加(入力)される。また、カラム信号処理回路62では、図4に示したカラム信号処理回路60と同様に、参照電圧生成部100が生成したランプ波が、第1の基板のカラム信号処理部14内の比較器16の他方の入力端子に印加(入力)される。

【0087】

カラム信号処理回路62では、第1の基板のカラム信号処理部14内の比較器16による比較結果である比較結果信号が、第1の基板のカラム信号処理部14内のレベルシフタ21に出力される。レベルシフタ21は、比較器16から入力された、比較的高い電圧である比較結果信号の出力レベルを、第2の基板で使用される比較的低い電圧の比較結果信号に変換する。そして、レベルシフタ21は、出力レベルを変換した比較結果信号を、基板間接続部18を介して、第2の基板のカラム信号処理部15内のカウンタ&ラッチ部19に出力する。

【0088】

カウンタ&ラッチ部19は、出力レベルが変換された比較結果信号が入力されたタイミングで停止した現在のカウント値を、単位画素50から出力された画素信号のレベルをアナログデジタル変換した結果のデジタル信号として、水平信号線70に出力する。

【0089】

このような動作によって、カラム信号処理回路62(シングルスロープ型AD変換器)は、単位画素50内の電荷蓄積部110に保持(蓄積)された光電変換信号に応じた信号電圧をアナログデジタル変換処理することができる。これにより、本第2の実施形態の固体撮像装置1でも、第1の実施形態の固体撮像装置1と同様に、入射した被写体光に応じたデジタル信号を、画像信号として出力することができる。

【0090】

また、カラム信号処理回路62を、図7に示したように、第1の基板のカラム信号処理部14と第2の基板のカラム信号処理部15とに分けて配置することによって、回路が形成されていない調整領域を少なくし、チップ面積を有効活用することができる。そして、本第2の実施形態の固体撮像装置1でも、第1の実施形態の固体撮像装置1と同様に、固体撮像装置1の実装面積を縮小することができる。なお、本第2の実施形態の固体撮像装置1における各構成要素の各基板への配置は、図5および図6に示した配置の例と同様に考えることができるため、詳細な説明は省略する。

【0091】

上記に述べたように、本第2の実施形態における固体撮像装置1でも、画素アレイ部40内のそれぞれの単位画素50およびカラム信号処理回路62を、第1の基板と第2の基板とに分けて形成することによって、第1の実施形態の固体撮像装置1と同様に、第1の基板と第2の基板との大きさの差を少なくすることができる。これにより、第1の基板内の調整領域を少なくすることができ、従来の固体撮像装置よりもチップ面積を有効に活用し、第1の実施形態の固体撮像装置1と同様に、固体撮像装置1の実装面積を縮小することができる。

【0092】

また、本第2の実施形態における固体撮像装置1では、信号処理回路の構成要素において、比較的高い電源電圧で駆動される比較器16を含むシングルスロープ型AD変換器の構成要素および参照電圧生成部100を第1の基板に配置し、比較的低い電源電圧で駆動されるカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を第2の基板に配置している。また、第1の基板に配置されたシングルスロープ型AD変換器の構成要素と、第2の基板に配置されたシングルスロープ型AD変換器の構成要素との間の信号レベルを合わせるため、レベルシフタ21を配置している。すなわち、本第2の実施形態における固体撮像装置1では、信号処理回路の各構成要素を駆動する電源電圧が比較的高いか低いかという基準に基づいて、各構成要素を、第1の基板または第2の基板のいずれかの基板に配置している。これにより、例えば、第2の基板のカラム信号処理部15内に配置するカウンタ&ラッチ部19を含むシングルスロープ型AD変換器の構成要素を形成する際に、耐圧電圧が低い微細な半導体プロセス技術を適用することができる。このことにより、固体撮像装置1の実装面積をさらに縮小することができ、固体撮像装置1のチップコストの低減を図ることができる。なお、この場合にも、カラム信号処理回路60内における動作速度など、他の要因も考慮して配置する回路を決定することが望ましい。

【0093】

上記に述べたように、本発明を実施するための形態によれば、予め定めた基準に基づいて、固体撮像装置の信号処理回路の各構成要素を、第1の基板と第2の基板とに分けて形成する。これにより、固体撮像装置を形成する第1の基板と第2の基板との大きさの差を少なくすることができる。このことにより、固体撮像装置の製造やチップに係るコストの削減を図ることができる。

【0094】

さらに、本発明を実施するための形態によれば、固体撮像装置を形成する第1の基板と第2の基板とを別々に作製することできるため、第1の基板と第2の基板とのそれぞれに適した半導体プロセスを使用することができる。これにより、固体撮像装置のコスト低減を図ることができる。

【0095】

また、本発明を実施するための形態によれば、ノイズ抑圧やアナログデジタル変換などの信号処理を行う信号処理回路を、第1の基板と第2の基板とに分けて形成するため、小さなチップ面積(実装面積)で信号処理回路を実現することができ、高品質な画像を得ることができる固体撮像装置を実現することができる。

【0096】

なお、本発明のある態様に係る固体撮像装置は、本実施形態においては、例えば、固体撮像装置1に対応し、撮像装置は、例えば、デジタルカメラ7に対応し、接続部は、例えば、基板間接続部13と、基板間接続部17と、基板間接続部18に対応する。また、本発明のある態様に係る光電変換素子は、本実施形態においては、例えば、光電変換部101に対応し、読み出し回路は、例えば、第2の転送トランジスタ104と、増幅トランジスタ106と、選択トランジスタ107とに対応し、信号処理回路は、例えば、カラム信号処理回路60と、参照電圧生成部100とに対応する。

【0097】

また、本発明のある態様に係る画素部は、本実施形態においては、例えば、画素アレイ部40、または画素部11および画素部12に対応し、画素は、例えば、単位画素50に対応し、第1信号処理回路に区分された回路要素は、例えば、比較器16およびレベルシフタ21、またはカラム信号処理部14に対応し、第2信号処理回路に区分された回路要素は、例えば、カウンタ&ラッチ部19、またはカラム信号処理部15に対応する。

【0098】

また、本発明のある態様に係る比較器は、本実施形態においては、例えば、比較器16に対応し、カウンタおよびラッチは、例えば、カウンタ&ラッチ部19に対応し、レベルシフタは、例えば、レベルシフタ21に対応し、参照電圧生成部は、例えば、参照電圧生成部100に対応する。

【0099】

また、本発明のある態様に係る読み出しトランジスタは、本実施形態においては、例えば、第2の転送トランジスタ104と、増幅トランジスタ106と、選択トランジスタ107に対応する。

【0100】

なお、本発明における具体的な構成は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更をすることができる。例えば、本発明を実施するための形態においては、シングルスロープ型AD変換器を用いて信号処理回路を構成した場合について説明したが、シングルスロープ型AD変換器の代わりに、パイプライン型AD変換器、デルタシグマ型AD変換器、または時間変換型AD変換器を用いて信号処理回路を構成することもできる。また、例えば、AD変換器のみではなく、他の信号処理回路やカラム信号処理回路であっても、それぞれの回路の動作や電源電圧に応じて第1の基板と第2の基板とに分割して配置することができれば、本発明を実施するための形態と同様に、チップ面積を有効に活用することができる。このことにより、少なくとも一方の基板を、好適な半導体プロセス技術が適用された製造工程で作製することができ、固体撮像装置の実装面積を縮小することができるという効果や、固体撮像装置のチップコストの低減と製造工程の削減とを図ることができるという効果を得ることができる。

【0101】

また、本発明における回路構成および駆動方法の具体的な構成は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の変更をすることができる。例えば、画素や信号処理回路の構成要素および駆動方法が変わった場合においても、固体撮像装置、単位画素、信号処理回路、またはカラム信号処理回路内の構成要素や回路構成に応じて駆動方法を変更することによって対応することができる。

【0102】

また、画素の行方向および列方向の配置は、本発明を実施するための形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において画素を配置する行方向および列方向の数を変更することができる。

【0103】

以上、本発明を実施するための形態をもとに説明したが、各構成要素や各処理プロセスの任意の組み合わせ、本発明の表現をコンピュータプログラムプロダクトなどに変換したものもまた、本発明の態様として有効である。ここで、コンピュータプログラムプロダクトとは、プログラムコードが記録された記録媒体(DVD媒体、ハードディスク媒体、メモリ媒体など)、プログラムコードが記録されたコンピュータ、プログラムコードが記録されたインターネットシステム(例えば、サーバとクライアント端末を含むシステム)など、プログラムコードが記録された記録媒体、装置、機器やシステムをいう。この場合、上述した各構成要素や各処理プロセスは各モジュールで実装され、その実装されたモジュールからなるプログラムコードはコンピュータプログラムプロダクト内に記録される。

【0104】

例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0105】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0106】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置された読み出し回路によって、前記接続部を経由して読み出し、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0107】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの回路要素が第1信号処理回路または第2信号処理回路に区分され、前記第1信号処理回路に区分された前記回路要素が前記第1の基板内に配置され、前記第2信号処理回路に区分された前記回路要素が前記第2の基板内に配置された信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0108】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された前記読み出し信号に対してアナログ信号処理を行う第1信号処理回路と、前記第2の基板に配置された前記第1信号処理回路によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせ、該読み出し信号に応じたデジタルの信号に変換させる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0109】

また、例えば、本発明のある態様に係るコンピュータプログラムプロダクトは、第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置の処理をコンピュータに実行させるためのプログラムコードが記録されたコンピュータプログラムプロダクトであって、前記第1の基板に配置された光電変換素子が入射光量に応じて発生した信号を、前記第2の基板に前記光電変換素子に対応して配置され、前記接続部を経由してソースおよびドレインの一方に受ける読み出しトランジスタのソースおよびドレインの他方から、アナログの読み出し信号として出力させる読み出しモジュールと、前記第1の基板に配置された所定の基準値よりも高い電源電圧で駆動する第1信号処理回路と、前記第2の基板に配置された前記所定の基準値よりも低い電源電圧で駆動する第2信号処理回路と、を備えた信号処理回路によって、前記読み出し信号に対して信号処理を行わせる信号処理モジュールと、を含むプログラムコードが記録されたコンピュータプログラムプロダクトである。

【0110】

また、例えば、図1に示したデジタルカメラ7の各構成要素による処理を実現するためのプログラムをコンピュータ読み取り可能な記録媒体に記録して、当該記録媒体に記録されたプログラムをコンピュータシステムに読み込ませ、実行することにより、デジタルカメラ7に係る上述した種々の処理を行ってもよい。なお、ここでいう「コンピュータシステム」とは、OSや周辺機器等のハードウェアを含むものであってもよい。また、「コンピュータシステム」は、WWWシステムを利用している場合であれば、ホームページ提供環境(あるいは表示環境)も含むものとする。また、「コンピュータ読み取り可能な記録媒体」とは、フレキシブルディスク、光磁気ディスク、ROM、フラッシュメモリ等の書き込み可能な不揮発性メモリ、CD−ROM等の可搬媒体、コンピュータシステムに内蔵されるハードディスク等の記憶装置のことをいう。

【0111】

さらに「コンピュータ読み取り可能な記録媒体」とは、インターネット等のネットワークや電話回線等の通信回線を介してプログラムが送信された場合のサーバやクライアントとなるコンピュータシステム内部の揮発性メモリ(例えばDRAM(Dynamic Random Access Memory))のように、一定時間プログラムを保持しているものも含むものとする。また、上記プログラムは、このプログラムを記憶装置等に格納したコンピュータシステムから、伝送媒体を介して、あるいは、伝送媒体中の伝送波により他のコンピュータシステムに伝送されてもよい。ここで、プログラムを伝送する「伝送媒体」は、インターネット等のネットワーク(通信網)や電話回線等の通信回線(通信線)のように情報を伝送する機能を有する媒体のことをいう。また、上記プログラムは、前述した機能の一部を実現するためのものであっても良い。さらに、前述した機能をコンピュータシステムにすでに記録されているプログラムとの組み合わせで実現できるもの、いわゆる差分ファイル(差分プログラム)であっても良い。

【0112】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲においての種々の変更も含まれる。

【0113】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする固体撮像装置であってもよい。

【0114】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0115】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0116】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする撮像装置であってもよい。

【0117】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0118】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由して読み出し、アナログの読み出し信号として出力する読み出し手段と、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0119】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする固体撮像装置であってもよい。

【0120】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0121】

また、本発明のある態様に係る固体撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された固体撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする固体撮像装置であってもよい。

【0122】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理手段と、を備え、前記信号処理手段は、当該信号処理手段を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理手段または第2信号処理手段に区分し、前記第1信号処理手段に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理手段に区分された前記回路要素を前記第2の基板内に配置する、ことを特徴とする撮像装置であってもよい。

【0123】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行い、該読み出し信号に応じたデジタルの信号に変換する信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、前記読み出し信号に対してアナログ信号処理を行う第1信号処理手段と、前記第2の基板に配置され、前記第1信号処理手段によってアナログ信号処理された読み出し信号に対してデジタル信号処理を行う第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0124】

また、本発明のある態様に係る撮像装置は、第1の基板と第2の基板とが、接続手段によって電気的に接続された撮像装置であって、前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換手段と、前記第2の基板に前記光電変換手段に対応して配置され、対応する前記光電変換手段で発生した信号を、対応する前記接続手段を経由してソースおよびドレインの一方に受け、ソースおよびドレインの他方から、アナログの読み出し信号として出力する読み出しトランジスタと、を具備する画素が、複数配置された画素手段と、前記読み出し信号に対して信号処理を行う信号処理手段と、を備え、前記信号処理手段は、前記第1の基板に配置され、所定の基準値よりも高い電源電圧で駆動する第1信号処理手段と、前記第2の基板に配置され、前記所定の基準値よりも低い電源電圧で駆動する第2信号処理手段と、を備える、ことを特徴とする撮像装置であってもよい。

【0125】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲において種々の代替物、変形、等価物による変更を行うこともできる。従って、本発明の範囲は、上記の説明を参照して決められるものではなく、請求項によって決められるべきであり、均等物の全ての範囲も含まれる。また、上述した特徴は、いずれも、好ましいか否かを問わず、他の特徴と組み合わせてもよい。また、請求項において、明示的に断らない限り、各構成要素は1またはそれ以上の数量である。また、請求項において「〜のための手段」のような語句を用いて明示的に記載する場合を除いて、請求項が、ミーンズ・プラス・ファンクションの限定を含むものと解してはならない。

【0126】

また、本発明の実施形態に係る固体撮像装置は、2枚の基板が接続部により接続されていてもよいし、3枚以上の基板が接続部で接続されていてもよい。3枚以上の基板が接続部で接続される固体撮像装置の場合、そのうちの2枚が請求項に係る第1の基板と第2の基板に相当する。

【符号の説明】

【0127】

1・・・固体撮像装置

2・・・レンズユニット部

3・・・画像信号処理装置

4・・・記録装置

5・・・カメラ制御装置

6・・・表示装置

7・・・デジタルカメラ

10・・・固体撮像装置制御信号発生回路

20・・・垂直読出し制御回路

30・・・水平読出し制御回路

40・・・画素アレイ部

50・・・単位画素

11・・・画素部

12・・・画素部

101・・・光電変換部

102・・・光電変換部リセットトランジスタ

103・・・第1の転送トランジスタ

104・・・第2の転送トランジスタ

105・・・画素リセットトランジスタ

106・・・増幅トランジスタ

107・・・選択トランジスタ

110・・・電荷蓄積部

13・・・基板間接続部

60,62・・・カラム信号処理回路

14・・・カラム信号処理部

15・・・カラム信号処理部

16・・・比較器

17・・・基板間接続部

18・・・基板間接続部

19・・・カウンタ&ラッチ部

21・・・レベルシフタ

70・・・水平信号線

80・・・出力回路

90・・・垂直信号線

100・・・参照電圧生成部

800・・・固体撮像装置

【特許請求の範囲】

【請求項1】

第1の基板と第2の基板とが、接続部によって電気的に接続された固体撮像装置であって、

前記第1の基板に配置され、入射光量に応じた信号を発生させる光電変換素子と、

前記第2の基板に前記光電変換素子に対応して配置され、対応する前記光電変換素子で発生した信号を、対応する前記接続部を経由して読み出し、アナログの読み出し信号として出力する読み出し回路と、

を具備する画素が、複数配置された画素部と、

前記読み出し信号に対して信号処理を行う回路要素を具備した信号処理回路と、

を備え、

前記信号処理回路は、

当該信号処理回路を構成する前記回路要素を、前記第1の基板側または前記第2の基板側に区分するための基準である区分基準に基づいて、それぞれの前記回路要素を、第1信号処理回路または第2信号処理回路に区分し、前記第1信号処理回路に区分された前記回路要素を前記第1の基板内に配置し、前記第2信号処理回路に区分された前記回路要素を前記第2の基板内に配置する、

ことを特徴とする固体撮像装置。