基準電流源回路

【課題】基準電圧の変動に影響されずに基準電流を出力する。

【解決手段】第1の電圧源トランジスタ(Tr1)のバイアス回路として第1のオペアンプ(OP1)の負帰還回路を用いる第1の帰還形定電圧回路と、第2の電圧源トランジスタ(Tr2)のバイアス回路として第2のオペアンプ(OP2)の正帰還回路を用いる第2の帰還形定電圧回路と、Tr1の第1の端子と電源端子との間に接続されかつ基準電流を出力するカレントミラー回路と、Tr1の第2の端子とTr2の第1の端子間に接続される基準抵抗と、Tr1の第1の端子とグランド端子との間に直列に接続される抵抗Ra,Rbと、基準電圧が印加されるバイアス電圧入力端子とを有し、バイアス電圧入力端子はOP1の反転入力端子に接続され、OP2の反転入力端子は抵抗Raと抵抗Rbとの間のノードに接続され、Tr2の第2の端子はグランド端子に接続されている。

【解決手段】第1の電圧源トランジスタ(Tr1)のバイアス回路として第1のオペアンプ(OP1)の負帰還回路を用いる第1の帰還形定電圧回路と、第2の電圧源トランジスタ(Tr2)のバイアス回路として第2のオペアンプ(OP2)の正帰還回路を用いる第2の帰還形定電圧回路と、Tr1の第1の端子と電源端子との間に接続されかつ基準電流を出力するカレントミラー回路と、Tr1の第2の端子とTr2の第1の端子間に接続される基準抵抗と、Tr1の第1の端子とグランド端子との間に直列に接続される抵抗Ra,Rbと、基準電圧が印加されるバイアス電圧入力端子とを有し、バイアス電圧入力端子はOP1の反転入力端子に接続され、OP2の反転入力端子は抵抗Raと抵抗Rbとの間のノードに接続され、Tr2の第2の端子はグランド端子に接続されている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は基準電流源回路に係わり、特に消費電流の低減が図れる基準電流源回路に関する。

【背景技術】

【0002】

各種電子機器等に組み込まれるアナログ回路の多くは、回路のバイアス電流が不可欠であり、そのための基準電流源が存在する。この基準電流源は常に一定の基準電流(Iref)を出力する(例えば、特許文献1)。

【0003】

【特許文献1】特開平10−132601号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来、基準電流(Iref)を作る場合、通常は基準電圧(Vref)を基準に種々の抵抗体で電流変換して形成する。しかし、基準電圧(Vref)の電圧値(Vref値)が変動すると、基準電流(Iref)の電流値(Iref値)が変動し、Iref値を高精度に得難い。

【0005】

本発明の目的は基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することにある。

本発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面からあきらかになるであろう。

【課題を解決するための手段】

【0006】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記のとおりである。

(1)基準電流源回路は、

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第1の電圧源トランジスタの前記第1の端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする。また、前記基準抵抗の両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることを特徴とする。

【発明の効果】

【0007】

本願において開示される発明のうち代表的なものによって得られる効果を簡単

に説明すれば、下記のとおりである。

前記(1)の手段によれば、(a)2つの差動電圧源(第1及び第2の帰還形定電圧回路)を用いることから、基準電圧(Vref)が変動しても2つの差動電圧源から出力される電圧の電圧差は不変である。この結果、Ra,Rbに流れる電流がRcに流れる電流に比較して10分の1の場合、基準電流(Iref)の変動も10分の1となり、高精度に基準電流(Iref)をアナログ回路に供給することができる。

【0008】

(b)また、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで、良好な温度特性を維持しつつ単位面積あたりの抵抗率が小さい抵抗体のみ使用する半導体集積回路のレイアウト面積より大きさを低減できる。2つの差動電圧源(第1及び第2の帰還形定電圧回路)から出力される電圧の電圧差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることにより、基準電流源を構成する抵抗体の面積の縮小が可能になる。例えば、基準抵抗(変換抵抗)Rcに対して1.25Vを印加する場合に比較して、基準抵抗Rcの両端間の電位差を0.03Vとした場合、基準抵抗Rcの面積を約1/38に低減できる。この低減値は、バイアス電圧入力端子の基準電圧(Vref)のVref値(V1)を1.25Vとし、Raを100kΩ、Rbを4MΩ、Rcを10kΩとした場合である。ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0009】

(c)温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体を適用する基準抵抗(変換抵抗)Rcでは、基準抵抗Rcの両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)と小さくすることから、良好な温度特性を維持しつつ消費電流の低減が図れる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【実施例1】

【0011】

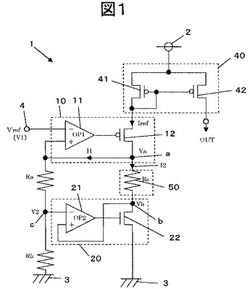

図1は本発明の実施例1である基準電流源回路を示す回路図である。基準電圧源回路1は、図1に示すように、2つの差動電圧源として第1の帰還形定電圧回路10及び第2の帰還形定電圧回路20を有している。第1の帰還形定電圧回路10は第1のオペアンプ(OP1)11と、この第1のオペアンプ11の出力端子に接続される第1の電圧源トランジスタ(Tr1)12からなっている。第1の電圧源トランジスタ12は、例えば、PMOSからなり、制御端子(ゲート電極)が第1のオペアンプ11の出力端子に接続されている。

【0012】

第2の帰還形定電圧回路20は第2のオペアンプ(OP2)21と、この第2のオペアンプ21の出力端子に接続される第2の電圧源トランジスタ(Tr2)22からなっている。第2の電圧源トランジスタ22は、例えば、NMOSからなり、制御端子(ゲート電極)が第2のオペアンプ21の出力端子に接続されている。

【0013】

第1の電圧源トランジスタ12の第1の端子(ドレイン電極)と、第1基準電圧(電源)が供給される第1基準電圧端子(電源端子)2との間には、基準電流(Iref)を出力するカレントミラー回路40が接続されている。カレントミラー回路40は、制御端子(ゲート電極)同士が接続された同一の特性を有するPMOS41,42を有する。PMOS41の制御端子は第1の電圧源トランジスタ12の第1の端子に接続されている。また、両方のPMOS41,42の第1の端子(ドレイン電極)は第1基準電圧端子2に接続されている。これによりカレントミラー回路40が構成され、PMOS42の第2の端子(ソース電極)から基準電流(Iref)が出力される。このカレントミラー回路40は基準電流(Iref)を負荷に吐出する吐出形である。

【0014】

一方、第1の電圧源トランジスタ12の第2の端子(ソース電極)と、第2の電圧源トランジスタ22の第1の端子(ドレイン電極)間には基準抵抗(変換抵抗)50が直列に接続されている。基準抵抗(Rc)50と第1の電圧源トランジスタ12との交点部分(ノード)aでの電圧はVaとなり、基準抵抗(Rc)50と第2の電圧源トランジスタ22とのノードbでの電圧はVbとなる。

【0015】

また、第1の電圧源トランジスタ12の第1の端子と、第2基準電圧(接地電位、グランド)が供給される第2基準電圧端子(グランド端子)3との間には2個の抵抗Ra,抵抗Rbが直列に接続されている。そして、第1の電圧源トランジスタ12の第1の端子と、第1のオペアンプ11の非反転入力端子(+)が接続されている。また、抵抗Raと抵抗Rbの抵抗分圧による電圧が第2のオペアンプ21の反転入力端子(−)に印加されるようになっている。即ち、抵抗Raと前記抵抗Rbとの間のノードcと、第2のオペアンプ21の反転入力端子(−)が接続されている。ノードcの電圧をV2とする。また、ノードaから第1のオペアンプ11及び抵抗Raに向かって流れる電流をI1とし、ノードaから基準抵抗(Rc)50に向かって流れる電流をI2とする。第1のオペアンプ11の反転入力端子(−)は基準電圧(Vref)が印加されるバイアス電圧入力端子4に接続されている。これにより、第1の帰還形定電圧回路10は第1の電圧源トランジスタ12のバイアス回路として第1のオペアンプ11の負帰還回路を用いる構造となる。基準電圧(Vref)としてV1が供給される。カレントミラー回路40のPMOS42の第2の端子からIref値を有する基準電流(Iref)が出力される。

【0016】

さらに、第2の帰還形定電圧回路20の第2の電圧源トランジスタ22の第2の端子(ソース電極)は第2基準電位端子3に接続されている。また、ノードbと第2のオペアンプ21の非反転入力端子(+)が接続されている。これにより、第2の帰還形定電圧回路20は第2の電圧源トランジスタ22のバイアス回路として第2のオペアンプ21の正帰還回路を用いる構造となる。

【0017】

つぎに、回路動作における電流及び電圧の関係について説明する。

第1の帰還形定電圧回路10でVaを作り、第2の帰還形定電圧回路20でVbを作り、基準抵抗(Rc)50に対してVa−Vbを印加する。

【0018】

オペアンプの直流電流(DC)のオフセットを0とした場合

Va=V1、Vb=V2、Iref=I1+I2となる。

【0019】

従って、I1は次式で与えられる。

【数1】

【0020】

また、V2は次式で与えられる。

【数2】

【0021】

また、I2は次式で与えられる。

【数3】

【0022】

ここで、一例について説明する。

V1=1.25V、Ra=100kΩ、Rb=4MΩ、Rc=10kΩとした場合、Va=1.25Vとなる。

【0023】

従って、

【数4】

となる。

【0024】

また、

V2=305n×4M≒1.22となる。

【0025】

従って、

【数5】

となる。

【0026】

また、Iref=305nA+3μA≒3.3μAとなる。

【0027】

基準電流源回路1では基準抵抗(Rc)50が10kΩで、基準電流(Iref)が3.3μAを実現できるが、1.25VをそのままV−I変換した場合、

【数6】

になり、抵抗値(抵抗体)、即ち、基準抵抗(Rc)50を約1/38に低減することができる。なお、ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0028】

実施例1によれば以下の効果を有する。

(1)2つの差動電圧源(第1及び第2の帰還形定電圧回路)を用いることから、基準電圧(Vref)が変動しても2つの差動電圧源から出力される電圧の電圧差は不変である。この結果、Ra,Rbに流れる電流がRcに流れる電流に比較して10分の1の場合、基準電流(Iref)の変動も10分の1となり、高精度に基準電流(Iref)をアナログ回路に供給することができる。

【0029】

(2)また、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、単位面積あたりの抵抗率が小さい抵抗体のみを使用する半導体集積回路よりレイアウト面積を低減できる。2つの差動電圧源(第1及び第2の帰還形定電圧回路)から出力される電圧の電圧差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることにより、基準電流源を構成する抵抗体の面積の縮小が可能になる。例えば、基準抵抗(変換抵抗)Rcに対して1.25Vを印加する場合に比較して、基準抵抗Rcの両端間の電位差を0.03Vとした場合、基準抵抗Rcの面積を約1/38に低減できる。この低減値は、バイアス電圧入力端子の基準電圧(Vref)のVref値(V1)を1.25Vとし、Raを100kΩ、Rbを4MΩ、Rcを10kΩとした場合である。なお、ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0030】

(3)温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体を適用する基準抵抗(変換抵抗)Rcでは、基準抵抗Rcの両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)と小さくすることから、良好な温度特性を維持しつつ消費電流の低減が図れる。

【0031】

(4)基準電流源回路1では、第1の帰還形定電圧回路10の第1の電圧源トランジスタ12をPMOSで形成していることからNMOSで構成する場合に比較して、オペアンプが印加できるゲート電極対ソース電極間電位を大きくできる。よってトランジスタサイズ低減と動作可能電圧範囲を拡大できる効果を有する。また、第2の帰還形定電圧回路20の第2の電圧源トランジスタ22をNMOSで形成していることからPMOSで構成する場合に比較して、オペアンプが印加できるゲート電極対ソース電極間電位を大きくできる。よってトランジスタサイズ低減と動作可能電圧範囲を拡大できる効果を有する。

【実施例2】

【0032】

図2は本発明の実施例2である基準電流源回路を示す回路図である。

実施例2の基準電流源回路1は、実施例1の基準電流源回路1において、基準電流(Iref)を出力するカレントミラー回路を第1の電圧源トランジスタ12側に設けず、第2の電圧源トランジスタ22側に設ける構成になっている。他の部分は実施例1の基準電流源回路1と同じである。

【0033】

実施例2の基準電流源回路1では、第1の帰還形定電圧回路10の第1の電圧源トランジスタ12の第1の端子(ドレイン電極)は直接第1基準電位端子2に接続されている。そして、第2の帰還形定電圧回路20の第1の電圧源トランジスタ12の第2の端子(ソース電極)と、グランドとなる第2基準電位端子3との間にカレントミラー回路60を接続した構造になっている。

【0034】

カレントミラー回路60は、制御端子(ゲート電極)同士が接続された同一の特性を有するNMOS61,62を有する。NMOS61の制御端子は第2の電圧源トランジスタ22の第2の端子(ソース電極)に接続されている。また、両方のNMOS61,62の第2の端子(ソース電極)は第2基準電位端子3に接続されている。これによりカレントミラー回路60が構成され、NMOS62の第1の端子(ドレイン電極)から基準電流(Iref)を吸い込むようになっている。このカレントミラー回路60は基準電流(Iref)を負荷から吸い込む吸込形である。

【0035】

実施例2によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができる。即ち、実施例2の基準電流源回路1は、基準電流(Iref)出力をNMOSにしたことから、基準電流(Iref)からI1を除外できるため、V1の影響を受けない。また、実施例2の基準電流源回路1においても実施例1の基準電流源回路1と同様に温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【実施例3】

【0036】

図3は本発明の実施例3である基準電流源回路を示す回路図である。

実施例3の基準電流源回路1は、実施例1において、抵抗Ra,抵抗Rbは第1の電圧源トランジスタ12の第2の端子と第2基準電位端子3との間に設けることなく、バイアス電圧入力端子4と第2基準電位端子3との間に抵抗Ra,抵抗Rbと直列に接続した構成になっている。そして、抵抗Ra,抵抗Rbの抵抗分圧電圧を第2の帰還形定電圧回路20の反転入力端子(−)に印加する構造になっている。換言するならば、抵抗Raと抵抗Rbのノードcと第2のオペアンプ21の反転入力端子(−)を接続したものである。

【0037】

実施例3では、第1の電圧源トランジスタ12の第1の端子(ドレイン電極)と第1基準電位端子2との間に、図1で示す吐出形のカレントミラー回路40を接続し、第2の電圧源トランジスタ22の第2の端子(ソース電極)と第2基準電位端子3との間に、図2で示す吸込形のカレントミラー回路60を接続してカレントミラー回路構成の出力構造としている。

【0038】

実施例3の基準電流源回路1は、抵抗RaにV1を入れるタイプであることから、基準電流(Iref)のV1依存がなくなり、より高精度に基準電流(Iref)を出力することができる。

【0039】

実施例3によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができるとともに、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【0040】

なお、実施例3の基準電流源回路1を半導体チップにモノリシックに形成した段階では、第1のオペアンプ11と第2のオペアンプ21のDCオフセット次第ではVbがVaより高くなり、回路動作しない場合がある。このような場合、基準抵抗(Rc)50の抵抗値を調整できる構造、例えば、フユーズトリミングできる構造にしておき、回路動作しない場合Va及びVbが適正になるようにフユーズトリミングすることによって基準電流源回路1を正しく動作させることができる。

【実施例4】

【0041】

図4は本発明の実施例4である基準電流源回路を示す回路図である。

実施例4の基準電流源回路1は、実施例1の基準電流源回路1において、基準電圧(Vref)をバイアス電圧入力端子4に供給する構成ではなく、電源を抵抗分圧して基準電圧(Vref)を生成する回路である。即ち、図4に示すように、電源が供給される第1基準電位端子2とグランドとなる第2基準電位端子3との間に、抵抗Rd,抵抗Ra,抵抗Rbを直列に接続し、抵抗Rdと抵抗Raとの間のノードdと第1のオペアンプ11の反転入力端子(−)を接続する構造になっている。ノードdの電圧が基準電圧(Vref)となる。また、抵抗Raと抵抗Rbの間のノードcは、実施例3と同様に第2のオペアンプ21の反転入力端子(−)に接続されている。

【0042】

実施例4の基準電流源回路1は、バイアス電圧入力端子4を設けなくともよい利点がある。実施例4によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができるとともに、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【0043】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。なお、実施例1の基準電流源回路1における基準電流(Iref)を出力する出力回路を、実施例3のように吐出形のカレントミラー回路40と、吸込形のカレントミラー回路60で構成してもよいことは勿論である。

【図面の簡単な説明】

【0044】

【図1】本発明の実施例1である基準電流源回路を示す回路図である。

【図2】本発明の実施例2である基準電流源回路を示す回路図である。

【図3】本発明の実施例3である基準電流源回路を示す回路図である。

【図4】本発明の実施例4である基準電流源回路を示す回路図である。

【符号の説明】

【0045】

1…基準電流源回路、2…第1基準電位端子、3…第2基準電位端子、4…バイアス電圧入力端子、10…第1の帰還形定電圧回路、11…第1のオペアンプ、12…第1の電圧源トランジスタ、20…第2の帰還形定電圧回路、21…第2のオペアンプ、22…第2の電圧源トランジスタ、40…カレントミラー回路、41,42…PMOS、50…基準抵抗(変換抵抗)、60…カレントミラー回路、61,62…NMOS。

【技術分野】

【0001】

本発明は基準電流源回路に係わり、特に消費電流の低減が図れる基準電流源回路に関する。

【背景技術】

【0002】

各種電子機器等に組み込まれるアナログ回路の多くは、回路のバイアス電流が不可欠であり、そのための基準電流源が存在する。この基準電流源は常に一定の基準電流(Iref)を出力する(例えば、特許文献1)。

【0003】

【特許文献1】特開平10−132601号公報

【発明の開示】

【発明が解決しようとする課題】

【0004】

従来、基準電流(Iref)を作る場合、通常は基準電圧(Vref)を基準に種々の抵抗体で電流変換して形成する。しかし、基準電圧(Vref)の電圧値(Vref値)が変動すると、基準電流(Iref)の電流値(Iref値)が変動し、Iref値を高精度に得難い。

【0005】

本発明の目的は基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することにある。

本発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面からあきらかになるであろう。

【課題を解決するための手段】

【0006】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記のとおりである。

(1)基準電流源回路は、

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第1の電圧源トランジスタの前記第1の端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする。また、前記基準抵抗の両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることを特徴とする。

【発明の効果】

【0007】

本願において開示される発明のうち代表的なものによって得られる効果を簡単

に説明すれば、下記のとおりである。

前記(1)の手段によれば、(a)2つの差動電圧源(第1及び第2の帰還形定電圧回路)を用いることから、基準電圧(Vref)が変動しても2つの差動電圧源から出力される電圧の電圧差は不変である。この結果、Ra,Rbに流れる電流がRcに流れる電流に比較して10分の1の場合、基準電流(Iref)の変動も10分の1となり、高精度に基準電流(Iref)をアナログ回路に供給することができる。

【0008】

(b)また、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで、良好な温度特性を維持しつつ単位面積あたりの抵抗率が小さい抵抗体のみ使用する半導体集積回路のレイアウト面積より大きさを低減できる。2つの差動電圧源(第1及び第2の帰還形定電圧回路)から出力される電圧の電圧差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることにより、基準電流源を構成する抵抗体の面積の縮小が可能になる。例えば、基準抵抗(変換抵抗)Rcに対して1.25Vを印加する場合に比較して、基準抵抗Rcの両端間の電位差を0.03Vとした場合、基準抵抗Rcの面積を約1/38に低減できる。この低減値は、バイアス電圧入力端子の基準電圧(Vref)のVref値(V1)を1.25Vとし、Raを100kΩ、Rbを4MΩ、Rcを10kΩとした場合である。ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0009】

(c)温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体を適用する基準抵抗(変換抵抗)Rcでは、基準抵抗Rcの両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)と小さくすることから、良好な温度特性を維持しつつ消費電流の低減が図れる。

【発明を実施するための最良の形態】

【0010】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【実施例1】

【0011】

図1は本発明の実施例1である基準電流源回路を示す回路図である。基準電圧源回路1は、図1に示すように、2つの差動電圧源として第1の帰還形定電圧回路10及び第2の帰還形定電圧回路20を有している。第1の帰還形定電圧回路10は第1のオペアンプ(OP1)11と、この第1のオペアンプ11の出力端子に接続される第1の電圧源トランジスタ(Tr1)12からなっている。第1の電圧源トランジスタ12は、例えば、PMOSからなり、制御端子(ゲート電極)が第1のオペアンプ11の出力端子に接続されている。

【0012】

第2の帰還形定電圧回路20は第2のオペアンプ(OP2)21と、この第2のオペアンプ21の出力端子に接続される第2の電圧源トランジスタ(Tr2)22からなっている。第2の電圧源トランジスタ22は、例えば、NMOSからなり、制御端子(ゲート電極)が第2のオペアンプ21の出力端子に接続されている。

【0013】

第1の電圧源トランジスタ12の第1の端子(ドレイン電極)と、第1基準電圧(電源)が供給される第1基準電圧端子(電源端子)2との間には、基準電流(Iref)を出力するカレントミラー回路40が接続されている。カレントミラー回路40は、制御端子(ゲート電極)同士が接続された同一の特性を有するPMOS41,42を有する。PMOS41の制御端子は第1の電圧源トランジスタ12の第1の端子に接続されている。また、両方のPMOS41,42の第1の端子(ドレイン電極)は第1基準電圧端子2に接続されている。これによりカレントミラー回路40が構成され、PMOS42の第2の端子(ソース電極)から基準電流(Iref)が出力される。このカレントミラー回路40は基準電流(Iref)を負荷に吐出する吐出形である。

【0014】

一方、第1の電圧源トランジスタ12の第2の端子(ソース電極)と、第2の電圧源トランジスタ22の第1の端子(ドレイン電極)間には基準抵抗(変換抵抗)50が直列に接続されている。基準抵抗(Rc)50と第1の電圧源トランジスタ12との交点部分(ノード)aでの電圧はVaとなり、基準抵抗(Rc)50と第2の電圧源トランジスタ22とのノードbでの電圧はVbとなる。

【0015】

また、第1の電圧源トランジスタ12の第1の端子と、第2基準電圧(接地電位、グランド)が供給される第2基準電圧端子(グランド端子)3との間には2個の抵抗Ra,抵抗Rbが直列に接続されている。そして、第1の電圧源トランジスタ12の第1の端子と、第1のオペアンプ11の非反転入力端子(+)が接続されている。また、抵抗Raと抵抗Rbの抵抗分圧による電圧が第2のオペアンプ21の反転入力端子(−)に印加されるようになっている。即ち、抵抗Raと前記抵抗Rbとの間のノードcと、第2のオペアンプ21の反転入力端子(−)が接続されている。ノードcの電圧をV2とする。また、ノードaから第1のオペアンプ11及び抵抗Raに向かって流れる電流をI1とし、ノードaから基準抵抗(Rc)50に向かって流れる電流をI2とする。第1のオペアンプ11の反転入力端子(−)は基準電圧(Vref)が印加されるバイアス電圧入力端子4に接続されている。これにより、第1の帰還形定電圧回路10は第1の電圧源トランジスタ12のバイアス回路として第1のオペアンプ11の負帰還回路を用いる構造となる。基準電圧(Vref)としてV1が供給される。カレントミラー回路40のPMOS42の第2の端子からIref値を有する基準電流(Iref)が出力される。

【0016】

さらに、第2の帰還形定電圧回路20の第2の電圧源トランジスタ22の第2の端子(ソース電極)は第2基準電位端子3に接続されている。また、ノードbと第2のオペアンプ21の非反転入力端子(+)が接続されている。これにより、第2の帰還形定電圧回路20は第2の電圧源トランジスタ22のバイアス回路として第2のオペアンプ21の正帰還回路を用いる構造となる。

【0017】

つぎに、回路動作における電流及び電圧の関係について説明する。

第1の帰還形定電圧回路10でVaを作り、第2の帰還形定電圧回路20でVbを作り、基準抵抗(Rc)50に対してVa−Vbを印加する。

【0018】

オペアンプの直流電流(DC)のオフセットを0とした場合

Va=V1、Vb=V2、Iref=I1+I2となる。

【0019】

従って、I1は次式で与えられる。

【数1】

【0020】

また、V2は次式で与えられる。

【数2】

【0021】

また、I2は次式で与えられる。

【数3】

【0022】

ここで、一例について説明する。

V1=1.25V、Ra=100kΩ、Rb=4MΩ、Rc=10kΩとした場合、Va=1.25Vとなる。

【0023】

従って、

【数4】

となる。

【0024】

また、

V2=305n×4M≒1.22となる。

【0025】

従って、

【数5】

となる。

【0026】

また、Iref=305nA+3μA≒3.3μAとなる。

【0027】

基準電流源回路1では基準抵抗(Rc)50が10kΩで、基準電流(Iref)が3.3μAを実現できるが、1.25VをそのままV−I変換した場合、

【数6】

になり、抵抗値(抵抗体)、即ち、基準抵抗(Rc)50を約1/38に低減することができる。なお、ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0028】

実施例1によれば以下の効果を有する。

(1)2つの差動電圧源(第1及び第2の帰還形定電圧回路)を用いることから、基準電圧(Vref)が変動しても2つの差動電圧源から出力される電圧の電圧差は不変である。この結果、Ra,Rbに流れる電流がRcに流れる電流に比較して10分の1の場合、基準電流(Iref)の変動も10分の1となり、高精度に基準電流(Iref)をアナログ回路に供給することができる。

【0029】

(2)また、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、単位面積あたりの抵抗率が小さい抵抗体のみを使用する半導体集積回路よりレイアウト面積を低減できる。2つの差動電圧源(第1及び第2の帰還形定電圧回路)から出力される電圧の電圧差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)とすることにより、基準電流源を構成する抵抗体の面積の縮小が可能になる。例えば、基準抵抗(変換抵抗)Rcに対して1.25Vを印加する場合に比較して、基準抵抗Rcの両端間の電位差を0.03Vとした場合、基準抵抗Rcの面積を約1/38に低減できる。この低減値は、バイアス電圧入力端子の基準電圧(Vref)のVref値(V1)を1.25Vとし、Raを100kΩ、Rbを4MΩ、Rcを10kΩとした場合である。なお、ここで、Rcは温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体、RaとRbは、単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い特性を有する抵抗体である。

【0030】

(3)温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体を適用する基準抵抗(変換抵抗)Rcでは、基準抵抗Rcの両端間の電位差をバイアス電圧以下(実用的に発生させることができる電圧差、例として1μV〜1V)と小さくすることから、良好な温度特性を維持しつつ消費電流の低減が図れる。

【0031】

(4)基準電流源回路1では、第1の帰還形定電圧回路10の第1の電圧源トランジスタ12をPMOSで形成していることからNMOSで構成する場合に比較して、オペアンプが印加できるゲート電極対ソース電極間電位を大きくできる。よってトランジスタサイズ低減と動作可能電圧範囲を拡大できる効果を有する。また、第2の帰還形定電圧回路20の第2の電圧源トランジスタ22をNMOSで形成していることからPMOSで構成する場合に比較して、オペアンプが印加できるゲート電極対ソース電極間電位を大きくできる。よってトランジスタサイズ低減と動作可能電圧範囲を拡大できる効果を有する。

【実施例2】

【0032】

図2は本発明の実施例2である基準電流源回路を示す回路図である。

実施例2の基準電流源回路1は、実施例1の基準電流源回路1において、基準電流(Iref)を出力するカレントミラー回路を第1の電圧源トランジスタ12側に設けず、第2の電圧源トランジスタ22側に設ける構成になっている。他の部分は実施例1の基準電流源回路1と同じである。

【0033】

実施例2の基準電流源回路1では、第1の帰還形定電圧回路10の第1の電圧源トランジスタ12の第1の端子(ドレイン電極)は直接第1基準電位端子2に接続されている。そして、第2の帰還形定電圧回路20の第1の電圧源トランジスタ12の第2の端子(ソース電極)と、グランドとなる第2基準電位端子3との間にカレントミラー回路60を接続した構造になっている。

【0034】

カレントミラー回路60は、制御端子(ゲート電極)同士が接続された同一の特性を有するNMOS61,62を有する。NMOS61の制御端子は第2の電圧源トランジスタ22の第2の端子(ソース電極)に接続されている。また、両方のNMOS61,62の第2の端子(ソース電極)は第2基準電位端子3に接続されている。これによりカレントミラー回路60が構成され、NMOS62の第1の端子(ドレイン電極)から基準電流(Iref)を吸い込むようになっている。このカレントミラー回路60は基準電流(Iref)を負荷から吸い込む吸込形である。

【0035】

実施例2によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができる。即ち、実施例2の基準電流源回路1は、基準電流(Iref)出力をNMOSにしたことから、基準電流(Iref)からI1を除外できるため、V1の影響を受けない。また、実施例2の基準電流源回路1においても実施例1の基準電流源回路1と同様に温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【実施例3】

【0036】

図3は本発明の実施例3である基準電流源回路を示す回路図である。

実施例3の基準電流源回路1は、実施例1において、抵抗Ra,抵抗Rbは第1の電圧源トランジスタ12の第2の端子と第2基準電位端子3との間に設けることなく、バイアス電圧入力端子4と第2基準電位端子3との間に抵抗Ra,抵抗Rbと直列に接続した構成になっている。そして、抵抗Ra,抵抗Rbの抵抗分圧電圧を第2の帰還形定電圧回路20の反転入力端子(−)に印加する構造になっている。換言するならば、抵抗Raと抵抗Rbのノードcと第2のオペアンプ21の反転入力端子(−)を接続したものである。

【0037】

実施例3では、第1の電圧源トランジスタ12の第1の端子(ドレイン電極)と第1基準電位端子2との間に、図1で示す吐出形のカレントミラー回路40を接続し、第2の電圧源トランジスタ22の第2の端子(ソース電極)と第2基準電位端子3との間に、図2で示す吸込形のカレントミラー回路60を接続してカレントミラー回路構成の出力構造としている。

【0038】

実施例3の基準電流源回路1は、抵抗RaにV1を入れるタイプであることから、基準電流(Iref)のV1依存がなくなり、より高精度に基準電流(Iref)を出力することができる。

【0039】

実施例3によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができるとともに、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【0040】

なお、実施例3の基準電流源回路1を半導体チップにモノリシックに形成した段階では、第1のオペアンプ11と第2のオペアンプ21のDCオフセット次第ではVbがVaより高くなり、回路動作しない場合がある。このような場合、基準抵抗(Rc)50の抵抗値を調整できる構造、例えば、フユーズトリミングできる構造にしておき、回路動作しない場合Va及びVbが適正になるようにフユーズトリミングすることによって基準電流源回路1を正しく動作させることができる。

【実施例4】

【0041】

図4は本発明の実施例4である基準電流源回路を示す回路図である。

実施例4の基準電流源回路1は、実施例1の基準電流源回路1において、基準電圧(Vref)をバイアス電圧入力端子4に供給する構成ではなく、電源を抵抗分圧して基準電圧(Vref)を生成する回路である。即ち、図4に示すように、電源が供給される第1基準電位端子2とグランドとなる第2基準電位端子3との間に、抵抗Rd,抵抗Ra,抵抗Rbを直列に接続し、抵抗Rdと抵抗Raとの間のノードdと第1のオペアンプ11の反転入力端子(−)を接続する構造になっている。ノードdの電圧が基準電圧(Vref)となる。また、抵抗Raと抵抗Rbの間のノードcは、実施例3と同様に第2のオペアンプ21の反転入力端子(−)に接続されている。

【0042】

実施例4の基準電流源回路1は、バイアス電圧入力端子4を設けなくともよい利点がある。実施例4によれば、実施例1と同様に基準電圧の変動によっても基準電流が変動し難い基準電流源回路を提供することができるとともに、温度特性が良好であるが単位面積あたりの抵抗率が小さい抵抗体と単位面積あたりの抵抗率が前記抵抗体より大きいが温度特性が前記抵抗体より悪い2種類の抵抗体を選択的に回路に用いることで良好な温度特性を維持しつつ、消費電流の低減及び回路面積の低減が達成できる。

【0043】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。なお、実施例1の基準電流源回路1における基準電流(Iref)を出力する出力回路を、実施例3のように吐出形のカレントミラー回路40と、吸込形のカレントミラー回路60で構成してもよいことは勿論である。

【図面の簡単な説明】

【0044】

【図1】本発明の実施例1である基準電流源回路を示す回路図である。

【図2】本発明の実施例2である基準電流源回路を示す回路図である。

【図3】本発明の実施例3である基準電流源回路を示す回路図である。

【図4】本発明の実施例4である基準電流源回路を示す回路図である。

【符号の説明】

【0045】

1…基準電流源回路、2…第1基準電位端子、3…第2基準電位端子、4…バイアス電圧入力端子、10…第1の帰還形定電圧回路、11…第1のオペアンプ、12…第1の電圧源トランジスタ、20…第2の帰還形定電圧回路、21…第2のオペアンプ、22…第2の電圧源トランジスタ、40…カレントミラー回路、41,42…PMOS、50…基準抵抗(変換抵抗)、60…カレントミラー回路、61,62…NMOS。

【特許請求の範囲】

【請求項1】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第1の電圧源トランジスタの前記第1の端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【請求項2】

前記基準抵抗の両端間の電位差をバイアス電圧以下とすることを特徴とする請求項1に記載の基準電流源回路。

【請求項3】

前記第1の電圧源トランジスタの前記第1の端子と前記第1基準電圧端子との間には基準電流を吐出するカレントミラー回路が接続され、

前記第2の電圧源トランジスタの前記第2の端子と前記第2基準電圧端子との間には基準電流を吸い込むカレントミラー回路が接続されていることを特徴とする請求項1に記載の基準電流源回路。

【請求項4】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記バイアス電圧入力端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【請求項5】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1基準電圧端子と前記第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、

前記抵抗Raと前記抵抗Rbとの間のノードは前記第1のオペアンプの反転入力端子に接続されて基準電圧を供給するように構成され、

前記抵抗Rbと前記抵抗Rcとの間のノードは前記第2のオペアンプの反転入力端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【請求項1】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第1の電圧源トランジスタの前記第1の端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【請求項2】

前記基準抵抗の両端間の電位差をバイアス電圧以下とすることを特徴とする請求項1に記載の基準電流源回路。

【請求項3】

前記第1の電圧源トランジスタの前記第1の端子と前記第1基準電圧端子との間には基準電流を吐出するカレントミラー回路が接続され、

前記第2の電圧源トランジスタの前記第2の端子と前記第2基準電圧端子との間には基準電流を吸い込むカレントミラー回路が接続されていることを特徴とする請求項1に記載の基準電流源回路。

【請求項4】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

基準電圧が印加されるバイアス電圧入力端子と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記バイアス電圧入力端子と前記第2基準電圧端子との間には直列に2個の抵抗Ra,Rbが接続され、

前記第1のオペアンプの反転入力端子は前記バイアス電圧入力端子に接続され、

前記第2のオペアンプの反転入力端子は前記抵抗Raと前記抵抗Rbとの間のノードに接続され、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【請求項5】

第1の電圧源トランジスタのバイアス回路として第1のオペアンプの負帰還回路を用いている第1の帰還形定電圧回路と、

第2の電圧源トランジスタのバイアス回路として第2のオペアンプの正帰還回路を用いている第2の帰還形定電圧回路と、

基準抵抗と、

第1基準電圧が供給される第1基準電圧端子と、

第2基準電圧が供給される第2基準電圧端子とを有し、

前記第1基準電圧端子と前記第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、

前記抵抗Raと前記抵抗Rbとの間のノードは前記第1のオペアンプの反転入力端子に接続されて基準電圧を供給するように構成され、

前記抵抗Rbと前記抵抗Rcとの間のノードは前記第2のオペアンプの反転入力端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第2の端子と前記第2の電圧源トランジスタの前記第1の端子間には前記基準抵抗が直列に接続され、

前記第2の電圧源トランジスタの前記第2の端子は前記第2基準電圧端子に接続され、

前記第1の電圧源トランジスタの前記第1の端子または/および前記第2の電圧源トランジスタの前記第2の端子には基準電流を出力するカレントミラー回路が接続されていることを特徴とする基準電流源回路。

【図1】

【図2】

【図3】

【図4】

【図2】

【図3】

【図4】

【公開番号】特開2007−219901(P2007−219901A)

【公開日】平成19年8月30日(2007.8.30)

【国際特許分類】

【出願番号】特願2006−40529(P2006−40529)

【出願日】平成18年2月17日(2006.2.17)

【出願人】(000100997)株式会社アキタ電子システムズ (41)

【Fターム(参考)】

【公開日】平成19年8月30日(2007.8.30)

【国際特許分類】

【出願日】平成18年2月17日(2006.2.17)

【出願人】(000100997)株式会社アキタ電子システムズ (41)

【Fターム(参考)】

[ Back to top ]