多層プリント配線板

【課題】 インダクタを有しつつも反りを抑制することを可能とする多層プリント配線板を提供する。

【解決手段】 コア基材30の内部には、第1導体パターンと第1ビア導体とによりインダクタL1、L2が形成されている。そして、コア基板30を構成する第1絶縁層30M,30A,30B,30C,30D,30E,30Fは無機繊維補強材を含んでいる。すなわち、インダクタL1、L2が形成される層には、剛性を高めるための無機繊維補強材が設けられているため、無機繊維補強材によって絶縁層の熱収縮が抑制されやすくなる。

【解決手段】 コア基材30の内部には、第1導体パターンと第1ビア導体とによりインダクタL1、L2が形成されている。そして、コア基板30を構成する第1絶縁層30M,30A,30B,30C,30D,30E,30Fは無機繊維補強材を含んでいる。すなわち、インダクタL1、L2が形成される層には、剛性を高めるための無機繊維補強材が設けられているため、無機繊維補強材によって絶縁層の熱収縮が抑制されやすくなる。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、絶縁層と該絶縁層上の導体パターンと該絶縁層の内部に形成され導体パターン同士を接続するビア導体とを有するビルドアップ層がコア基板上に設けられている多層プリント配線板に関するものである。

【背景技術】

【0002】

特許文献1では、異なる層に形成された導体パターンを電気的に接続することで、配線板にインダクタを形成するものである。この技術を用いることで、インピーダンスの上昇を抑制することが可能となる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−16504号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示されているようなインダクタにおいては、得られるインダクタンスに影響を及ぼすという理由から、渦巻き状の導体パターンの内部を含めた近傍には導体を配置することはできない。このため、インダクタが形成される層においては、導体に対する樹脂の割合が必然的に大きくなる。その結果、例えば信頼性試験等による熱履歴が配線板に加わった際には、樹脂の熱収縮の影響が大きくなり、配線板の反りを引き起こす可能性がある。

【0005】

本発明は、上述した課題を解決するためになされたものであり、その目的とするところは、インダクタを有しつつも反りを抑制することを可能とする多層プリント配線板を提供することにある。

【課題を解決するための手段】

【0006】

請求項1に記載の発明は、複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材と、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層と、

を備える多層プリント配線板であって、

前記複数の第1絶縁層は無機繊維補強材を含み、

前記コア基材は、前記第1導体パターンと前記第1ビア導体とにより形成されるインダクタを有していることを技術的特徴とする。

【発明の効果】

【0007】

請求項1の多層プリント配線板では、コア基材が、複数の第1絶縁層と第1絶縁層上の第1導体パターンと第1絶縁層の内部に形成され第1導体パターン同士を接続する第1ビア導体とを有する。さらに、コア基材の内部には、第1導体パターンと第1ビア導体とによりインダクタが形成されている。このインダクタは、損失の少ない電圧を半導体素子に供給する目的で、コア基材の内部に設けられる。そして、各第1絶縁層は無機繊維補強材(例えば、ガラスクロス、ガラス不織布、アラミドクロス、アラミド不織布等)を含んでいる。

すなわち、インダクタが形成される層には、剛性を高めるための無機繊維補強材が設けられている。このため、無機繊維補強材によって絶縁層の熱収縮が抑制されやすくなる。その結果、例えば製造過程や信頼性試験において配線板に熱履歴が加わった場合でも、配線板の反りが抑制されると考えられる。ひいては、バンプの高さが均一になり、半導体素子の実装性が向上する。

【図面の簡単な説明】

【0008】

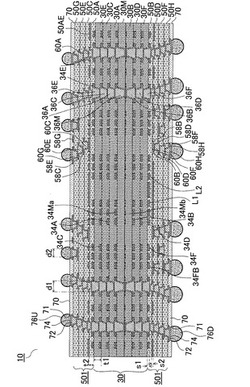

【図1】本発明の第1実施形態に係る多層プリント配線板の断面図である。

【図2】第1実施形態に係るインダクタンスの導体パターンの構成を示す図である。

【図3】ビルドアップ層における第2ビア導体の配置を示す模式図である。

【図4】ビルドアップ層における第2ビア導体の配置を示す模式図である。

【図5】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図6】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図7】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図8】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図9】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図10】第2実施形態の多層プリント配線板の断面図である。

【発明を実施するための形態】

【0009】

[第1実施形態]

図1は第1実施形態の多層プリント配線板の断面図である。

多層プリント配線板10は、コア基材30を有している。コア基材30は、複数の第1絶縁層30M,30A,30B,30C,30D,30E,30Fと、第1絶縁層上の第1導体パターン34Ma,34Mb,34A,34B,34C,34D,34E,34Fと、第1絶縁層の内部に形成され第1導体パターン同士を接続する第1ビア導体36M,36A,36B,36C,36D,36E,36Fとを有する。

コア基材30を形成する第1絶縁層は無機繊維補強材を含んでいる。この無機繊維補強材としては特に限定されないが、例えばガラスクロス、ガラス不織布、アラミドクロス、アラミド不織布等が挙げられる。

また、本実施形態ではコア基材30を形成する第1導体パターンは8層であるが、後述するインダクタにおいて所望のインダクタンスを得られるのであれば、その層数は特に限定されない。

【0010】

コア基材30を構成する第1絶縁層のうち、厚み方向の中央に位置する第1絶縁層30Mの表面には第1導体パターン34Maが形成され、その反対側の第1絶縁層30Mの裏面には第1導体パターン34Mbが形成されている。第1絶縁層30Mの内部には第1ビア導体36Mが形成され、この第1ビア導体36Mにより第1導体パターン34Maと第1導体パターン34Mbとが接続されている。

【0011】

第1絶縁層30Mの表面上には、第1絶縁層30A,30C,30Eが順次積層されている。第1絶縁層30A,30C,30E上には、それぞれ第1導体パターン34A,34C,34Eが形成されている。そして、第1導体パターン34Aと第1導体パターン34Maとが第1ビア導体36Aにより接続され、第1導体パターン34Aと第1導体パターン34Cとが第1ビア導体36Cにより接続され、第1導体パターン34Cと第1導体パターン34Eとが第1ビア導体36Eにより接続されている。

【0012】

一方、第1絶縁層30Mの裏面上には、第1絶縁層30B,30D,30Fが順次積層されている。第1絶縁層30B,30D,30F上には、それぞれ第1導体パターン34B,34D,34Fが形成されている。そして、第1導体パターン34Bと第1導体パターン34Mbとが第1ビア導体36Bにより接続され、第1導体パターン34Bと第1導体パターン34Dとが第1ビア導体36Dにより接続され、第1導体パターン34Dと第1導体パターン34Fとが第1ビア導体36Fにより接続されている。

【0013】

コア基材30は、半導体素子(図示せず)が実装される側の第1面と、第1面とは反対側の第2面とを有している。コア基材30の第1面上及び第2面上には、それぞれ第2絶縁層と第2絶縁層上の第2導体パターンと第2絶縁層の内部に形成され第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層501,502が設けられている。

ビルドアップ層501,502を形成する第2絶縁層は無機繊維補強材を含んでいない。

コア基材30の第1面上のビルドアップ層501を形成する第2絶縁層50A上には第2導体パターン58Aが設けられている。第2導体パターン58Aと第1導体パターン34Eとは第2ビア導体60Aにより接続されている。第2絶縁層50A及び第2導体パターン58A上には、第2絶縁層50C,50E,50Gが順次積層されている。第2絶縁層50C,50E,50G上には、それぞれ第2導体パターン58C,58E,58Gが形成されている。そして、上下の第2導体パターン同士は、各第2絶縁層の内部に設けられている第2ビア導体60C,60E,60Gによりそれぞれ接続されている。

【0014】

一方、コア基材30の第2面上のビルドアップ層502を形成する第2絶縁層50B上には第2導体パターン58Bが設けられている。第2導体パターン58Bと第1導体パターン34Fとは第2ビア導体60Bにより接続されている。第2絶縁層50B及び第2導体パターン58B上には、第2絶縁層50D,50F,50Hが順次積層されている。第2絶縁層50D,50F,50H上には、それぞれ第2導体パターン58D,58F,58Hが形成されている。そして、上下の第2導体パターン同士は、各第2絶縁層の内部に設けられている第2ビア導体60D,60F,60Hによりそれぞれ接続されている。

【0015】

上面側の最外層の層間樹脂絶縁層50G上には開口71を有するソルダーレジスト層70が設けられている。開口71の内部には半導体素子を接続するための半田バンプ76Uが形成されている。下面側の最外層の層間樹脂絶縁層50H上には開口71を有するソルダーレジスト層70が設けられている。この開口71の内部には、外部基板であるマザーボード等との接続用の半田バンプ76Dが形成されている。

【0016】

コア基材30内にはインダクタが形成されている。

図2に示すように、本実施形態のインダクタは、各第1絶縁層の表面上に形成されている渦巻き状の第1導体パターン群と、上下に位置する渦巻き状の第1導体パターン群とを接続する第1ビア導体とからなる。なお、図2においては、インダクタを形成する第1導体パターン群のうち、下側最外層の第1導体パターン群34F及びそれらの上層の第1導体パターン群34Dと、上側最外層の第1導体パターン34E及びそれらの下層の第1導体パターン群34Cとが開示されている。これら以外の第1導体パターン群は省略されている。

本実施形態では、少なくとも隣接する一対のインダクタL1,L2を有する。これら一対のインダクタL1,L2は電気的に接続されている。これにより、半導体素子の内部のスイッチング部で変換された電圧がインダクタL1,L2及びキャパシタ(図示せず)を介して平滑化されるようになる。

なお、インダクタL1,L2を形成する導体パターンのデザインは特に限定されることはない。インダクタの個数も特に限定されない。

【0017】

図1に示すように、コア基板30を形成する各第1絶縁層30M,30A,30B,30C,30D,30E,30F上には、それぞれプレーン層が設けられている。これらのプレーン層は、電源用又はグランド用として機能する。各プレーン層は、インダクタL1,L2を形成する第1導体パターンが形成される箇所に凹部を有している。これにより、平面方向においてインダクタL1,L2とプレーン層とが離間されており、所望のインダクタンスが得られやすくなる。

【0018】

インダクタL1,L2の周囲に位置する第1ビア導体は、コア基材30の厚み方向において直線状に積層されている。なお、「直線状に積層されている」とは、厚み方向に隣接する上下の第1ビア導体の少なくとも一部が平面方向において重なり合っている状態を意味する。仮に、このような第1ビア導体が電源系として機能する場合、電源ラインが短縮されることになり、半導体素子に供給される電圧の損失が極力抑制される。

【0019】

本実施形態では、インダクタL1,L2は、半導体素子が実装される領域(バンプ76Uが形成されている領域)の直下に設けられる。この場合、損失の無い電圧を半導体素子へ供給することが容易となる。

【0020】

本実施形態の多層プリント配線板では、インダクタを形成する導体パターン34E、34C、34A、34Ma、34Mb、34B、34D、34Fのうち、上下に隣接する導体パターンの間に位置する第1絶縁層30M,30A,30B,30C,30D,30E,30Fには、無機繊維補強材が含有されている。このため、剛性の高い無機繊維補強材によって第1絶縁層の熱収縮が抑制されやすくなる。その結果、例えば製造過程や信頼性試験において配線板に熱履歴が加わった場合でも、配線板の反りが抑制されると考えられる。

【0021】

本実施形態の多層プリント配線板では、コア基材30内にインダクタL1,L2が形成されている。仮に、コア基材30の第1面上及び第2面上の一方のビルドアップ層のみにインダクタL1,L2を形成した場合、上層のビルドアップ層501における導体の体積と下層のビルドアップ層502における導体の体積との間に差が大きくなる。この場合、配線板に熱履歴が加わった際の熱収縮量に差が生じ、反りが発生しやすくなる。しかしながら、本実施形態の構成では、コア基材30内にインダクタL1,L2を形成するため、上層と下層のビルドアップ層の対称性が保ちやすく、反りが生じ難くなると考えられる。

【0022】

本実施形態の多層プリント配線板では、複数の第1絶縁層30E、30C、30A、30M、30B、30D、30Fの内部にそれぞれ設けられたビア導体36E、36C、36A、36M、36B、36D、36Fにより、コア基材30の表裏の電気的な接続を確保する。このため、1つのビア導体の開口に対する深さ(アスペクト比)は、同じ厚みのコア基材を貫通する貫通孔と比較して小さくなる。このため、ビア導体の開口が小径であっても、めっきを充填する際にめっき液の液流れが良好なものとなる。その結果、ボイドが入り難くなって個々のビア導体の信頼性が高まり、コア基材の表裏面での接続信頼性が向上する。インダクタを形成するビア導体へのボイドの発生を抑制することで、インダクタの性能(Q値)を高めることが可能となる。

【0023】

コア基材30の第1ビア導体の径d1はビルドアップ層501,502の第2ビア導体の径d2よりも大きい。例えば、コア基材30の第1ビア導体の径d1は80μm、ビルドアップ層の第2ビア導体の径d2は50μmである。すなわち、インダクタとして機能する、コア基材30内の第1ビア導体の径を大きくすることで、インダクタの性能(Q値)をさらに高めることが可能となる。

【0024】

本実施形態の多層プリント配線板では、インダクタL1,L2を形成する第1導体パターンの厚みs1が、ビルドアップ層501,502の第2導体パターン58Bの厚みs2よりも大きい。例えば、コア基材30の第1導体パターンの厚みs1が20〜40μm、ビルドアップ層の第2導体パターンの厚みs2が10〜18μmである。インダクタL1,L2を形成する第1導体パターンの厚みを厚くすることで、インダクタの性能が向上する。さらに、コア基材30に剛性を持たせることができる。

一方、ビルドアップ層501,502の第2導体パターンの厚みを相対的に薄くすることで、ビルドアップ層501,502側での導体パターンのファインピッチ化を実現でき、配線板全体の厚みを抑制しながら、多層化が可能になる。

【0025】

本実施形態の多層プリント配線板では、コア基材30を形成する第1絶縁層30E、30C、30A、30M、30B、30D、30Fの厚みt1が、ビルドアップ層501,502を形成する第2絶縁層50G、50E、50C、50A、50B、50D、50F、50Hの厚みt2よりも大きい。例えば、第1絶縁層の厚みが約60μmで、第2絶縁層の厚みが約40μmである。コア基材30を形成する複数の第1絶縁層の厚みを厚くすることで、コア基材30の剛性を確保することが可能となる。さらに、インダクタL1,L2を形成する第1ビア導体の深さが相対的に大きくなり、インダクタンスを確保しやすくなる。

一方、第2絶縁層の厚みを相対的に薄くすることで、ビルドアップ層側での導体パターンのファインピッチ化を実現でき、全体の厚みを抑制しつつ多層化が可能になる。

【0026】

本実施形態の多層プリント配線板では、コア基材30の第1ビア導体のうち、インダクタL1,L2を形成しない第1ビア導体36E、36C、36A、36M、36B、36D、36Fは、厚み方向において直線状に積層されている。このため、電源ライン又は信号ラインを最短にすることが可能となる。また、第1ビア導体を積層することで、コア基材30の剛性を確保することができる。

【0027】

また、本実施形態においては、インダクタL1,L2を形成する最上層の第1導体パターン34Eと、ビルドアップ層501の最上層に位置する第2導体パターン58Gとを接続する複数の第2ビア導体は直線状に積層されている。なお、「直線状に積層されている」とは、厚み方向に隣接する上下の第2ビア導体の少なくとも一部が平面方向において重なり合っている状態を意味する。ここで、ビルドアップ層501を形成する第2絶縁層50A上には電源用(グランド)プレーン層50AEが設けられている。

仮に、図3(A)に示すように、上下の第2ビア導体60A,60Cが平面方向にずれている場合、プレーン層50AEと第2導体パターン58A(ビアランド)とを絶縁するための凹部50Zの体積が増大し、磁界が漏れやすくなる(図3(B)参照)。このため、インダクタンスが小さくなる可能性がある。一方、図4(A)に示すように、ビルドアップ層における複数の第2ビア導体(例えば60A,60C)が直線状に積層されている場合、プレーン層50AEと第2導体パターン58A(ビアランド)とを絶縁するための凹部50Zの体積は相対的に小さくなる。その結果、磁界の漏れが抑制され、所望のインダクタンスが得られやすくなる。

【0028】

[第1実施形態の多層プリント配線板の製造方法]

図5〜図9は第1実施形態の多層プリント配線板の製造方法を示す。

ガラスクロス芯材にエポキシ系樹脂を含浸させたプリプレグからなる絶縁層30Mの両面に銅箔32、32が積層されてなる両面銅張り積層板(CCL−HL832NSLC)を出発材料とする(図5(A))。

【0029】

レーザにより、片面側の銅箔32及び絶縁層30Mを貫通するビア用開口31が形成される(図5(B))。次いで、無電解めっき膜33が形成される(図5(C))。電解めっき処理が行われ、電解めっき膜35が絶縁層表面、及び、開口31内に形成される(図5(D))。そして、電解めっき膜上に所定パターンのエッチングレジスト37が形成され(図5(E))、エッチングレジストが形成されていない部分の電解めっき膜35、無電解めっき膜33、銅箔32が除去される(図5(F))。エッチングレジストが除去され、無電解めっき膜33及び電解めっき膜35から成るビア導体36M、無電解めっき膜33、電解めっき膜35及び銅箔32から成る導体パターン34Ma,34Mbが形成される(図5(G))。

【0030】

絶縁層30Mの上面には、銅箔32aを有する絶縁層30Aが積層されるとともに、絶縁層30Mの下面には、銅箔32bを有する絶縁層30Bが積層される(図6(A))。銅箔32a、32bをエッチングすることでその厚みを薄くした後、レーザにより、絶縁層30A側にビア導体36Mに至るビア用開口31Aが形成するとともに、絶縁層30B側にビア導体36Mに至るビア用開口31Bを形成する(図6(B))。無電解めっき膜33a、33bが形成される(図6(C))。電解めっき処理が行われ、電解めっき膜35a、35bが絶縁層表面、及び、開口31A、31B内に形成される(図6(D))。電解めっき膜上に所定パターンのエッチングレジスト37a、37bが形成される(図6(E))。エッチングレジストが形成されていない部分の電解めっき膜35a、35b、無電解めっき膜33a、33b、銅箔32a、32bが除去された後、エッチングレジストが除去され、無電解めっき膜33a及び電解めっき膜35aから成るビア導体36Aと、無電解めっき膜33a、電解めっき膜35a及び銅箔32aから成る導体パターン34Aとが形成される。さらに、無電解めっき膜33b及び電解めっき膜35bから成るビア導体36Bと、無電解めっき膜33b、電解めっき膜35b及び銅箔32bから成る導体パターン34Bとが形成される(図6(F))。

【0031】

図6中に示した処理が繰り返され、ビア導体36C及び導体パターン34Cを備える絶縁層30Cと、ビア導体36D及び導体パターン34Dを備える絶縁層30Dとが積層される。更に、ビア導体36E及び導体パターン34Eを備える絶縁層30Eと、ビア導体36F及び導体パターン34Fを備える絶縁層30Fとが積層され、本実施形態のコア基材30が完成する(図7(A))。

【0032】

コア基板30の第1面上及び第2面上に、無機繊維補強材(ガラスクロス芯材など)を含まない層間絶縁層用樹脂フィルムが積層され、熱硬化により層間樹脂絶縁層50A、50Bが形成される(図7(B))。

【0033】

CO2ガスレーザにて層間樹脂絶縁層50Aの内部には、導体パターン34E、ビア導体36Eに至る開口51Aが設けられ、層間樹脂絶縁層50Bの内部には、導体パターン34F、ビア導体36Fに至る開口51Bが設けられる(図7(C))。クロム酸、過マンガン酸塩などの酸化剤等に浸漬させることによって、層間樹脂絶縁層50A、50Bの表面が粗化される(図示せず)。

【0034】

層間樹脂絶縁層50A、50Bの表層にパラジウムなどの触媒が付与されて、無電解めっき液に5〜60分間浸漬させることにより、0.1〜5μmの範囲で無電解めっき膜53a、53bが設けられる(図7(D))。

【0035】

上記処理を終えた積層体に、市販の感光性ドライフィルムが貼り付けられ、フォトマスクフィルムを載置して露光した後、炭酸ナトリウムで現像処理し、厚さ15μmのめっきレジスト54a、54bが設けられる(図8(A))。電解めっき処理により、厚さ15μmの電解めっき膜56a、56bが形成される(図8(B))。

【0036】

めっきレジストが5%NaOHで剥離除去された後、そのめっきレジスト下の無電解めっき膜53a、53bが硝酸および硫酸と過酸化水素の混合液を用いるエッチングにて溶解除去される。これにより、無電解めっき膜53a、53bと電解めっき膜56a、56bとからなる、厚さ約15μmの導体パターン58A、58Bとビア導体60A、60Bとが形成される(図8(C))。第二銅錯体と有機酸とを含有するエッチング液によって、導体パターン58A、58B及びビア導体60A、60B表面が粗化される(図示せず)。

【0037】

図7(B)〜図8(C)の処理が繰り返され、コア基材30の第1面上にビルドアップ層501が設けられ、第2面上にビルドアップ層502が設けられる(図8(D))。

【0038】

次に、市販のソルダーレジスト組成物が塗布され、これを露光・現像することで、開口部71を備えるソルダーレジスト層70が形成される(図9(A))。

【0039】

積層体が無電解ニッケルめっき液に浸漬され、開口部71内にニッケルめっき層72が形成される。さらに、その積層体が無電解金めっき液に浸漬され、ニッケルめっき層72上に、金めっき層74が形成される(図9(B))。ニッケル−金層以外にも、ニッケル−パラジウム−金層を形成してもよい。

【0040】

開口部71の内部に半田ボールが搭載され、リフローを行うことで、上面側に半田バンプ76Uが、裏面側に半田バンプ76Dが形成される。これにより、多層プリント配線板10が完成する(図9(C)及び図1)。

【0041】

[第2実施形態]

図10は、第2実施形態の多層プリント配線板の断面図を示す。

第2実施形態の多層プリント配線板では、コア基板30に設けられたインダクタL1,L2の直下のビルドアップ層502内にさらにインダクタL3,L4が形成されている。

このインダクタL3,L4は、導体パターン58B、導体パターン58D、導体パターン50F、ビア導体60B、ビア導体60D、ビア導体60F及びビア導体60Fにより形成されている。なお、このビルドアップ層502に設けられたインダクタL3,L4は、コア基材30内のインダクタL1,L2と同様のデザインであってもよく、異なるデザインであってもよい。

【0042】

これによれば、ビルドアップ層502にもインダクタが形成されることになるため、コア基材30内のインダクタンス分のみによらず、更なるインダクタンス成分を確保することが可能になる。また、コア基材30の表裏のビルドアップ層501,502における導体の体積の差を調整でき、配線板の反りを低減することが可能になると考えられる。

【符号の説明】

【0043】

10 多層プリント配線板

30 コア基材

30M,30A,30B,30C,30D,30E,30F 第1絶縁層

34Ma,34Mb,34A,34B,34C,34D,34E,34F 第1導体パターン

36M,36A,36B,36C,36D,36E,36F 第1ビア導体

50G、50E、50C、50A、50B、50D、50F、50H 第2絶縁層

58A,58B,58C,58D,58E,58F,58G,58H, 第2導体パターン

60A,60B,60C,60D,60E,60F,60G,60H, 第2ビア導体

【技術分野】

【0001】

本発明は、絶縁層と該絶縁層上の導体パターンと該絶縁層の内部に形成され導体パターン同士を接続するビア導体とを有するビルドアップ層がコア基板上に設けられている多層プリント配線板に関するものである。

【背景技術】

【0002】

特許文献1では、異なる層に形成された導体パターンを電気的に接続することで、配線板にインダクタを形成するものである。この技術を用いることで、インピーダンスの上昇を抑制することが可能となる。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】特開2009−16504号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

しかしながら、特許文献1に開示されているようなインダクタにおいては、得られるインダクタンスに影響を及ぼすという理由から、渦巻き状の導体パターンの内部を含めた近傍には導体を配置することはできない。このため、インダクタが形成される層においては、導体に対する樹脂の割合が必然的に大きくなる。その結果、例えば信頼性試験等による熱履歴が配線板に加わった際には、樹脂の熱収縮の影響が大きくなり、配線板の反りを引き起こす可能性がある。

【0005】

本発明は、上述した課題を解決するためになされたものであり、その目的とするところは、インダクタを有しつつも反りを抑制することを可能とする多層プリント配線板を提供することにある。

【課題を解決するための手段】

【0006】

請求項1に記載の発明は、複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材と、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層と、

を備える多層プリント配線板であって、

前記複数の第1絶縁層は無機繊維補強材を含み、

前記コア基材は、前記第1導体パターンと前記第1ビア導体とにより形成されるインダクタを有していることを技術的特徴とする。

【発明の効果】

【0007】

請求項1の多層プリント配線板では、コア基材が、複数の第1絶縁層と第1絶縁層上の第1導体パターンと第1絶縁層の内部に形成され第1導体パターン同士を接続する第1ビア導体とを有する。さらに、コア基材の内部には、第1導体パターンと第1ビア導体とによりインダクタが形成されている。このインダクタは、損失の少ない電圧を半導体素子に供給する目的で、コア基材の内部に設けられる。そして、各第1絶縁層は無機繊維補強材(例えば、ガラスクロス、ガラス不織布、アラミドクロス、アラミド不織布等)を含んでいる。

すなわち、インダクタが形成される層には、剛性を高めるための無機繊維補強材が設けられている。このため、無機繊維補強材によって絶縁層の熱収縮が抑制されやすくなる。その結果、例えば製造過程や信頼性試験において配線板に熱履歴が加わった場合でも、配線板の反りが抑制されると考えられる。ひいては、バンプの高さが均一になり、半導体素子の実装性が向上する。

【図面の簡単な説明】

【0008】

【図1】本発明の第1実施形態に係る多層プリント配線板の断面図である。

【図2】第1実施形態に係るインダクタンスの導体パターンの構成を示す図である。

【図3】ビルドアップ層における第2ビア導体の配置を示す模式図である。

【図4】ビルドアップ層における第2ビア導体の配置を示す模式図である。

【図5】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図6】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図7】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図8】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図9】第1実施形態の多層プリント配線板の製造方法を示す工程図である。

【図10】第2実施形態の多層プリント配線板の断面図である。

【発明を実施するための形態】

【0009】

[第1実施形態]

図1は第1実施形態の多層プリント配線板の断面図である。

多層プリント配線板10は、コア基材30を有している。コア基材30は、複数の第1絶縁層30M,30A,30B,30C,30D,30E,30Fと、第1絶縁層上の第1導体パターン34Ma,34Mb,34A,34B,34C,34D,34E,34Fと、第1絶縁層の内部に形成され第1導体パターン同士を接続する第1ビア導体36M,36A,36B,36C,36D,36E,36Fとを有する。

コア基材30を形成する第1絶縁層は無機繊維補強材を含んでいる。この無機繊維補強材としては特に限定されないが、例えばガラスクロス、ガラス不織布、アラミドクロス、アラミド不織布等が挙げられる。

また、本実施形態ではコア基材30を形成する第1導体パターンは8層であるが、後述するインダクタにおいて所望のインダクタンスを得られるのであれば、その層数は特に限定されない。

【0010】

コア基材30を構成する第1絶縁層のうち、厚み方向の中央に位置する第1絶縁層30Mの表面には第1導体パターン34Maが形成され、その反対側の第1絶縁層30Mの裏面には第1導体パターン34Mbが形成されている。第1絶縁層30Mの内部には第1ビア導体36Mが形成され、この第1ビア導体36Mにより第1導体パターン34Maと第1導体パターン34Mbとが接続されている。

【0011】

第1絶縁層30Mの表面上には、第1絶縁層30A,30C,30Eが順次積層されている。第1絶縁層30A,30C,30E上には、それぞれ第1導体パターン34A,34C,34Eが形成されている。そして、第1導体パターン34Aと第1導体パターン34Maとが第1ビア導体36Aにより接続され、第1導体パターン34Aと第1導体パターン34Cとが第1ビア導体36Cにより接続され、第1導体パターン34Cと第1導体パターン34Eとが第1ビア導体36Eにより接続されている。

【0012】

一方、第1絶縁層30Mの裏面上には、第1絶縁層30B,30D,30Fが順次積層されている。第1絶縁層30B,30D,30F上には、それぞれ第1導体パターン34B,34D,34Fが形成されている。そして、第1導体パターン34Bと第1導体パターン34Mbとが第1ビア導体36Bにより接続され、第1導体パターン34Bと第1導体パターン34Dとが第1ビア導体36Dにより接続され、第1導体パターン34Dと第1導体パターン34Fとが第1ビア導体36Fにより接続されている。

【0013】

コア基材30は、半導体素子(図示せず)が実装される側の第1面と、第1面とは反対側の第2面とを有している。コア基材30の第1面上及び第2面上には、それぞれ第2絶縁層と第2絶縁層上の第2導体パターンと第2絶縁層の内部に形成され第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層501,502が設けられている。

ビルドアップ層501,502を形成する第2絶縁層は無機繊維補強材を含んでいない。

コア基材30の第1面上のビルドアップ層501を形成する第2絶縁層50A上には第2導体パターン58Aが設けられている。第2導体パターン58Aと第1導体パターン34Eとは第2ビア導体60Aにより接続されている。第2絶縁層50A及び第2導体パターン58A上には、第2絶縁層50C,50E,50Gが順次積層されている。第2絶縁層50C,50E,50G上には、それぞれ第2導体パターン58C,58E,58Gが形成されている。そして、上下の第2導体パターン同士は、各第2絶縁層の内部に設けられている第2ビア導体60C,60E,60Gによりそれぞれ接続されている。

【0014】

一方、コア基材30の第2面上のビルドアップ層502を形成する第2絶縁層50B上には第2導体パターン58Bが設けられている。第2導体パターン58Bと第1導体パターン34Fとは第2ビア導体60Bにより接続されている。第2絶縁層50B及び第2導体パターン58B上には、第2絶縁層50D,50F,50Hが順次積層されている。第2絶縁層50D,50F,50H上には、それぞれ第2導体パターン58D,58F,58Hが形成されている。そして、上下の第2導体パターン同士は、各第2絶縁層の内部に設けられている第2ビア導体60D,60F,60Hによりそれぞれ接続されている。

【0015】

上面側の最外層の層間樹脂絶縁層50G上には開口71を有するソルダーレジスト層70が設けられている。開口71の内部には半導体素子を接続するための半田バンプ76Uが形成されている。下面側の最外層の層間樹脂絶縁層50H上には開口71を有するソルダーレジスト層70が設けられている。この開口71の内部には、外部基板であるマザーボード等との接続用の半田バンプ76Dが形成されている。

【0016】

コア基材30内にはインダクタが形成されている。

図2に示すように、本実施形態のインダクタは、各第1絶縁層の表面上に形成されている渦巻き状の第1導体パターン群と、上下に位置する渦巻き状の第1導体パターン群とを接続する第1ビア導体とからなる。なお、図2においては、インダクタを形成する第1導体パターン群のうち、下側最外層の第1導体パターン群34F及びそれらの上層の第1導体パターン群34Dと、上側最外層の第1導体パターン34E及びそれらの下層の第1導体パターン群34Cとが開示されている。これら以外の第1導体パターン群は省略されている。

本実施形態では、少なくとも隣接する一対のインダクタL1,L2を有する。これら一対のインダクタL1,L2は電気的に接続されている。これにより、半導体素子の内部のスイッチング部で変換された電圧がインダクタL1,L2及びキャパシタ(図示せず)を介して平滑化されるようになる。

なお、インダクタL1,L2を形成する導体パターンのデザインは特に限定されることはない。インダクタの個数も特に限定されない。

【0017】

図1に示すように、コア基板30を形成する各第1絶縁層30M,30A,30B,30C,30D,30E,30F上には、それぞれプレーン層が設けられている。これらのプレーン層は、電源用又はグランド用として機能する。各プレーン層は、インダクタL1,L2を形成する第1導体パターンが形成される箇所に凹部を有している。これにより、平面方向においてインダクタL1,L2とプレーン層とが離間されており、所望のインダクタンスが得られやすくなる。

【0018】

インダクタL1,L2の周囲に位置する第1ビア導体は、コア基材30の厚み方向において直線状に積層されている。なお、「直線状に積層されている」とは、厚み方向に隣接する上下の第1ビア導体の少なくとも一部が平面方向において重なり合っている状態を意味する。仮に、このような第1ビア導体が電源系として機能する場合、電源ラインが短縮されることになり、半導体素子に供給される電圧の損失が極力抑制される。

【0019】

本実施形態では、インダクタL1,L2は、半導体素子が実装される領域(バンプ76Uが形成されている領域)の直下に設けられる。この場合、損失の無い電圧を半導体素子へ供給することが容易となる。

【0020】

本実施形態の多層プリント配線板では、インダクタを形成する導体パターン34E、34C、34A、34Ma、34Mb、34B、34D、34Fのうち、上下に隣接する導体パターンの間に位置する第1絶縁層30M,30A,30B,30C,30D,30E,30Fには、無機繊維補強材が含有されている。このため、剛性の高い無機繊維補強材によって第1絶縁層の熱収縮が抑制されやすくなる。その結果、例えば製造過程や信頼性試験において配線板に熱履歴が加わった場合でも、配線板の反りが抑制されると考えられる。

【0021】

本実施形態の多層プリント配線板では、コア基材30内にインダクタL1,L2が形成されている。仮に、コア基材30の第1面上及び第2面上の一方のビルドアップ層のみにインダクタL1,L2を形成した場合、上層のビルドアップ層501における導体の体積と下層のビルドアップ層502における導体の体積との間に差が大きくなる。この場合、配線板に熱履歴が加わった際の熱収縮量に差が生じ、反りが発生しやすくなる。しかしながら、本実施形態の構成では、コア基材30内にインダクタL1,L2を形成するため、上層と下層のビルドアップ層の対称性が保ちやすく、反りが生じ難くなると考えられる。

【0022】

本実施形態の多層プリント配線板では、複数の第1絶縁層30E、30C、30A、30M、30B、30D、30Fの内部にそれぞれ設けられたビア導体36E、36C、36A、36M、36B、36D、36Fにより、コア基材30の表裏の電気的な接続を確保する。このため、1つのビア導体の開口に対する深さ(アスペクト比)は、同じ厚みのコア基材を貫通する貫通孔と比較して小さくなる。このため、ビア導体の開口が小径であっても、めっきを充填する際にめっき液の液流れが良好なものとなる。その結果、ボイドが入り難くなって個々のビア導体の信頼性が高まり、コア基材の表裏面での接続信頼性が向上する。インダクタを形成するビア導体へのボイドの発生を抑制することで、インダクタの性能(Q値)を高めることが可能となる。

【0023】

コア基材30の第1ビア導体の径d1はビルドアップ層501,502の第2ビア導体の径d2よりも大きい。例えば、コア基材30の第1ビア導体の径d1は80μm、ビルドアップ層の第2ビア導体の径d2は50μmである。すなわち、インダクタとして機能する、コア基材30内の第1ビア導体の径を大きくすることで、インダクタの性能(Q値)をさらに高めることが可能となる。

【0024】

本実施形態の多層プリント配線板では、インダクタL1,L2を形成する第1導体パターンの厚みs1が、ビルドアップ層501,502の第2導体パターン58Bの厚みs2よりも大きい。例えば、コア基材30の第1導体パターンの厚みs1が20〜40μm、ビルドアップ層の第2導体パターンの厚みs2が10〜18μmである。インダクタL1,L2を形成する第1導体パターンの厚みを厚くすることで、インダクタの性能が向上する。さらに、コア基材30に剛性を持たせることができる。

一方、ビルドアップ層501,502の第2導体パターンの厚みを相対的に薄くすることで、ビルドアップ層501,502側での導体パターンのファインピッチ化を実現でき、配線板全体の厚みを抑制しながら、多層化が可能になる。

【0025】

本実施形態の多層プリント配線板では、コア基材30を形成する第1絶縁層30E、30C、30A、30M、30B、30D、30Fの厚みt1が、ビルドアップ層501,502を形成する第2絶縁層50G、50E、50C、50A、50B、50D、50F、50Hの厚みt2よりも大きい。例えば、第1絶縁層の厚みが約60μmで、第2絶縁層の厚みが約40μmである。コア基材30を形成する複数の第1絶縁層の厚みを厚くすることで、コア基材30の剛性を確保することが可能となる。さらに、インダクタL1,L2を形成する第1ビア導体の深さが相対的に大きくなり、インダクタンスを確保しやすくなる。

一方、第2絶縁層の厚みを相対的に薄くすることで、ビルドアップ層側での導体パターンのファインピッチ化を実現でき、全体の厚みを抑制しつつ多層化が可能になる。

【0026】

本実施形態の多層プリント配線板では、コア基材30の第1ビア導体のうち、インダクタL1,L2を形成しない第1ビア導体36E、36C、36A、36M、36B、36D、36Fは、厚み方向において直線状に積層されている。このため、電源ライン又は信号ラインを最短にすることが可能となる。また、第1ビア導体を積層することで、コア基材30の剛性を確保することができる。

【0027】

また、本実施形態においては、インダクタL1,L2を形成する最上層の第1導体パターン34Eと、ビルドアップ層501の最上層に位置する第2導体パターン58Gとを接続する複数の第2ビア導体は直線状に積層されている。なお、「直線状に積層されている」とは、厚み方向に隣接する上下の第2ビア導体の少なくとも一部が平面方向において重なり合っている状態を意味する。ここで、ビルドアップ層501を形成する第2絶縁層50A上には電源用(グランド)プレーン層50AEが設けられている。

仮に、図3(A)に示すように、上下の第2ビア導体60A,60Cが平面方向にずれている場合、プレーン層50AEと第2導体パターン58A(ビアランド)とを絶縁するための凹部50Zの体積が増大し、磁界が漏れやすくなる(図3(B)参照)。このため、インダクタンスが小さくなる可能性がある。一方、図4(A)に示すように、ビルドアップ層における複数の第2ビア導体(例えば60A,60C)が直線状に積層されている場合、プレーン層50AEと第2導体パターン58A(ビアランド)とを絶縁するための凹部50Zの体積は相対的に小さくなる。その結果、磁界の漏れが抑制され、所望のインダクタンスが得られやすくなる。

【0028】

[第1実施形態の多層プリント配線板の製造方法]

図5〜図9は第1実施形態の多層プリント配線板の製造方法を示す。

ガラスクロス芯材にエポキシ系樹脂を含浸させたプリプレグからなる絶縁層30Mの両面に銅箔32、32が積層されてなる両面銅張り積層板(CCL−HL832NSLC)を出発材料とする(図5(A))。

【0029】

レーザにより、片面側の銅箔32及び絶縁層30Mを貫通するビア用開口31が形成される(図5(B))。次いで、無電解めっき膜33が形成される(図5(C))。電解めっき処理が行われ、電解めっき膜35が絶縁層表面、及び、開口31内に形成される(図5(D))。そして、電解めっき膜上に所定パターンのエッチングレジスト37が形成され(図5(E))、エッチングレジストが形成されていない部分の電解めっき膜35、無電解めっき膜33、銅箔32が除去される(図5(F))。エッチングレジストが除去され、無電解めっき膜33及び電解めっき膜35から成るビア導体36M、無電解めっき膜33、電解めっき膜35及び銅箔32から成る導体パターン34Ma,34Mbが形成される(図5(G))。

【0030】

絶縁層30Mの上面には、銅箔32aを有する絶縁層30Aが積層されるとともに、絶縁層30Mの下面には、銅箔32bを有する絶縁層30Bが積層される(図6(A))。銅箔32a、32bをエッチングすることでその厚みを薄くした後、レーザにより、絶縁層30A側にビア導体36Mに至るビア用開口31Aが形成するとともに、絶縁層30B側にビア導体36Mに至るビア用開口31Bを形成する(図6(B))。無電解めっき膜33a、33bが形成される(図6(C))。電解めっき処理が行われ、電解めっき膜35a、35bが絶縁層表面、及び、開口31A、31B内に形成される(図6(D))。電解めっき膜上に所定パターンのエッチングレジスト37a、37bが形成される(図6(E))。エッチングレジストが形成されていない部分の電解めっき膜35a、35b、無電解めっき膜33a、33b、銅箔32a、32bが除去された後、エッチングレジストが除去され、無電解めっき膜33a及び電解めっき膜35aから成るビア導体36Aと、無電解めっき膜33a、電解めっき膜35a及び銅箔32aから成る導体パターン34Aとが形成される。さらに、無電解めっき膜33b及び電解めっき膜35bから成るビア導体36Bと、無電解めっき膜33b、電解めっき膜35b及び銅箔32bから成る導体パターン34Bとが形成される(図6(F))。

【0031】

図6中に示した処理が繰り返され、ビア導体36C及び導体パターン34Cを備える絶縁層30Cと、ビア導体36D及び導体パターン34Dを備える絶縁層30Dとが積層される。更に、ビア導体36E及び導体パターン34Eを備える絶縁層30Eと、ビア導体36F及び導体パターン34Fを備える絶縁層30Fとが積層され、本実施形態のコア基材30が完成する(図7(A))。

【0032】

コア基板30の第1面上及び第2面上に、無機繊維補強材(ガラスクロス芯材など)を含まない層間絶縁層用樹脂フィルムが積層され、熱硬化により層間樹脂絶縁層50A、50Bが形成される(図7(B))。

【0033】

CO2ガスレーザにて層間樹脂絶縁層50Aの内部には、導体パターン34E、ビア導体36Eに至る開口51Aが設けられ、層間樹脂絶縁層50Bの内部には、導体パターン34F、ビア導体36Fに至る開口51Bが設けられる(図7(C))。クロム酸、過マンガン酸塩などの酸化剤等に浸漬させることによって、層間樹脂絶縁層50A、50Bの表面が粗化される(図示せず)。

【0034】

層間樹脂絶縁層50A、50Bの表層にパラジウムなどの触媒が付与されて、無電解めっき液に5〜60分間浸漬させることにより、0.1〜5μmの範囲で無電解めっき膜53a、53bが設けられる(図7(D))。

【0035】

上記処理を終えた積層体に、市販の感光性ドライフィルムが貼り付けられ、フォトマスクフィルムを載置して露光した後、炭酸ナトリウムで現像処理し、厚さ15μmのめっきレジスト54a、54bが設けられる(図8(A))。電解めっき処理により、厚さ15μmの電解めっき膜56a、56bが形成される(図8(B))。

【0036】

めっきレジストが5%NaOHで剥離除去された後、そのめっきレジスト下の無電解めっき膜53a、53bが硝酸および硫酸と過酸化水素の混合液を用いるエッチングにて溶解除去される。これにより、無電解めっき膜53a、53bと電解めっき膜56a、56bとからなる、厚さ約15μmの導体パターン58A、58Bとビア導体60A、60Bとが形成される(図8(C))。第二銅錯体と有機酸とを含有するエッチング液によって、導体パターン58A、58B及びビア導体60A、60B表面が粗化される(図示せず)。

【0037】

図7(B)〜図8(C)の処理が繰り返され、コア基材30の第1面上にビルドアップ層501が設けられ、第2面上にビルドアップ層502が設けられる(図8(D))。

【0038】

次に、市販のソルダーレジスト組成物が塗布され、これを露光・現像することで、開口部71を備えるソルダーレジスト層70が形成される(図9(A))。

【0039】

積層体が無電解ニッケルめっき液に浸漬され、開口部71内にニッケルめっき層72が形成される。さらに、その積層体が無電解金めっき液に浸漬され、ニッケルめっき層72上に、金めっき層74が形成される(図9(B))。ニッケル−金層以外にも、ニッケル−パラジウム−金層を形成してもよい。

【0040】

開口部71の内部に半田ボールが搭載され、リフローを行うことで、上面側に半田バンプ76Uが、裏面側に半田バンプ76Dが形成される。これにより、多層プリント配線板10が完成する(図9(C)及び図1)。

【0041】

[第2実施形態]

図10は、第2実施形態の多層プリント配線板の断面図を示す。

第2実施形態の多層プリント配線板では、コア基板30に設けられたインダクタL1,L2の直下のビルドアップ層502内にさらにインダクタL3,L4が形成されている。

このインダクタL3,L4は、導体パターン58B、導体パターン58D、導体パターン50F、ビア導体60B、ビア導体60D、ビア導体60F及びビア導体60Fにより形成されている。なお、このビルドアップ層502に設けられたインダクタL3,L4は、コア基材30内のインダクタL1,L2と同様のデザインであってもよく、異なるデザインであってもよい。

【0042】

これによれば、ビルドアップ層502にもインダクタが形成されることになるため、コア基材30内のインダクタンス分のみによらず、更なるインダクタンス成分を確保することが可能になる。また、コア基材30の表裏のビルドアップ層501,502における導体の体積の差を調整でき、配線板の反りを低減することが可能になると考えられる。

【符号の説明】

【0043】

10 多層プリント配線板

30 コア基材

30M,30A,30B,30C,30D,30E,30F 第1絶縁層

34Ma,34Mb,34A,34B,34C,34D,34E,34F 第1導体パターン

36M,36A,36B,36C,36D,36E,36F 第1ビア導体

50G、50E、50C、50A、50B、50D、50F、50H 第2絶縁層

58A,58B,58C,58D,58E,58F,58G,58H, 第2導体パターン

60A,60B,60C,60D,60E,60F,60G,60H, 第2ビア導体

【特許請求の範囲】

【請求項1】

複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材と、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層と、

を備える多層プリント配線板であって、

前記複数の第1絶縁層は無機繊維補強材を含み、

前記コア基材は、前記第1導体パターンと前記第1ビア導体とにより形成されるインダクタを有している。

【請求項2】

請求項1の多層プリント配線板であって:

前記インダクタの周囲に位置する少なくとも一部の第1ビア導体は、前記コア基材の厚み方向において直線状に積層されている。

【請求項3】

請求項1の多層プリント配線板であって:

前記第1導体パターンの厚みは、前記第2導体パターンの厚みよりも厚い。

【請求項4】

請求項1の多層プリント配線板であって:

前記第1ビア導体の直径は、前記第2ビア導体の直径よりも大きい。

【請求項5】

請求項1の多層プリント配線板であって:

前記第1絶縁層の厚みは、前記第2絶縁層の厚みよりも厚い。

【請求項6】

請求項1の多層プリント配線板であって:

前記第2導体パターンのうち、最外層に位置する第2導体パターン上には、半導体素子を接続するバンプが設けられ、該バンプが形成される領域の直下に前記インダクタが設けられている。

【請求項7】

請求項6の多層プリント配線板であって:

前記コア基材は、前記半導体素子が実装される側の第1面と該第1面とは反対側の第2面とを有し、

前記第1面上に設けられて前記インダクタを形成する第1導体パターンと、前記最外層に位置する前記第2導体パターンとを接続する複数の第2ビア導体は、直線状に積層されている。

【請求項8】

請求項1の多層プリント配線板であって:

前記コア基材の第2面上に設けられているビルドアップ層のうち、前記インダクタの形成領域の直下には、前記第2導体パターンと前記第2ビア導体とにより形成されるインダクタがさらに設けられている。

【請求項9】

請求項1の多層プリント配線板であって:

前記コア基材は、6層以上の第1導体パターンを有する。

【請求項10】

複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材を形成することと、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層を形成することと、

を備える多層プリント配線板の製造方法であって、

前記第1絶縁層は無機繊維補強材を含み、

前記第1導体パターンと前記第1ビア導体とによりインダクタを形成する。

【請求項11】

請求項10の多層プリント配線板の製造方法であって:

前記第1導体パターンの厚みを前記第2導体パターンよりも厚くする。

【請求項12】

請求項10の多層プリント配線板の製造方法であって:

前記第1導体パターンはサブトラクティブ法により形成され、前記第2導体パターンはセミアディティブ法により形成される。

【請求項1】

複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材と、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層と、

を備える多層プリント配線板であって、

前記複数の第1絶縁層は無機繊維補強材を含み、

前記コア基材は、前記第1導体パターンと前記第1ビア導体とにより形成されるインダクタを有している。

【請求項2】

請求項1の多層プリント配線板であって:

前記インダクタの周囲に位置する少なくとも一部の第1ビア導体は、前記コア基材の厚み方向において直線状に積層されている。

【請求項3】

請求項1の多層プリント配線板であって:

前記第1導体パターンの厚みは、前記第2導体パターンの厚みよりも厚い。

【請求項4】

請求項1の多層プリント配線板であって:

前記第1ビア導体の直径は、前記第2ビア導体の直径よりも大きい。

【請求項5】

請求項1の多層プリント配線板であって:

前記第1絶縁層の厚みは、前記第2絶縁層の厚みよりも厚い。

【請求項6】

請求項1の多層プリント配線板であって:

前記第2導体パターンのうち、最外層に位置する第2導体パターン上には、半導体素子を接続するバンプが設けられ、該バンプが形成される領域の直下に前記インダクタが設けられている。

【請求項7】

請求項6の多層プリント配線板であって:

前記コア基材は、前記半導体素子が実装される側の第1面と該第1面とは反対側の第2面とを有し、

前記第1面上に設けられて前記インダクタを形成する第1導体パターンと、前記最外層に位置する前記第2導体パターンとを接続する複数の第2ビア導体は、直線状に積層されている。

【請求項8】

請求項1の多層プリント配線板であって:

前記コア基材の第2面上に設けられているビルドアップ層のうち、前記インダクタの形成領域の直下には、前記第2導体パターンと前記第2ビア導体とにより形成されるインダクタがさらに設けられている。

【請求項9】

請求項1の多層プリント配線板であって:

前記コア基材は、6層以上の第1導体パターンを有する。

【請求項10】

複数の第1絶縁層と、該第1絶縁層上の第1導体パターンと、前記第1絶縁層の内部に形成され前記第1導体パターン同士を接続する第1ビア導体とを有するコア基材を形成することと、

前記コア基材上に設けられ、無機繊維補強材を含まない第2絶縁層と、該第2絶縁層上の第2導体パターンと、前記第2絶縁層の内部に形成され前記第2導体パターン同士を接続する第2ビア導体とを有するビルドアップ層を形成することと、

を備える多層プリント配線板の製造方法であって、

前記第1絶縁層は無機繊維補強材を含み、

前記第1導体パターンと前記第1ビア導体とによりインダクタを形成する。

【請求項11】

請求項10の多層プリント配線板の製造方法であって:

前記第1導体パターンの厚みを前記第2導体パターンよりも厚くする。

【請求項12】

請求項10の多層プリント配線板の製造方法であって:

前記第1導体パターンはサブトラクティブ法により形成され、前記第2導体パターンはセミアディティブ法により形成される。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【公開番号】特開2013−70035(P2013−70035A)

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願番号】特願2012−173150(P2012−173150)

【出願日】平成24年8月3日(2012.8.3)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

【公開日】平成25年4月18日(2013.4.18)

【国際特許分類】

【出願日】平成24年8月3日(2012.8.3)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

[ Back to top ]