情報処理装置

【目的】 I/Oアクセスの処理効率を上げてCPUの実行効率を向上する情報処理装置を提供することである。

【構成】 CPU1がアドレス及びデータバス6を介してI/Oコントローラ3をアクセスし、このI/Oコントローラ3がアドレス及びデータバス6の占有/解放の切り替えを行なう。その後、I/Oコントローラ3がI/Oポート4を介して入出力装置5をアクセスし、I/Oポート4と入出力装置5間でデータのやりとりを行ない、CPU1がI/Oアクセス命令をI/Oコントローラ3に送出した時に、アドレス及びデータバス6は解放されてCPU1は次の命令を実行できる。さらに、I/Oコントローラ3はデータのやりとりが終了すると、CPU1にI/Oレスポンス信号線7を介してI/Oレスポンス信号を送出して、CPU1がI/Oアクセス結果の処理を行なう。

【構成】 CPU1がアドレス及びデータバス6を介してI/Oコントローラ3をアクセスし、このI/Oコントローラ3がアドレス及びデータバス6の占有/解放の切り替えを行なう。その後、I/Oコントローラ3がI/Oポート4を介して入出力装置5をアクセスし、I/Oポート4と入出力装置5間でデータのやりとりを行ない、CPU1がI/Oアクセス命令をI/Oコントローラ3に送出した時に、アドレス及びデータバス6は解放されてCPU1は次の命令を実行できる。さらに、I/Oコントローラ3はデータのやりとりが終了すると、CPU1にI/Oレスポンス信号線7を介してI/Oレスポンス信号を送出して、CPU1がI/Oアクセス結果の処理を行なう。

【発明の詳細な説明】

【0001】

【産業上の利用分野】本発明は、情報処理装置に係り、特に入出力装置をコントロールするCPUを備えた情報処理装置に関する。

【0002】

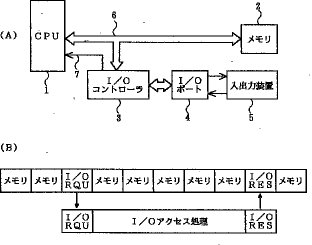

【従来の技術】従来の情報処理装置は、図2の(A)に示すように、CPU1が、入出力装置5とのデータのやりとりを行なう時、CPU1はI/Oポート14にアクセスを行ない、CPU1とI/Oポート14間で、アドレス及びデータバス6は占有されてしまう。

【0003】この時、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえず、I/Oアクセスの処理が終了してから、CPU1は次の処理を行なう。

【0004】CPU1の処理能力を上げるためには、内部の処理をパイプライン化して、処理効率を上げているものもあるが、パイプラインの効果はCPU1内部のみ有効で、CPU1外部のバス上でのパイプライン処理は不可能である。

【0005】

【発明が解決しようとする課題】従来の情報処理装置では、CPU1がI/Oポート14をアクセスして、入出力装置5とのデータのやりとりを行なう時、CPU1とI/Oポート14間で、アドレス及びデータバス6は占有されてしまい、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえない。

【0006】I/Oアクセスの処理が終了すると、CPU1は次の処理を行なうが、このI/Oアクセスによる処理時間は、図2の(B)に示すように、メモリアクセスによる処理時間に比べかなり長いものであり、プログラムの実行速度に悪影響を与えている。

【0007】また、I/Oアクセス中は、入出力装置5とのデータのやりとりが完了するまで、アドレス及びデータバス6を占有している。

【0008】本発明の目的は、I/Oアクセスの処理効率を上げてCPUの実行効率を向上する情報処理装置を提供することである。

【0009】

【課題を解決するための手段】上述の目的を達成するために、本発明の情報処理装置は、CPUと、このCPUの指令の下に、入出力装置の入出力を制御するプログラムが格納されたメモリと、このプログラムの制御により上記入出力装置の入出力を制御するI/Oコントローラと、このI/Oコントローラの出力信号に基づいて上記入出力装置のデータの入出力を行なうI/Oポートとを具備し、上記CPUがI/Oアクセス信号をI/Oコントローラに送出することで、上記I/Oコントローラからリクエスト信号を上記CPUへ送出してアドレスバス及びデータバスを開放し、上記I/Oポートと入出力装置とのデータの入出力処理終了後、上記I/Oコントローラからレスポンス信号を上記CPUに送出して入出力を制御することを特徴とする。

【0010】

【実施例】次に、本発明の情報処理装置における一実施例について、図1を参照して説明する。

【0011】図1は、本発明の一実施例による構成図(A)及びI/Oアクセス図(B)である。

【0012】本発明の情報処理装置における一実施例は、図1に示すように、アドレス及びデータバス6を介して各種周辺装置とのデータ処理を行なうCPU1と、データの入出力を制御するプログラムが格納されたメモリ2と、このプログラムの制御によりデータの入出力が終了した時にI/Oレスポンス信号線7を介してレスポンス信号をCPU1に送出するI/Oコントローラ3と、このI/Oコントローラ3の出力信号に基づいてデータの入出力を行なうI/Oポート4と、このI/Oポート4によりデータの入出力が制御される入出力装置5とで構成される。

【0013】図1の(B)に示すように、本発明の情報処理装置における一実施例の動作は、CPU1がアドレス及びデータバス6を介してI/Oコントローラ3をアクセスし、このI/Oコントローラ3がアドレス及びデータバス6の占有/解放の切り替えを行なう。

【0014】その後、I/Oコントローラ3がI/Oポート4を介して入出力装置5をアクセスし、I/Oポート4と入出力装置5間でデータのやりとりを行なう。

【0015】さらに、CPU1がI/Oアクセス命令をI/Oコントローラ3に送出すると(I/ORQU:I/Oリクエスト)、I/Oコントローラ4がI/Oポート4へのアクセスを行なわれ、この時にアドレス及びデータバス6は解放されるので、CPU1は次の命令を実行することができる。

【0016】ただし、実行される命令がI/Oアクセスの場合、以前のI/Oアクセス処理が終了するまで実行されずに待たされるが、メモリアクセスが連続する場合は、その命令は実行されていく。

【0017】また、I/Oコントローラ3はI/Oポート4へアクセスを行ない、データのやりとりが終了すると、CPU1にアクセス準備完了を知らせるため、I/Oレスポンス信号線7を介してI/Oレスポンス信号をCPU1に送出し、CPU1がI/Oアクセス結果の処理を行なう(IORES:I/Oレスポンス)。

【0018】つまり、CPU1はメモリアクセス処理とI/Oアクセス処理を平行して実行でき、かつI/Oアクセス処理中のアドレス及びデータバス6の解放を行ない、CPU1の実行効率を上げることができる。

【0019】従って、CPU1はI/Oリクエスト機能を備え、I/Oからのアクセス準備完了の信号を受けてから、I/Oリクエスト時のI/O命令を実行することにより、外部バスを含めたパイプライン動作が可能となり、CPU1の実行効率を上げることができる。

【0020】次に、従来の情報処理装置について、図2を参照して説明する。

【0021】図2は、従来例の構成図(A)及びI/Oアクセス図(B)である。

【0022】従来の情報処理装置は、図2の(A)に示すように、アドレス及びデータバス6を介して各種周辺装置とのデータ処理を行なうCPU1と、データの入出力を制御するプログラムが格納されたメモリ2と、このプログラムの制御によりデータの入出力を行なうI/Oポート14と、このI/Oポート14によりデータの入出力が制御される入出力装置5とで構成される。

【0023】図2の(B)に示すように、従来の情報処理装置の動作は、CPU1が入出力装置5とデータのやりとりを行なう時、CPU1はアドレス及びデータバス6を介して、I/Oポート14へアクセスを行なう。

【0024】この時、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえず、I/Oアクセスの処理が終了してから、CPU1は次の処理を行なう。

【0025】つまり、CPU1はメモリアクセス処理か、I/Oアクセス処理のどちらか1つしか実行できない。

【0026】

【発明の効果】本発明の情報処理装置によれば、入出力装置の入出力を制御するI/Oコントローラを備えることで、I/OアクセスによるCPUの占有時間を低減し、かつプログラムの実行速度を向上させる効果がある。

【図面の簡単な説明】

【図1】本発明の一実施例による構成図(A)及びI/Oアクセス図(B)である。

【図2】従来例の構成図(A)及びI/Oアクセス図(B)である。

【符号の説明】

1 CPU

2 メモリ

3 I/Oコントローラ

4,14 I/Oポート

5 入出力装置

6 アドレスバス及びデータバス

7 レスポンス信号(I/Oレスポンス信号線)

I/OREQ レスポンス信号(I/Oレスポンス)

I/ORQU リクエスト信号(I/Oリクエスト)

【0001】

【産業上の利用分野】本発明は、情報処理装置に係り、特に入出力装置をコントロールするCPUを備えた情報処理装置に関する。

【0002】

【従来の技術】従来の情報処理装置は、図2の(A)に示すように、CPU1が、入出力装置5とのデータのやりとりを行なう時、CPU1はI/Oポート14にアクセスを行ない、CPU1とI/Oポート14間で、アドレス及びデータバス6は占有されてしまう。

【0003】この時、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえず、I/Oアクセスの処理が終了してから、CPU1は次の処理を行なう。

【0004】CPU1の処理能力を上げるためには、内部の処理をパイプライン化して、処理効率を上げているものもあるが、パイプラインの効果はCPU1内部のみ有効で、CPU1外部のバス上でのパイプライン処理は不可能である。

【0005】

【発明が解決しようとする課題】従来の情報処理装置では、CPU1がI/Oポート14をアクセスして、入出力装置5とのデータのやりとりを行なう時、CPU1とI/Oポート14間で、アドレス及びデータバス6は占有されてしまい、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえない。

【0006】I/Oアクセスの処理が終了すると、CPU1は次の処理を行なうが、このI/Oアクセスによる処理時間は、図2の(B)に示すように、メモリアクセスによる処理時間に比べかなり長いものであり、プログラムの実行速度に悪影響を与えている。

【0007】また、I/Oアクセス中は、入出力装置5とのデータのやりとりが完了するまで、アドレス及びデータバス6を占有している。

【0008】本発明の目的は、I/Oアクセスの処理効率を上げてCPUの実行効率を向上する情報処理装置を提供することである。

【0009】

【課題を解決するための手段】上述の目的を達成するために、本発明の情報処理装置は、CPUと、このCPUの指令の下に、入出力装置の入出力を制御するプログラムが格納されたメモリと、このプログラムの制御により上記入出力装置の入出力を制御するI/Oコントローラと、このI/Oコントローラの出力信号に基づいて上記入出力装置のデータの入出力を行なうI/Oポートとを具備し、上記CPUがI/Oアクセス信号をI/Oコントローラに送出することで、上記I/Oコントローラからリクエスト信号を上記CPUへ送出してアドレスバス及びデータバスを開放し、上記I/Oポートと入出力装置とのデータの入出力処理終了後、上記I/Oコントローラからレスポンス信号を上記CPUに送出して入出力を制御することを特徴とする。

【0010】

【実施例】次に、本発明の情報処理装置における一実施例について、図1を参照して説明する。

【0011】図1は、本発明の一実施例による構成図(A)及びI/Oアクセス図(B)である。

【0012】本発明の情報処理装置における一実施例は、図1に示すように、アドレス及びデータバス6を介して各種周辺装置とのデータ処理を行なうCPU1と、データの入出力を制御するプログラムが格納されたメモリ2と、このプログラムの制御によりデータの入出力が終了した時にI/Oレスポンス信号線7を介してレスポンス信号をCPU1に送出するI/Oコントローラ3と、このI/Oコントローラ3の出力信号に基づいてデータの入出力を行なうI/Oポート4と、このI/Oポート4によりデータの入出力が制御される入出力装置5とで構成される。

【0013】図1の(B)に示すように、本発明の情報処理装置における一実施例の動作は、CPU1がアドレス及びデータバス6を介してI/Oコントローラ3をアクセスし、このI/Oコントローラ3がアドレス及びデータバス6の占有/解放の切り替えを行なう。

【0014】その後、I/Oコントローラ3がI/Oポート4を介して入出力装置5をアクセスし、I/Oポート4と入出力装置5間でデータのやりとりを行なう。

【0015】さらに、CPU1がI/Oアクセス命令をI/Oコントローラ3に送出すると(I/ORQU:I/Oリクエスト)、I/Oコントローラ4がI/Oポート4へのアクセスを行なわれ、この時にアドレス及びデータバス6は解放されるので、CPU1は次の命令を実行することができる。

【0016】ただし、実行される命令がI/Oアクセスの場合、以前のI/Oアクセス処理が終了するまで実行されずに待たされるが、メモリアクセスが連続する場合は、その命令は実行されていく。

【0017】また、I/Oコントローラ3はI/Oポート4へアクセスを行ない、データのやりとりが終了すると、CPU1にアクセス準備完了を知らせるため、I/Oレスポンス信号線7を介してI/Oレスポンス信号をCPU1に送出し、CPU1がI/Oアクセス結果の処理を行なう(IORES:I/Oレスポンス)。

【0018】つまり、CPU1はメモリアクセス処理とI/Oアクセス処理を平行して実行でき、かつI/Oアクセス処理中のアドレス及びデータバス6の解放を行ない、CPU1の実行効率を上げることができる。

【0019】従って、CPU1はI/Oリクエスト機能を備え、I/Oからのアクセス準備完了の信号を受けてから、I/Oリクエスト時のI/O命令を実行することにより、外部バスを含めたパイプライン動作が可能となり、CPU1の実行効率を上げることができる。

【0020】次に、従来の情報処理装置について、図2を参照して説明する。

【0021】図2は、従来例の構成図(A)及びI/Oアクセス図(B)である。

【0022】従来の情報処理装置は、図2の(A)に示すように、アドレス及びデータバス6を介して各種周辺装置とのデータ処理を行なうCPU1と、データの入出力を制御するプログラムが格納されたメモリ2と、このプログラムの制御によりデータの入出力を行なうI/Oポート14と、このI/Oポート14によりデータの入出力が制御される入出力装置5とで構成される。

【0023】図2の(B)に示すように、従来の情報処理装置の動作は、CPU1が入出力装置5とデータのやりとりを行なう時、CPU1はアドレス及びデータバス6を介して、I/Oポート14へアクセスを行なう。

【0024】この時、CPU1はI/Oアクセスの処理が終了するまで、何も処理を行なえず、I/Oアクセスの処理が終了してから、CPU1は次の処理を行なう。

【0025】つまり、CPU1はメモリアクセス処理か、I/Oアクセス処理のどちらか1つしか実行できない。

【0026】

【発明の効果】本発明の情報処理装置によれば、入出力装置の入出力を制御するI/Oコントローラを備えることで、I/OアクセスによるCPUの占有時間を低減し、かつプログラムの実行速度を向上させる効果がある。

【図面の簡単な説明】

【図1】本発明の一実施例による構成図(A)及びI/Oアクセス図(B)である。

【図2】従来例の構成図(A)及びI/Oアクセス図(B)である。

【符号の説明】

1 CPU

2 メモリ

3 I/Oコントローラ

4,14 I/Oポート

5 入出力装置

6 アドレスバス及びデータバス

7 レスポンス信号(I/Oレスポンス信号線)

I/OREQ レスポンス信号(I/Oレスポンス)

I/ORQU リクエスト信号(I/Oリクエスト)

【特許請求の範囲】

【請求項1】 CPUと、このCPUの指令の下に、入出力装置の入出力を制御するプログラムが格納されたメモリと、このプログラムの制御により上記入出力装置の入出力を制御するI/Oコントローラと、このI/Oコントローラの出力信号に基づいて上記入出力装置のデータの入出力を行なうI/Oポートとを具備し、上記CPUがI/Oアクセス信号をI/Oコントローラに送出することで、上記I/Oコントローラからリクエスト信号を上記CPUへ送出してアドレスバス及びデータバスを開放し、上記I/Oポートと入出力装置とのデータの入出力処理終了後、上記I/Oコントローラからレスポンス信号を上記CPUに送出して入出力を制御することを特徴とする情報処理装置。

【請求項1】 CPUと、このCPUの指令の下に、入出力装置の入出力を制御するプログラムが格納されたメモリと、このプログラムの制御により上記入出力装置の入出力を制御するI/Oコントローラと、このI/Oコントローラの出力信号に基づいて上記入出力装置のデータの入出力を行なうI/Oポートとを具備し、上記CPUがI/Oアクセス信号をI/Oコントローラに送出することで、上記I/Oコントローラからリクエスト信号を上記CPUへ送出してアドレスバス及びデータバスを開放し、上記I/Oポートと入出力装置とのデータの入出力処理終了後、上記I/Oコントローラからレスポンス信号を上記CPUに送出して入出力を制御することを特徴とする情報処理装置。

【図2】

【図1】

【図1】

【公開番号】特開平5−204813

【公開日】平成5年(1993)8月13日

【国際特許分類】

【出願番号】特願平4−10405

【出願日】平成4年(1992)1月23日

【出願人】(000001937)日本電気ホームエレクトロニクス株式会社 (8)

【公開日】平成5年(1993)8月13日

【国際特許分類】

【出願日】平成4年(1992)1月23日

【出願人】(000001937)日本電気ホームエレクトロニクス株式会社 (8)

[ Back to top ]