突入電流低減回路および電気機器

【課題】二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得る。

【解決手段】動作回路10と直列に挿入されたダイオードブリッジDB2と、ダイオードブリッジDB2の交流端子間に接続された抵抗素子R1と、ダイオードブリッジDB2の直流端子間に接続された電流制御回路21とを備え、この電流制御回路21に、直流端子間に接続されたスイッチング素子Q1と、スイッチング素子Q1のバイアス制御点に接続されるとともに、交流電源を用いて動作回路10で生成して第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる容量素子C1と、容量素子C1に並列接続された抵抗素子R2と、直流電源により容量素子C1を充電する充電経路に挿入された抵抗素子R3と、充電経路に挿入されて電流制御回路21から動作回路10への逆電流を阻止するダイオードD3とを備える。

【解決手段】動作回路10と直列に挿入されたダイオードブリッジDB2と、ダイオードブリッジDB2の交流端子間に接続された抵抗素子R1と、ダイオードブリッジDB2の直流端子間に接続された電流制御回路21とを備え、この電流制御回路21に、直流端子間に接続されたスイッチング素子Q1と、スイッチング素子Q1のバイアス制御点に接続されるとともに、交流電源を用いて動作回路10で生成して第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる容量素子C1と、容量素子C1に並列接続された抵抗素子R2と、直流電源により容量素子C1を充電する充電経路に挿入された抵抗素子R3と、充電経路に挿入されて電流制御回路21から動作回路10への逆電流を阻止するダイオードD3とを備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電源供給制御技術に関し、特に電源から負荷回路への突入電流を低減する突入電流低減技術に関する。

【背景技術】

【0002】

インバータやコンバータなどの電力変換回路は、高い周波数でACまたはDCの入力電源をスイッチングして、所望の電圧を持つACまたはDCの出力電源へ変換する回路である。このような電力変換回路では、AC電源から得られたDC電源に含まれる変動成分を平滑化するため、大容量の容量素子が用いられている。

したがって、電源投入時に、この容量素子を充電するよう突入電流が流入する。この突入電流は、急峻で振幅も大きいため、不要電磁波を放出し、周囲の電子機器内にノイズ電流を誘発させる原因にもなる。

【0003】

従来、このような突入電流を低減させる突入電流低減技術として、スイッチング素子を用いて突入電流を低減する方法が提案されている(例えば、特許文献1など参照)。図8は、従来の突入電流低減回路を示す回路図である。

図8の突入電流低減回路50では、突入電流が流れる供給経路上にNチャネルMOSFETからなるスイッチング素子Q51を配置し、動作回路10に設けられている大容量の容量素子C0の電源投入当初はスイッチング素子Q51をオフしておき、ある程度まで容量素子C0を充電した後、スイッチング素子Q51をターンオンすることにより、電源投入時における容量素子C0への突入電流を低減している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3990421号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

突入電流は、電気機器の利用者が意図的に電源を投入する場合だけでなく、交流電源が停電から復帰する場合にも流れる。停電から復帰までの時間が短い瞬時停電の場合も同様である。また、照明機器の場合、利用者が交流電源の電源スイッチを一旦オフして消灯した後、思い直して直ぐにスイッチをオンして点灯させる場合がある。さらに、人感センサにより照明機器の点灯/消灯を制御する場合にも、利用者の動きに応じて、一旦オフして消灯した後、直ぐにオンして点灯することがある。したがって、このような交流電源の瞬断が行われた場合でも、突入電流低減回路において、動作回路への突入電流を低減させる必要がある。

【0006】

前述した従来技術では、電源投入当初において、動作回路10に設けられている大容量の容量素子C0に充電電流を供給する供給経路が、スイッチング素子Q51のターンオンを遅延させて突入電流低減動作を制御する時定数回路で兼用されている。

具体的には、スイッチング素子Q51のドレイン端子とゲート端子との間に接続された抵抗素子R51と、スイッチング素子Q51のゲート端子とソース端子との間に接続された抵抗素子R52とが供給経路を構成しており、抵抗素子R52とこれに並列接続された容量素子C1とが時定数回路を構成している。

【0007】

さて、電源投入当初においては、スイッチング素子Q51のドレイン端子とソース端子との間の端子間抵抗がほぼ無限大であり、その後、時定数回路によりバイアス電圧(ゲート電圧)が徐々に上昇してスイッチング素子Q51がターンオンし、端子間抵抗がほぼゼロとなる。この際、スイッチング素子Q51がターンオンするまでは抵抗素子R1,R2の供給経路を介して容量素子C0が徐々に充電され、スイッチング素子Q51がターンオンした後は、スイッチング素子Q51を介して容量素子C0が一気に充電される。

【0008】

したがって、電源投入時に供給経路を介して最初に発生する一次突入電流の後に、スイッチング素子Q51がターンオンするタイミングで二次突入電流が発生する。この二次突入電流の大きさは、スイッチング素子Q51のターンオン前後における容量素子C0の電位差に起因し、電位差が大きいほど二次突入電流は大きくなり、不要電磁波の放出原因になる。

【0009】

ここで、交流電源の瞬断に対する応答性を考慮した場合、時定数回路の容量素子C1に充電されている電荷が電源の再投入時に残っていると、スイッチング素子Q51がオン状態のまま電源が再投入されることになり、一次突入電流を低減できなくなる。このため、容量素子C1の電荷をすばやく放電して、交流電源の瞬断に対する応答性を確保するためには、時定数回路の時定数を小さいほうが望ましいことになる。

【0010】

しかしながら、時定数を小さくすると、電源の投入に応じて抵抗素子R51を介して容量素子C51が充電されてバイアス電圧がすぐに上昇するため、容量素子C0が十分充電されていない状態で、早めにスイッチング素子Q51がターンオンすることになる。このため、スイッチング素子Q51のターンオン前後における容量素子C0の電位差が大きくなり、二次突入電流が大きくなる。

したがって、前述した従来技術によれば、二次突入電流の低減を実現するためには時定数回路の時定数を小さくできないため、交流電源の瞬断に対して良好な応答性を得ることができないという問題点があった。

【0011】

本発明はこのような課題を解決するためのものであり、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることができる突入電流低減技術を提供することを目的としている。

【課題を解決するための手段】

【0012】

このような目的を達成するために、本発明にかかる突入電流低減回路は、交流源からの交流電源を動作回路へ供給する供給経路に対して、動作回路と直列に挿入されたダイオードブリッジと、ダイオードブリッジの交流端子間に接続された第1の抵抗素子と、ダイオードブリッジの直流端子間に接続された電流制御回路とを備え、電流制御回路は、直流端子間に接続されたスイッチング素子と、スイッチング素子のバイアス制御点に接続されるとともに、交流電源を用いて動作回路で生成されて第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる第2の容量素子と、容量素子に並列接続された第2の抵抗素子と、直流電源により第2の容量素子を充電する充電経路に挿入された第3の抵抗素子と、充電経路に挿入されて電流制御回路から動作回路への逆電流を阻止するダイオードとを備えるものである。

また、本発明にかかる電気機器は、前述した突入電流低減回路を備える電気機器である。

【発明の効果】

【0013】

本発明によれば、突入電流低減回路に設けられたスイッチング素子のバイアス供給点に接続されている第2の容量素子が、交流電源を用いて動作回路で生成して第1の容量素子に充電された直流電源により充電経路を介して充電されるため、第1の容量素子がある程度充電された状態となってから、スイッチング素子がターンオンされることになる。したがって、スイッチング素子のターンオン前後における第1の容量素子の電位差が小さくなってから、スイッチング素子をターンオンさせることができ、スイッチング素子のターンオン時における二次突入電流を低減できる。

【0014】

このため、スイッチング素子のターンオン時における二次突入電流を低減するために、第2の容量素子とこれに並列接続された第2の抵抗素子の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断時間に見合った短い時定数を設定することができる。よって、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【図面の簡単な説明】

【0015】

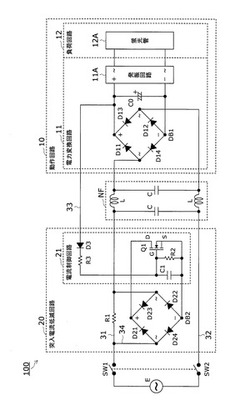

【図1】第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【図2】突入電流低減回路の動作(V1>V2)を示す説明図である。

【図3】突入電流低減回路の動作(V1<V2)を示す説明図である。

【図4】従来の突入電流低減回路の動作を示す信号波形図である。

【図5】本実施の形態にかかる突入電流低減回路の動作を示す信号波形図である。

【図6】交流電源の瞬断時間の変化に対する突入電流特性を示すグラフである。

【図7】第2の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【図8】従来の突入電流低減回路を示す回路図である。

【発明を実施するための形態】

【0016】

次に、本発明の実施の形態について図面を参照して説明する。

[第1の実施の形態]

まず、図1を参照して、本発明の第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器について説明する。図1は、第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【0017】

[電気機器]

電気機器100は、交流源Eとその両端に設けられたスイッチSW1,SW2とを含む交流回路に接続されて、交流源EからスイッチSW1,SW2を介して供給された単相の交流電源により動作する動作回路10を備えている。

図1の例では、動作回路10として、交流電源により蛍光管を点灯駆動する照明用動作回路が示されている。

【0018】

動作回路10には、主な回路構成として、電力変換回路11と負荷回路12が設けられている。

電力変換回路11は、交流源Eから供給された交流電源を直流電源に一旦変換した後、負荷回路12で用いる周波数の交流電源に再変換して出力する機能を有している。

負荷回路12は、電力変換回路11からの交流電源により動作する機能を有している。

【0019】

電力変換回路11には、主な回路として、ダイオードブリッジDB1、容量素子C0(第1の容量素子)、および発振回路11Aが設けられている。

ダイオードブリッジDB1は、ブリッジ接続された4つのダイオードD11,D12,D13,D14からなり、入力された交流電源を整流して直流電源に変換して出力する機能を有している。

【0020】

容量素子C0は、ダイオードブリッジDB1の直流出力端子(+端子,−端子)間に接続された大容量の電解コンデンサからなり、ダイオードブリッジDB1から出力された直流電源を平滑化する機能を有している。

発振回路11Aは、共振型DC−AC変換回路などのインバータからなり、直流入力端子(+端子,−端子)に入力された、容量素子C0で平滑化された直流電源を、負荷回路12で用いる周波数の二次交流電源に再変換して、交流出力端子(〜端子)から出力する機能を有している。

【0021】

負荷回路12には、主な回路として、蛍光管12Aが設けられている。

蛍光管12Aは、発振回路11Aの交流出力端子間に接続されて、発振回路11Aから出力された二次交流電源により点灯する機能を有している。

【0022】

これにより、動作回路10では、交流源Eから供給経路31,32を介して供給された交流電源が、電力変換回路11に入力されて、ダイオードブリッジDB1により直流電源に変換されて、容量素子C0で平滑化された後、発振回路11Aで二次交流電源に再変換されて負荷回路12へ出力され、この二次交流電源により負荷回路12の蛍光管12Aが点灯する。

【0023】

ノイズフィルタNFは、電源ライン用EMIフィルタなど、一般的なノイズフィルタからなり、動作回路10の入力側に設けられて、動作回路10の発振回路11Aで発生した高周波ノイズを除去する機能を有している。

このノイズフィルタNFは、交流源Eから動作回路10へ交流電源が供給される供給経路31,32上にそれぞれ挿入された2つのコイルL(ノーマルモードチョーク)と、これらコイルLの入力端子間および出力端子間にそれぞれ接続された2つの容量素子C(アクロスザライン容量素子)とから構成されている。

【0024】

[突入電流低減回路]

突入電流低減回路20は、交流源Eからの交流電源を動作回路10へ供給する供給経路に対して、動作回路10と直列に挿入されて、交流電流の供給開始時に動作回路10へ流れ込む突入電流を低減する回路である。図1の例では、交流源Eから動作回路10へ交流電源が供給される供給経路のうちスイッチSW1側の供給経路31において、スイッチSW1とノイズフィルタとの間に挿入されている。

【0025】

この突入電流低減回路20には、主な回路部として、ダイオードブリッジDB2、抵抗素子(第1の抵抗素子)R1、および電流制御回路21が設けられている。

【0026】

ダイオードブリッジDB2は、ブリッジ接続された4つのダイオードD21,D22,D23,D24からなり、動作回路10に交流電源を供給する供給経路に対して、動作回路10と直列に挿入されている。具体的には、スイッチSW1側の供給経路31のうちスイッチSW1とノイズフィルタとの間に挿入されており、ダイオードブリッジDB2の一方の交流端子(〜端子)がSW1に接続され、他方の交流端子(〜端子)がノイズフィルタNFに接続されている。

【0027】

抵抗素子R1は、ダイオードブリッジDB2の交流端子間に接続されている。

電流制御回路21は、ダイオードブリッジDB2の直流端子(+端子,−端子)間に接続されている。

【0028】

電流制御回路21は、スイッチング素子Q1、容量素子C1(第2の容量素子)、抵抗素子(第2の抵抗素子)R2、抵抗素子(第3の抵抗素子)R3、およびダイオードD3から構成されている。

スイッチング素子Q1は、NチャネルMOSFETからなり、ドレイン端子がダイオードブリッジDB2の正側直流端子(+端子)に接続され、ソース端子がダイオードブリッジDB2の負側直流端子(−端子)に接続されている。

【0029】

容量素子C1は、スイッチング素子Q1のバイアス制御点、すなわちゲート端子とソース端子との間に接続された容量素子からなり、交流電源を用いて動作回路10で生成した直流電源により充電されて、スイッチング素子Q1のバイアス制御点におけるバイアス電圧(ゲート電圧)を上昇させる機能を有している。

抵抗素子R2は、容量素子C1に並列接続された抵抗素子である。

【0030】

抵抗素子R3は、直流電源により容量素子C1を充電する充電経路33に挿入された抵抗素子である。

ダイオードD3は、充電経路33に挿入されて、電流制御回路21から動作回路10への逆電流を阻止するダイオードである。

【0031】

[第1の実施の形態の動作]

次に、本実施の形態にかかる突入電流低減回路20の動作について説明する。

まず、図2を参照して、スイッチSW1,SW2の操作に応じた電気機器100への電源投入時、SW1側のV1電圧がSW2側の電圧V2より高い交流電源が交流源EからスイッチSW1,SW2を介して突入電流低減回路20へ印加された場合について説明する。図2は、突入電流低減回路の動作(V1>V2)を示す説明図である。なお、動作開始時において、容量素子C0,C1は放電されているものとする。また、図2において、ノイズフィルタNFは省略されている。

【0032】

スイッチSW1,SW2が短絡して、交流源Eからの入力電圧VinがVin=V1−V2=0から上昇し始めると、まずノイズフィルタNFの容量素子Cへ高周波の突入電流が流れようとし、その後、電力変換回路11の容量素子C0へ低周波の突入電流が流れようとする。

このとき、まず交流源Eから、供給経路31上のスイッチSW1、抵抗素子R1およびダイオードD11を介して、容量素子C0の充電が始まる。

【0033】

電源投入当初において、容量素子C1は抵抗素子R2により放電されており、スイッチング素子Q1のバイアス電圧(バイアス電圧)VGSもゼロなので、スイッチング素子Q1はカットオフされている。

これにより、電源投入当初の充電電流は、供給経路31上のスイッチSW1から抵抗素子R1およびダイオードD11を介して容量素子C0へ流れ込み、供給経路32上のダイオードD12を介してスイッチSW2へ戻る。このため、電源投入当初、最初に発生する一次突入電流は、抵抗素子R1により低減され、その後の充電継続に応じて、抵抗素子R1を流れる充電電流により容量素子C0が徐々に充電される。

【0034】

この後、容量素子C0の充電が進むにつれて、スイッチSW2から見た容量素子C0の正側端子の電位VCが上昇し、充電経路33上のダイオードD3および抵抗素子R3を介して容量素子C1が徐々に充電される。

これにより、電源投入当初には電位VCと同電位であったスイッチング素子Q1のソース電位VSに比較して、電位VCが十分高くなり、バイアス電圧VGSが上昇して、スイッチング素子Q1がターンオンする。

【0035】

このため、抵抗素子R1を迂回する供給経路34、すなわちダイオードD21、スイッチング素子Q1、およびダイオードD22からなる新たな供給経路が形成され、この供給経路34を介して容量素子C0の充電が開始される。

この供給経路34は、抵抗素子R1を持つ供給経路31に比較して抵抗値がほとんどゼロであるため、スイッチング素子Q1のターンオン時に、より大きな充電電流、すなわち二次突入電流が容量素子C0へ流れ込む。

【0036】

しかし、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1は、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされる。これにより、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1がターンオンするため、スイッチング素子Q1のターンオン時における二次突入電流が低減される。

【0037】

このようにして、V1>V2の場合、電気機器100への電源投入時における最初の一次突入電流、およびスイッチング素子Q1のターンオン時における二次突入電流が、それぞれ低減されることになる。

【0038】

次に、図3を参照して、スイッチSW1,SW2の操作に応じた電気機器100への電源投入時、SW1側のV1電圧がSW2側の電圧V2より低い交流電源が交流源EからスイッチSW1,SW2を介して突入電流低減回路20へ印加された場合について説明する。図3は、突入電流低減回路の動作(V1<V2)を示す説明図である。なお、動作開始時において、容量素子C0,C1は放電されているものとする。また、図3において、ノイズフィルタNFは省略されている。

【0039】

スイッチSW1,SW2が短絡して、交流源Eからの入力電圧VinがVin=V1−V2=0から上昇し始めると、まずノイズフィルタNFの容量素子Cへ高周波の突入電流が流れようとし、その後、電力変換回路11の容量素子C0へ低周波の突入電流が流れようとする。

このとき、まず交流源Eから、供給経路32上のスイッチSW2を介して、容量素子C0の充電が始まる。

【0040】

電源投入当初において、容量素子C1は抵抗素子R2により放電されており、スイッチング素子Q1のバイアス電圧(バイアス電圧)VGSもゼロなので、スイッチング素子Q1はカットオフされている。

これにより、電源投入当初の充電電流は、スイッチSW2から供給経路32上のダイオードD13を介して容量素子C0へ流れ込み、供給経路31上のダイオードD14、および抵抗素子R1を介してスイッチSW1へ戻る。このため、電源投入当初、最初に発生する一次突入電流は、抵抗素子R1により低減され、その後の充電継続に応じて、抵抗素子R1を流れる充電電流により容量素子C0が徐々に充電される。

【0041】

この後、容量素子C0の充電が進むにつれて、スイッチSW1から見た容量素子C0の正側端子の電位VCが上昇し、充電経路33上のダイオードD3および抵抗素子R3を介して容量素子C1が徐々に充電される。

これにより、電源投入当初には電位VCと同電位であったスイッチング素子Q1のソース電位VSに比較して、電位VCが十分高くなり、バイアス電圧VGSが上昇して、スイッチング素子Q1がターンオンする。

【0042】

このため、抵抗素子R1を迂回する供給経路34、すなわちダイオードD23、スイッチング素子Q1、およびダイオードD24からなる新たな供給経路が形成され、この供給経路34を介して容量素子C0の充電が開始される。

この供給経路34は、抵抗素子R1を持つ供給経路31に比較して抵抗値がほとんどゼロであるため、スイッチング素子Q1のターンオン時に、より大きな充電電流、すなわち二次突入電流が容量素子C0へ流れ込む。

【0043】

しかし、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1は、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされる。これにより、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1がターンオンするため、スイッチング素子Q1のターンオン時における二次突入電流が低減される。

【0044】

このようにして、V1<V2の場合にも、電気機器100への電源投入時における最初の一次突入電流、およびスイッチング素子Q1のターンオン時における二次突入電流が、それぞれ低減されることになる。

【0045】

図4は、従来の突入電流低減回路の動作を示す信号波形図である。ここでは、前述の図8に示した従来の突入電流低減回路20における、容量素子C0の両端電圧、スイッチング素子Q51のバイアス電圧、および交流源E(200V/50Hz)からの充電電流に関する信号波形がそれぞれ示されている。横軸は、1div当たり100msのスケールであり、交流電源が時刻T0から時刻T1までの100msにわたり瞬断されている。この際、容量素子C51は22μFであり、抵抗素子R52は10kΩであり、時定数は220msである。

【0046】

この図4では、時刻T0での交流電源の遮断に応じて、バイアス電圧が低下し始めるものの、その低下は緩やかであり、時刻T1においてもバイアス電圧が高いままである。これは、容量素子C51と抵抗素子R52の時定数が220msと、瞬断時間100msの2倍程度と大きいため、時刻T1になっても容量素子C51の電荷が放電しきらないからである。このため、時刻T1の電源再投入時において、スイッチング素子Q51が完全にカットオフされないまま、電源が再投入されたため、充電電流には計測画面読みで約2.9Aの大きさでパルス状の一次突入電流が発生したものと考えられる。

【0047】

図5は、本実施の形態にかかる突入電流低減回路の動作を示す信号波形図である。ここでは、前述の図1に示した本実施の形態にかかる突入電流低減回路20における、容量素子C0の両端電圧、スイッチング素子Q1のバイアス電圧、および交流源E(200V/50Hz)からの充電電流に関する信号波形がそれぞれ示されている。横軸は、1div当たり100msのスケールであり、交流電源が時刻T0から時刻T1までの100msにわたり瞬断されている。この際、容量素子C1は4.7μFであり、抵抗素子R2は8.2kΩであり、時定数は39msである。

【0048】

この図5では、時刻T0での交流電源の遮断に応じて、図4に比較してバイアス電圧が急速に低下し始め、時刻T1においては容量素子C1の電荷が放電してバイアス電圧がほぼゼロの状態である。これは、容量素子C1と抵抗素子R2の時定数が39msと、瞬断時間100msの1/2以下と小さいため、時刻T1において容量素子C1の電荷が放電しているからである。このため、時刻T1の電源再投入時において、スイッチング素子Q1がほぼカットオフされた状態で、電源が再投入されたため、充電電流に発生したパルス状の一次突入電流は、抵抗素子R1により、計測画面読みで図4に比較して約1/3の約1.1Aまで低減されていることが分かる。

【0049】

図6は、交流電源の瞬断時間の変化に対する突入電流特性を示すグラフである。ここでは、横軸が交流電源の瞬断時間を示し、縦軸が突入電流を示している。図6において、特性IR0は、前述した従来の突入電流低減回路による突入電流特性であり、容量素子C1と抵抗素子R2の時定数は図4と同様の220msである。特性IR1は、本実施の形態にかかる突入電流低減回路による突入電流特性であり、容量素子C1と抵抗素子R2の時定数は図5と同様の39msである。

例えば、電気機器100の交流電源の瞬断に対する許容最小瞬断時間が100msである場合、特性IR0では計測値約15.5Aの突入電流が発生するが、特性IR1では特性IR0の1/10の約1.5Aまで突入電流まで大幅に低減できていることがわかる。

【0050】

[第1の実施の形態の効果]

このように、本実施の形態では、交流源Eからの交流電源を動作回路へ供給する供給経路31に対して、動作回路10と直列に挿入されたダイオードブリッジDB2と、ダイオードブリッジDB2の交流端子間に接続された抵抗素子R1と、ダイオードブリッジDB2の直流端子間に接続された電流制御回路21とを備え、この電流制御回路21に、直流端子間に接続されたスイッチング素子Q1と、スイッチング素子Q1のバイアス制御点に接続されるとともに、交流電源を用いて動作回路10で生成して第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる容量素子C1と、容量素子C1に並列接続された抵抗素子R2と、直流電源により容量素子C1を充電する充電経路に挿入された抵抗素子R3と、充電経路に挿入されて電流制御回路21から動作回路10への逆電流を阻止するダイオードD3とを備えている。

【0051】

これにより、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1が、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされることになる。したがって、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1をターンオンさせることができ、スイッチング素子Q1のターンオン時における二次突入電流を低減できる。

【0052】

このため、スイッチング素子Q1のターンオン時における二次突入電流を低減するために、容量素子C1と抵抗素子R2の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断時間に見合った短い時定数を設定することができる。よって、本実施の形態によれば、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【0053】

また、本実施の形態では、スイッチング素子Q1として、NMOSFETを用いた場合を例として説明したが、代わりにNPNバイポーラトランジスタを用いてもよい。また、PMOSFETやPNPバイポーラトランジスタを用いてもよい。さらには、スイッチング素子Q1として、フォトカプラとFETが合体した光MOS−FET(フォトリレー)を用いてもよい。また、スイッチSW1,SW2は両切スイッチである必要はなく、スイッチSW1,SW2のいずれか一方からなる片切スイッチであってもよい。

【0054】

[第2の実施の形態]

次に、図7を参照して、本発明の第2の実施の形態にかかる突入電流低減回路20について説明する。図7は、第2の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図であり、前述した図1と同じまたは同等部分には同一符号を付してある。

【0055】

第1の実施の形態では、動作回路10において、電力変換回路11がインバータなどの発振回路11Aからなり、負荷回路12が蛍光管12Aからなる場合を例として説明した。本実施の形態では、動作回路10において、電力変換回路11がコンバータなどの電圧変換回路11Bからなり、負荷回路12がLEDモジュール12Bからなる場合を例として説明する。

【0056】

本実施の形態において、電力変換回路11は、交流源Eから供給された交流電源を直流電源に一旦変換した後、電圧変換回路11Bにより負荷回路12で用いる直流電源に再変換して出力する機能を有している。

負荷回路12は、電力変換回路11からの直流電源により動作する機能を有している。

【0057】

電圧変換回路11Bは、共振型DC−DC変換回路などのコンバータからなり、ダイオードブリッジDB1で整流されて直流入力端子(+端子,−端子)に入力された直流電源を、負荷回路12で用いる電圧の二次直流電源に再変換(昇圧または降圧)して、直流出力端子(+端子,−端子)から出力する機能と有している。

容量素子C0は、電圧変換回路11Bの直流出力端子(+端子,−端子)間に接続された大容量の電解コンデンサからなり、電圧変換回路11Bから出力された二次直流電源を平滑化する機能を有している。

【0058】

LEDモジュール12Bは、複数のLEDが配列接続された回路モジュールからなり、電圧変換回路11Bの直流出力端子間に接続されて、発振回路11Aから出力された二次直流電源により各LEDを点灯する機能を有している。

【0059】

本実施の形態の動作回路10における、これら以外の構成については、図1と同様であり、ここでの詳細な説明は省略する。

また、本実施の形態にかかる突入電流低減回路20の構成は、図1と同様である。特に、電力変換回路11の容量素子C0が電圧変換回路11Bの出力側に設けられているものの、第1の実施の形態と同様にして、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1が、容量素子C0の正側端子の電位VCにより充電経路33を介して充電される。

【0060】

これにより、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされることになる。したがって、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1をターンオンさせることができ、スイッチング素子Q1のターンオン時における二次突入電流を低減できる。

【0061】

このため、スイッチング素子Q1のターンオン時における二次突入電流を低減するために、容量素子C1と抵抗素子R2の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断に見合った短い時定数を設定することができる。よって、本実施の形態によれば、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【0062】

[実施の形態の拡張]

以上、実施形態を参照して本発明を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明のスコープ内で当業者が理解しうる様々な変更をすることができる。

【符号の説明】

【0063】

100…電気機器、10…動作回路、11A…発振回路、11B…電力変換回路、12…負荷回路、12A…蛍光管、12B…LEDモジュール、20…突入電流低減回路、21…電流制御回路、31,32,34…供給経路、33…充電経路、E…交流源、SW1,SW2…スイッチ、NF…ノイズフィルタ、DB1…ダイオードブリッジ、D11,D12,D13,D14…ダイオード、C0…容量素子(第1の容量素子)、DB2…ダイオードブリッジ、D21,D22,D23,D24…ダイオード、R1…抵抗素子(第1の抵抗素子)、R2…抵抗素子(第2の抵抗素子)、R3…抵抗素子(第3の抵抗素子)、C1…容量素子(第2の容量素子)、Q1…スイッチング素子、D3…ダイオード。

【技術分野】

【0001】

本発明は、電源供給制御技術に関し、特に電源から負荷回路への突入電流を低減する突入電流低減技術に関する。

【背景技術】

【0002】

インバータやコンバータなどの電力変換回路は、高い周波数でACまたはDCの入力電源をスイッチングして、所望の電圧を持つACまたはDCの出力電源へ変換する回路である。このような電力変換回路では、AC電源から得られたDC電源に含まれる変動成分を平滑化するため、大容量の容量素子が用いられている。

したがって、電源投入時に、この容量素子を充電するよう突入電流が流入する。この突入電流は、急峻で振幅も大きいため、不要電磁波を放出し、周囲の電子機器内にノイズ電流を誘発させる原因にもなる。

【0003】

従来、このような突入電流を低減させる突入電流低減技術として、スイッチング素子を用いて突入電流を低減する方法が提案されている(例えば、特許文献1など参照)。図8は、従来の突入電流低減回路を示す回路図である。

図8の突入電流低減回路50では、突入電流が流れる供給経路上にNチャネルMOSFETからなるスイッチング素子Q51を配置し、動作回路10に設けられている大容量の容量素子C0の電源投入当初はスイッチング素子Q51をオフしておき、ある程度まで容量素子C0を充電した後、スイッチング素子Q51をターンオンすることにより、電源投入時における容量素子C0への突入電流を低減している。

【先行技術文献】

【特許文献】

【0004】

【特許文献1】特許第3990421号公報

【発明の概要】

【発明が解決しようとする課題】

【0005】

突入電流は、電気機器の利用者が意図的に電源を投入する場合だけでなく、交流電源が停電から復帰する場合にも流れる。停電から復帰までの時間が短い瞬時停電の場合も同様である。また、照明機器の場合、利用者が交流電源の電源スイッチを一旦オフして消灯した後、思い直して直ぐにスイッチをオンして点灯させる場合がある。さらに、人感センサにより照明機器の点灯/消灯を制御する場合にも、利用者の動きに応じて、一旦オフして消灯した後、直ぐにオンして点灯することがある。したがって、このような交流電源の瞬断が行われた場合でも、突入電流低減回路において、動作回路への突入電流を低減させる必要がある。

【0006】

前述した従来技術では、電源投入当初において、動作回路10に設けられている大容量の容量素子C0に充電電流を供給する供給経路が、スイッチング素子Q51のターンオンを遅延させて突入電流低減動作を制御する時定数回路で兼用されている。

具体的には、スイッチング素子Q51のドレイン端子とゲート端子との間に接続された抵抗素子R51と、スイッチング素子Q51のゲート端子とソース端子との間に接続された抵抗素子R52とが供給経路を構成しており、抵抗素子R52とこれに並列接続された容量素子C1とが時定数回路を構成している。

【0007】

さて、電源投入当初においては、スイッチング素子Q51のドレイン端子とソース端子との間の端子間抵抗がほぼ無限大であり、その後、時定数回路によりバイアス電圧(ゲート電圧)が徐々に上昇してスイッチング素子Q51がターンオンし、端子間抵抗がほぼゼロとなる。この際、スイッチング素子Q51がターンオンするまでは抵抗素子R1,R2の供給経路を介して容量素子C0が徐々に充電され、スイッチング素子Q51がターンオンした後は、スイッチング素子Q51を介して容量素子C0が一気に充電される。

【0008】

したがって、電源投入時に供給経路を介して最初に発生する一次突入電流の後に、スイッチング素子Q51がターンオンするタイミングで二次突入電流が発生する。この二次突入電流の大きさは、スイッチング素子Q51のターンオン前後における容量素子C0の電位差に起因し、電位差が大きいほど二次突入電流は大きくなり、不要電磁波の放出原因になる。

【0009】

ここで、交流電源の瞬断に対する応答性を考慮した場合、時定数回路の容量素子C1に充電されている電荷が電源の再投入時に残っていると、スイッチング素子Q51がオン状態のまま電源が再投入されることになり、一次突入電流を低減できなくなる。このため、容量素子C1の電荷をすばやく放電して、交流電源の瞬断に対する応答性を確保するためには、時定数回路の時定数を小さいほうが望ましいことになる。

【0010】

しかしながら、時定数を小さくすると、電源の投入に応じて抵抗素子R51を介して容量素子C51が充電されてバイアス電圧がすぐに上昇するため、容量素子C0が十分充電されていない状態で、早めにスイッチング素子Q51がターンオンすることになる。このため、スイッチング素子Q51のターンオン前後における容量素子C0の電位差が大きくなり、二次突入電流が大きくなる。

したがって、前述した従来技術によれば、二次突入電流の低減を実現するためには時定数回路の時定数を小さくできないため、交流電源の瞬断に対して良好な応答性を得ることができないという問題点があった。

【0011】

本発明はこのような課題を解決するためのものであり、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることができる突入電流低減技術を提供することを目的としている。

【課題を解決するための手段】

【0012】

このような目的を達成するために、本発明にかかる突入電流低減回路は、交流源からの交流電源を動作回路へ供給する供給経路に対して、動作回路と直列に挿入されたダイオードブリッジと、ダイオードブリッジの交流端子間に接続された第1の抵抗素子と、ダイオードブリッジの直流端子間に接続された電流制御回路とを備え、電流制御回路は、直流端子間に接続されたスイッチング素子と、スイッチング素子のバイアス制御点に接続されるとともに、交流電源を用いて動作回路で生成されて第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる第2の容量素子と、容量素子に並列接続された第2の抵抗素子と、直流電源により第2の容量素子を充電する充電経路に挿入された第3の抵抗素子と、充電経路に挿入されて電流制御回路から動作回路への逆電流を阻止するダイオードとを備えるものである。

また、本発明にかかる電気機器は、前述した突入電流低減回路を備える電気機器である。

【発明の効果】

【0013】

本発明によれば、突入電流低減回路に設けられたスイッチング素子のバイアス供給点に接続されている第2の容量素子が、交流電源を用いて動作回路で生成して第1の容量素子に充電された直流電源により充電経路を介して充電されるため、第1の容量素子がある程度充電された状態となってから、スイッチング素子がターンオンされることになる。したがって、スイッチング素子のターンオン前後における第1の容量素子の電位差が小さくなってから、スイッチング素子をターンオンさせることができ、スイッチング素子のターンオン時における二次突入電流を低減できる。

【0014】

このため、スイッチング素子のターンオン時における二次突入電流を低減するために、第2の容量素子とこれに並列接続された第2の抵抗素子の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断時間に見合った短い時定数を設定することができる。よって、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【図面の簡単な説明】

【0015】

【図1】第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【図2】突入電流低減回路の動作(V1>V2)を示す説明図である。

【図3】突入電流低減回路の動作(V1<V2)を示す説明図である。

【図4】従来の突入電流低減回路の動作を示す信号波形図である。

【図5】本実施の形態にかかる突入電流低減回路の動作を示す信号波形図である。

【図6】交流電源の瞬断時間の変化に対する突入電流特性を示すグラフである。

【図7】第2の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【図8】従来の突入電流低減回路を示す回路図である。

【発明を実施するための形態】

【0016】

次に、本発明の実施の形態について図面を参照して説明する。

[第1の実施の形態]

まず、図1を参照して、本発明の第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器について説明する。図1は、第1の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図である。

【0017】

[電気機器]

電気機器100は、交流源Eとその両端に設けられたスイッチSW1,SW2とを含む交流回路に接続されて、交流源EからスイッチSW1,SW2を介して供給された単相の交流電源により動作する動作回路10を備えている。

図1の例では、動作回路10として、交流電源により蛍光管を点灯駆動する照明用動作回路が示されている。

【0018】

動作回路10には、主な回路構成として、電力変換回路11と負荷回路12が設けられている。

電力変換回路11は、交流源Eから供給された交流電源を直流電源に一旦変換した後、負荷回路12で用いる周波数の交流電源に再変換して出力する機能を有している。

負荷回路12は、電力変換回路11からの交流電源により動作する機能を有している。

【0019】

電力変換回路11には、主な回路として、ダイオードブリッジDB1、容量素子C0(第1の容量素子)、および発振回路11Aが設けられている。

ダイオードブリッジDB1は、ブリッジ接続された4つのダイオードD11,D12,D13,D14からなり、入力された交流電源を整流して直流電源に変換して出力する機能を有している。

【0020】

容量素子C0は、ダイオードブリッジDB1の直流出力端子(+端子,−端子)間に接続された大容量の電解コンデンサからなり、ダイオードブリッジDB1から出力された直流電源を平滑化する機能を有している。

発振回路11Aは、共振型DC−AC変換回路などのインバータからなり、直流入力端子(+端子,−端子)に入力された、容量素子C0で平滑化された直流電源を、負荷回路12で用いる周波数の二次交流電源に再変換して、交流出力端子(〜端子)から出力する機能を有している。

【0021】

負荷回路12には、主な回路として、蛍光管12Aが設けられている。

蛍光管12Aは、発振回路11Aの交流出力端子間に接続されて、発振回路11Aから出力された二次交流電源により点灯する機能を有している。

【0022】

これにより、動作回路10では、交流源Eから供給経路31,32を介して供給された交流電源が、電力変換回路11に入力されて、ダイオードブリッジDB1により直流電源に変換されて、容量素子C0で平滑化された後、発振回路11Aで二次交流電源に再変換されて負荷回路12へ出力され、この二次交流電源により負荷回路12の蛍光管12Aが点灯する。

【0023】

ノイズフィルタNFは、電源ライン用EMIフィルタなど、一般的なノイズフィルタからなり、動作回路10の入力側に設けられて、動作回路10の発振回路11Aで発生した高周波ノイズを除去する機能を有している。

このノイズフィルタNFは、交流源Eから動作回路10へ交流電源が供給される供給経路31,32上にそれぞれ挿入された2つのコイルL(ノーマルモードチョーク)と、これらコイルLの入力端子間および出力端子間にそれぞれ接続された2つの容量素子C(アクロスザライン容量素子)とから構成されている。

【0024】

[突入電流低減回路]

突入電流低減回路20は、交流源Eからの交流電源を動作回路10へ供給する供給経路に対して、動作回路10と直列に挿入されて、交流電流の供給開始時に動作回路10へ流れ込む突入電流を低減する回路である。図1の例では、交流源Eから動作回路10へ交流電源が供給される供給経路のうちスイッチSW1側の供給経路31において、スイッチSW1とノイズフィルタとの間に挿入されている。

【0025】

この突入電流低減回路20には、主な回路部として、ダイオードブリッジDB2、抵抗素子(第1の抵抗素子)R1、および電流制御回路21が設けられている。

【0026】

ダイオードブリッジDB2は、ブリッジ接続された4つのダイオードD21,D22,D23,D24からなり、動作回路10に交流電源を供給する供給経路に対して、動作回路10と直列に挿入されている。具体的には、スイッチSW1側の供給経路31のうちスイッチSW1とノイズフィルタとの間に挿入されており、ダイオードブリッジDB2の一方の交流端子(〜端子)がSW1に接続され、他方の交流端子(〜端子)がノイズフィルタNFに接続されている。

【0027】

抵抗素子R1は、ダイオードブリッジDB2の交流端子間に接続されている。

電流制御回路21は、ダイオードブリッジDB2の直流端子(+端子,−端子)間に接続されている。

【0028】

電流制御回路21は、スイッチング素子Q1、容量素子C1(第2の容量素子)、抵抗素子(第2の抵抗素子)R2、抵抗素子(第3の抵抗素子)R3、およびダイオードD3から構成されている。

スイッチング素子Q1は、NチャネルMOSFETからなり、ドレイン端子がダイオードブリッジDB2の正側直流端子(+端子)に接続され、ソース端子がダイオードブリッジDB2の負側直流端子(−端子)に接続されている。

【0029】

容量素子C1は、スイッチング素子Q1のバイアス制御点、すなわちゲート端子とソース端子との間に接続された容量素子からなり、交流電源を用いて動作回路10で生成した直流電源により充電されて、スイッチング素子Q1のバイアス制御点におけるバイアス電圧(ゲート電圧)を上昇させる機能を有している。

抵抗素子R2は、容量素子C1に並列接続された抵抗素子である。

【0030】

抵抗素子R3は、直流電源により容量素子C1を充電する充電経路33に挿入された抵抗素子である。

ダイオードD3は、充電経路33に挿入されて、電流制御回路21から動作回路10への逆電流を阻止するダイオードである。

【0031】

[第1の実施の形態の動作]

次に、本実施の形態にかかる突入電流低減回路20の動作について説明する。

まず、図2を参照して、スイッチSW1,SW2の操作に応じた電気機器100への電源投入時、SW1側のV1電圧がSW2側の電圧V2より高い交流電源が交流源EからスイッチSW1,SW2を介して突入電流低減回路20へ印加された場合について説明する。図2は、突入電流低減回路の動作(V1>V2)を示す説明図である。なお、動作開始時において、容量素子C0,C1は放電されているものとする。また、図2において、ノイズフィルタNFは省略されている。

【0032】

スイッチSW1,SW2が短絡して、交流源Eからの入力電圧VinがVin=V1−V2=0から上昇し始めると、まずノイズフィルタNFの容量素子Cへ高周波の突入電流が流れようとし、その後、電力変換回路11の容量素子C0へ低周波の突入電流が流れようとする。

このとき、まず交流源Eから、供給経路31上のスイッチSW1、抵抗素子R1およびダイオードD11を介して、容量素子C0の充電が始まる。

【0033】

電源投入当初において、容量素子C1は抵抗素子R2により放電されており、スイッチング素子Q1のバイアス電圧(バイアス電圧)VGSもゼロなので、スイッチング素子Q1はカットオフされている。

これにより、電源投入当初の充電電流は、供給経路31上のスイッチSW1から抵抗素子R1およびダイオードD11を介して容量素子C0へ流れ込み、供給経路32上のダイオードD12を介してスイッチSW2へ戻る。このため、電源投入当初、最初に発生する一次突入電流は、抵抗素子R1により低減され、その後の充電継続に応じて、抵抗素子R1を流れる充電電流により容量素子C0が徐々に充電される。

【0034】

この後、容量素子C0の充電が進むにつれて、スイッチSW2から見た容量素子C0の正側端子の電位VCが上昇し、充電経路33上のダイオードD3および抵抗素子R3を介して容量素子C1が徐々に充電される。

これにより、電源投入当初には電位VCと同電位であったスイッチング素子Q1のソース電位VSに比較して、電位VCが十分高くなり、バイアス電圧VGSが上昇して、スイッチング素子Q1がターンオンする。

【0035】

このため、抵抗素子R1を迂回する供給経路34、すなわちダイオードD21、スイッチング素子Q1、およびダイオードD22からなる新たな供給経路が形成され、この供給経路34を介して容量素子C0の充電が開始される。

この供給経路34は、抵抗素子R1を持つ供給経路31に比較して抵抗値がほとんどゼロであるため、スイッチング素子Q1のターンオン時に、より大きな充電電流、すなわち二次突入電流が容量素子C0へ流れ込む。

【0036】

しかし、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1は、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされる。これにより、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1がターンオンするため、スイッチング素子Q1のターンオン時における二次突入電流が低減される。

【0037】

このようにして、V1>V2の場合、電気機器100への電源投入時における最初の一次突入電流、およびスイッチング素子Q1のターンオン時における二次突入電流が、それぞれ低減されることになる。

【0038】

次に、図3を参照して、スイッチSW1,SW2の操作に応じた電気機器100への電源投入時、SW1側のV1電圧がSW2側の電圧V2より低い交流電源が交流源EからスイッチSW1,SW2を介して突入電流低減回路20へ印加された場合について説明する。図3は、突入電流低減回路の動作(V1<V2)を示す説明図である。なお、動作開始時において、容量素子C0,C1は放電されているものとする。また、図3において、ノイズフィルタNFは省略されている。

【0039】

スイッチSW1,SW2が短絡して、交流源Eからの入力電圧VinがVin=V1−V2=0から上昇し始めると、まずノイズフィルタNFの容量素子Cへ高周波の突入電流が流れようとし、その後、電力変換回路11の容量素子C0へ低周波の突入電流が流れようとする。

このとき、まず交流源Eから、供給経路32上のスイッチSW2を介して、容量素子C0の充電が始まる。

【0040】

電源投入当初において、容量素子C1は抵抗素子R2により放電されており、スイッチング素子Q1のバイアス電圧(バイアス電圧)VGSもゼロなので、スイッチング素子Q1はカットオフされている。

これにより、電源投入当初の充電電流は、スイッチSW2から供給経路32上のダイオードD13を介して容量素子C0へ流れ込み、供給経路31上のダイオードD14、および抵抗素子R1を介してスイッチSW1へ戻る。このため、電源投入当初、最初に発生する一次突入電流は、抵抗素子R1により低減され、その後の充電継続に応じて、抵抗素子R1を流れる充電電流により容量素子C0が徐々に充電される。

【0041】

この後、容量素子C0の充電が進むにつれて、スイッチSW1から見た容量素子C0の正側端子の電位VCが上昇し、充電経路33上のダイオードD3および抵抗素子R3を介して容量素子C1が徐々に充電される。

これにより、電源投入当初には電位VCと同電位であったスイッチング素子Q1のソース電位VSに比較して、電位VCが十分高くなり、バイアス電圧VGSが上昇して、スイッチング素子Q1がターンオンする。

【0042】

このため、抵抗素子R1を迂回する供給経路34、すなわちダイオードD23、スイッチング素子Q1、およびダイオードD24からなる新たな供給経路が形成され、この供給経路34を介して容量素子C0の充電が開始される。

この供給経路34は、抵抗素子R1を持つ供給経路31に比較して抵抗値がほとんどゼロであるため、スイッチング素子Q1のターンオン時に、より大きな充電電流、すなわち二次突入電流が容量素子C0へ流れ込む。

【0043】

しかし、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1は、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされる。これにより、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1がターンオンするため、スイッチング素子Q1のターンオン時における二次突入電流が低減される。

【0044】

このようにして、V1<V2の場合にも、電気機器100への電源投入時における最初の一次突入電流、およびスイッチング素子Q1のターンオン時における二次突入電流が、それぞれ低減されることになる。

【0045】

図4は、従来の突入電流低減回路の動作を示す信号波形図である。ここでは、前述の図8に示した従来の突入電流低減回路20における、容量素子C0の両端電圧、スイッチング素子Q51のバイアス電圧、および交流源E(200V/50Hz)からの充電電流に関する信号波形がそれぞれ示されている。横軸は、1div当たり100msのスケールであり、交流電源が時刻T0から時刻T1までの100msにわたり瞬断されている。この際、容量素子C51は22μFであり、抵抗素子R52は10kΩであり、時定数は220msである。

【0046】

この図4では、時刻T0での交流電源の遮断に応じて、バイアス電圧が低下し始めるものの、その低下は緩やかであり、時刻T1においてもバイアス電圧が高いままである。これは、容量素子C51と抵抗素子R52の時定数が220msと、瞬断時間100msの2倍程度と大きいため、時刻T1になっても容量素子C51の電荷が放電しきらないからである。このため、時刻T1の電源再投入時において、スイッチング素子Q51が完全にカットオフされないまま、電源が再投入されたため、充電電流には計測画面読みで約2.9Aの大きさでパルス状の一次突入電流が発生したものと考えられる。

【0047】

図5は、本実施の形態にかかる突入電流低減回路の動作を示す信号波形図である。ここでは、前述の図1に示した本実施の形態にかかる突入電流低減回路20における、容量素子C0の両端電圧、スイッチング素子Q1のバイアス電圧、および交流源E(200V/50Hz)からの充電電流に関する信号波形がそれぞれ示されている。横軸は、1div当たり100msのスケールであり、交流電源が時刻T0から時刻T1までの100msにわたり瞬断されている。この際、容量素子C1は4.7μFであり、抵抗素子R2は8.2kΩであり、時定数は39msである。

【0048】

この図5では、時刻T0での交流電源の遮断に応じて、図4に比較してバイアス電圧が急速に低下し始め、時刻T1においては容量素子C1の電荷が放電してバイアス電圧がほぼゼロの状態である。これは、容量素子C1と抵抗素子R2の時定数が39msと、瞬断時間100msの1/2以下と小さいため、時刻T1において容量素子C1の電荷が放電しているからである。このため、時刻T1の電源再投入時において、スイッチング素子Q1がほぼカットオフされた状態で、電源が再投入されたため、充電電流に発生したパルス状の一次突入電流は、抵抗素子R1により、計測画面読みで図4に比較して約1/3の約1.1Aまで低減されていることが分かる。

【0049】

図6は、交流電源の瞬断時間の変化に対する突入電流特性を示すグラフである。ここでは、横軸が交流電源の瞬断時間を示し、縦軸が突入電流を示している。図6において、特性IR0は、前述した従来の突入電流低減回路による突入電流特性であり、容量素子C1と抵抗素子R2の時定数は図4と同様の220msである。特性IR1は、本実施の形態にかかる突入電流低減回路による突入電流特性であり、容量素子C1と抵抗素子R2の時定数は図5と同様の39msである。

例えば、電気機器100の交流電源の瞬断に対する許容最小瞬断時間が100msである場合、特性IR0では計測値約15.5Aの突入電流が発生するが、特性IR1では特性IR0の1/10の約1.5Aまで突入電流まで大幅に低減できていることがわかる。

【0050】

[第1の実施の形態の効果]

このように、本実施の形態では、交流源Eからの交流電源を動作回路へ供給する供給経路31に対して、動作回路10と直列に挿入されたダイオードブリッジDB2と、ダイオードブリッジDB2の交流端子間に接続された抵抗素子R1と、ダイオードブリッジDB2の直流端子間に接続された電流制御回路21とを備え、この電流制御回路21に、直流端子間に接続されたスイッチング素子Q1と、スイッチング素子Q1のバイアス制御点に接続されるとともに、交流電源を用いて動作回路10で生成して第1の容量素子に充電された直流電源により充電されてバイアス制御点におけるバイアス電圧を上昇させる容量素子C1と、容量素子C1に並列接続された抵抗素子R2と、直流電源により容量素子C1を充電する充電経路に挿入された抵抗素子R3と、充電経路に挿入されて電流制御回路21から動作回路10への逆電流を阻止するダイオードD3とを備えている。

【0051】

これにより、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1が、容量素子C0の正側端子の電位VCにより充電経路33を介して充電されるため、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされることになる。したがって、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1をターンオンさせることができ、スイッチング素子Q1のターンオン時における二次突入電流を低減できる。

【0052】

このため、スイッチング素子Q1のターンオン時における二次突入電流を低減するために、容量素子C1と抵抗素子R2の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断時間に見合った短い時定数を設定することができる。よって、本実施の形態によれば、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【0053】

また、本実施の形態では、スイッチング素子Q1として、NMOSFETを用いた場合を例として説明したが、代わりにNPNバイポーラトランジスタを用いてもよい。また、PMOSFETやPNPバイポーラトランジスタを用いてもよい。さらには、スイッチング素子Q1として、フォトカプラとFETが合体した光MOS−FET(フォトリレー)を用いてもよい。また、スイッチSW1,SW2は両切スイッチである必要はなく、スイッチSW1,SW2のいずれか一方からなる片切スイッチであってもよい。

【0054】

[第2の実施の形態]

次に、図7を参照して、本発明の第2の実施の形態にかかる突入電流低減回路20について説明する。図7は、第2の実施の形態にかかる突入電流低減回路、およびこの突入電流低減回路を備える電気機器の構成を示す回路図であり、前述した図1と同じまたは同等部分には同一符号を付してある。

【0055】

第1の実施の形態では、動作回路10において、電力変換回路11がインバータなどの発振回路11Aからなり、負荷回路12が蛍光管12Aからなる場合を例として説明した。本実施の形態では、動作回路10において、電力変換回路11がコンバータなどの電圧変換回路11Bからなり、負荷回路12がLEDモジュール12Bからなる場合を例として説明する。

【0056】

本実施の形態において、電力変換回路11は、交流源Eから供給された交流電源を直流電源に一旦変換した後、電圧変換回路11Bにより負荷回路12で用いる直流電源に再変換して出力する機能を有している。

負荷回路12は、電力変換回路11からの直流電源により動作する機能を有している。

【0057】

電圧変換回路11Bは、共振型DC−DC変換回路などのコンバータからなり、ダイオードブリッジDB1で整流されて直流入力端子(+端子,−端子)に入力された直流電源を、負荷回路12で用いる電圧の二次直流電源に再変換(昇圧または降圧)して、直流出力端子(+端子,−端子)から出力する機能と有している。

容量素子C0は、電圧変換回路11Bの直流出力端子(+端子,−端子)間に接続された大容量の電解コンデンサからなり、電圧変換回路11Bから出力された二次直流電源を平滑化する機能を有している。

【0058】

LEDモジュール12Bは、複数のLEDが配列接続された回路モジュールからなり、電圧変換回路11Bの直流出力端子間に接続されて、発振回路11Aから出力された二次直流電源により各LEDを点灯する機能を有している。

【0059】

本実施の形態の動作回路10における、これら以外の構成については、図1と同様であり、ここでの詳細な説明は省略する。

また、本実施の形態にかかる突入電流低減回路20の構成は、図1と同様である。特に、電力変換回路11の容量素子C0が電圧変換回路11Bの出力側に設けられているものの、第1の実施の形態と同様にして、スイッチング素子Q1のバイアス供給点に接続されている容量素子C1が、容量素子C0の正側端子の電位VCにより充電経路33を介して充電される。

【0060】

これにより、容量素子C0がある程度充電された状態となってから、スイッチング素子Q1がターンオンされることになる。したがって、スイッチング素子Q1のターンオン前後における容量素子C0の電位差が小さくなってから、スイッチング素子Q1をターンオンさせることができ、スイッチング素子Q1のターンオン時における二次突入電流を低減できる。

【0061】

このため、スイッチング素子Q1のターンオン時における二次突入電流を低減するために、容量素子C1と抵抗素子R2の時定数をある程度長く設定する必要がなくなることから、交流電源の瞬断に見合った短い時定数を設定することができる。よって、本実施の形態によれば、二次突入電流を低減しつつ、交流電源の瞬断に対して良好な応答性を得ることが可能となる。

【0062】

[実施の形態の拡張]

以上、実施形態を参照して本発明を説明したが、本発明は上記実施形態に限定されるものではない。本発明の構成や詳細には、本発明のスコープ内で当業者が理解しうる様々な変更をすることができる。

【符号の説明】

【0063】

100…電気機器、10…動作回路、11A…発振回路、11B…電力変換回路、12…負荷回路、12A…蛍光管、12B…LEDモジュール、20…突入電流低減回路、21…電流制御回路、31,32,34…供給経路、33…充電経路、E…交流源、SW1,SW2…スイッチ、NF…ノイズフィルタ、DB1…ダイオードブリッジ、D11,D12,D13,D14…ダイオード、C0…容量素子(第1の容量素子)、DB2…ダイオードブリッジ、D21,D22,D23,D24…ダイオード、R1…抵抗素子(第1の抵抗素子)、R2…抵抗素子(第2の抵抗素子)、R3…抵抗素子(第3の抵抗素子)、C1…容量素子(第2の容量素子)、Q1…スイッチング素子、D3…ダイオード。

【特許請求の範囲】

【請求項1】

交流源からの交流電源を動作回路へ供給する供給経路に対して、前記動作回路と直列に挿入されたダイオードブリッジと、

前記ダイオードブリッジの交流端子間に接続された第1の抵抗素子と、

前記ダイオードブリッジの直流端子間に接続された電流制御回路と

を備え、

前記電流制御回路は、前記直流端子間に接続されたスイッチング素子と、前記スイッチング素子のバイアス制御点に接続されるとともに、前記交流電源を用いて前記動作回路で生成されて第1の容量素子に充電された直流電源により充電されて前記バイアス制御点におけるバイアス電圧を上昇させる第2の容量素子と、前記容量素子に並列接続された第2の抵抗素子と、前記直流電源により前記第2の容量素子を充電する充電経路に挿入された第3の抵抗素子と、前記充電経路に挿入されて前記電流制御回路から前記動作回路への逆電流を阻止するダイオードとを備える

ことを特徴とする突入電流低減回路。

【請求項2】

請求項1に記載の突入電流低減回路を備える電気機器。

【請求項1】

交流源からの交流電源を動作回路へ供給する供給経路に対して、前記動作回路と直列に挿入されたダイオードブリッジと、

前記ダイオードブリッジの交流端子間に接続された第1の抵抗素子と、

前記ダイオードブリッジの直流端子間に接続された電流制御回路と

を備え、

前記電流制御回路は、前記直流端子間に接続されたスイッチング素子と、前記スイッチング素子のバイアス制御点に接続されるとともに、前記交流電源を用いて前記動作回路で生成されて第1の容量素子に充電された直流電源により充電されて前記バイアス制御点におけるバイアス電圧を上昇させる第2の容量素子と、前記容量素子に並列接続された第2の抵抗素子と、前記直流電源により前記第2の容量素子を充電する充電経路に挿入された第3の抵抗素子と、前記充電経路に挿入されて前記電流制御回路から前記動作回路への逆電流を阻止するダイオードとを備える

ことを特徴とする突入電流低減回路。

【請求項2】

請求項1に記載の突入電流低減回路を備える電気機器。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2012−113498(P2012−113498A)

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願番号】特願2010−261581(P2010−261581)

【出願日】平成22年11月24日(2010.11.24)

【出願人】(000102739)エヌ・ティ・ティ・アドバンステクノロジ株式会社 (265)

【出願人】(590004648)株式会社共進電機製作所 (7)

【Fターム(参考)】

【公開日】平成24年6月14日(2012.6.14)

【国際特許分類】

【出願日】平成22年11月24日(2010.11.24)

【出願人】(000102739)エヌ・ティ・ティ・アドバンステクノロジ株式会社 (265)

【出願人】(590004648)株式会社共進電機製作所 (7)

【Fターム(参考)】

[ Back to top ]