系統連系インバータ装置

【課題】スイッチングノイズを低減し、系統連系インバータ装置の小型・軽量化を図る。

【解決手段】コントローラ7は、パルス幅変調信号の変調度がスイッチングノイズを最小にする最適変調度となるような振幅の変調波を生成する変調波生成部7dとその変調波を用いてパルス幅変調信号を生成するPWM信号生成部7eを備える。変調波生成7dは、変調波テーブル7aから最適変調度となる振幅の変調波の波形データを読み出し、その波形データの位相を力率調整部7bで算出した位相(無効電力を制御目標に追従させるための位相)を用いて補正することにより変調波を生成する。そして、PWM信号生成部7eがその変調波のレベルと所定の三角波のレベルを比較してPWM信号を生成する。PWM信号の変調度が最適変調度に固定されるので、スイッチングノイズが抑制される。

【解決手段】コントローラ7は、パルス幅変調信号の変調度がスイッチングノイズを最小にする最適変調度となるような振幅の変調波を生成する変調波生成部7dとその変調波を用いてパルス幅変調信号を生成するPWM信号生成部7eを備える。変調波生成7dは、変調波テーブル7aから最適変調度となる振幅の変調波の波形データを読み出し、その波形データの位相を力率調整部7bで算出した位相(無効電力を制御目標に追従させるための位相)を用いて補正することにより変調波を生成する。そして、PWM信号生成部7eがその変調波のレベルと所定の三角波のレベルを比較してPWM信号を生成する。PWM信号の変調度が最適変調度に固定されるので、スイッチングノイズが抑制される。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、燃料電池や太陽電池などの直流電源から出力される直流電力を交流電力に逆変換し、その交流電力を商用電力系統に供給する系統連系インバータ装置に関する。

【背景技術】

【0002】

系統連系インバータ装置の構成要素には直流電源から出力される直流電力を交流電力に逆変換する電力逆変換回路(インバータ)とその電力逆変換回路から出力される交流信号(交流電圧信号と交流電流信号)に含まれるスイッチングノイズを除去するフィルタ回路とが含まれる。

【0003】

フィルタ回路の容量は、インバータから出力される交流信号に含まれるスイッチングノイズのレベル(交流信号に重畳されるリップルノイズの大きさ)が大きくなるのに応じて大きくなるので、インバータで生じるスイッチングノイズが大きければ、フィルタ回路のキャパシタやインダクタの回路要素が大型化する。

【0004】

フィルタ回路は、系統連系インバータ装置の小型化や低コスト化を阻害する主要な回路要素であるから、インバータで生じるスイッチングノイズのレベルを可及的に抑制してフィルタの容量を小さくすることが望ましい。

【0005】

図17は、変調度M=1のPWM(Pulse Width Modulation)信号で三相インバータを動作させた時の三相インバータの出力電圧(線間電圧)をFFT(First Fourier Transform)解析したスペクラム分布の一例を示す図である。なお、変調度Mは、三角波比較方式によるパルス幅変調では、M=(変調波の振幅のピーク値)/(搬送波の振幅のピーク値)である。

【0006】

図17は、図18に示す回路モデルで三相インバータINVに400[v]の直流電圧(以下、「バス電圧」という。)を入力し、変調度M=1のPWM信号を三相インバータINVに入力した場合の出力電圧に含まれる周波数成分をFFT解析したものである。

【0007】

なお、回路モデルではフィルタ回路は省略し、三相インバータINVに対する負荷を5Ωとしている。また、PWM信号は、特開2010−136567号公報に記載の変調波を4.8[kHz]の三角波(搬送波)とレベル比較して生成されるパルス信号である。同公報に記載の変調波は、1周期を均等に3つの区間I,II,IIIに分け、区間Iは、相電圧から一つ前の相電圧を差し引いて得られる線間電圧の波形を有し、区間Iに続く区間IIは、相電圧から一つ後の相電圧を差し引いて得られる線間電圧の波形を有し、区間IIに続く区間IIIは、ゼロレベルの波形を有する信号である。インバータINVから出力させるU,V,Wの各相の相電圧をvu,vv,vwとすると、例えば、U相の変調波vu’は、−π/6≦θ≦3π/6で線間電圧vuw=vu−vw、3π/6≦θ≦7π/6で線間電圧vuv=vu−vv、7π/6≦θ≦11π/6で0レベルの波形を有する信号である。

【0008】

図17に示すように、三相インバータINVから出力される線間電圧には基本波成分(変調波の周波数と同一の周波数成分:図17では60[Hz])と、パルス幅変調における搬送波の周波数fc(以下、「キャリア周波数fc」という。)及びその整数倍の周波数(n×fc)と同一の周波数におけるサイドバンドの周波数成分とが含まれる。基本波成分以外の成分がスイッチングノイズの成分であるが、最もレベルの高い成分(以下、「最大ノイズ成分」という。)は、キャリア周波数fc=4.8[kHz]のサイドバンド成分(点Nmax参照)である。

【0009】

図19は、PWM信号の変調度Mを変化させて図17に示すFFT解析を行い、各変調度Mにおける最大ノイズ成分のレベルをプロットしたものである。図19に示すように、スイッチングノイズの特性は、変調度Mが0.55付近で最大となり、0.878で極小点Pminを有する。

【0010】

系統連系インバータ装置は、インバータの出力電圧を電力系統の電圧(以下、「系統電圧」という。)よりも高くして出力電流を電力系統側に出力する(直流電源から供給される電力を電力系統側に出力する)制御を行う。インバータの出力電圧の振幅(ピーク値)を「Vinv」、搬送波の振幅(ピーク値)を「Vc」、変調波の振幅(ピーク値)を「Vs」とすると、変調度Mは、M=Vs/Vcで表わされ、インバータのバス電圧を「Vdc」、三角波比較方式によるパルス幅変調の電圧利用率などの係数を「k」とすると、Vinv=k×M×Vdcの関係がある。電力系統に連系されているときには、系統連系インバータ装置は、インバータの出力電圧Vinvを系統電圧対抗分(系統電圧Vgと同一の電圧)以上に制御するから、Vg≦k×M×Vdcとなる。従って、系統連系インバータ装置では、変調度Mは、(Vg/k×Vdc)≦M≦1の範囲で変動し、フルレンジで変動することはない。

【0011】

例えば、202v系の電力系統に連系させる場合、バス電圧Vdcを系統電圧が規定値よりも10%上昇した場合でもフルブリッジ回路で構成されるインバータから定格電力が出力できる電圧に設定するとすれば、そのバス電圧Vdcは、

Vdc=[(202×1.1)×√(2)×0.866]×1.1×2/√(3)

≒345.7 …(1)

となる。

【0012】

(1)式において、「202」は、系統電圧(電力系統の線間電圧)vgの実効値Vrmsである。系統電圧の実効値Vrmsを1.1倍しているのは、系統電圧が10%上昇した場合でも定格電力が出力できることを反映したものである。また、「√(2)」を掛ける処理は瞬時値に変換するための処理であり、「0.866」を掛ける処理は、変調波に三次高調波成分を加算した場合、電圧利用率が0.866に改善されることに基づく処理である。また、波括弧内の値を1.1倍しているのは、フィルタにおける電圧降下分と制御量分を加味した処理であり、「2」を掛ける処理は、フルブリッジ回路のインバータから出力される交流電圧の正負の振幅が入力電圧の振幅の2倍になることに基づく処理である。また、「√(3)」で割る処理は線間電圧を相電圧にするための処理である。なお、デッドタイムなどの影響は無視している。

【0013】

系統電圧vgのレベルが許容範囲(±10%)の下限値に低下したときに電力系統への連系を可能にするバス電圧Vdcを算出すると、この場合は、インバータの出力電圧vinvが系統電圧対抗分だけとなるから、(1)式でフィルタにおける電圧降下分の係数を除去し、系統電圧の変動分の係数を1.1から0.9に変更することにより、

Vdc=[(202×0.9)×√(2)×0.866]×2/√(3)

≒257.4 …(2)

となる。

【0014】

従って、202v系の電力系統に連系させる系統連系インバータ装置でバス電圧Vdcを「345.7[v]」に設定した場合、変調度Mの変動範囲の最小値は、

M=257.4/345.7≒0.745 …(3)

で求められ、変調度Mの変動範囲は0.745〜1.00となる。

【0015】

そして、系統連系インバータ装置に特開2010−136567号公報に記載の変調方式を用いた場合は、変調度Mは0.745〜1.00の範囲で変動するから、M=0.878でスイッチングノイズが最小になる特性を有する。

【0016】

図20は、従来の系統連系インバータ装置の基本的な構成の一例を示すブロック図である。

【0017】

図20に示す系統連系インバータ装置100は、直流電源として太陽電池102を用いたものであり、インバータ104の入力電圧Vdc(バス電圧Vdc)を所定のバス電圧基準値Vrefに安定化させるために太陽電池102とインバータ104の間にDC/DCコンバータ103が設けられている。

【0018】

インバータ104は、6個のスイッチング素子を2個ずつ直列に接続した3組の直列回路(以下、「アーム」という。)を太陽電池102から直流電力が供給される入力ラインに並列に接続した三相フルブリッジ回路で構成される電圧型のインバータ(図18の三相インバータINV参照)である。インバータ104は、コントローラ107から入力される6個のPWM信号で各アーム内の2個のスイッチング素子を交互にオン・オフ動作させてバス電圧VdcをU,V,Wの各相の交流電圧vu,vv,vwに変換する。なお、大文字の符号「V」は直流電圧を示し、小文字の符号「v」は交流電圧を示している。また、交流電圧vu,vv,vwの添え字の「u,v,w」は、それぞれ対応する相を示している。

【0019】

コントローラ107は、マイクロコンピュータで構成され、ディジタル演算処理によりPWM信号の生成処理を行う。コントローラ107は、U,V,Wの各相について、インバータ104の出力電圧の制御目標vuo,vvo,vwo(フィルタ105を通過した正弦波の交流電圧)を変調波として生成し、その制御目標vuo,vvo,vwoを搬送波である所定の三角波vtと比較することによりPWM信号を生成する。なお、コントローラ107は、所定の周期でPWM信号の生成処理を行うので、制御目標vuo,vvo,vwoと三角波vtの瞬時値を生成し、両瞬時値を比較してPWM信号の瞬時値(ハイレベル若しくはローレベル)を出力する。

【0020】

U相の制御目標vuoは、インバータ104の出力電流iuがインバータ104と電力系統101との間のインピーダンス(主としてフィルタ105と変圧器106のリアクトルによるインピーダンス。以下、「連系用リアクトル」という。)を流れることによる電圧降下分の電圧を系統電圧にベクトル合成した電圧の振幅に相当する。系統電圧は電力系統101により制御されるので、コントローラ107は、連系用リアクトルの電圧を制御することにより制御目標vuoを制御する。連系用リアクトルのインピーダンスはフィルタ105及び変圧器106の設計値として固定されるから、連系用リアクトルの電圧は、インバータ104の出力電流iuにより制御される。従って、コントローラ107は、実質的にインバータ104の出力電流iuを制御することによって制御目標vuoを制御する。V相,W相の制御目標vuoについても同様である。

【0021】

コントローラ107内のバス電圧指令値生成部107a、無効電力指令値生成部107b、無効電力算出部107c、uvw−dq変換部107d、PI補償部107e,107f,107g,107h、非干渉化部107i,107j、dq−uvw変換部107kは出力電圧の制御目標vuo,vvo,vwoを生成するための処理ブロックである。また、PWM信号生成部107mは、制御目標vuo,vvo,vwoと三角波vtを比較してPWM信号を生成するための処理ブロックである。なお、dq−uvw変換部107kの前段若しくは後段に系統電圧対抗分を加算する処理ブロックが設けられるが、図20ではその処理ブロックを省略している。

【0022】

コントローラ107は、dq回転座標系でインバータ104の出力電流の制御目標Ido,Iqoを生成する。すなわち、コントローラ107は、バス電圧指令値生成部107aでバス電圧基準値Vrefを設定し、そのバス電圧基準値Vrefに対する直流電圧計108で実測されるバス電圧Vdcの偏差ΔVdc=Vref−Vdcを求め、その偏差ΔVdcに所定のPI補償の演算をしてインバータ104の出力電流の制御基準のdq回転座標系におけるd軸成分Idrefを設定する。d軸成分Idrefの制御は、インバータ104のバス電圧Vdcを所定のバス電圧基準値Vrefに安定化するための制御である。

【0023】

また、コントローラ107は、無効電力指令値生成部107bで無効電力指令値Qo(力率1の運転時ではQo=0)を設定するとともに、交流電圧計109で実測されるインバータ104の出力電圧vu,vv,vw及び交流電流計110で実測されるインバータ104の出力電流iu,iv,iwを用いて無効電力演算部107cでインバータ104から出力される無効電力Qrを算出する。そして、コントローラ107は、無効電力指令値Qoに対する無効電力演算部107cの無効電力算出値Qrの偏差ΔQ=Qo−Qrを求め、その偏差ΔQに所定のPI補償の演算をしてインバータ104の出力電流の制御基準のdq回転座標系におけるq軸成分Iqrefを設定する。q軸成分Iqrefの制御は、インバータ104から出力される無効電力を指令した無効電力量にするための制御である。

【0024】

更に、コントローラ107は、交流電流計110で検出したインバータ104の出力電流iu,iv,iwをuvw−dq変換部107dで下記(4)式に示すuvw−dq座標変換式によりdq回転座標系のd軸成分Idとq軸成分Iqに変換し、制御基準Idref,Iqrefに対するインバータ104の出力電流の実測値Id,Iqの偏差ΔId=Idref−Id,ΔIq=Iqref−Iqをそれぞれ算出する。

【0025】

【数1】

【0026】

更に、コントローラ107は、偏差ΔIdに所定のPI補償の演算をするとともに、インバータ104の出力電流の実測値Iqにフィルタ105のインピーダンス成分ωLを乗じて干渉量を演算し、その演算値を偏差ΔIdのPI補償演算値に加算してインバータ104の出力電流の制御目標のdq回転座標系におけるd軸成分Idoを設定する。また、コントローラ107は、偏差ΔIqに所定のPI補償の演算をするとともに、インバータ104の出力電流の実測値Idにフィルタ105のインピーダンス成分ωLを乗じて干渉量を演算し、その演算値を偏差ΔIqのPI補償演算値から減算してインバータ104の出力電流の制御目標のdq回転座標系におけるq軸成分Iqoを設定する。

【0027】

そして、コントローラ107は、その制御目標Ido,Iqoに図略の系統電圧対抗分をそれぞれ加算してインバータ104の出力電圧のdq回転座標系における制御目標Vdo,Vqoを算出し、その制御目標Vdo,Vqoをdq−uvw変換部107kで下記(5)式に示すdq−uvw座標変換式により三相電圧に変換することで、U,V,Wの各相の制御目標vuo,vvo,vwoを生成する。

【0028】

【数2】

【0029】

そして、コントローラ107は、PWM信号生成部107mで制御目標vuo,vvo,vwoのレベルをそれぞれ三角波vtのレベルと比較し、比較結果に応じたレベルのパルス信号を生成することでU,V,Wの各相に対するPWM信号を生成する。

【先行技術文献】

【特許文献】

【0030】

【特許文献1】特開2004−260942号公報

【特許文献2】特開2006−101581号公報

【特許文献3】特開2007−037256号公報

【発明の概要】

【発明が解決しようとする課題】

【0031】

系統連系インバータ装置100では、インバータ104におけるスイッチング損失を可及的に抑制して高効率で電力系統101に電力を供給することが求められる。また、系統連系インバータ装置100では、フィルタ105を構成するインダクタ及びキャパシタの各素子を可及的に小型、軽量にして装置全体の小型化、軽量化、低コスト化が求められる。

【0032】

フィルタ105を構成するインダクタ及びキャパシタの各素子の値は、インバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさによって決定される。従って、コントローラ107によるインバータ104の制御をスイッチングノイズの大きさを抑制するようにすれば、フィルタ105を構成する各素子の小型化、軽量化に繋がり、系統連系インバータ装置100の小型化、軽量化、低コスト化に寄与する。

【0033】

しかし、従来のインバータ104の制御では、インバータ104のバス電圧Vdcを所定のバス電圧基準値Vrefにするように、インバータ104の出力電流iu,iv,iwを制御するので、コントローラ107で生成されるPWM信号の変調度Mが変動し、それに応じてインバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさも変動する。従って、フィルタ105を構成するインダクタ及びキャパシタは、スイッチングノイズの大きさの変動幅の最大値に基づいて選定する必要があり、フィルタ105の小型化、軽量化が困難となっている。

【0034】

また、コントローラ107の制御系には電流マイナーループ(uvw−dq変換部107d、PI補償部107g,107h、非干渉化部107i,107j及びdq−uvw変換部107kによる処理部分)が含まれるので、制御系の構成も複雑になる。

【0035】

PWM信号の変調度Mを、インバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさが変動範囲の最小となる値に固定すれば、スイッチングノイズの大きさが従来よりも抑制されるので、フィルタ105の更なる小型化及び軽量化が可能になる。また、変調度Mを固定する制御は、インバータ104の出力電流の制御目標のdq回転座標系におけるd軸成分Idoを固定する制御に相当するから、従来のように電流マイナーループによってインバータ104の出力電流を制御目標の変動に追従させる制御も不要になり、制御系の簡素化も期待できる。

【0036】

本発明は、コントローラの制御系をPWM信号の変調度を所定値に固定する制御系とすることによって制御系の簡素化を可能にするとともに、装置の小型化、軽量化、低コスト化を図ることができる系統連系インバータ装置を提供することを目的とする。

【課題を解決するための手段】

【0037】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0038】

本発明によって提供される系統連系インバータ装置は、複数のスイッチング素子を有し、これらのスイッチング素子により前記直流電源から供給される直流電力を断続することで交流電力に逆変換する電力逆変換手段と、前記電力逆変換手段の出力信号に含まれるスイッチングノイズを除去して電力系統に出力するノイズ除去手段と、前記複数のスイッチ素子をオン・オフ駆動するパルス幅変調信号を制御することによって前記電力逆変換手段の電力逆変換動作を制御する制御手段と、を備えた系統連系インバータ装置において、前記制御手段は、前記パルス幅変調信号の変調度が予め設定された変調度となる振幅の変調波を生成する変調波生成手段と、前記変調波生成手段で生成された変調波を用いて前記パルス幅変調信号を生成するパルス幅変調信号生成手段と、を備えたことを特徴とする(請求項1)。

【0039】

なお、上記の系統連系インバータ装置において、前記変調波生成手段は、前記変調波の波形データを記憶した記憶手段と、前記電力系統に出力される無効電力を検出し、その検出値を前記無効電力の制御目標にするための位相を算出する位相算出手段と、前記記憶手段から読み出した前記変調波の波形データの位相を前記位相算出手段で算出した位相で補正して前記パルス幅変調信号を生成するための変調波を生成する位相補正手段と、を含む構成にするとよい(請求項2)。

【0040】

また、請求項1又は2に記載の系統連系インバータ装置において、前記電力逆変換手段は、三相インバータで構成され、前記変調波生成手段は、各相の変調波として、1/3周期の期間が各相の相電圧から当該相より相順が1つ前の相電圧を差し引いて得られる線間電圧の波形となり、続く1/3周期の期間が各相の相電圧から当該相より相順が1つ後の相電圧を差し引いて得られる線間電圧の波形となる波形となり、残りの1/3周期の期間がゼロとなる波形を有する制御目標を生成するとよい(請求項3)。

【0041】

また、請求項1又は2に記載の系統連系インバータ装置において、前記電力逆変換手段は、三相インバータで構成され、前記変調波生成手段は、各相の変調波として前記三相インバータから出力される相電圧の制御目標を生成するとよい(請求項4)。

【0042】

また、請求項3に記載の系統連系インバータ装置において、相毎に前記変調波生成手段で生成された制御目標の三次高調波を生成する三次高調波生成手段と、前記変調波生成手段で生成された各相の前記制御目標に前記三次高調波生成手段で生成された各相に対応する三次高調波を加算する信号加算手段と、を更に備え、前記パルス幅変調信号生成手段は、相毎に前記制御目標に代えて前記信号加算手段から出力される信号を用いて前記パルス幅変調信号を生成するとよい(請求項5)。

【0043】

また、上記の系統連系インバータ装置において、予め設定された変調度は、0.7から1.0の間の値に設定されるとよい(請求項6)。

【0044】

また、上記の系統連系インバータ装置において、前記パルス幅変調信号生成手段は、前記変調波生成手段で生成された変調波のレベルと所定の三角波のレベルを比較することにより前記パルス幅変調信号を生成するとよい(請求項7)。

【発明の効果】

【0045】

本発明によれば、パルス幅変調信号を生成するための変調波として、パルス幅変調信号の変調度が予め設定された変調度となる所定の変調波を生成し、その変調波を用いてパルス幅変調信号を生成するので、例えば、パルス幅変調信号の変調度をスイッチングノイズやコモンモードノイズを最も小さくすることができる変調度にすることによって、系統連系インバータ装置のスイッチングノイズやコモンモードノイズを抑制することができる。

【0046】

また、ノイズ除去手段の特性を従来よりも緩和できるので、ノイズ除去手段の小型化、軽量化が可能になり、系統連系インバータ装置の小型・軽量化及び低コスト化を図ることができる。

【0047】

また、パルス幅変調信号の変調度を固定する制御を行うので、従来の電流マイナーループによる制御系が不要になる。これにより、制御手段における制御の安定性や過渡特性が向上する。また、電力逆変換手段に供給される直流電圧のレベルが変動したり、ノイズ除去手段での電圧降下が変化したりした場合でもパルス幅変調信号の変調度は一定になるので、パルス幅変調信号を生成する際の電圧利用率を一定にすることができる。

【図面の簡単な説明】

【0048】

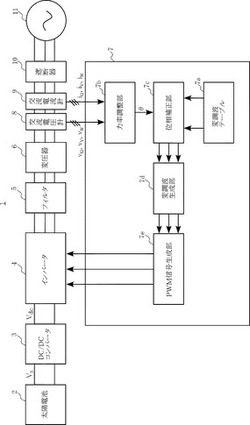

【図1】本発明に係る系統連系インバータ装置のブロック構成を示す図である。

【図2】DC/DCコンバータの回路構成の一例を示す図である。

【図3】インバータの回路構成の一例を示す図である。

【図4】正弦波の変調波を用いた三角波比較方式によりPWM信号を生成する第1のパルス幅変調方式を説明するための図である。

【図5】非正弦波の変調波を用いた三角波比較方式によりPWM信号を生成する第2のパルス幅変調方式を説明するための図である。

【図6】変調波生成部が第2のパルス幅変調方式で変調波を生成する場合の変調波の波形を説明するための図である。

【図7】図18に示す回路モデルで従来の方法1,2と本発明の方法の3種類についてPWM制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした結果である。

【図8】シミュレーション1の条件で従来の方法1によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図9】シミュレーション1の条件で従来の方法2によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図10】シミュレーション1の条件で本発明の方法によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図11】第1のパルス幅変調方式で変調度M=1のPWM信号を生成した時のインバータの出力電圧に含まれるスイッチングノイズをFFT解析した結果を示す図である。

【図12】第1のパルス幅変調方式で生成したPWM信号を用いてインバータを駆動した場合のインバータの出力電圧に含まれるスイッチングノイズと変調度Mの関係を示す図である。

【図13】図18に示す回路モデルの三相負荷の中性点に交流電圧計を設けた構成で、第2のパルス幅変調方式によりバス電圧の制御値を400[v]、変調度Mを「1.0」に固定する制御をした場合のインバータの出力電圧に含まれるコモンモードノイズをFFT解析した結果を示す図である。

【図14】変調度Mを「0.8」に変更して図13と同様のFFT解析をした結果を示す図である。

【図15】バス電圧の制御値を300[v]に変更して図13と同様のFFT解析をした結果を示す図である。

【図16】バス電圧の制御値を300[v]、変調度Mを「0.8」に変更して図13と同様のFFT解析をした結果を示す図である。

【図17】変調度M=1のPWM信号で三相インバータを動作させた時の三相インバータの出力電圧に含まれるスイッチングノイズをFFT解析したスペクラム分布の一例を示す図である。

【図18】図17に示すFFT解析を行った系統連系インバータ装置の回路モデルを示す図である。

【図19】変調波の振幅を変化させて図17に示すFFT解析を行い、各変調度Mにおける最大ノイズ成分のレベルをプロットした図である。

【図20】従来の系統連系インバータ装置の基本的な構成の一例を示すブロック図である。

【発明を実施するための形態】

【0049】

本発明に係る系統連系インバータ装置を図1乃至図16を用いて説明する。

【0050】

図1は、本発明に係る系統連系インバータ装置のブロック構成を示す図である。

【0051】

図1に示す系統連系インバータ装置1は、太陽電池2を電力源とするインバータ装置である。また、図2と図3は、それぞれ系統連系インバータ装置1内のDC/DCコンバータ3とインバータ4の回路構成の一例を示す図である。

【0052】

系統連系インバータ装置1は、基本的なブロック構成として太陽電池2、DC/DCコンバータ3、インバータ4、フィルタ5、変圧器6及びコントローラ7を備え、変圧器6の出力端は遮断器10を介して電力系統11に接続される。また、変圧器6の出力端には系統連系インバータ装置1から出力されるU,V,Wの各相の交流電圧vu,vv,vwと交流電流iu,iv,iwの実測値をコントローラ7に入力するために交流電圧計8と交流電流計9とが設けられている。

【0053】

太陽電池2は、太陽からの光エネルギーを電気エネルギーに変換する電力源として機能する。直流電源としては、太陽電池2に代えて、燃料電池等の他の直流電源を用いることができる。太陽電池2は、山形の電力−電圧特性を有し、動作点が最大電力点からずれると、出力電力が減少する特性を有する。また、最大電力点は日射量によって変化するので、系統連系インバータ装置1では、一般に太陽電池2の動作点が最大電力点を追尾する(すなわち、出力電圧を最大電力点電圧にする)MPPT制御(Maximum Power Point Tracking、最大電力点追尾制御)が行われる。

【0054】

DC/DCコンバータ3は、インバータ4に入力される直流電圧(バス電圧)Vdcを所定のバス電圧基準値Vrefに安定化させる機能を果たす。DC/DCコンバータ3は、太陽電池2から出力される直流電圧Vsをバス電圧基準値Vrefに昇圧する。図1ではDC/DCコンバータ3のコントローラを省略しているが、コントローラ7は、インバータ4のバス電圧Vdcがバス電圧基準値Vrefに固定されるように制御するので、DC/DCコンバータ3のコントローラは、DC/DCコンバータ3の入力電圧、すなわち、太陽電池2の直流電圧Vsが最大電力点電圧を追尾するように制御する。

【0055】

DC/DCコンバータ3は、例えば、図2に示す周知の昇圧型コンバータである。昇圧型DC/DCコンバータは、スイッチング素子Qを所定の周期でオン・オフさせることにより、オン期間に太陽電池2からの電気エネルギーを磁気エネルギーに変換してチョークコイルLに蓄積し、オフ期間にその磁気エネルギーを再度電気エネルギーに変換してダイオードDを介してコンデンサCに出力する動作を繰り返す。スイッチング素子Qとしては、バイポーラ・トランジスタ、FET(Field Effect Transistor)、サイリスタ、IGBT(Insulated Gate Bipolar Transistor)等の各種の半導体スイッチング素子が利用される。

【0056】

インバータ4は、太陽電池2からDC/DCコンバータ3を介して入力される直流電力を三相交流電力に逆変換して電力系統11に出力する。インバータ4は、図3に示すように、6個のスイッチング素子Q1a,Q1b,Q2a,Q2b,Q3a,Q3bを用いた三相フルブリッジ回路で構成される三相インバータである。6個のスイッチング素子Qka,Qkb(k=1,2,3)もDC/DCコンバータ3のスイッチング素子Qと同様に上記の各種の半導体スイッチング素子を使用することができる。

【0057】

三相フルブリッジ回路は、スイッチング素子Q1a,Q1bの直列回路A1、スイッチング素子Q2a,Q2bの直列回路A2及びスイッチング素子Q3a,Q3bの直列回路A3を電源ラインLVに並列接続した構成である。各スイッチング素子Qka,Qkbにはそれぞれ帰還ダイオードDka,Dkb(k=1,2,3)が逆並列に接続されている。電源ラインLVにはDC/DCコンバータ3から出力される直流電圧(バス電圧)Vdcが供給される。

【0058】

各直列回路Ak(k=1,2,3)の一対のスイッチング素子Qka,Qkb(k=1,2,3)は、コントローラ7から出力される一対のPWM信号Ska,Skb(k=1,2,3)によってオン・オフ駆動される。PWM信号Skbは、PWM信号Skaに対してレベルが反転している。従って、スイッチング素子Qkaとスイッチング素子Qkbは、PWM信号Ska,Skbによって交互にオン・オフ動作をする。

【0059】

PWM信号Ska,Skbは、コントローラ7によって、インバータ4の出力電圧の制御目標vuo,vvo,vwo(変調波の瞬時値)と変調波よりも高周波の三角波vt(搬送波の瞬時値)とを比較する三角波比較方式により生成される。インバータ4の出力電圧の制御目標vuo,vvo,vwoの波形は互いに位相が2/3πだけずれるから、PWM信号S1a,S1b、PWM信号S2a,S2b及びPWM信号S3a,S3bのパルス幅のパターンは、互いに位相が2π/3だけずれている。各直列回路Akの一対のスイッチング素子Qka,Qkbが一対のPWM信号Ska,Skbによってオン・オフ動作することにより、直列回路A1の接続点n1、直列回路A2の接続点n2及び直列回路A3の接続点n3からそれぞれU相、V相、W相の各相に対する交流電圧vu,vv,vwが出力される。

【0060】

フィルタ5は、インバータ4から出力されるU相、V相、W相の三相交流信号(交流電圧vu,vv,vwと交流電流iu,iv,iw)に含まれるスイッチングノイズを除去する。フィルタ5は、図3に示すように、等価的に接続点n1,n2,n3の出力ラインにそれぞれインダクタLFを接続し、その後段の各出力ライン間にキャパシタCFを接続した逆L型回路で構成される。インバータ4の接続点n1,n2,n3から出力される信号の波形は微小な階段状の変化をするが、フィルタ5を通すことによってスイッチングノイズの成分が除去されるので、インバータ4の出力信号の波形は綺麗な正弦波となる。定常状態では、インバータ4から出力される交流電圧vu,vv,vwの波形は目標値vuo,vvo,vwoの波形となる。

【0061】

変圧器6は、昇圧トランスで構成され、フィルタ5から出力される正弦波の交流電圧のレベルを系統電圧とほぼ同一のレベルに昇圧する。交流電圧計8は、変圧器6から出力されるインバータ4の出力電圧(U,V,Wの各相の相電圧vu,vv,vw)を検出する。また、交流電流計9は、変圧器6から出力されるインバータ4の出力電流(U,V,Wの各相の電流iu,iv,iw)を検出する。交流電圧計8及び交流電流計9の検出値は、コントローラ4に入力され、PWM信号Ska,Skbの生成処理に利用される。

【0062】

コントローラ7は、マイクロコンピュータ若しくはFPGA(Field-Programmable Gate Array)により構成され、ディジタル演算処理により、所定の周期でインバータ4の出力電圧の制御目標vuo,vvo,vwoと所定の三角波vtとを生成し、相毎に制御目標vuo,vvo,vwoのレベルを三角波vtのレベルと比較してPWM信号Ska,Skb(k=1,2,3)を生成する。搬送波である三角波vtの波形は予め決められている。従って、コントローラ7は、インバータ4の出力電圧の制御目標vuo,vvo,vwoを生成する第1処理部とその制御目標vuo,vvo,vwoのレベルを三角波vtのレベルと比較してPWM信号Ska,Skbを生成する第2処理部とを備える。図1の変調波テーブル7a、力率調整部7b、位相補正部7c及び変調波生成部7dは第1処理部を構成し、PWM信号生成部7eは第2処理部を構成している。

【0063】

本発明は、インバータ4から出力される交流電圧及び交流電流に含まれるスイッチングノイズがPWM信号Ska,Skbの変調度Mによって変化し、スイッチングノイズを好適に抑制にする変調度M*(以下、「最適変調度M*」という。)があることに着目し、第1処理部で生成するインバータ4の出力電圧の制御目標vuo,vvo,vwoの波形を第2処理部で生成されるPWM信号Ska,Skbの変調度Mが最適変調度M*となるように制御する構成に特徴を有する。最適変調度M*は、変調度Mの変動範囲において、スイッチングノイズの最大ノイズ成分が最小になる変調度である。

【0064】

三相インバータにおける三角波比較方式によるPWM信号の生成においては、図4に示すように、インバータの出力電圧の制御目標vuo,vvo,vwoとして、相毎に正弦波の相電圧vmを生成し、振幅の中央のゼロレベルを合わせて三角波vtと比較する方式(以下、「第1のパルス幅変調方式」という。)と、図5に示すように、相毎に、1周期Tを均等に3つの区間I,II,IIIに分け、区間Iと区間IIは線間電圧の波形を有し、区間IIIはレベル「0」の波形を有する電圧vm’を生成し、振幅の最小レベルを合わせて三角波vtと比較する方式(以下、「第2のパルス幅変調方式」という。)と、がある。第1のパルス幅変調方式は、一般的な方法であるが、第2のパルス幅変調方式は、例えば、上述した特開2010−136547号公報に開示されている方式である。

【0065】

本発明は、第1のパルス幅変調方式及び第2のパルス幅変調方式のいずれにも適用可能であるので、まず、コントローラ7が第2のパルス幅変調方式でPWM信号を生成する場合について説明する。第2のパルス幅変調方式でPWM信号Ska,Skbを生成する場合は、例えば、図17〜図19を用いて説明した例では、最適変調度M*は「0.878」である(図19参照)。

【0066】

第2のパルス幅変調方式のU,V,Wの各相の制御目標(変調波)は、図5に示す電圧vm’と同一の波形を有する。インバータ4から出力されるU,V,Wの各相の相電圧の制御目標をvuo,vvo,vwoとすると、U相の制御目標(変調波)vuo’の波形は、図6に示すように、位相(θ+2nπ)(n=0,1,…)に対して、

(a1)−π/6≦θ≦3π/6:vuo’=vuwo=vuo−vwo

(a2)3π/6≦θ≦7π/6:vuo’=vuvo=vuo−vvo

(a3)7π/6≦θ≦11π/6:vuo’=0

の合成をしたものである。

【0067】

また、V相の制御目標(変調波)vvo’の波形は、

(b1)−π/6≦θ≦3π/6:vvo’=vvwo=vvo−vwo

(b2)3π/6≦θ≦7π/6:vvo’=0

(b3)7π/6≦θ≦11π/6:vvo’=vvuo=vvo−vuo

の合成をしたものである。

【0068】

また、W相の制御目標(変調波)vwo’の波形は、

(c1)−π/6≦θ≦3π/6:vwo’=0

(c2)3π/6≦θ≦7π/6:vwo’=vwvo=vwo−vvo

(c3)7π/6≦θ≦11π/6:vwo’=vwuo=vwo−vuo

の合成をしたものである。

【0069】

インバータ4の出力電圧の制御目標vuo’,vvo’,vwo’を生成するためのU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoは、インバータ4の出力電流の制御目標iuo,ivo,iwoが連系用リアクトルを流れることによる電圧降下分の電圧を系統電圧にベクトル合成することによって得られる。本発明に係る系統連系インバータ装置1では、変調波の振幅を最適変調度M*の振幅に固定するので、各相の相電圧の制御目標vuo,vvo,vwoも最適変調度M*に基づき予め設定することができる。そこで、本実施形態では、最適変調度M*に基づいて各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを予め設定している。

【0070】

そして、本実施形態では、αβ座標系における制御目標(Vαo,Vβo)に対して、インバータ4から出力される無効電力を無効電力指令値に追随させるための位相補正とαβ−uvw座標変換とを行ってU,V,Wの各相の制御目標(変調波)vuo’,vvo’,vwo’を生成するようにしている。

【0071】

コントローラ7は、上記の処理をするための機能ブロックとして、変調波テーブル7a、力率調整部7b、位相補正部7c、変調波生成部7d及びPWM信号生成部7eを備える。変調波テーブル7aは、最適変調度M*に基づいて予め設定された各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータを記憶するブロックである。

【0072】

力率調整部7bは、交流電圧計8で検出されるインバータ4の出力電圧vu,vv,vwと交流電流計9で検出されるインバータ4の出力電流iu,iv,iwとを用いてインバータ4から出力される無効電力Qを算出し、その算出値Qから無効電力Qを無効電力指令値Qo(力率1の運転時ではQo=0)にするための位相θを算出する。

【0073】

位相補正部7cは、変調波テーブル7aから各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを読み出し、力率調整部7bで算出された位相θを用いて下記(6’)式に示す演算式により上記の位相補正とαβ−uvw座標変換の演算処理を行い、U,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを生成する。

【0074】

【数3】

【0075】

なお、(6)式において、θの行列は、αβ座標系における電圧ベクトルの位相を位相θだけ進めたり、遅らせたりするための演算処理である。0<θであれば、電圧ベクトルの位相は進み位相に補正され、θ<0であれば、電圧ベクトルの位相は遅れ位相に補正される。

【0076】

変調波生成部7dは、位相補正部7cで生成されるU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを用いて上記の(a1)〜(a3)、(b1)〜(b3)、(c1)〜(c3)の合成処理をすることによりU,V,Wの各相の変調波vuo’,vvo’,vwo’を生成し、PWM信号生成部7eに入力する。

【0077】

PWM信号生成部7eは、振幅Vcを有する高周波の三角波vtを生成し、三角波vtの最小レベル(−Vc)とU,V,Wの各相の変調波vuo’,vvo’,vwo’のゼロレベルを合わせてそれぞれレベルを比較してインバータ4の直列回路A1,A2,A3に対するPMW信号S1a,S2a,S3aを生成する。また、PWM信号生成部7eは、PMW信号S1a,S2a,S3aのレベルを反転することによりPMW信号S1b,S2b,S3bを生成する。そして、PWM信号生成部7eは、そのPMW信号S1a,S2a,S3a,S1b,S2b,S3bをインバータ4に入力する。

【0078】

なお、変調波生成部7dから入力される変調波vuo’,vvo’,vwo’の振幅Vm(Vmは相電圧の制御目標vuo,vvo,vwoの振幅)と三角波vtの振幅Vcとの間には、Vm/Vc=M*=0.878の関係がある。従って、変調波テーブル7aに記憶されている各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータは、変調波生成部7dで生成される変調波vuo’,vvo’,vwo’の振幅がVm/Vc=M*を満たすように予め設定されている。

【0079】

次に、本実施形態に係る系統連系インバータ装置1の特徴的な構成の作用・効果について説明する。

【0080】

コントローラ7は、系統連系インバータ装置1を電力系統11に連系させた後は、太陽電池2から供給される直流電力をインバータ4で交流電力に変換して電力系統11に出力する制御をする。従来の系統連系インバータ装置100は、インバータ104のバス電圧Vdcをバス電圧基準値Vrefに保持するように、インバータ104の出力電流の制御目標を設定し、電流マイナーループによってインバータ104の出力電流iu,iv,iwを制御目標に制御している。このため、従来の系統連系インバータ装置100では、PWM信号生成部107mで生成されるPWM信号の変調度Mが変動し、その変調度Mの変動に基づきスイッチングノイズも大きく変動する。

【0081】

これに対し、系統連系インバータ装置1は、変調度Mをスイッチングノイズの最大ノイズ成分が最も小さくなる最適変調度M*に固定し、インバータ4の出力電流iu,iv,iwを固定する制御をしているので、スイッチングノイズを最小の状態に抑制することができる。

【0082】

図7は、図18に示す回路モデルで従来の方法1,2と本発明の方法の3種類についてPWM制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレーションした結果である。

【0083】

シミュレーション1は、キャリア周波数fc=4.8[kHz]、系統周波数fg=60[Hz]、電力系統11の線間電圧の実効値Vrms=202[v]、インバータINVから定格電力を出力したときのフィルタでの電圧降下分5%の条件で、従来の方法1、従来の方法2及び本発明の方法のそれぞれについて定常状態でのスイッチングノイズの最大ノイズ成分の発生状況をシミュレートしたものである。

【0084】

従来の方法1は、図17を用いて説明したシミュレーションのPWM制御方法に相当し、バス電圧Vdcを(1)式に示す電圧(345.7[v])に制御する方法である。従来の方法2は、バス電圧Vdcを電力系統11に連系可能な最小値に設定する場合のPWM制御方法である。また、本発明の方法は、PWM信号の変調度Mを最適変調度M*(=0.878)に固定するPWM制御方法である。スイッチングノイズの大きさはバス電圧Vdcが低いほど低くなるようなイメージがあるので、バス電圧Vdcを最も厳しい条件に設定した場合と本発明の方法とでいずれがスイッチングノイズを抑制できるかを検証するために、今回のシミュレーションでは従来の方法2を加えている。

【0085】

従来の方法1では、バス電圧Vdcは、345.7[v]に制御される。一方、従来の方法2では、バス電圧Vdcは、実効値Vrms=202[v]の電力系統に定格電力を出力するために必要な最小のバス電圧値となるので、

Vdc=(202×√(2)×0.866]×2×1.05/√(3)

≒299.9[v] …(7)

となる。(7)式は、(1)式の係数「1.1」をなくし、フィルタ5の電圧降下分の係数「1.1」を定格出力時のフィルタでの電圧降下分5%の条件である係数「1.05」に変更したものである。

【0086】

インバータの出力電圧Vinv、変調度M及びバス電圧Vdcの間にはVinv=k×M×Vdc(kは電圧利用率などの諸係数)の関係がある。従来の方法2では電力系統に連系させるために必要なバス電圧が最小値に制御されるので、従来の方法2の変調率M2は「1」となる。これに対し、従来の方法1ではバス電圧Vdcが345.7[v]に設定されるので、従来の方法1の変調率M1はM1=299.9/345.7≒0.867となる。一方、本発明の方法は、変調度M3を最適変調度M*=0.878に設定するので、バス電圧VdcはVdc=299.9/M*=299.9/0.878=341.6[v]に制御されることになる。

【0087】

シミュレーション2は、シミュレーション1に対して系統電圧が許容範囲(±10%)の上限値(Vrms=222[v])に上昇した場合に条件を変更したものであり、シミュレーション3は、シミュレーション1に対して系統電圧が許容範囲(±10%)の下限値(Vrms=182[v])に低下した場合に条件を変更したものである。

【0088】

シミュレーション2ではシミュレーション1に対して系統電圧が1.1倍になるので、従来の方法2のバス電圧Vdcもシミュレーション1の場合の1.1倍となる。一方、シミュレーション3ではシミュレーション1に対して系統電圧が0.9倍になるので、従来の方法2のバス電圧Vdcもシミュレーション1の場合の0.9倍となる。

【0089】

従って、シミュレーション2のバス電圧Vdcは、

Vdc=(202×1.1×√(2)×0.866]×2×1.05/√(3)

≒329.6[v] …(8)

となる。

【0090】

また、シミュレーション3のバス電圧Vdcは、

Vdc=(202×0.9×√(2)×0.866]×2×1.05/√(3)

≒270.2[v] …(9)

となる。また、本発明の方法のシミュレーション2,3のバス電圧Vdcは、(8)式,(9)式の演算値を1/0.878倍したものであり、それぞれ375.5[v]、307.8[v]となる。

【0091】

従って、従来の方法1の変調度M1は、シミュレーション2ではM1=329.9/345.7≒0.953に上昇し、シミュレーション3ではM1=270.0/345.7≒0.782に低下する。なお、従来の方法2の変調度M2と本発明の変調度M3は、シミュレーション1の場合と変わらず、それぞれ「1」と「0.878」である。

【0092】

図8〜図10は、シミュレーション1の条件で従来の方法1、従来の方法2及び本発明の方法によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。図8は、従来の方法1によるPWM変調制御の場合、図9は、従来の方法2によるPWM変調制御の場合、図10は、本発明の方法によるPWM変調制御の場合の波形図であり、図7のシミュレーション1のNmax1,Nmax2,Nmax3は、図8〜図10の各波形図に示す最大ノイズ成分Nmax1,Nmax2,Nmax3の値を記載したものである。

【0093】

また、シミュレーション4〜6は、それぞれシミュレーション1〜3でインバータの出力電圧を系統電圧対抗分だけにしたものである。シミュレーション4〜6では、インバータから電流が出力されず、フィルタでの電圧降下が生じないから、シミュレーション4〜6の従来の方法2のバス電圧Vdcは、それぞれ(7)式〜(9)式で係数「1.05」を除去した演算式により算出される。

【0094】

すなわち、シミュレーション4の従来の方法2のバス電圧Vdcは、

Vdc=(202×√(2)×0.866]×2/√(3)

≒285.7 …(10)

となり、シミュレーション5の従来の方法2のバス電圧Vdcは、

Vdc=(202×1.1×√(2)×0.866]×2/√(3)

≒313.9 …(11)

となり、シミュレーション6の従来の方法2のバス電圧Vdcは、

Vdc=(202×0.9×√(2)×0.866]×2/√(3)

≒257.4 …(12)

となる。

【0095】

また、本発明の方法のシミュレーション4〜6のバス電圧Vdcは、(10)式〜(12)式の演算値を1/0.878倍したものであり、それぞれ325.4[v]、357.6[v]、293.1[v]となる。

【0096】

従って、従来の方法1の変調度M1は、シミュレーション4ではM1=285.7/345.7≒0.826となり、シミュレーション5ではM1=313.9/345.7≒0.908となり、シミュレーション6ではM1=257.4/345.7≒0.745となる。また、従来の方法2の変調度M2と本発明の変調度M3は、シミュレーション1の場合と同様にそれぞれ「1」と「0.878」である。

【0097】

図には示していないが、シミュレーション2〜6についても図8〜図10に示すような波形図が得られ、図7のシミュレーション2〜6のNmax1,Nmax2,Nmax3もその波形図における最大ノイズ成分Nmax1,Nmax2,Nmax3の値を記載したものである。

【0098】

図7によれば、シミュレーション1,2,5では従来の方法2の方が従来の方法1よりもスイッチングノイズの最大ノイズ成分が大きく、バス電圧Vdcが低いほど最大ノイズ成分が低くなるとは一概に言えないことが分かる。そして、シミュレーション1〜6のいずれの場合も変調度Mを最適変調度M*に制御する本発明の方法がスイッチングノイズを最も小さく制御できることが分かる。

【0099】

以上より、変調度Mを最適変調度M*に制御する系統連系インバータ装置1は、系統電圧のレベルが許容範囲内に制御されている状態で、インバータ4から電力を出力しない場合及びインバータ4から定格電力を出力する場合のいずれの場合でもスイッチングノイズを最小に制御できることが分かる。

【0100】

また、従来の方法1(従来の系統連系インバータ装置100が採用する方法)では、動作条件の変化によって最大ノイズ成分Nmax1のレベルが大きく変動するのに対し、本実施形態に係る系統連系インバータ装置1が採用する変調度Mを最適変調度M*に制御する方法では、動作条件が変化しても最大ノイズ成分Nmax3のレベルは余り変動しない。上記のシミュレーション1〜6では、最大ノイズ成分Nmax1の最小レベルと最大レベルはそれぞれ61.09[v]、92.49[v]で、その変動幅は31.4[v]であるのに対し、最大ノイズ成分Nmax3の最小レベルと最大レベルはそれぞれ49.53[v]、63.46[v]で、その変動幅は13.93[v]である。すなわち、本実施形態に係る系統連系インバータ装置1は、従来の系統連系インバータ装置100に対してスイッチングノイズを最大約50%抑制できる効果がある。

【0101】

従って、本実施形態に係る系統連系インバータ装置1では、スイッチングノイズを可及的に抑制するように制御するので、フィルタ5の周波数特性の減衰傾度を従来の系統連系インバータ装置100のフィルタ105よりも緩和することができ、これによりフィルタ5を構成するインダクタンスLF若しくはキャパシタンスCFの小型化、軽量化を図ることができる。

【0102】

また、系統連系インバータ装置1では、PWM信号生成部7eの変調度Mを最適変調度M*に固定するので、インバータ4の出力電流の制御目標を生成するための制御系や電流マイナーループ等が不要になり、コントローラ4の安定性や過渡特性が向上する。また、系統電圧のレベルが変動したり、フィルタ5での電圧降下分が変化したりしてもPWM信号生成部7eにおけるPWM信号生成処理での電圧利用率を一定に保持することができる。

【0103】

次に、コントローラ7が第1のパルス幅変調方式でPWM信号を生成する場合について説明する。

【0104】

図11は、第1のパルス幅変調方式で変調度M=1のPWM信号を生成した時のインバータの出力電圧をFFT解析した結果を示す図である。図12は、第1のパルス幅変調方式で生成したPWM信号を用いてインバータを駆動した場合のインバータの出力電圧に含まれるスイッチングノイズと変調度Mの関係を解析した結果を示す図である。図11,図12の解析条件は、図17,図19の解析条件と同じである。従って、図11の解析結果は図17の解析結果に対応し、図12の解析結果は図19の解析結果に対応している。

【0105】

図12の特性Aは、キャリア周波数fcのサイドバンド成分の最大値をプロットした特性であり、特性A’は、変調波に三次高調波を注入した場合のキャリア周波数fcのサイドバンド成分の最大値をプロットした特性である。また、特性Bは、キャリア周波数fcの2倍波のサイドバンド成分の最大値をプロットした特性であり、特性B’は、変調波に三次高調波を注入した場合のキャリア周波数fcの2倍波のサイドバンド成分の最大値をプロットした特性である。

【0106】

第2のパルス幅変調方式では、最大ノイズ成分が常にキャリア周波数fc=4.8[kHz]のサイドバンド成分の最大値であり、その最大ノイズ成分のレベルは、変調度Mの変動範囲(0.74〜1.0)では、図19に示したように変調度M*=0.878で極小となる特性を有している。これに対し、第1のパルス幅変調方式では、キャリア周波数fc=4.8[kHz]のサイドバンド成分の最大値は、図12の特性A,A’に示すように、変調度Mの変動範囲(0.74〜1.0)では単調に減少し、極小点を有しない。その一方、キャリア周波数fcの2倍波9.6[kHz]のサイドバンド成分の最大値は、特性B,B’に示すように単調に増加し、特性B(変調波に三次高調波を注入しない場合)では変調度Mが凡そ0.88以上の領域でキャリア周波数fcのサイドバンド成分の最大値よりも大きくなり(特性A,B参照)、特性B’(変調波に三次高調波を注入した場合)では変調度Mが凡そ0.86以上の領域でキャリア周波数fcのサイドバンド成分の最大値よりも大きくなっている(特性A’,B’参照)。

【0107】

第1のパルス幅変調方式でPWM信号を生成するときは、変調度Mが凡そ0.86〜0.88の値よりも小さい場合は最大ノイズ成分がキャリア周波数fcのサイドバンド成分の最大値となるが、変調度Mが凡そ0.86〜0.88の値以上の場合は最大ノイズ成分がキャリア周波数fcの2倍波のサイドバンド成分の最大値となる特性を有する。フィルタ5で最も除去し難いのは、遮断周波数に近いキャリア周波数fcのサイドバンド成分であるので、第1のパルス幅変調方式によるPWM信号の生成でもキャリア周波数fcのサイドバンド成分の最大値が最小になる変調度Mを最適変調度M*に設定することが考えられる。すなわち、第1のパルス幅変調方式では最適変調度M*=1.0に設定することが考えられる。

【0108】

しかしながら、フィルタ5のノイズ除去効率を考えると、フィルタ5にはできるだけ高周波成分を入力しない方が好ましい。この観点から第1のパルス幅変調方式での最適変調度M*を検討すると、キャリア周波数fcのサイドバンド成分の最大値とキャリア周波数fcの2倍波のサイドバンド成分の最大値とが交差する変調度MとM=1.0の範囲で最適変調度M*に選定するのが好ましいと考えられる。従って、変調波に三次高調波を注入しない場合は、M=0.88〜1.0の範囲で最適変調度M*を設定するとよく、変調波に三次高調波を注入する場合は、M=0.86〜1.0の範囲で最適変調度M*を設定するとよい。

【0109】

図1に示す構成で第1のパルス幅変調方式により変調波(正弦波の三相相電圧)を生成する場合は、変調波生成部7dで上記の(a1)〜(a3)、(b1)〜(b3)、(c1)〜(c3)の合成処理は行われず、位相補正部7cで生成されるU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoが各相の変調波として設定される。従って、変調波生成部7dで三次高調波の加算処理を行わない場合は、例えば、最適変調度M*を「0.88」とし、その最適変調度M*に基づいてU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータが予め設定され、変調波テーブル7aに記憶されている。

【0110】

コントローラ7は、変調波テーブル7aから制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを読み出し、力率調整部7bで算出された位相θを用いて(6’)式に示す演算式により位相補正とαβ−uvw座標変換の演算処理を行い、U,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを各相の変調波として生成する。

【0111】

そして、コントローラ7は、その変調波vuo,vvo,vwoをそれぞれ中央のレベル(ゼロレベル)を三角波vtの中央のレベル(ゼロレベル)と合わせてレベル比較することによりPMW信号S1a,S2b,S3cを生成する。また、コントローラ7は、PMW信号S1a,S2a,S3aのレベルを反転することによりPMW信号S1b,S2b,S3bを生成し、そのPMW信号Ska,Skb(k=1,2,3)をインバータ4に入力する。

【0112】

なお、第1のパルス幅変調方式では、電圧利用率を改善するため、変調波生成部7dで三次高調波を加算する処理をしてもよい。すなわち、変調波生成部7dで、位相補正部7cで生成される各相の変調波vuo,vvo,vwoから三次高調波を生成し、各三次高調波を所定の振幅比率(例えば、変調波に対して1/6)で対応する相の変調波vuo,vvo,vwoに加算するようにしてもよい。この場合は、例えば、最適変調度M*を「0.86」とし、その最適変調度M*に基づいてU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータが予め設定され、変調波テーブル7aに記憶される。変調波に三次高調波を注入する場合は、電圧利用率を「0.866」に改善することができる。

【0113】

なお、上記実施形態では、変調波テーブル7aにU,V,Wの各相の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを記憶しているが、U,V,Wの各相の制御目標vuo,vvo,vwoを記憶するようにしてもよい。この場合は、位相補正部7cでは、下記(13)式に示す演算式により位相補正の演算処理を行ってU,V,Wの各相の制御目標(変調波)vuo’,vvo’,vwo’を生成するとよい。

【0114】

【数4】

【0115】

上記の実施形態では、スイッチングノイズを可及的に低減するという観点から変調度Mを最適変調度M*に固定するようにPWM信号の生成制御をすることを説明したが、スイッチングノイズ以外のノイズ対策の観点でも同様の制御をすることができる。例えば、インバータを用いたパワーエレクトロニクス機器では、EMC(Electro Magnetic Interference)対策としてコモンモードノイズを可及的に低減したいという要求があり、この要求は系統連系インバータ装置でも同様である。

【0116】

図13〜図16は、図18に示す回路モデルの5Ωの三相負荷の中性点に交流電圧計を設けた構成で、第2のパルス幅変調方式によりPWM変調の制御をした場合のインバータINVの出力電圧に含まれるコモンモードノイズを100[kHz]〜1.0[MHz]の範囲でFFT解析したものである。図13は、バス電圧Vdcの制御値を400[v]、変調度Mを「1.0」に制御した場合であり、図14は、バス電圧Vdcの制御値を400[v]、変調度Mを「0.8」に制御した場合である。また、図15は、バス電圧Vdcの制御値を300[v]、変調度Mを「1.0」に制御した場合であり、図16は、バス電圧Vdcの制御値を300[v]、変調度Mを「0.8」に制御した場合である。

【0117】

図13〜図16に示すように、コモンモードノイズは、周波数が高くなるのに応じて指数関数的に低下する。そして、ノイズ成分のレベルは、(Vdc,M)=(400v,0.8)、(400v,1.0)、(300v,0.8)、(300v,1.0)の順に小さくなっている。図示はしていないが、第1のパルス幅変調方式によりPWM変調の制御をした場合をFFT解析したでも同様の傾向が見られる。

【0118】

変調度Mを「1.0」に制御すると、バス電圧基準値Vrefは自動的に小さく制御されるので、コモンモードノイズを抑制する場合は、変調度Mを「1.0」に固定する制御をすれば、スイッチングノイズの場合と同様にコモンモードノイズを従来の変調方法よりも抑制することができる。

【0119】

なお、高調波補償を行う場合は、高調波補償により変調波の振幅に変調度余裕が生じるので、最適変調度M*はM*=(1.0−高調波補償用の変調度余裕分)にするとよい。

【0120】

上記の実施形態では、三角波比較方式によりPWM信号を生成する系統連系インバータ装置について説明したが、本発明は、他の方式によりPWM信号を生成する系統連系インバータ装置にも適用することができる。例えば、WO2009/041276号公報に記載されるPWM信号の生成方式を用いた系統連系インバータ装置にも適用することができる。

【0121】

WO2009/041276号公報に記載のパルス幅変調方式の具体的な内容は同公報に記載されているので、ここでは詳細は省略する。同公報に記載のパルス幅変調方式の要旨は、PWMホールド法を用いて系統連系インバータ装置1のインバータ4〜変圧器6の回路を線形システムにモデル化し、その線形システムにおけるインバータ4の出力電圧を入力とする状態方程式からパルス信号のオン時間(パルス幅)を入力とする状態方程式を導出する。そして、その状態方程式の解を演算することによってパルス信号の各パルスのオン時間をリアルタイムで求めるというものである。すなわち、WO2009/041276号公報に記載のパルス幅変調方式は、入力をパルス信号のオン時間とする状態方程式の解を求める演算式を用いてインバータ4の相電圧の制御目標からPWM信号を直接生成する方式である。

【0122】

従って、本発明は、変調波のレベルをキャリア信号のレベルと比較する処理をしないで、変調波のレベルから直接的にPWM信号を生成する変調方式にも適用することができる。

【符号の説明】

【0123】

1 インバータ装置

2 太陽電池

3 DC/DCコンバータ

4 インバータ

Q1a,Q1b,Q2a,Q2b,Q3a,Q3b スイッチング素子

D1a,D1b,D2a,D2b,D3a,D3b 帰還ダイオード

5 フィルタ

6 変圧器

7 コントローラ

7a 変調波テーブル

7b 力率調整部

7c 位相補正部

7d 変調波生成部

7e PWM信号生成部

8 交流電圧計

9 交流電流計

10 遮断器

11 電力系統

【技術分野】

【0001】

本発明は、燃料電池や太陽電池などの直流電源から出力される直流電力を交流電力に逆変換し、その交流電力を商用電力系統に供給する系統連系インバータ装置に関する。

【背景技術】

【0002】

系統連系インバータ装置の構成要素には直流電源から出力される直流電力を交流電力に逆変換する電力逆変換回路(インバータ)とその電力逆変換回路から出力される交流信号(交流電圧信号と交流電流信号)に含まれるスイッチングノイズを除去するフィルタ回路とが含まれる。

【0003】

フィルタ回路の容量は、インバータから出力される交流信号に含まれるスイッチングノイズのレベル(交流信号に重畳されるリップルノイズの大きさ)が大きくなるのに応じて大きくなるので、インバータで生じるスイッチングノイズが大きければ、フィルタ回路のキャパシタやインダクタの回路要素が大型化する。

【0004】

フィルタ回路は、系統連系インバータ装置の小型化や低コスト化を阻害する主要な回路要素であるから、インバータで生じるスイッチングノイズのレベルを可及的に抑制してフィルタの容量を小さくすることが望ましい。

【0005】

図17は、変調度M=1のPWM(Pulse Width Modulation)信号で三相インバータを動作させた時の三相インバータの出力電圧(線間電圧)をFFT(First Fourier Transform)解析したスペクラム分布の一例を示す図である。なお、変調度Mは、三角波比較方式によるパルス幅変調では、M=(変調波の振幅のピーク値)/(搬送波の振幅のピーク値)である。

【0006】

図17は、図18に示す回路モデルで三相インバータINVに400[v]の直流電圧(以下、「バス電圧」という。)を入力し、変調度M=1のPWM信号を三相インバータINVに入力した場合の出力電圧に含まれる周波数成分をFFT解析したものである。

【0007】

なお、回路モデルではフィルタ回路は省略し、三相インバータINVに対する負荷を5Ωとしている。また、PWM信号は、特開2010−136567号公報に記載の変調波を4.8[kHz]の三角波(搬送波)とレベル比較して生成されるパルス信号である。同公報に記載の変調波は、1周期を均等に3つの区間I,II,IIIに分け、区間Iは、相電圧から一つ前の相電圧を差し引いて得られる線間電圧の波形を有し、区間Iに続く区間IIは、相電圧から一つ後の相電圧を差し引いて得られる線間電圧の波形を有し、区間IIに続く区間IIIは、ゼロレベルの波形を有する信号である。インバータINVから出力させるU,V,Wの各相の相電圧をvu,vv,vwとすると、例えば、U相の変調波vu’は、−π/6≦θ≦3π/6で線間電圧vuw=vu−vw、3π/6≦θ≦7π/6で線間電圧vuv=vu−vv、7π/6≦θ≦11π/6で0レベルの波形を有する信号である。

【0008】

図17に示すように、三相インバータINVから出力される線間電圧には基本波成分(変調波の周波数と同一の周波数成分:図17では60[Hz])と、パルス幅変調における搬送波の周波数fc(以下、「キャリア周波数fc」という。)及びその整数倍の周波数(n×fc)と同一の周波数におけるサイドバンドの周波数成分とが含まれる。基本波成分以外の成分がスイッチングノイズの成分であるが、最もレベルの高い成分(以下、「最大ノイズ成分」という。)は、キャリア周波数fc=4.8[kHz]のサイドバンド成分(点Nmax参照)である。

【0009】

図19は、PWM信号の変調度Mを変化させて図17に示すFFT解析を行い、各変調度Mにおける最大ノイズ成分のレベルをプロットしたものである。図19に示すように、スイッチングノイズの特性は、変調度Mが0.55付近で最大となり、0.878で極小点Pminを有する。

【0010】

系統連系インバータ装置は、インバータの出力電圧を電力系統の電圧(以下、「系統電圧」という。)よりも高くして出力電流を電力系統側に出力する(直流電源から供給される電力を電力系統側に出力する)制御を行う。インバータの出力電圧の振幅(ピーク値)を「Vinv」、搬送波の振幅(ピーク値)を「Vc」、変調波の振幅(ピーク値)を「Vs」とすると、変調度Mは、M=Vs/Vcで表わされ、インバータのバス電圧を「Vdc」、三角波比較方式によるパルス幅変調の電圧利用率などの係数を「k」とすると、Vinv=k×M×Vdcの関係がある。電力系統に連系されているときには、系統連系インバータ装置は、インバータの出力電圧Vinvを系統電圧対抗分(系統電圧Vgと同一の電圧)以上に制御するから、Vg≦k×M×Vdcとなる。従って、系統連系インバータ装置では、変調度Mは、(Vg/k×Vdc)≦M≦1の範囲で変動し、フルレンジで変動することはない。

【0011】

例えば、202v系の電力系統に連系させる場合、バス電圧Vdcを系統電圧が規定値よりも10%上昇した場合でもフルブリッジ回路で構成されるインバータから定格電力が出力できる電圧に設定するとすれば、そのバス電圧Vdcは、

Vdc=[(202×1.1)×√(2)×0.866]×1.1×2/√(3)

≒345.7 …(1)

となる。

【0012】

(1)式において、「202」は、系統電圧(電力系統の線間電圧)vgの実効値Vrmsである。系統電圧の実効値Vrmsを1.1倍しているのは、系統電圧が10%上昇した場合でも定格電力が出力できることを反映したものである。また、「√(2)」を掛ける処理は瞬時値に変換するための処理であり、「0.866」を掛ける処理は、変調波に三次高調波成分を加算した場合、電圧利用率が0.866に改善されることに基づく処理である。また、波括弧内の値を1.1倍しているのは、フィルタにおける電圧降下分と制御量分を加味した処理であり、「2」を掛ける処理は、フルブリッジ回路のインバータから出力される交流電圧の正負の振幅が入力電圧の振幅の2倍になることに基づく処理である。また、「√(3)」で割る処理は線間電圧を相電圧にするための処理である。なお、デッドタイムなどの影響は無視している。

【0013】

系統電圧vgのレベルが許容範囲(±10%)の下限値に低下したときに電力系統への連系を可能にするバス電圧Vdcを算出すると、この場合は、インバータの出力電圧vinvが系統電圧対抗分だけとなるから、(1)式でフィルタにおける電圧降下分の係数を除去し、系統電圧の変動分の係数を1.1から0.9に変更することにより、

Vdc=[(202×0.9)×√(2)×0.866]×2/√(3)

≒257.4 …(2)

となる。

【0014】

従って、202v系の電力系統に連系させる系統連系インバータ装置でバス電圧Vdcを「345.7[v]」に設定した場合、変調度Mの変動範囲の最小値は、

M=257.4/345.7≒0.745 …(3)

で求められ、変調度Mの変動範囲は0.745〜1.00となる。

【0015】

そして、系統連系インバータ装置に特開2010−136567号公報に記載の変調方式を用いた場合は、変調度Mは0.745〜1.00の範囲で変動するから、M=0.878でスイッチングノイズが最小になる特性を有する。

【0016】

図20は、従来の系統連系インバータ装置の基本的な構成の一例を示すブロック図である。

【0017】

図20に示す系統連系インバータ装置100は、直流電源として太陽電池102を用いたものであり、インバータ104の入力電圧Vdc(バス電圧Vdc)を所定のバス電圧基準値Vrefに安定化させるために太陽電池102とインバータ104の間にDC/DCコンバータ103が設けられている。

【0018】

インバータ104は、6個のスイッチング素子を2個ずつ直列に接続した3組の直列回路(以下、「アーム」という。)を太陽電池102から直流電力が供給される入力ラインに並列に接続した三相フルブリッジ回路で構成される電圧型のインバータ(図18の三相インバータINV参照)である。インバータ104は、コントローラ107から入力される6個のPWM信号で各アーム内の2個のスイッチング素子を交互にオン・オフ動作させてバス電圧VdcをU,V,Wの各相の交流電圧vu,vv,vwに変換する。なお、大文字の符号「V」は直流電圧を示し、小文字の符号「v」は交流電圧を示している。また、交流電圧vu,vv,vwの添え字の「u,v,w」は、それぞれ対応する相を示している。

【0019】

コントローラ107は、マイクロコンピュータで構成され、ディジタル演算処理によりPWM信号の生成処理を行う。コントローラ107は、U,V,Wの各相について、インバータ104の出力電圧の制御目標vuo,vvo,vwo(フィルタ105を通過した正弦波の交流電圧)を変調波として生成し、その制御目標vuo,vvo,vwoを搬送波である所定の三角波vtと比較することによりPWM信号を生成する。なお、コントローラ107は、所定の周期でPWM信号の生成処理を行うので、制御目標vuo,vvo,vwoと三角波vtの瞬時値を生成し、両瞬時値を比較してPWM信号の瞬時値(ハイレベル若しくはローレベル)を出力する。

【0020】

U相の制御目標vuoは、インバータ104の出力電流iuがインバータ104と電力系統101との間のインピーダンス(主としてフィルタ105と変圧器106のリアクトルによるインピーダンス。以下、「連系用リアクトル」という。)を流れることによる電圧降下分の電圧を系統電圧にベクトル合成した電圧の振幅に相当する。系統電圧は電力系統101により制御されるので、コントローラ107は、連系用リアクトルの電圧を制御することにより制御目標vuoを制御する。連系用リアクトルのインピーダンスはフィルタ105及び変圧器106の設計値として固定されるから、連系用リアクトルの電圧は、インバータ104の出力電流iuにより制御される。従って、コントローラ107は、実質的にインバータ104の出力電流iuを制御することによって制御目標vuoを制御する。V相,W相の制御目標vuoについても同様である。

【0021】

コントローラ107内のバス電圧指令値生成部107a、無効電力指令値生成部107b、無効電力算出部107c、uvw−dq変換部107d、PI補償部107e,107f,107g,107h、非干渉化部107i,107j、dq−uvw変換部107kは出力電圧の制御目標vuo,vvo,vwoを生成するための処理ブロックである。また、PWM信号生成部107mは、制御目標vuo,vvo,vwoと三角波vtを比較してPWM信号を生成するための処理ブロックである。なお、dq−uvw変換部107kの前段若しくは後段に系統電圧対抗分を加算する処理ブロックが設けられるが、図20ではその処理ブロックを省略している。

【0022】

コントローラ107は、dq回転座標系でインバータ104の出力電流の制御目標Ido,Iqoを生成する。すなわち、コントローラ107は、バス電圧指令値生成部107aでバス電圧基準値Vrefを設定し、そのバス電圧基準値Vrefに対する直流電圧計108で実測されるバス電圧Vdcの偏差ΔVdc=Vref−Vdcを求め、その偏差ΔVdcに所定のPI補償の演算をしてインバータ104の出力電流の制御基準のdq回転座標系におけるd軸成分Idrefを設定する。d軸成分Idrefの制御は、インバータ104のバス電圧Vdcを所定のバス電圧基準値Vrefに安定化するための制御である。

【0023】

また、コントローラ107は、無効電力指令値生成部107bで無効電力指令値Qo(力率1の運転時ではQo=0)を設定するとともに、交流電圧計109で実測されるインバータ104の出力電圧vu,vv,vw及び交流電流計110で実測されるインバータ104の出力電流iu,iv,iwを用いて無効電力演算部107cでインバータ104から出力される無効電力Qrを算出する。そして、コントローラ107は、無効電力指令値Qoに対する無効電力演算部107cの無効電力算出値Qrの偏差ΔQ=Qo−Qrを求め、その偏差ΔQに所定のPI補償の演算をしてインバータ104の出力電流の制御基準のdq回転座標系におけるq軸成分Iqrefを設定する。q軸成分Iqrefの制御は、インバータ104から出力される無効電力を指令した無効電力量にするための制御である。

【0024】

更に、コントローラ107は、交流電流計110で検出したインバータ104の出力電流iu,iv,iwをuvw−dq変換部107dで下記(4)式に示すuvw−dq座標変換式によりdq回転座標系のd軸成分Idとq軸成分Iqに変換し、制御基準Idref,Iqrefに対するインバータ104の出力電流の実測値Id,Iqの偏差ΔId=Idref−Id,ΔIq=Iqref−Iqをそれぞれ算出する。

【0025】

【数1】

【0026】

更に、コントローラ107は、偏差ΔIdに所定のPI補償の演算をするとともに、インバータ104の出力電流の実測値Iqにフィルタ105のインピーダンス成分ωLを乗じて干渉量を演算し、その演算値を偏差ΔIdのPI補償演算値に加算してインバータ104の出力電流の制御目標のdq回転座標系におけるd軸成分Idoを設定する。また、コントローラ107は、偏差ΔIqに所定のPI補償の演算をするとともに、インバータ104の出力電流の実測値Idにフィルタ105のインピーダンス成分ωLを乗じて干渉量を演算し、その演算値を偏差ΔIqのPI補償演算値から減算してインバータ104の出力電流の制御目標のdq回転座標系におけるq軸成分Iqoを設定する。

【0027】

そして、コントローラ107は、その制御目標Ido,Iqoに図略の系統電圧対抗分をそれぞれ加算してインバータ104の出力電圧のdq回転座標系における制御目標Vdo,Vqoを算出し、その制御目標Vdo,Vqoをdq−uvw変換部107kで下記(5)式に示すdq−uvw座標変換式により三相電圧に変換することで、U,V,Wの各相の制御目標vuo,vvo,vwoを生成する。

【0028】

【数2】

【0029】

そして、コントローラ107は、PWM信号生成部107mで制御目標vuo,vvo,vwoのレベルをそれぞれ三角波vtのレベルと比較し、比較結果に応じたレベルのパルス信号を生成することでU,V,Wの各相に対するPWM信号を生成する。

【先行技術文献】

【特許文献】

【0030】

【特許文献1】特開2004−260942号公報

【特許文献2】特開2006−101581号公報

【特許文献3】特開2007−037256号公報

【発明の概要】

【発明が解決しようとする課題】

【0031】

系統連系インバータ装置100では、インバータ104におけるスイッチング損失を可及的に抑制して高効率で電力系統101に電力を供給することが求められる。また、系統連系インバータ装置100では、フィルタ105を構成するインダクタ及びキャパシタの各素子を可及的に小型、軽量にして装置全体の小型化、軽量化、低コスト化が求められる。

【0032】

フィルタ105を構成するインダクタ及びキャパシタの各素子の値は、インバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさによって決定される。従って、コントローラ107によるインバータ104の制御をスイッチングノイズの大きさを抑制するようにすれば、フィルタ105を構成する各素子の小型化、軽量化に繋がり、系統連系インバータ装置100の小型化、軽量化、低コスト化に寄与する。

【0033】

しかし、従来のインバータ104の制御では、インバータ104のバス電圧Vdcを所定のバス電圧基準値Vrefにするように、インバータ104の出力電流iu,iv,iwを制御するので、コントローラ107で生成されるPWM信号の変調度Mが変動し、それに応じてインバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさも変動する。従って、フィルタ105を構成するインダクタ及びキャパシタは、スイッチングノイズの大きさの変動幅の最大値に基づいて選定する必要があり、フィルタ105の小型化、軽量化が困難となっている。

【0034】

また、コントローラ107の制御系には電流マイナーループ(uvw−dq変換部107d、PI補償部107g,107h、非干渉化部107i,107j及びdq−uvw変換部107kによる処理部分)が含まれるので、制御系の構成も複雑になる。

【0035】

PWM信号の変調度Mを、インバータ104から出力される交流電圧vu,vv,vw及び交流電流iu,iv,iwに含まれるスイッチングノイズの大きさが変動範囲の最小となる値に固定すれば、スイッチングノイズの大きさが従来よりも抑制されるので、フィルタ105の更なる小型化及び軽量化が可能になる。また、変調度Mを固定する制御は、インバータ104の出力電流の制御目標のdq回転座標系におけるd軸成分Idoを固定する制御に相当するから、従来のように電流マイナーループによってインバータ104の出力電流を制御目標の変動に追従させる制御も不要になり、制御系の簡素化も期待できる。

【0036】

本発明は、コントローラの制御系をPWM信号の変調度を所定値に固定する制御系とすることによって制御系の簡素化を可能にするとともに、装置の小型化、軽量化、低コスト化を図ることができる系統連系インバータ装置を提供することを目的とする。

【課題を解決するための手段】

【0037】

上記課題を解決するため、本発明では、次の技術的手段を講じている。

【0038】

本発明によって提供される系統連系インバータ装置は、複数のスイッチング素子を有し、これらのスイッチング素子により前記直流電源から供給される直流電力を断続することで交流電力に逆変換する電力逆変換手段と、前記電力逆変換手段の出力信号に含まれるスイッチングノイズを除去して電力系統に出力するノイズ除去手段と、前記複数のスイッチ素子をオン・オフ駆動するパルス幅変調信号を制御することによって前記電力逆変換手段の電力逆変換動作を制御する制御手段と、を備えた系統連系インバータ装置において、前記制御手段は、前記パルス幅変調信号の変調度が予め設定された変調度となる振幅の変調波を生成する変調波生成手段と、前記変調波生成手段で生成された変調波を用いて前記パルス幅変調信号を生成するパルス幅変調信号生成手段と、を備えたことを特徴とする(請求項1)。

【0039】

なお、上記の系統連系インバータ装置において、前記変調波生成手段は、前記変調波の波形データを記憶した記憶手段と、前記電力系統に出力される無効電力を検出し、その検出値を前記無効電力の制御目標にするための位相を算出する位相算出手段と、前記記憶手段から読み出した前記変調波の波形データの位相を前記位相算出手段で算出した位相で補正して前記パルス幅変調信号を生成するための変調波を生成する位相補正手段と、を含む構成にするとよい(請求項2)。

【0040】

また、請求項1又は2に記載の系統連系インバータ装置において、前記電力逆変換手段は、三相インバータで構成され、前記変調波生成手段は、各相の変調波として、1/3周期の期間が各相の相電圧から当該相より相順が1つ前の相電圧を差し引いて得られる線間電圧の波形となり、続く1/3周期の期間が各相の相電圧から当該相より相順が1つ後の相電圧を差し引いて得られる線間電圧の波形となる波形となり、残りの1/3周期の期間がゼロとなる波形を有する制御目標を生成するとよい(請求項3)。

【0041】

また、請求項1又は2に記載の系統連系インバータ装置において、前記電力逆変換手段は、三相インバータで構成され、前記変調波生成手段は、各相の変調波として前記三相インバータから出力される相電圧の制御目標を生成するとよい(請求項4)。

【0042】

また、請求項3に記載の系統連系インバータ装置において、相毎に前記変調波生成手段で生成された制御目標の三次高調波を生成する三次高調波生成手段と、前記変調波生成手段で生成された各相の前記制御目標に前記三次高調波生成手段で生成された各相に対応する三次高調波を加算する信号加算手段と、を更に備え、前記パルス幅変調信号生成手段は、相毎に前記制御目標に代えて前記信号加算手段から出力される信号を用いて前記パルス幅変調信号を生成するとよい(請求項5)。

【0043】

また、上記の系統連系インバータ装置において、予め設定された変調度は、0.7から1.0の間の値に設定されるとよい(請求項6)。

【0044】

また、上記の系統連系インバータ装置において、前記パルス幅変調信号生成手段は、前記変調波生成手段で生成された変調波のレベルと所定の三角波のレベルを比較することにより前記パルス幅変調信号を生成するとよい(請求項7)。

【発明の効果】

【0045】

本発明によれば、パルス幅変調信号を生成するための変調波として、パルス幅変調信号の変調度が予め設定された変調度となる所定の変調波を生成し、その変調波を用いてパルス幅変調信号を生成するので、例えば、パルス幅変調信号の変調度をスイッチングノイズやコモンモードノイズを最も小さくすることができる変調度にすることによって、系統連系インバータ装置のスイッチングノイズやコモンモードノイズを抑制することができる。

【0046】

また、ノイズ除去手段の特性を従来よりも緩和できるので、ノイズ除去手段の小型化、軽量化が可能になり、系統連系インバータ装置の小型・軽量化及び低コスト化を図ることができる。

【0047】

また、パルス幅変調信号の変調度を固定する制御を行うので、従来の電流マイナーループによる制御系が不要になる。これにより、制御手段における制御の安定性や過渡特性が向上する。また、電力逆変換手段に供給される直流電圧のレベルが変動したり、ノイズ除去手段での電圧降下が変化したりした場合でもパルス幅変調信号の変調度は一定になるので、パルス幅変調信号を生成する際の電圧利用率を一定にすることができる。

【図面の簡単な説明】

【0048】

【図1】本発明に係る系統連系インバータ装置のブロック構成を示す図である。

【図2】DC/DCコンバータの回路構成の一例を示す図である。

【図3】インバータの回路構成の一例を示す図である。

【図4】正弦波の変調波を用いた三角波比較方式によりPWM信号を生成する第1のパルス幅変調方式を説明するための図である。

【図5】非正弦波の変調波を用いた三角波比較方式によりPWM信号を生成する第2のパルス幅変調方式を説明するための図である。

【図6】変調波生成部が第2のパルス幅変調方式で変調波を生成する場合の変調波の波形を説明するための図である。

【図7】図18に示す回路モデルで従来の方法1,2と本発明の方法の3種類についてPWM制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした結果である。

【図8】シミュレーション1の条件で従来の方法1によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図9】シミュレーション1の条件で従来の方法2によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図10】シミュレーション1の条件で本発明の方法によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。

【図11】第1のパルス幅変調方式で変調度M=1のPWM信号を生成した時のインバータの出力電圧に含まれるスイッチングノイズをFFT解析した結果を示す図である。

【図12】第1のパルス幅変調方式で生成したPWM信号を用いてインバータを駆動した場合のインバータの出力電圧に含まれるスイッチングノイズと変調度Mの関係を示す図である。

【図13】図18に示す回路モデルの三相負荷の中性点に交流電圧計を設けた構成で、第2のパルス幅変調方式によりバス電圧の制御値を400[v]、変調度Mを「1.0」に固定する制御をした場合のインバータの出力電圧に含まれるコモンモードノイズをFFT解析した結果を示す図である。

【図14】変調度Mを「0.8」に変更して図13と同様のFFT解析をした結果を示す図である。

【図15】バス電圧の制御値を300[v]に変更して図13と同様のFFT解析をした結果を示す図である。

【図16】バス電圧の制御値を300[v]、変調度Mを「0.8」に変更して図13と同様のFFT解析をした結果を示す図である。

【図17】変調度M=1のPWM信号で三相インバータを動作させた時の三相インバータの出力電圧に含まれるスイッチングノイズをFFT解析したスペクラム分布の一例を示す図である。

【図18】図17に示すFFT解析を行った系統連系インバータ装置の回路モデルを示す図である。

【図19】変調波の振幅を変化させて図17に示すFFT解析を行い、各変調度Mにおける最大ノイズ成分のレベルをプロットした図である。

【図20】従来の系統連系インバータ装置の基本的な構成の一例を示すブロック図である。

【発明を実施するための形態】

【0049】

本発明に係る系統連系インバータ装置を図1乃至図16を用いて説明する。

【0050】

図1は、本発明に係る系統連系インバータ装置のブロック構成を示す図である。

【0051】

図1に示す系統連系インバータ装置1は、太陽電池2を電力源とするインバータ装置である。また、図2と図3は、それぞれ系統連系インバータ装置1内のDC/DCコンバータ3とインバータ4の回路構成の一例を示す図である。

【0052】

系統連系インバータ装置1は、基本的なブロック構成として太陽電池2、DC/DCコンバータ3、インバータ4、フィルタ5、変圧器6及びコントローラ7を備え、変圧器6の出力端は遮断器10を介して電力系統11に接続される。また、変圧器6の出力端には系統連系インバータ装置1から出力されるU,V,Wの各相の交流電圧vu,vv,vwと交流電流iu,iv,iwの実測値をコントローラ7に入力するために交流電圧計8と交流電流計9とが設けられている。

【0053】

太陽電池2は、太陽からの光エネルギーを電気エネルギーに変換する電力源として機能する。直流電源としては、太陽電池2に代えて、燃料電池等の他の直流電源を用いることができる。太陽電池2は、山形の電力−電圧特性を有し、動作点が最大電力点からずれると、出力電力が減少する特性を有する。また、最大電力点は日射量によって変化するので、系統連系インバータ装置1では、一般に太陽電池2の動作点が最大電力点を追尾する(すなわち、出力電圧を最大電力点電圧にする)MPPT制御(Maximum Power Point Tracking、最大電力点追尾制御)が行われる。

【0054】

DC/DCコンバータ3は、インバータ4に入力される直流電圧(バス電圧)Vdcを所定のバス電圧基準値Vrefに安定化させる機能を果たす。DC/DCコンバータ3は、太陽電池2から出力される直流電圧Vsをバス電圧基準値Vrefに昇圧する。図1ではDC/DCコンバータ3のコントローラを省略しているが、コントローラ7は、インバータ4のバス電圧Vdcがバス電圧基準値Vrefに固定されるように制御するので、DC/DCコンバータ3のコントローラは、DC/DCコンバータ3の入力電圧、すなわち、太陽電池2の直流電圧Vsが最大電力点電圧を追尾するように制御する。

【0055】

DC/DCコンバータ3は、例えば、図2に示す周知の昇圧型コンバータである。昇圧型DC/DCコンバータは、スイッチング素子Qを所定の周期でオン・オフさせることにより、オン期間に太陽電池2からの電気エネルギーを磁気エネルギーに変換してチョークコイルLに蓄積し、オフ期間にその磁気エネルギーを再度電気エネルギーに変換してダイオードDを介してコンデンサCに出力する動作を繰り返す。スイッチング素子Qとしては、バイポーラ・トランジスタ、FET(Field Effect Transistor)、サイリスタ、IGBT(Insulated Gate Bipolar Transistor)等の各種の半導体スイッチング素子が利用される。

【0056】

インバータ4は、太陽電池2からDC/DCコンバータ3を介して入力される直流電力を三相交流電力に逆変換して電力系統11に出力する。インバータ4は、図3に示すように、6個のスイッチング素子Q1a,Q1b,Q2a,Q2b,Q3a,Q3bを用いた三相フルブリッジ回路で構成される三相インバータである。6個のスイッチング素子Qka,Qkb(k=1,2,3)もDC/DCコンバータ3のスイッチング素子Qと同様に上記の各種の半導体スイッチング素子を使用することができる。

【0057】

三相フルブリッジ回路は、スイッチング素子Q1a,Q1bの直列回路A1、スイッチング素子Q2a,Q2bの直列回路A2及びスイッチング素子Q3a,Q3bの直列回路A3を電源ラインLVに並列接続した構成である。各スイッチング素子Qka,Qkbにはそれぞれ帰還ダイオードDka,Dkb(k=1,2,3)が逆並列に接続されている。電源ラインLVにはDC/DCコンバータ3から出力される直流電圧(バス電圧)Vdcが供給される。

【0058】

各直列回路Ak(k=1,2,3)の一対のスイッチング素子Qka,Qkb(k=1,2,3)は、コントローラ7から出力される一対のPWM信号Ska,Skb(k=1,2,3)によってオン・オフ駆動される。PWM信号Skbは、PWM信号Skaに対してレベルが反転している。従って、スイッチング素子Qkaとスイッチング素子Qkbは、PWM信号Ska,Skbによって交互にオン・オフ動作をする。

【0059】

PWM信号Ska,Skbは、コントローラ7によって、インバータ4の出力電圧の制御目標vuo,vvo,vwo(変調波の瞬時値)と変調波よりも高周波の三角波vt(搬送波の瞬時値)とを比較する三角波比較方式により生成される。インバータ4の出力電圧の制御目標vuo,vvo,vwoの波形は互いに位相が2/3πだけずれるから、PWM信号S1a,S1b、PWM信号S2a,S2b及びPWM信号S3a,S3bのパルス幅のパターンは、互いに位相が2π/3だけずれている。各直列回路Akの一対のスイッチング素子Qka,Qkbが一対のPWM信号Ska,Skbによってオン・オフ動作することにより、直列回路A1の接続点n1、直列回路A2の接続点n2及び直列回路A3の接続点n3からそれぞれU相、V相、W相の各相に対する交流電圧vu,vv,vwが出力される。

【0060】

フィルタ5は、インバータ4から出力されるU相、V相、W相の三相交流信号(交流電圧vu,vv,vwと交流電流iu,iv,iw)に含まれるスイッチングノイズを除去する。フィルタ5は、図3に示すように、等価的に接続点n1,n2,n3の出力ラインにそれぞれインダクタLFを接続し、その後段の各出力ライン間にキャパシタCFを接続した逆L型回路で構成される。インバータ4の接続点n1,n2,n3から出力される信号の波形は微小な階段状の変化をするが、フィルタ5を通すことによってスイッチングノイズの成分が除去されるので、インバータ4の出力信号の波形は綺麗な正弦波となる。定常状態では、インバータ4から出力される交流電圧vu,vv,vwの波形は目標値vuo,vvo,vwoの波形となる。

【0061】

変圧器6は、昇圧トランスで構成され、フィルタ5から出力される正弦波の交流電圧のレベルを系統電圧とほぼ同一のレベルに昇圧する。交流電圧計8は、変圧器6から出力されるインバータ4の出力電圧(U,V,Wの各相の相電圧vu,vv,vw)を検出する。また、交流電流計9は、変圧器6から出力されるインバータ4の出力電流(U,V,Wの各相の電流iu,iv,iw)を検出する。交流電圧計8及び交流電流計9の検出値は、コントローラ4に入力され、PWM信号Ska,Skbの生成処理に利用される。

【0062】

コントローラ7は、マイクロコンピュータ若しくはFPGA(Field-Programmable Gate Array)により構成され、ディジタル演算処理により、所定の周期でインバータ4の出力電圧の制御目標vuo,vvo,vwoと所定の三角波vtとを生成し、相毎に制御目標vuo,vvo,vwoのレベルを三角波vtのレベルと比較してPWM信号Ska,Skb(k=1,2,3)を生成する。搬送波である三角波vtの波形は予め決められている。従って、コントローラ7は、インバータ4の出力電圧の制御目標vuo,vvo,vwoを生成する第1処理部とその制御目標vuo,vvo,vwoのレベルを三角波vtのレベルと比較してPWM信号Ska,Skbを生成する第2処理部とを備える。図1の変調波テーブル7a、力率調整部7b、位相補正部7c及び変調波生成部7dは第1処理部を構成し、PWM信号生成部7eは第2処理部を構成している。

【0063】

本発明は、インバータ4から出力される交流電圧及び交流電流に含まれるスイッチングノイズがPWM信号Ska,Skbの変調度Mによって変化し、スイッチングノイズを好適に抑制にする変調度M*(以下、「最適変調度M*」という。)があることに着目し、第1処理部で生成するインバータ4の出力電圧の制御目標vuo,vvo,vwoの波形を第2処理部で生成されるPWM信号Ska,Skbの変調度Mが最適変調度M*となるように制御する構成に特徴を有する。最適変調度M*は、変調度Mの変動範囲において、スイッチングノイズの最大ノイズ成分が最小になる変調度である。

【0064】

三相インバータにおける三角波比較方式によるPWM信号の生成においては、図4に示すように、インバータの出力電圧の制御目標vuo,vvo,vwoとして、相毎に正弦波の相電圧vmを生成し、振幅の中央のゼロレベルを合わせて三角波vtと比較する方式(以下、「第1のパルス幅変調方式」という。)と、図5に示すように、相毎に、1周期Tを均等に3つの区間I,II,IIIに分け、区間Iと区間IIは線間電圧の波形を有し、区間IIIはレベル「0」の波形を有する電圧vm’を生成し、振幅の最小レベルを合わせて三角波vtと比較する方式(以下、「第2のパルス幅変調方式」という。)と、がある。第1のパルス幅変調方式は、一般的な方法であるが、第2のパルス幅変調方式は、例えば、上述した特開2010−136547号公報に開示されている方式である。

【0065】

本発明は、第1のパルス幅変調方式及び第2のパルス幅変調方式のいずれにも適用可能であるので、まず、コントローラ7が第2のパルス幅変調方式でPWM信号を生成する場合について説明する。第2のパルス幅変調方式でPWM信号Ska,Skbを生成する場合は、例えば、図17〜図19を用いて説明した例では、最適変調度M*は「0.878」である(図19参照)。

【0066】

第2のパルス幅変調方式のU,V,Wの各相の制御目標(変調波)は、図5に示す電圧vm’と同一の波形を有する。インバータ4から出力されるU,V,Wの各相の相電圧の制御目標をvuo,vvo,vwoとすると、U相の制御目標(変調波)vuo’の波形は、図6に示すように、位相(θ+2nπ)(n=0,1,…)に対して、

(a1)−π/6≦θ≦3π/6:vuo’=vuwo=vuo−vwo

(a2)3π/6≦θ≦7π/6:vuo’=vuvo=vuo−vvo

(a3)7π/6≦θ≦11π/6:vuo’=0

の合成をしたものである。

【0067】

また、V相の制御目標(変調波)vvo’の波形は、

(b1)−π/6≦θ≦3π/6:vvo’=vvwo=vvo−vwo

(b2)3π/6≦θ≦7π/6:vvo’=0

(b3)7π/6≦θ≦11π/6:vvo’=vvuo=vvo−vuo

の合成をしたものである。

【0068】

また、W相の制御目標(変調波)vwo’の波形は、

(c1)−π/6≦θ≦3π/6:vwo’=0

(c2)3π/6≦θ≦7π/6:vwo’=vwvo=vwo−vvo

(c3)7π/6≦θ≦11π/6:vwo’=vwuo=vwo−vuo

の合成をしたものである。

【0069】

インバータ4の出力電圧の制御目標vuo’,vvo’,vwo’を生成するためのU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoは、インバータ4の出力電流の制御目標iuo,ivo,iwoが連系用リアクトルを流れることによる電圧降下分の電圧を系統電圧にベクトル合成することによって得られる。本発明に係る系統連系インバータ装置1では、変調波の振幅を最適変調度M*の振幅に固定するので、各相の相電圧の制御目標vuo,vvo,vwoも最適変調度M*に基づき予め設定することができる。そこで、本実施形態では、最適変調度M*に基づいて各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを予め設定している。

【0070】

そして、本実施形態では、αβ座標系における制御目標(Vαo,Vβo)に対して、インバータ4から出力される無効電力を無効電力指令値に追随させるための位相補正とαβ−uvw座標変換とを行ってU,V,Wの各相の制御目標(変調波)vuo’,vvo’,vwo’を生成するようにしている。

【0071】

コントローラ7は、上記の処理をするための機能ブロックとして、変調波テーブル7a、力率調整部7b、位相補正部7c、変調波生成部7d及びPWM信号生成部7eを備える。変調波テーブル7aは、最適変調度M*に基づいて予め設定された各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータを記憶するブロックである。

【0072】

力率調整部7bは、交流電圧計8で検出されるインバータ4の出力電圧vu,vv,vwと交流電流計9で検出されるインバータ4の出力電流iu,iv,iwとを用いてインバータ4から出力される無効電力Qを算出し、その算出値Qから無効電力Qを無効電力指令値Qo(力率1の運転時ではQo=0)にするための位相θを算出する。

【0073】

位相補正部7cは、変調波テーブル7aから各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを読み出し、力率調整部7bで算出された位相θを用いて下記(6’)式に示す演算式により上記の位相補正とαβ−uvw座標変換の演算処理を行い、U,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを生成する。

【0074】

【数3】

【0075】

なお、(6)式において、θの行列は、αβ座標系における電圧ベクトルの位相を位相θだけ進めたり、遅らせたりするための演算処理である。0<θであれば、電圧ベクトルの位相は進み位相に補正され、θ<0であれば、電圧ベクトルの位相は遅れ位相に補正される。

【0076】

変調波生成部7dは、位相補正部7cで生成されるU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを用いて上記の(a1)〜(a3)、(b1)〜(b3)、(c1)〜(c3)の合成処理をすることによりU,V,Wの各相の変調波vuo’,vvo’,vwo’を生成し、PWM信号生成部7eに入力する。

【0077】

PWM信号生成部7eは、振幅Vcを有する高周波の三角波vtを生成し、三角波vtの最小レベル(−Vc)とU,V,Wの各相の変調波vuo’,vvo’,vwo’のゼロレベルを合わせてそれぞれレベルを比較してインバータ4の直列回路A1,A2,A3に対するPMW信号S1a,S2a,S3aを生成する。また、PWM信号生成部7eは、PMW信号S1a,S2a,S3aのレベルを反転することによりPMW信号S1b,S2b,S3bを生成する。そして、PWM信号生成部7eは、そのPMW信号S1a,S2a,S3a,S1b,S2b,S3bをインバータ4に入力する。

【0078】

なお、変調波生成部7dから入力される変調波vuo’,vvo’,vwo’の振幅Vm(Vmは相電圧の制御目標vuo,vvo,vwoの振幅)と三角波vtの振幅Vcとの間には、Vm/Vc=M*=0.878の関係がある。従って、変調波テーブル7aに記憶されている各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータは、変調波生成部7dで生成される変調波vuo’,vvo’,vwo’の振幅がVm/Vc=M*を満たすように予め設定されている。

【0079】

次に、本実施形態に係る系統連系インバータ装置1の特徴的な構成の作用・効果について説明する。

【0080】

コントローラ7は、系統連系インバータ装置1を電力系統11に連系させた後は、太陽電池2から供給される直流電力をインバータ4で交流電力に変換して電力系統11に出力する制御をする。従来の系統連系インバータ装置100は、インバータ104のバス電圧Vdcをバス電圧基準値Vrefに保持するように、インバータ104の出力電流の制御目標を設定し、電流マイナーループによってインバータ104の出力電流iu,iv,iwを制御目標に制御している。このため、従来の系統連系インバータ装置100では、PWM信号生成部107mで生成されるPWM信号の変調度Mが変動し、その変調度Mの変動に基づきスイッチングノイズも大きく変動する。

【0081】

これに対し、系統連系インバータ装置1は、変調度Mをスイッチングノイズの最大ノイズ成分が最も小さくなる最適変調度M*に固定し、インバータ4の出力電流iu,iv,iwを固定する制御をしているので、スイッチングノイズを最小の状態に抑制することができる。

【0082】

図7は、図18に示す回路モデルで従来の方法1,2と本発明の方法の3種類についてPWM制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレーションした結果である。

【0083】

シミュレーション1は、キャリア周波数fc=4.8[kHz]、系統周波数fg=60[Hz]、電力系統11の線間電圧の実効値Vrms=202[v]、インバータINVから定格電力を出力したときのフィルタでの電圧降下分5%の条件で、従来の方法1、従来の方法2及び本発明の方法のそれぞれについて定常状態でのスイッチングノイズの最大ノイズ成分の発生状況をシミュレートしたものである。

【0084】

従来の方法1は、図17を用いて説明したシミュレーションのPWM制御方法に相当し、バス電圧Vdcを(1)式に示す電圧(345.7[v])に制御する方法である。従来の方法2は、バス電圧Vdcを電力系統11に連系可能な最小値に設定する場合のPWM制御方法である。また、本発明の方法は、PWM信号の変調度Mを最適変調度M*(=0.878)に固定するPWM制御方法である。スイッチングノイズの大きさはバス電圧Vdcが低いほど低くなるようなイメージがあるので、バス電圧Vdcを最も厳しい条件に設定した場合と本発明の方法とでいずれがスイッチングノイズを抑制できるかを検証するために、今回のシミュレーションでは従来の方法2を加えている。

【0085】

従来の方法1では、バス電圧Vdcは、345.7[v]に制御される。一方、従来の方法2では、バス電圧Vdcは、実効値Vrms=202[v]の電力系統に定格電力を出力するために必要な最小のバス電圧値となるので、

Vdc=(202×√(2)×0.866]×2×1.05/√(3)

≒299.9[v] …(7)

となる。(7)式は、(1)式の係数「1.1」をなくし、フィルタ5の電圧降下分の係数「1.1」を定格出力時のフィルタでの電圧降下分5%の条件である係数「1.05」に変更したものである。

【0086】

インバータの出力電圧Vinv、変調度M及びバス電圧Vdcの間にはVinv=k×M×Vdc(kは電圧利用率などの諸係数)の関係がある。従来の方法2では電力系統に連系させるために必要なバス電圧が最小値に制御されるので、従来の方法2の変調率M2は「1」となる。これに対し、従来の方法1ではバス電圧Vdcが345.7[v]に設定されるので、従来の方法1の変調率M1はM1=299.9/345.7≒0.867となる。一方、本発明の方法は、変調度M3を最適変調度M*=0.878に設定するので、バス電圧VdcはVdc=299.9/M*=299.9/0.878=341.6[v]に制御されることになる。

【0087】

シミュレーション2は、シミュレーション1に対して系統電圧が許容範囲(±10%)の上限値(Vrms=222[v])に上昇した場合に条件を変更したものであり、シミュレーション3は、シミュレーション1に対して系統電圧が許容範囲(±10%)の下限値(Vrms=182[v])に低下した場合に条件を変更したものである。

【0088】

シミュレーション2ではシミュレーション1に対して系統電圧が1.1倍になるので、従来の方法2のバス電圧Vdcもシミュレーション1の場合の1.1倍となる。一方、シミュレーション3ではシミュレーション1に対して系統電圧が0.9倍になるので、従来の方法2のバス電圧Vdcもシミュレーション1の場合の0.9倍となる。

【0089】

従って、シミュレーション2のバス電圧Vdcは、

Vdc=(202×1.1×√(2)×0.866]×2×1.05/√(3)

≒329.6[v] …(8)

となる。

【0090】

また、シミュレーション3のバス電圧Vdcは、

Vdc=(202×0.9×√(2)×0.866]×2×1.05/√(3)

≒270.2[v] …(9)

となる。また、本発明の方法のシミュレーション2,3のバス電圧Vdcは、(8)式,(9)式の演算値を1/0.878倍したものであり、それぞれ375.5[v]、307.8[v]となる。

【0091】

従って、従来の方法1の変調度M1は、シミュレーション2ではM1=329.9/345.7≒0.953に上昇し、シミュレーション3ではM1=270.0/345.7≒0.782に低下する。なお、従来の方法2の変調度M2と本発明の変調度M3は、シミュレーション1の場合と変わらず、それぞれ「1」と「0.878」である。

【0092】

図8〜図10は、シミュレーション1の条件で従来の方法1、従来の方法2及び本発明の方法によりPWM変調制御を行った場合のスイッチングノイズの最大ノイズ成分の発生状況をシミュレートした波形図である。図8は、従来の方法1によるPWM変調制御の場合、図9は、従来の方法2によるPWM変調制御の場合、図10は、本発明の方法によるPWM変調制御の場合の波形図であり、図7のシミュレーション1のNmax1,Nmax2,Nmax3は、図8〜図10の各波形図に示す最大ノイズ成分Nmax1,Nmax2,Nmax3の値を記載したものである。

【0093】

また、シミュレーション4〜6は、それぞれシミュレーション1〜3でインバータの出力電圧を系統電圧対抗分だけにしたものである。シミュレーション4〜6では、インバータから電流が出力されず、フィルタでの電圧降下が生じないから、シミュレーション4〜6の従来の方法2のバス電圧Vdcは、それぞれ(7)式〜(9)式で係数「1.05」を除去した演算式により算出される。

【0094】

すなわち、シミュレーション4の従来の方法2のバス電圧Vdcは、

Vdc=(202×√(2)×0.866]×2/√(3)

≒285.7 …(10)

となり、シミュレーション5の従来の方法2のバス電圧Vdcは、

Vdc=(202×1.1×√(2)×0.866]×2/√(3)

≒313.9 …(11)

となり、シミュレーション6の従来の方法2のバス電圧Vdcは、

Vdc=(202×0.9×√(2)×0.866]×2/√(3)

≒257.4 …(12)

となる。

【0095】

また、本発明の方法のシミュレーション4〜6のバス電圧Vdcは、(10)式〜(12)式の演算値を1/0.878倍したものであり、それぞれ325.4[v]、357.6[v]、293.1[v]となる。

【0096】

従って、従来の方法1の変調度M1は、シミュレーション4ではM1=285.7/345.7≒0.826となり、シミュレーション5ではM1=313.9/345.7≒0.908となり、シミュレーション6ではM1=257.4/345.7≒0.745となる。また、従来の方法2の変調度M2と本発明の変調度M3は、シミュレーション1の場合と同様にそれぞれ「1」と「0.878」である。

【0097】

図には示していないが、シミュレーション2〜6についても図8〜図10に示すような波形図が得られ、図7のシミュレーション2〜6のNmax1,Nmax2,Nmax3もその波形図における最大ノイズ成分Nmax1,Nmax2,Nmax3の値を記載したものである。

【0098】

図7によれば、シミュレーション1,2,5では従来の方法2の方が従来の方法1よりもスイッチングノイズの最大ノイズ成分が大きく、バス電圧Vdcが低いほど最大ノイズ成分が低くなるとは一概に言えないことが分かる。そして、シミュレーション1〜6のいずれの場合も変調度Mを最適変調度M*に制御する本発明の方法がスイッチングノイズを最も小さく制御できることが分かる。

【0099】

以上より、変調度Mを最適変調度M*に制御する系統連系インバータ装置1は、系統電圧のレベルが許容範囲内に制御されている状態で、インバータ4から電力を出力しない場合及びインバータ4から定格電力を出力する場合のいずれの場合でもスイッチングノイズを最小に制御できることが分かる。

【0100】

また、従来の方法1(従来の系統連系インバータ装置100が採用する方法)では、動作条件の変化によって最大ノイズ成分Nmax1のレベルが大きく変動するのに対し、本実施形態に係る系統連系インバータ装置1が採用する変調度Mを最適変調度M*に制御する方法では、動作条件が変化しても最大ノイズ成分Nmax3のレベルは余り変動しない。上記のシミュレーション1〜6では、最大ノイズ成分Nmax1の最小レベルと最大レベルはそれぞれ61.09[v]、92.49[v]で、その変動幅は31.4[v]であるのに対し、最大ノイズ成分Nmax3の最小レベルと最大レベルはそれぞれ49.53[v]、63.46[v]で、その変動幅は13.93[v]である。すなわち、本実施形態に係る系統連系インバータ装置1は、従来の系統連系インバータ装置100に対してスイッチングノイズを最大約50%抑制できる効果がある。

【0101】

従って、本実施形態に係る系統連系インバータ装置1では、スイッチングノイズを可及的に抑制するように制御するので、フィルタ5の周波数特性の減衰傾度を従来の系統連系インバータ装置100のフィルタ105よりも緩和することができ、これによりフィルタ5を構成するインダクタンスLF若しくはキャパシタンスCFの小型化、軽量化を図ることができる。

【0102】

また、系統連系インバータ装置1では、PWM信号生成部7eの変調度Mを最適変調度M*に固定するので、インバータ4の出力電流の制御目標を生成するための制御系や電流マイナーループ等が不要になり、コントローラ4の安定性や過渡特性が向上する。また、系統電圧のレベルが変動したり、フィルタ5での電圧降下分が変化したりしてもPWM信号生成部7eにおけるPWM信号生成処理での電圧利用率を一定に保持することができる。

【0103】

次に、コントローラ7が第1のパルス幅変調方式でPWM信号を生成する場合について説明する。

【0104】

図11は、第1のパルス幅変調方式で変調度M=1のPWM信号を生成した時のインバータの出力電圧をFFT解析した結果を示す図である。図12は、第1のパルス幅変調方式で生成したPWM信号を用いてインバータを駆動した場合のインバータの出力電圧に含まれるスイッチングノイズと変調度Mの関係を解析した結果を示す図である。図11,図12の解析条件は、図17,図19の解析条件と同じである。従って、図11の解析結果は図17の解析結果に対応し、図12の解析結果は図19の解析結果に対応している。

【0105】

図12の特性Aは、キャリア周波数fcのサイドバンド成分の最大値をプロットした特性であり、特性A’は、変調波に三次高調波を注入した場合のキャリア周波数fcのサイドバンド成分の最大値をプロットした特性である。また、特性Bは、キャリア周波数fcの2倍波のサイドバンド成分の最大値をプロットした特性であり、特性B’は、変調波に三次高調波を注入した場合のキャリア周波数fcの2倍波のサイドバンド成分の最大値をプロットした特性である。

【0106】

第2のパルス幅変調方式では、最大ノイズ成分が常にキャリア周波数fc=4.8[kHz]のサイドバンド成分の最大値であり、その最大ノイズ成分のレベルは、変調度Mの変動範囲(0.74〜1.0)では、図19に示したように変調度M*=0.878で極小となる特性を有している。これに対し、第1のパルス幅変調方式では、キャリア周波数fc=4.8[kHz]のサイドバンド成分の最大値は、図12の特性A,A’に示すように、変調度Mの変動範囲(0.74〜1.0)では単調に減少し、極小点を有しない。その一方、キャリア周波数fcの2倍波9.6[kHz]のサイドバンド成分の最大値は、特性B,B’に示すように単調に増加し、特性B(変調波に三次高調波を注入しない場合)では変調度Mが凡そ0.88以上の領域でキャリア周波数fcのサイドバンド成分の最大値よりも大きくなり(特性A,B参照)、特性B’(変調波に三次高調波を注入した場合)では変調度Mが凡そ0.86以上の領域でキャリア周波数fcのサイドバンド成分の最大値よりも大きくなっている(特性A’,B’参照)。

【0107】

第1のパルス幅変調方式でPWM信号を生成するときは、変調度Mが凡そ0.86〜0.88の値よりも小さい場合は最大ノイズ成分がキャリア周波数fcのサイドバンド成分の最大値となるが、変調度Mが凡そ0.86〜0.88の値以上の場合は最大ノイズ成分がキャリア周波数fcの2倍波のサイドバンド成分の最大値となる特性を有する。フィルタ5で最も除去し難いのは、遮断周波数に近いキャリア周波数fcのサイドバンド成分であるので、第1のパルス幅変調方式によるPWM信号の生成でもキャリア周波数fcのサイドバンド成分の最大値が最小になる変調度Mを最適変調度M*に設定することが考えられる。すなわち、第1のパルス幅変調方式では最適変調度M*=1.0に設定することが考えられる。

【0108】

しかしながら、フィルタ5のノイズ除去効率を考えると、フィルタ5にはできるだけ高周波成分を入力しない方が好ましい。この観点から第1のパルス幅変調方式での最適変調度M*を検討すると、キャリア周波数fcのサイドバンド成分の最大値とキャリア周波数fcの2倍波のサイドバンド成分の最大値とが交差する変調度MとM=1.0の範囲で最適変調度M*に選定するのが好ましいと考えられる。従って、変調波に三次高調波を注入しない場合は、M=0.88〜1.0の範囲で最適変調度M*を設定するとよく、変調波に三次高調波を注入する場合は、M=0.86〜1.0の範囲で最適変調度M*を設定するとよい。

【0109】

図1に示す構成で第1のパルス幅変調方式により変調波(正弦波の三相相電圧)を生成する場合は、変調波生成部7dで上記の(a1)〜(a3)、(b1)〜(b3)、(c1)〜(c3)の合成処理は行われず、位相補正部7cで生成されるU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoが各相の変調波として設定される。従って、変調波生成部7dで三次高調波の加算処理を行わない場合は、例えば、最適変調度M*を「0.88」とし、その最適変調度M*に基づいてU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータが予め設定され、変調波テーブル7aに記憶されている。

【0110】

コントローラ7は、変調波テーブル7aから制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを読み出し、力率調整部7bで算出された位相θを用いて(6’)式に示す演算式により位相補正とαβ−uvw座標変換の演算処理を行い、U,V,Wの各相の相電圧の制御目標vuo,vvo,vwoを各相の変調波として生成する。

【0111】

そして、コントローラ7は、その変調波vuo,vvo,vwoをそれぞれ中央のレベル(ゼロレベル)を三角波vtの中央のレベル(ゼロレベル)と合わせてレベル比較することによりPMW信号S1a,S2b,S3cを生成する。また、コントローラ7は、PMW信号S1a,S2a,S3aのレベルを反転することによりPMW信号S1b,S2b,S3bを生成し、そのPMW信号Ska,Skb(k=1,2,3)をインバータ4に入力する。

【0112】

なお、第1のパルス幅変調方式では、電圧利用率を改善するため、変調波生成部7dで三次高調波を加算する処理をしてもよい。すなわち、変調波生成部7dで、位相補正部7cで生成される各相の変調波vuo,vvo,vwoから三次高調波を生成し、各三次高調波を所定の振幅比率(例えば、変調波に対して1/6)で対応する相の変調波vuo,vvo,vwoに加算するようにしてもよい。この場合は、例えば、最適変調度M*を「0.86」とし、その最適変調度M*に基づいてU,V,Wの各相の相電圧の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoのデータが予め設定され、変調波テーブル7aに記憶される。変調波に三次高調波を注入する場合は、電圧利用率を「0.866」に改善することができる。

【0113】

なお、上記実施形態では、変調波テーブル7aにU,V,Wの各相の制御目標vuo,vvo,vwoのαβ座標系におけるα軸成分Vαoとβ軸成分Vβoを記憶しているが、U,V,Wの各相の制御目標vuo,vvo,vwoを記憶するようにしてもよい。この場合は、位相補正部7cでは、下記(13)式に示す演算式により位相補正の演算処理を行ってU,V,Wの各相の制御目標(変調波)vuo’,vvo’,vwo’を生成するとよい。

【0114】

【数4】

【0115】

上記の実施形態では、スイッチングノイズを可及的に低減するという観点から変調度Mを最適変調度M*に固定するようにPWM信号の生成制御をすることを説明したが、スイッチングノイズ以外のノイズ対策の観点でも同様の制御をすることができる。例えば、インバータを用いたパワーエレクトロニクス機器では、EMC(Electro Magnetic Interference)対策としてコモンモードノイズを可及的に低減したいという要求があり、この要求は系統連系インバータ装置でも同様である。

【0116】

図13〜図16は、図18に示す回路モデルの5Ωの三相負荷の中性点に交流電圧計を設けた構成で、第2のパルス幅変調方式によりPWM変調の制御をした場合のインバータINVの出力電圧に含まれるコモンモードノイズを100[kHz]〜1.0[MHz]の範囲でFFT解析したものである。図13は、バス電圧Vdcの制御値を400[v]、変調度Mを「1.0」に制御した場合であり、図14は、バス電圧Vdcの制御値を400[v]、変調度Mを「0.8」に制御した場合である。また、図15は、バス電圧Vdcの制御値を300[v]、変調度Mを「1.0」に制御した場合であり、図16は、バス電圧Vdcの制御値を300[v]、変調度Mを「0.8」に制御した場合である。

【0117】

図13〜図16に示すように、コモンモードノイズは、周波数が高くなるのに応じて指数関数的に低下する。そして、ノイズ成分のレベルは、(Vdc,M)=(400v,0.8)、(400v,1.0)、(300v,0.8)、(300v,1.0)の順に小さくなっている。図示はしていないが、第1のパルス幅変調方式によりPWM変調の制御をした場合をFFT解析したでも同様の傾向が見られる。

【0118】

変調度Mを「1.0」に制御すると、バス電圧基準値Vrefは自動的に小さく制御されるので、コモンモードノイズを抑制する場合は、変調度Mを「1.0」に固定する制御をすれば、スイッチングノイズの場合と同様にコモンモードノイズを従来の変調方法よりも抑制することができる。

【0119】

なお、高調波補償を行う場合は、高調波補償により変調波の振幅に変調度余裕が生じるので、最適変調度M*はM*=(1.0−高調波補償用の変調度余裕分)にするとよい。

【0120】

上記の実施形態では、三角波比較方式によりPWM信号を生成する系統連系インバータ装置について説明したが、本発明は、他の方式によりPWM信号を生成する系統連系インバータ装置にも適用することができる。例えば、WO2009/041276号公報に記載されるPWM信号の生成方式を用いた系統連系インバータ装置にも適用することができる。

【0121】

WO2009/041276号公報に記載のパルス幅変調方式の具体的な内容は同公報に記載されているので、ここでは詳細は省略する。同公報に記載のパルス幅変調方式の要旨は、PWMホールド法を用いて系統連系インバータ装置1のインバータ4〜変圧器6の回路を線形システムにモデル化し、その線形システムにおけるインバータ4の出力電圧を入力とする状態方程式からパルス信号のオン時間(パルス幅)を入力とする状態方程式を導出する。そして、その状態方程式の解を演算することによってパルス信号の各パルスのオン時間をリアルタイムで求めるというものである。すなわち、WO2009/041276号公報に記載のパルス幅変調方式は、入力をパルス信号のオン時間とする状態方程式の解を求める演算式を用いてインバータ4の相電圧の制御目標からPWM信号を直接生成する方式である。

【0122】

従って、本発明は、変調波のレベルをキャリア信号のレベルと比較する処理をしないで、変調波のレベルから直接的にPWM信号を生成する変調方式にも適用することができる。

【符号の説明】

【0123】

1 インバータ装置

2 太陽電池

3 DC/DCコンバータ

4 インバータ

Q1a,Q1b,Q2a,Q2b,Q3a,Q3b スイッチング素子

D1a,D1b,D2a,D2b,D3a,D3b 帰還ダイオード

5 フィルタ

6 変圧器

7 コントローラ

7a 変調波テーブル

7b 力率調整部

7c 位相補正部

7d 変調波生成部

7e PWM信号生成部

8 交流電圧計

9 交流電流計

10 遮断器

11 電力系統

【特許請求の範囲】

【請求項1】

複数のスイッチング素子を有し、これらのスイッチング素子により前記直流電源から供給される直流電力を断続することで交流電力に逆変換する電力逆変換手段と、

前記電力逆変換手段の出力信号に含まれるスイッチングノイズを除去して電力系統に出力するノイズ除去手段と、

前記複数のスイッチ素子をオン・オフ駆動するパルス幅変調信号を制御することによって前記電力逆変換手段の電力逆変換動作を制御する制御手段と、

を備えた系統連系インバータ装置において、

前記制御手段は、

前記パルス幅変調信号の変調度が予め設定された変調度となる振幅の変調波を生成する変調波生成手段と、

前記変調波生成手段で生成された変調波を用いて前記パルス幅変調信号を生成するパルス幅変調信号生成手段と、

を備えたことを特徴とする、系統連系インバータ装置。

【請求項2】

前記変調波生成手段は、

前記変調波の波形データを記憶した記憶手段と、

前記電力系統に出力される無効電力を検出し、その検出値を前記無効電力の制御目標にするための位相を算出する位相算出手段と、

前記記憶手段から読み出した前記変調波の波形データの位相を前記位相算出手段で算出した位相で補正して前記パルス幅変調信号を生成するための変調波を生成する位相補正手段と、

を含む、請求項1に記載の系統連系インバータ装置。

【請求項3】

前記電力逆変換手段は、三相インバータで構成され、

前記変調波生成手段は、各相の変調波として、1/3周期の期間が各相の相電圧から当該相より相順が1つ前の相電圧を差し引いて得られる線間電圧の波形となり、続く1/3周期の期間が各相の相電圧から当該相より相順が1つ後の相電圧を差し引いて得られる線間電圧の波形となる波形となり、残りの1/3周期の期間がゼロとなる波形を有する制御目標を生成する、請求項1又は2に記載の系統連系インバータ装置。

【請求項4】

前記電力逆変換手段は、三相インバータで構成され、

前記変調波生成手段は、各相の変調波として前記三相インバータから出力される相電圧の制御目標を生成する、請求項1又は2に記載の系統連系インバータ装置。

【請求項5】

相毎に前記変調波生成手段で生成された制御目標の三次高調波を生成する三次高調波生成手段と、

前記変調波生成手段で生成された各相の前記制御目標に前記三次高調波生成手段で生成された各相に対応する三次高調波を加算する信号加算手段と、

を更に備え、

前記パルス幅変調信号生成手段は、相毎に前記制御目標に代えて前記信号加算手段から出力される信号を用いて前記パルス幅変調信号を生成する、請求項4に記載の系統連系インバータ装置。

【請求項6】

予め設定された変調度は、0.7から1.0の間の値に設定される、請求項1乃至5のいずれかに記載の系統連系インバータ装置。

【請求項7】

前記パルス幅変調信号生成手段は、前記変調波生成手段で生成された変調波のレベルと所定の三角波のレベルを比較することにより前記パルス幅変調信号を生成する、請求項1乃至6のいずれかに記載の系統連系インバータ装置。

【請求項1】

複数のスイッチング素子を有し、これらのスイッチング素子により前記直流電源から供給される直流電力を断続することで交流電力に逆変換する電力逆変換手段と、

前記電力逆変換手段の出力信号に含まれるスイッチングノイズを除去して電力系統に出力するノイズ除去手段と、

前記複数のスイッチ素子をオン・オフ駆動するパルス幅変調信号を制御することによって前記電力逆変換手段の電力逆変換動作を制御する制御手段と、

を備えた系統連系インバータ装置において、

前記制御手段は、

前記パルス幅変調信号の変調度が予め設定された変調度となる振幅の変調波を生成する変調波生成手段と、

前記変調波生成手段で生成された変調波を用いて前記パルス幅変調信号を生成するパルス幅変調信号生成手段と、

を備えたことを特徴とする、系統連系インバータ装置。

【請求項2】

前記変調波生成手段は、

前記変調波の波形データを記憶した記憶手段と、

前記電力系統に出力される無効電力を検出し、その検出値を前記無効電力の制御目標にするための位相を算出する位相算出手段と、

前記記憶手段から読み出した前記変調波の波形データの位相を前記位相算出手段で算出した位相で補正して前記パルス幅変調信号を生成するための変調波を生成する位相補正手段と、

を含む、請求項1に記載の系統連系インバータ装置。

【請求項3】

前記電力逆変換手段は、三相インバータで構成され、

前記変調波生成手段は、各相の変調波として、1/3周期の期間が各相の相電圧から当該相より相順が1つ前の相電圧を差し引いて得られる線間電圧の波形となり、続く1/3周期の期間が各相の相電圧から当該相より相順が1つ後の相電圧を差し引いて得られる線間電圧の波形となる波形となり、残りの1/3周期の期間がゼロとなる波形を有する制御目標を生成する、請求項1又は2に記載の系統連系インバータ装置。

【請求項4】

前記電力逆変換手段は、三相インバータで構成され、

前記変調波生成手段は、各相の変調波として前記三相インバータから出力される相電圧の制御目標を生成する、請求項1又は2に記載の系統連系インバータ装置。

【請求項5】

相毎に前記変調波生成手段で生成された制御目標の三次高調波を生成する三次高調波生成手段と、

前記変調波生成手段で生成された各相の前記制御目標に前記三次高調波生成手段で生成された各相に対応する三次高調波を加算する信号加算手段と、

を更に備え、

前記パルス幅変調信号生成手段は、相毎に前記制御目標に代えて前記信号加算手段から出力される信号を用いて前記パルス幅変調信号を生成する、請求項4に記載の系統連系インバータ装置。

【請求項6】

予め設定された変調度は、0.7から1.0の間の値に設定される、請求項1乃至5のいずれかに記載の系統連系インバータ装置。

【請求項7】

前記パルス幅変調信号生成手段は、前記変調波生成手段で生成された変調波のレベルと所定の三角波のレベルを比較することにより前記パルス幅変調信号を生成する、請求項1乃至6のいずれかに記載の系統連系インバータ装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19】

【図20】

【公開番号】特開2013−38844(P2013−38844A)

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願番号】特願2011−170899(P2011−170899)

【出願日】平成23年8月4日(2011.8.4)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

【公開日】平成25年2月21日(2013.2.21)

【国際特許分類】

【出願日】平成23年8月4日(2011.8.4)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

[ Back to top ]