電子部品内蔵配線板及びその製造方法

【課題】電子部品内蔵配線板における電気的接続の信頼性を高める。

【解決手段】配線板10が、キャビティR10を有する基板100と、キャビティR10に収容され、電極210、220を有する電子部品200と、電子部品200上に形成された接着層400(絶縁層)と、接着層400に形成された孔401a、402a(ビアホール)内に導体が形成されてなるビア導体401b、402bと、ビア導体401b、402bを介して電極210、220に電気的に接続される導体層301と、を有し、導体層301が、電極210、220の少なくとも1つの外側の縁の直上に面状の導体パターンを有する。

【解決手段】配線板10が、キャビティR10を有する基板100と、キャビティR10に収容され、電極210、220を有する電子部品200と、電子部品200上に形成された接着層400(絶縁層)と、接着層400に形成された孔401a、402a(ビアホール)内に導体が形成されてなるビア導体401b、402bと、ビア導体401b、402bを介して電極210、220に電気的に接続される導体層301と、を有し、導体層301が、電極210、220の少なくとも1つの外側の縁の直上に面状の導体パターンを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電子部品内蔵配線板及びその製造方法に関する。

【背景技術】

【0002】

特許文献1及び特許文献2にはそれぞれ、電極を有する電子部品と、その電子部品上に形成された絶縁層と、その絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、そのビア導体を介して電子部品の電極に電気的に接続される導体層と、を有する電子部品内蔵配線板が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2008/155967号

【特許文献2】特開2003−309373号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、少なくとも片面に導体膜(例えば銅箔)を有する支持材を用いて、その導体膜上に、絶縁性の接着層を介して、電子部品(例えばコンデンサ)を固定し、その電子部品を、支持材に固定されたままコア基板の開口部に配置する電子部品内蔵配線板の製造方法が提案されている。こうした製造方法は、ビア導体等の位置精度を高める上で有効であると考えられる。しかしながら、この方法で、特許文献1又は特許文献2に記載される電子部品内蔵配線板を製造しようとすると、その製造過程において電子部品の電極が損傷する可能性があり、完成した電子部品内蔵配線板の電気的接続について高い信頼性を得ることは困難になる(詳しくは、後述する)。

【0005】

本発明は、こうした実情に鑑みてなされたものであり、電子部品内蔵配線板における電気的接続の信頼性を高めることを目的とする。

【課題を解決するための手段】

【0006】

本発明に係る電子部品内蔵配線板は、収容部を有する基板と、前記収容部に収容され、電極を有する電子部品と、前記電子部品上に形成された絶縁層と、前記絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、前記ビア導体を介して前記電極に電気的に接続される導体層と、を有する電子部品内蔵配線板であって、前記導体層は、前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する。

【0007】

前記導体層は、前記電子部品の外縁近傍における前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、ことが好ましい。

【0008】

前記面状の導体パターンは、前記ビア導体のランドである、ことが好ましい。

【0009】

前記電子部品は、一端近傍に第1電極を、他端近傍に第2電極をそれぞれ有し、前記面状の導体パターンは、前記電子部品の前記一端及び前記他端の少なくとも一方の直上に位置する、ことが好ましい。

【0010】

前記第1電極及び前記第2電極は、前記電子部品の長手方向に並んでいる、ことが好ましい。

【0011】

前記導体層は、前記一端又は前記他端から、前記電子部品の内側及び外側へそれぞれ少なくとも50μmまでの領域に、前記面状の導体パターンを有する、ことが好ましい。

【0012】

前記導体層は、前記電極全域の直上に前記面状の導体パターンを有する、ことが好ましい。

【0013】

前記電極は、前記電子部品の側面と上面と下面とに形成される、ことが好ましい。

【0014】

前記電極の1つが、複数の前記ビア導体を介して、前記ビア導体の1つのランドと接続される、ことが好ましい。

【0015】

前記絶縁層の少なくとも一部は、接着材料からなる、ことが好ましい。

【0016】

前記電子部品は、コンデンサからなる、ことが好ましい。

【0017】

前記面状の導体パターンは、エッチングによりパターニングされる、ことが好ましい。

【0018】

前記面状の導体パターンは、金属箔を含む、ことが好ましい。

【0019】

前記電子部品は、前記電子部品内蔵配線板のコア部に形成された開口部に配置される、ことが好ましい。

【0020】

前記ビアホールは、前記開口部における前記絶縁層に形成される、ことが好ましい。

【0021】

前記コア部上に導体層を有し、前記電極に電気的に接続される導体層は、前記コア部上の導体層と同一の層にある、ことが好ましい。

【0022】

本発明に係る電子部品内蔵配線板の製造方法は、電極を有する電子部品を準備することと、前記電子部品上に絶縁層を形成することと、前記絶縁層にビアホールを形成することと、前記ビアホール内にビア導体を形成することと、前記電極の外側の縁の直上に、少なくとも一箇所で前記ビア導体を介して前記電極に電気的に接続される面状の導体パターンを形成することと、を含む。

【0023】

前記面状の導体パターンを、サブトラクティブ法により形成する、ことが好ましい。

【0024】

前記絶縁層の形成は、少なくとも片面に導体膜を有する支持材を準備することと、前記導体膜上に、絶縁性の接着層を介して、前記電子部品を固定することと、開口部を有する絶縁基板を準備することと、前記接着層により固定された状態の前記電子部品を、前記絶縁基板の前記開口部に配置することと、前記電子部品から前記支持材を取り外すことと、を含む、ことが好ましい。

【発明の効果】

【0025】

本発明によれば、電子部品内蔵配線板における電気的接続の信頼性を高めることが可能になる。

【図面の簡単な説明】

【0026】

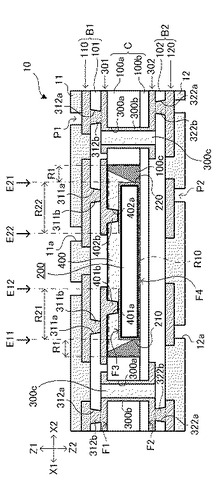

【図1】本発明の実施形態1に係る電子部品内蔵配線板の断面図である。

【図2】本発明の実施形態1に係る電子部品内蔵配線板に内蔵される電子部品(コンデンサ)の断面図である。

【図3】本発明の実施形態1に係る電子部品内蔵配線板において、キャビティに収容された電子部品(コンデンサ)を示す平面図である。

【図4】本発明の実施形態1に係る電子部品内蔵配線板において、ビア導体を介して電子部品(コンデンサ)の電極に電気的に接続される導体パターンを示す平面図である。

【図5】本発明の実施形態1に係る電子部品内蔵配線板の製造方法を示すフローチャートである。

【図6A】図5に示す製造方法において、片面に導体膜を有する支持材を準備する工程を説明するための図である。

【図6B】図5に示す製造方法において、支持材の導体膜に孔を形成する工程を説明するための図である。

【図6C】図5に示す製造方法において、支持材の導体膜上に接着層を形成する工程を説明するための図である。

【図6D】図5に示す製造方法において、支持材上に、絶縁性の接着層を介して、電子部品を固定する工程を説明するための図である。

【図7A】図6Dの工程により支持材上に固定された電子部品を示す図である。

【図7B】電子部品の電極表面における、支持材上の導体膜と接触し易い領域を示す図である。

【図8】図5に示す製造方法において、コア部を形成する第1の工程を説明するための図である。

【図9】図5に示す製造方法において、コア部を形成する第2の工程を説明するための図である。

【図10】図5に示す製造方法において、コア部を形成する第3の工程を説明するための図である。

【図11A】図5に示す製造方法において、コア部を形成する第4の工程を説明するための図である。

【図11B】図5に示す製造方法において、コア部を形成する第5の工程を説明するための図である。

【図12A】図5に示す製造方法において、コア部を形成する第6の工程を説明するための図である。

【図12B】図5に示す製造方法において、コア部上の導体層をパターニングする工程を説明するための図である。

【図13】比較例に係る電子部品内蔵配線板において、ビア導体を介して電子部品(コンデンサ)の電極に電気的に接続される導体パターンを示す平面図である。

【図14】図5に示す製造方法において、ビルドアップの第1の工程を説明するための図である。

【図15】図14の工程の後の第2の工程を説明するための図である。

【図16】図15の工程の後の第3の工程を説明するための図である。

【図17】図16の工程の後の第4の工程を説明するための図である。

【図18】本発明の実施形態2に係る電子部品内蔵配線板の断面図である。

【図19A】本発明の実施形態2に係る第1の導体層の形成方法の第1の工程を説明するための図である。

【図19B】図19Aの工程の後の第2の工程を説明するための図である。

【図19C】図19Bの工程の後の第3の工程を説明するための図である。

【図20A】本発明の実施形態2に係る第2の導体層の形成方法の第1の工程を説明するための図である。

【図20B】図20Aの工程の後の第2の工程を説明するための図である。

【図21A】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第1の別例を示す図である。

【図21B】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第2の別例を示す図である。

【図22A】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第3の別例を示す図である。

【図22B】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第4の別例を示す図である。

【図23A】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての正四角形を示す図である。

【図23B】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての十字形を示す図である。

【図23C】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての正多角星形を示す図である。

【図24】本発明の実施形態において、電子部品及びキャビティの形状の別例を示す図である。

【図25】本発明の実施形態において、電子部品(コンデンサ)の電極に電気的に接続されるビア導体の数を変更した別例を示す図である。

【図26】本発明の他の実施形態において、片面配線板を示す図である。

【図27】本発明の実施形態において、電子部品の第1の別例を示す図である。

【図28】本発明の実施形態において、電子部品の第2の別例を示す図である。

【図29】本発明の実施形態において、電子部品の第3の別例を示す図である。

【図30】本発明の他の実施形態において、電子部品の電極に電気的に接続されるビア導体がコンフォーマル導体である電子部品内蔵配線板を示す図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施形態について、図面を参照しつつ詳細に説明する。なお、図中、矢印Z1、Z2は、それぞれ配線板の主面(表裏面)の法線方向に相当する配線板の積層方向(又は配線板の厚み方向)を指す。一方、矢印X1、X2及びY1、Y2は、それぞれ積層方向に直交する方向(又は各層の側方)を指す。配線板の主面は、X−Y平面となる。また、配線板の側面は、X−Z平面又はY−Z平面となる。

【0028】

相反する法線方向を向いた2つの主面を、第1面又は第3面(Z1側の面)、第2面又は第4面(Z2側の面)という。積層方向において、コアに近い側を下層(又は内層側)、コアから遠い側を上層(又は外層側)という。また、X−Y平面において、電子部品(より詳しくはその重心)から離れる側を外側といい、電子部品に近づく側を内側という。直上は、Z方向(Z1側又はZ2側)を意味する。平面形状は、特に指定がなければ、X−Y平面の形状を意味する。

【0029】

導体層は、一乃至複数の導体パターンで構成される層である。導体層は、電気回路を構成する導体パターン、例えば配線(グランドも含む)、パッド、又はランド等を含む場合もあれば、電気回路を構成しない平面状の導体パターン(以下、ベタパターンという)等を含む場合もある。

【0030】

開口部には、孔や溝のほか、切欠や切れ目等も含まれる。孔は貫通孔に限られず、非貫通の孔も含めて、孔という。孔には、ビアホール及びスルーホールが含まれる。以下、ビアホール内(壁面又は底面)に形成される導体をビア導体といい、スルーホール内(壁面)に形成される導体をスルーホール導体という。

【0031】

めっきには、電解めっき等の湿式めっきのほか、PVD(Physical Vapor Deposition)やCVD(Chemical Vapor Deposition)等の乾式めっきも含まれる。

【0032】

「準備すること」には、材料や部品を購入して自ら製造することのほかに、完成品を購入して使用することなども含まれる。

【0033】

電子部品が開口部に配置されることには、電子部品の全体が開口部に完全に収容されることのほか、電子部品の一部のみが開口部に配置されることも含まれる。

【0034】

以下、本発明を具体化した実施形態について、図面を参照しつつ詳細に説明する。

【0035】

(実施形態1)

本実施形態に係る配線板10は、図1に示すように、コア部Cと、第1ビルドアップ部B1と、第2ビルドアップ部B2と、電子部品200と、ソルダーレジスト11、12と、を有する。配線板10は、電子部品内蔵配線板であり、例えば矩形板状のリジッド配線板からなる。ただしこれに限られず、配線板10は、フレキシブル配線板であってもよい。以下、コア部Cの表裏面(2つの主面)の一方を第1面F1、他方を第2面F2という。また、電子部品200の表裏面(2つの主面)のうち、第1面F1と同じ方向を向く面を第3面F3といい、他方を第4面F4という。

【0036】

コア部Cは、絶縁層100aと、絶縁層100bと、スルーホール導体300bと、から構成される。絶縁層100aには貫通孔が形成されており、絶縁層100bが、その貫通孔の一方の開口を塞いでいる。これにより、コア部Cには、絶縁層100aを貫通する孔からなるキャビティR10が形成される。キャビティR10は、電子部品200が収容される開口部に相当する。

【0037】

コア部Cの第1面F1上には、導体層301及び第1ビルドアップ部B1が形成され、コア部Cの第2面F2上には、導体層302及び第2ビルドアップ部B2が形成される。第1ビルドアップ部B1は、絶縁層101(層間絶縁層)と、導体層110と、から構成され、第2ビルドアップ部B2は、絶縁層102(層間絶縁層)と、導体層120と、から構成される。電子部品200は、配線板10に内蔵される。第1ビルドアップ部B1、第2ビルドアップ部B2上にはそれぞれ、ソルダーレジスト11、12が形成される。

【0038】

コア部Cにはスルーホール300aが形成され、スルーホール300aの壁面に導体(例えば銅めっき)が形成されることにより、スルーホール導体300b(コンフォーマル導体)が形成される。また、スルーホール300aにおけるスルーホール導体300bの内側には、絶縁体300cが充填される。コア部Cの第1面F1上の導体層301とコア部Cの第2面F2上の導体層302とは、スルーホール導体300bを介して、互いに電気的に接続される。本実施形態では、スルーホール300aの形状が略円柱である。すなわち、スルーホール300aは、略一定の幅を有する。本実施形態では、絶縁体300cが、上層の絶縁層101(詳しくは樹脂絶縁層)を構成する絶縁材料(詳しくは樹脂)からなる。ただしこれに限られず、絶縁体300cは、別途用意した任意の絶縁材料からなってもよい。

【0039】

電子部品200は、キャビティR10に配置されることにより、絶縁層100aの側方(X方向又はY方向)に位置する。本実施形態では、電子部品200の略全体がキャビティR10に完全に収容される。しかしこれに限られず、電子部品200の一部のみがキャビティR10に配置されてもよい。本実施形態では、電子部品200の第3面F3が、接着層400で覆われている。また、キャビティR10における電子部品200と絶縁層100aとの隙間R1には、接着層400及び絶縁体100cが充填されている。本実施形態では、電子部品200の表面が、接着層400及び絶縁体100cにより完全に覆われている。これにより、電子部品200が、接着層400及び絶縁体100cで保護されるとともに、所定の位置に固定される。

【0040】

本実施形態では、接着層400が、例えばNCP(非導電性液状ポリマー)等の絶縁性接着材料からなる。すなわち、本実施形態では、電子部品200上に、接着材料からなる絶縁層(接着層400)が形成されている。接着層400は、例えば製造工程において電子部品200を一時的にキャリア(支持材)に固定するために用いられる(図6C及び図6D参照)。

【0041】

本実施形態では、絶縁体100cが、コア部Cの絶縁層100b(詳しくは樹脂絶縁層)を構成する絶縁材料(詳しくは樹脂)からなる(図9参照)。ただしこれに限られず、絶縁体100cは、別途用意した任意の絶縁材料からなってもよい。

【0042】

絶縁層101は、コア部Cの第1面F1上に形成され、絶縁層102は、コア部Cの第2面F2上に形成される。そして、キャビティR10(孔)の開口のうち、絶縁層100bによって塞がれていない側の開口は絶縁層101によって塞がれる。

【0043】

絶縁層101上には導体層110が形成され、絶縁層102上には導体層120が形成される。本実施形態では、導体層110及び120が、最外層となる。ただしこれに限られず、より多くの層間絶縁層及び導体層を積層してもよい。

【0044】

導体層110は、第1面F1側の最外の導体層となり、導体層120は、第2面F2側の最外の導体層となる。導体層110、120上にはそれぞれ、ソルダーレジスト11、12が形成される。ただし、ソルダーレジスト11、12にはそれぞれ、開口部11a、12aが形成されている。このため、導体層110の所定の部位(開口部11aに位置する部位)は、ソルダーレジスト11に覆われず露出しており、パッドP1となる。また、導体層120の所定の部位(開口部12aに位置する部位)は、パッドP2となる。パッドP1は、例えば他の配線板と電気的に接続するための外部接続端子となり、パッドP2は、例えば電子部品を実装するための外部接続端子となる。ただしこれに限られず、パッドP1、P2の用途は任意である。

【0045】

本実施形態では、パッドP1、P2が、その表面に、例えばNi/Au膜からなる耐食層を有する。耐食層は、スパッタリング等により形成することができる。また、OSP(Organic Solderability Preservative)処理を行うことにより、有機保護膜からなる耐食層を形成してもよい。なお、耐食層は必須の構成ではなく、必要がなければ割愛してもよい。

【0046】

電子部品200の第3面F3を覆う接着層400(キャビティR10における接着層400)には、孔401a及び402a(それぞれビアホール)が形成される。孔401aは電子部品200の電極210に至り、孔402aは電子部品200の電極220に至る。孔401a、402a内にそれぞれ導体(例えば銅のめっき)が充填されることにより、各孔内の導体がそれぞれ、ビア導体401b、402b(それぞれフィルド導体)となる。キャビティR10における接着層400に孔401a、402a(ビアホール)を形成することで、配線板10(電子部品内蔵配線板)を薄型化し易くなる。

【0047】

電子部品200の電極210と導体層301とは、ビア導体401bを介して、互いに電気的に接続され、また、電子部品200の電極220と導体層301とは、ビア導体402bを介して、互いに電気的に接続される。本実施形態では、接着層400上の導体層(電極210、220に電気的に接続される導体層)は、コア部C上に導体層と同一の層(導体層301)にある。これにより、配線板10(電子部品内蔵配線板)を薄型化し易くなる。

【0048】

絶縁層101には孔311a及び312a(それぞれビアホール)が形成され、絶縁層102には孔322a(ビアホール)が形成される。孔311aは導体層301(詳しくは、電極210、220に電気的に接続される導体パターン)に至り、孔312aは導体層301に至り、孔322aは導体層302に至る。孔311a、312a、322a内にそれぞれ導体(例えば銅のめっき)が充填されることにより、各孔内の導体がそれぞれ、ビア導体311b、312b、322b(それぞれフィルド導体)となる。ビア導体311b、312b、322bの形状はそれぞれ、例えばコア部Cに向かって幅が狭くなるテーパ円柱(円錐台)である。

【0049】

導体層301と導体層110とは、ビア導体311b、312bを介して、互いに電気的に接続され、また、導体層302と導体層120とは、ビア導体322bを介して、互いに電気的に接続される。

【0050】

本実施形態では、電子部品200及びビア導体401b、402b、311bが、電源ラインを構成し、ビア導体312b、322b及びスルーホール導体300bが、信号ラインを構成する。また、本実施形態において、ビア導体312b、322bは、いずれもフィルド導体であり、スルーホール導体300bはコンフォーマル導体である。

【0051】

電子部品200は、例えば図2に示すように、チップ型のMLCC(積層セラミック・コンデンサ)であり、コンデンサ本体201と、面状の電極210及び220と、を有する。電極210及び220は、電子部品200の長手方向(X方向)に並んでいる。コンデンサ本体201は、複数の誘電層231〜239と複数の導体層211〜214及び221〜224とが交互に積層されて構成される。誘電層231〜239はそれぞれ、例えばセラミックからなり、導体層211〜214は電極210と電気的に接続され、導体層221〜224は電極220と電気的に接続される。

【0052】

電極210及び220は、コンデンサ本体201の両端部にそれぞれ形成されている。詳しくは、本実施形態では、電極210及び220がそれぞれU字状の断面形状(X−Z平面)を有し、電子部品200の側面と上面と下面とに形成される。コンデンサ本体201は、下面(第4面F4側の面)から、側面、そして上面(第3面F3側の面)にかけて、電極210及び220で覆われる。以下、電極210のうち、コンデンサ本体201の上面を覆う部分を上部210aといい、コンデンサ本体201の側面を覆う部分を側部210bといい、コンデンサ本体201の下面を覆う部分を下部210cという。また、電極220のうち、コンデンサ本体201の上面を覆う部分を上部220aといい、コンデンサ本体201の側面を覆う部分を側部220bといい、コンデンサ本体201の下面を覆う部分を下部220cという。本実施形態では、電極210の上部210aがビア導体401bに電気的に接続され、電極220の上部220aがビア導体402bに電気的に接続される。

【0053】

電極210と電極220との間に位置するコンデンサ本体201の中央部は、図2に示されるように、電極210、220に覆われず、誘電層231、239(セラミック)が露出するため、比較的強度が弱くなる。しかし、電子部品200が配線板10に実装(内蔵)された状態においては、コンデンサ本体201の中央部は接着層400又は絶縁体100c等で覆われるため(図1参照)、それらの絶縁材料(樹脂等)により、コンデンサ本体201が保護されると考えられる。

【0054】

絶縁層100a及び100bはそれぞれ、例えばガラスクロス(心材)にエポキシ樹脂を含浸させたもの(以下、ガラエポという)からなる。心材は、主材料(本実施形態ではエポキシ樹脂)よりも熱膨張率の小さい材料である。心材としては、例えばガラス繊維(例えばガラス布又はガラス不織布)、アラミド繊維(例えばアラミド不織布)、又はシリカフィラー等の無機材料が好ましいと考えられる。ただし、絶縁層100a及び100bの材料はそれぞれ、基本的に任意であり、心材を含まない樹脂であってもよい。例えばエポキシ樹脂に代えて、ポリエステル樹脂、ビスマレイミドトリアジン樹脂(BT樹脂)、イミド樹脂(ポリイミド)、フェノール樹脂、又はアリル化フェニレンエーテル樹脂(A−PPE樹脂)等を用いてもよい。各絶縁層は、異種材料からなる複数の層から構成されていてもよい。

【0055】

本実施形態では、絶縁層101、102の各々が、例えばガラエポからなる。ただしこれに限定されず、例えば絶縁層101、102は心材を含まない樹脂からなってもよい。また、絶縁層101、102の材料は、基本的に任意である。例えばエポキシ樹脂に代えて、ポリエステル樹脂、ビスマレイミドトリアジン樹脂(BT樹脂)、イミド樹脂(ポリイミド)、フェノール樹脂、又はアリル化フェニレンエーテル樹脂(A−PPE樹脂)等を用いてもよい。各絶縁層は、異種材料からなる複数の層から構成されていてもよい。

【0056】

導体層301、302、110、120はそれぞれ、例えば銅箔及び銅めっき等から構成される(後述の図12A及び図16参照)。各導体層は、例えば電気回路(例えば電子部品200を含む電気回路)を構成する配線、ランド、及び配線板10の強度を高めるためのベタパターンなどを有する。

【0057】

配線板10における各導体層及び各ビア導体の材料は、導体であれば任意であり、金属でも非金属でもよい。各導体層及び各ビア導体は、異種材料からなる複数の層から構成されていてもよい。

【0058】

図3に、電子部品200がコア部CのキャビティR10に収容された状態を示す。

【0059】

キャビティR10の開口形状は、例えば略長方形である。電子部品200の形状は、例えば矩形板状であり、電子部品200の主面の形状は、例えば略長方形である。すなわち、電子部品200の外縁は4辺で構成される。本実施形態では、電子部品200がキャビティR10に対応した平面形状(例えば略同じ大きさの相似形)を有する。

【0060】

ここで、図3中に示す各寸法の好ましい値の一例を示す。

【0061】

キャビティR10の長手方向の幅D1は約1080μmであり、キャビティR10の短手方向の幅D2は約580μmである。電子部品200の長手方向の幅D11は約1000μmであり、電子部品200の短手方向の幅D12は約500μmである。電子部品200とキャビティR10との隙間の長手方向の幅D3は、約40μm(クリアランスは2倍の約80μm)であり、電子部品200とキャビティR10との隙間の短手方向の幅D4は、約40μm(クリアランスは2倍の約80μm)である。電極210の上部210aもしくは下部210c、又は、電極220の上部220aもしくは下部220cの幅D13は、約250μmである。

【0062】

ビア導体401b及び402bの幅(最大直径)はそれぞれ約60μmであり、ビア導体401bとビア導体402bとのピッチD5は、約800μmである。

【0063】

コア部Cの厚さは約200μmであり、電子部品200の厚さ(電極も含めた厚さ)は約150μm〜330μmの範囲にある。絶縁層101及び102の厚さはそれぞれ約60μmであり、各導体層の厚さは約25μmであり、ソルダーレジスト11及び12の厚さはそれぞれ約20μmである。そして、配線板10全体の厚さは約460μmである。また、各導体層のL(ライン)/S(スペース)は約60/60μmである。

【0064】

図4に、導体層301のうち、電子部品200に電気的に接続される導体パターン301a〜301dを示す。図4に示されるように、導体パターン301a及び301bはそれぞれ面状の導体パターンであり、導体パターン301c及び301dはそれぞれ線状の導体パターンである。本実施形態では、導体層301が、サブトラクティブ法により形成される(後述の図8〜図12B参照)。導体パターン301a〜301dはそれぞれ、金属箔(例えば銅箔)を含み(後述の図12A参照)、エッチングによりパターニングされる(後述の図12B参照)。ただしこれに限られず、導体パターン301a〜301dの材質及び製造方法は任意である。

【0065】

本実施形態では、絶縁層100a上に、例えば導体パターン301a及び301bが形成される。導体パターン301a及び301bの各々の形状及び寸法は、例えば約420μm(図4中の幅D30)×約670μm(図4中の幅D33)の矩形状である。ここで、導体パターン301aはビア導体401bのランドに相当し、導体パターン301bはビア導体402bのランドに相当する。

【0066】

電極210は、第1端E13から第2端E14までの幅(本実施形態では、図3に示す電子部品200の幅D12と同じ)をもって、外側端E11から内側端E12まで形成される。また、電極220は、第1端E23から第2端E24までの幅(本実施形態では、図3に示す電子部品200の幅D12と同じ)をもって、外側端E21から内側端E22まで形成される。本実施形態では、第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21がそれぞれ、電子部品200の端面(側面)、すなわち外縁と一致する。ただし、これらが一致することは必須ではない(後述の図21A及び図21B参照)。

【0067】

図4中、電極210の外側端E11から導体パターン301aの外側端までの寸法D31は、例えば約50μm以上である。また、図4中、電極210の外側端E11から導体パターン301aの内側端までの寸法D32は、例えば約50μm以上である。すなわち、本実施形態では、導体層301が、電子部品200の一端(外側端E11)から、電子部品200の内側及び外側へそれぞれ少なくとも50μmまでの領域に、面状の導体パターン301aを有する。

【0068】

なお、ここでは導体パターン301aについてのみ言及したが、導体パターン301bについても同様である。すなわち、導体層301は、電子部品200の他端(外側端E21)から、電子部品200の内側及び外側へそれぞれ少なくとも50μmまでの領域に、面状の導体パターン301bを有する。

【0069】

導体パターン301a(ビア導体401bのランド)は、絶縁層100a上において電極210の上部210aの直上領域R21の全部を含む領域に形成され、導体パターン301b(ビア導体402bのランド)は、絶縁層100a上において電極220の上部220aの直上領域R22の全部を含む領域に形成される。より詳しくは、導体パターン301aは、X方向(電子部品200の長手方向)の一側においては電極210の内側端E12よりも内側(X2側)まで形成され、X方向の他側においてはキャビティR10の壁面F10よりも外側(X1側)まで形成される。また、導体パターン301aは、Y方向(電子部品200の短手方向)の両側においてそれぞれ、キャビティR10の壁面F10よりも外側まで形成される。さらに、導体パターン301bは、X方向(電子部品200の長手方向)の一側においては電極220の内側端E22よりも内側(X1側)まで形成され、X方向の他側においてはキャビティR10の壁面F10よりも外側(X2側)まで形成される。また、導体パターン301bは、Y方向(電子部品200の短手方向)の両側においてそれぞれ、キャビティR10の壁面F10よりも外側まで形成される。

【0070】

本実施形態では、電子部品200が、一端(外側端E11)近傍に電極210(第1電極)を、他端(外側端E21)近傍に電極220(第2電極)をそれぞれ有する。これら電極210及び220は、電子部品200の長手方向(X方向)に並んでいる。そして、導体層301は、電子部品200の電極210、220の各々の外側の縁(詳しくは、その全部)の直上に面状の導体パターン301a、301bを有する。電極210の外側の縁とは、電極210、220の縁(4辺)のうち、外側を向いている外側端E11、第1端E13、及び第2端E14の3辺(内側を向いている内側端E12を除く3辺)をいい、電極220の外側の縁とは、電極220の縁(4辺)のうち、外側を向いている外側端E21、第1端E23、及び第2端E24の3辺(内側を向いている内側端E22を除く3辺)をいう。また、本実施形態では、これら3辺が、電子部品200の外縁と一致する。すなわち、導体パターン301aは、電子部品200の外縁の直上に位置し、導体パターン301bは、電子部品200の外縁の直上に位置する。

【0071】

本実施形態では、導体パターン301aが、電極210の外側端E11及び内側端E12(詳しくは、それぞれ第1端E13から第2端E14までの全域)の直上に位置する。そして、導体パターン301aの内側(X2側)の1辺を除く3辺(X1、Y1、Y2側の3辺)は、キャビティR10の外側に位置し、隙間R1を跨いでいる。また、導体パターン301bは、電極220の外側端E21及び内側端E22(詳しくは、それぞれ第1端E23から第2端E24までの全域)の直上に位置する。そして、導体パターン301bの内側(X1側)の1辺を除く3辺(X2、Y1、Y2側の3辺)は、キャビティR10の外側に位置し、隙間R1を跨いでいる。ただしこれに限られず、導体パターン301a、301bの上記各3辺は、隙間R1の直上に配置されてもよい(後述の図21A参照)。

【0072】

本実施形態では、導体パターン301aが電極210全域の直上に位置し、導体パターン301bが電極220全域の直上に位置する。ただしこれに限られず、導体パターン301a又は301bが電極210又は220全域の直上に配置されることは必須ではない(後述の図21B参照)。

【0073】

導体パターン301aは、ビア導体401bを介して、電子部品200の電極210と電気的に接続され、導体パターン301bは、ビア導体402bを介して、電子部品200の電極220と電気的に接続される(図1参照)。そして、導体パターン301aは導体パターン301c(配線)と電気的に接続され、また、導体パターン301bは導体パターン301d(配線)と電気的に接続される。導体パターン301a、301bはそれぞれ、導体パターン301c、301dを介して、例えば導体層301の図示しない他の導体パターンと電気的に接続される。なお、導体パターン301a〜301dはそれぞれ、導体層301に含まれる導体パターンであり、例えば導体層301のパターニングにより同時に形成される(後述の図12A及び図12B参照)。本実施形態では、導体パターン301aと導体パターン301c(配線)、また、導体パターン301bと導体パターン301d(配線)がそれぞれ、一体的に形成される。

【0074】

以下、図5等を参照して、配線板10の製造方法について説明する。図5は、本実施形態に係る配線板10の製造方法の概略的な内容及び手順を示すフローチャートである。なお、説明の便宜上、製造途中の配線板は、いずれの工程においても積層板と称す。

【0075】

ステップS11では、図6Aに示すように、片面に金属箔1002(導体膜)を有するキャリア1001(例えば金属箔付き支持板)を準備する。キャリア1001は、アルミニウム等の導電材料又は絶縁性ポリマー等の絶縁材料からなる。金属箔1002は、例えば銅箔からなる。

【0076】

その後、図6Bに示すように、例えばUVレーザにより、金属箔1002を貫通してキャリア1001に達するような孔1003、1004を形成する。孔1003、1004により、キャリア1001に窪みが形成される。本実施形態では、孔1003、1004がアライメントマークとして機能する。これにより、孔401a及び402aを形成する際に(後述の図11A参照)、孔401a及び402aと電子部品200の電極210及び220との位置合わせが容易になる。

【0077】

続けて、図5のステップS12で、キャリア1001(支持材)上に接着層を形成する。具体的には、図6Cに示すように、例えばNCPコーティングにより、金属箔1002上(詳しくは、キャリア1001の中央部)に、接着層400を形成する。これにより、孔1003及び1004にそれぞれ、接着層400が充填される。

【0078】

続けて、図5のステップS13で、接着層400上に、電子部品200を配置する。

【0079】

具体的には、図6Dに示すように、電極210及び220を有する電子部品200を準備し、電子部品200を接着層400上に載置した後、例えば加圧及び加熱を行う。これにより、接着層400が硬化し、金属箔1002上に、絶縁性の接着層400を介して、電子部品200が固定される。電子部品200の電極210、220はそれぞれ、孔1003、1004上に配置される。

【0080】

この際、電子部品200は、キャリア1001の主面に平行な角度で固定されるとは限らない。例えば図7Aに示すように、電子部品200が、キャリア1001の主面に対して角度θ1だけ傾いて固定されることも考えられる。この場合、電子部品200の電極210又は220が、接着層400(絶縁体)を介さずに、キャリア1001上の金属箔1002と直接接触することがある。図7Aの例では、接触箇所P0において電子部品200の電極210と金属箔1002とが接触しており、接触箇所P0は、外側端E11近傍に配置される。電子部品200は、長手方向に傾き易く、電子部品200の電極210又は220と金属箔1002とは、図7B中に示す電子部品200の長手方向の両端(外側端E11及びE21)近傍の領域R31及びR32で接触し易い。

【0081】

続けて、図5のステップS14で、コア部を形成する。

【0082】

具体的には、図8に示すように、キャビティR10(孔)を有する絶縁層100a(絶縁基板)を、金属箔1002上に配置する。これにより、接着層400により固定された状態の電子部品200が、絶縁層100aのキャビティR10に配置される。電子部品200は、絶縁層100aにより包囲される。また、絶縁層100a上及び電子部品200の第4面F4上に、半硬化の状態で絶縁層100bを配置する。絶縁層100aは、例えば完全に硬化したガラエポからなり、絶縁層100bは、例えばガラエポのプリプレグからなる。さらに、絶縁層100b上に、金属箔1005を配置する。金属箔1005は、例えば銅箔からなる。

【0083】

続けて、図9に示すように、絶縁層100bを半硬化の状態でプレスすることにより、絶縁層100bから樹脂を流出させてキャビティR10へ流し込む。これにより、キャビティR10における絶縁層100a(絶縁基板)と電子部品200との隙間R1に絶縁体100c(絶縁層100bを構成する樹脂)が充填される。

【0084】

キャビティR10に絶縁体100cが充填されたら、例えば加熱により、その充填樹脂(絶縁体100c)を硬化させる。その後、図10に示すように、電子部品200からキャリア1001(支持材)を取り外す。

【0085】

続けて、図11Aに示すように、例えばZ1側からレーザを金属箔1002に照射することにより、接着層400に孔401a、402aを形成する。なお、レーザ光の吸収効率を高めるため、レーザ照射に先立って金属箔1002の表面を黒化処理してもよい。

【0086】

続けて、図11Bに示すように、例えばドリルを用いて、積層板に穴を開ける。これにより、絶縁層100a及び100bを貫通するスルーホール300aが形成される。

【0087】

なお、スルーホール300a及び孔401a、402aを形成した後には、デスミア(クリーニング)を行うことが好ましい。デスミアにより、不要な導通(ショート)が抑制される。

【0088】

続けて、例えばパネルめっき法により、図12Aに示すように、積層板の表面、すなわち金属箔1002、1005上、スルーホール300aの壁面、及び孔401a、402a内にそれぞれ、無電解めっき膜1006及び電解めっき1007を形成する。具体的には、まず、例えば化学めっき法により例えば銅の無電解めっき膜1006を形成して、続けてめっき液を用いて、無電解めっき膜1006をシード層として、例えば銅の電解めっき1007を形成する。これにより、スルーホール300aの壁面に無電解めっき膜1006及び電解めっき1007が形成され、スルーホール導体300bが形成される。そしてその結果、絶縁層100a及び100bと、スルーホール導体300bと、を有するコア部Cが形成される。また、孔401a、402aの各々に無電解めっき膜1006及び電解めっき1007が充填されることにより、ビア導体401b、402bが形成される。

【0089】

続けて、図5のステップS15で、例えばエッチングレジスト及びエッチング液を用いて、コア部Cの第1面F1上及び第2面F2上に形成された各導体層のパターニングを行う。具体的には、導体層301、302に対応したパターンを有するエッチングレジストで各導体層を覆い、各導体層の、エッチングレジストで覆われない部分(エッチングレジストの開口部で露出する部位)を、エッチングで除去する。これにより、図12Bに示すように、コア部Cの第1面F1、第2面F2上にそれぞれ、導体層301、302が形成される。なお、エッチングは、湿式に限られず、乾式であってもよい。

【0090】

本実施形態では、導体層301が、電子部品200の電極210、220の各々の外側の縁の直上に面状の導体パターン301a、301b(図4参照)を有する。また、導体パターン301aが、電子部品200の外縁の直上に位置し、導体パターン301bが、電子部品200の外縁の直上に位置する。このため、上記導体層301のパターニングのためのエッチングにおいて、電子部品200の電極210、220の損傷等を抑制することが可能になる。以下、比較例を用いて、このことについてさらに説明する。

【0091】

図13に、比較例を示す。なお、図13に示す比較例において、本実施形態に係る配線板10の要素と対応する要素には、便宜上、配線板10の要素(図1、図4等を参照)と同一の符号を付している。

【0092】

図13に示す比較例では、電子部品200の電極210、220に接続されるビア導体401b、402bのランド(面状の導体パターン301a、301b)が小さくなっており、導体層301は、電極210の外側端E11及び電極220の外側端E21の直上に面状の導体パターン301a、301bを有さない。これにより、電子部品200の電極210又は220と金属箔1002とが接触し易い領域R31及びR32(図7A及び図7B参照)の少なくとも一部(詳しくは、その直上領域)には、導体パターン301a、301bが形成されないことになる。この場合、上記導体層301のパターニングのためのエッチングにおいては、領域R31又はR32にある導体もエッチングで除去することになるため、電子部品200の電極210又は220と金属箔1002との接触箇所P0(図7A)にエッチングが行われる可能性が高くなる。そして、接触箇所P0にエッチングが行われると、電子部品200の電極210又は220と金属箔1002との境界(図7A参照)でエッチングが止まらず、電極210又は220までエッチングされてしまう懸念がある。

【0093】

この点、本実施形態に係る配線板10では、導体層301が、電子部品200の一端(外側端E11)から電子部品200の内側へ少なくとも50μmまでの領域(詳しくは、その直上領域)に面状の導体パターン301aを有し、電子部品200の他端(外側端E21)から電子部品200の内側へ少なくとも50μmまでの領域(詳しくは、その直上領域)に面状の導体パターン301bを有する。ここで、電子部品200の一端(外側端E11)又は他端(外側端E21)から電子部品200の内側へ50μmまでの領域は、領域R31又はR32に相当し、この領域では、電子部品200の電極210又は220と金属箔1002とが接触し易いと考えられる(図7A及び図7B参照)。

【0094】

本実施形態に係る配線板10では、導体層301が、電子部品200の一端(外側端E11)又は他端(外側端E21)から電子部品200の内側へ50μmまでの領域、すなわち領域R31、R32(詳しくは、その直上領域)にそれぞれ、面状の導体パターン301a、301bを有するため(図7A及び図7B参照)、上記導体層301のパターニングのためのエッチング(図12B参照)において、領域R31、R32にある導体をエッチングせずに残存させることになる。このため、電子部品200の電極210又は220と金属箔1002との接触箇所P0(図7A)にエッチングが行われる可能性は低くなる。接触箇所P0以外の部分では、電子部品200の電極210又は220と金属箔1002との間に接着層400が存在し(図7A参照)、接着層400は絶縁体であるため、導体(例えば銅)用のエッチング液に対する耐性を高くし易い。このため、接触箇所P0以外の部分にエッチングが行われた場合には、電子部品200の電極210又は220と金属箔1002との間(特に接着層400)でエッチングが止まり易くなると考えられる。これにより、製造過程における電子部品200の電極210、220の損傷等が抑制されるようになり、ひいては配線板10の電気的信頼性を高めることが可能になる。その結果、配線板10の歩留まりが向上すると考えられる。

【0095】

なお、領域R31、R32の中でも特に電子部品200の電極210又は220と金属箔1002とが接触し易い箇所は、電子部品200の電極210又は220の外側の縁の直上であると考えられる。このため、導体層301が、少なくとも電子部品200の電極210又は220の外側の縁の直上に面状の導体パターン301a、301bを有していれば、製造過程における電子部品200の電極210、220の損傷等が抑制されるようになり、ひいては配線板10の電気的信頼性を高めることが可能になると考えられる。

【0096】

続けて、図5のステップS16で、コア部Cの両面にビルドアップを行う。

【0097】

具体的には、図14に示すように、コア部Cの第1面F1上及び導体層301上に絶縁層101を配置し、コア部Cの第2面F2上及び導体層302上に絶縁層102を配置する。さらに、絶縁層101上に金属箔1008を配置し、絶縁層102上に金属箔1009を配置する。絶縁層101及び102はそれぞれ、例えばガラエポのプリプレグからなる。そして、半硬化状態の絶縁層101及び102をコア部C及び導体層301、302に接着させ、プレスする。これにより、図15に示すように、絶縁層101及び102の各々を構成する樹脂(絶縁体300c)が流出して、スルーホール300aにおけるスルーホール導体300bの内側に充填される。また、プレスと同時に又はプレスの後に、積層板を加熱して絶縁層101、102の各々を硬化させる。両面の絶縁層101、102の硬化を同時に行うことにより、コア部Cの反りを抑制し易くなる。

【0098】

続けて、例えばレーザにより、絶縁層101及び金属箔1008に孔311a及び312a(それぞれビアホール)を形成し、絶縁層102及び金属箔1009に孔322a(ビアホール)を形成する(図16参照)。孔311a及び312aの各々は絶縁層101及び金属箔1008を貫通し、孔322aは絶縁層102及び金属箔1009を貫通する。そして、孔311a及び312aの各々は導体層301に至り、孔322aは導体層302に至る。より詳しくは、孔311aは面状の導体パターン301a、301b(図4)に至る。その後、必要に応じて、デスミアを行う。

【0099】

続けて、例えばパネルめっき法により、図16に示すように、積層板の表面、すなわち金属箔1008、1009上及び孔311a、312a、322a内にそれぞれ、例えば銅の無電解めっき膜1010、1011及び電解めっき1012、1013を形成する。具体的には、まず、例えば化学めっき法により例えば銅の無電解めっき膜1010、1011を形成して、続けてめっき液を用いて、無電解めっき膜1010、1011をシード層として、例えば銅の電解めっき1012、1013を形成する。これにより、孔311a及び312a、孔322aに、それぞれ電解めっき1012、1013が充填され、例えば銅のめっきからなるビア導体311b、312b、322bが形成される。

【0100】

続けて、例えばエッチングレジスト及びエッチング液を用いて、絶縁層101、102上に形成された各導体層のパターニングを行う。具体的には、導体層110、120に対応したパターンを有するエッチングレジストで各導体層を覆い、各導体層の、エッチングレジストで覆われない部分(エッチングレジストの開口部で露出する部位)を、エッチングで除去する。これにより、図17に示すように、絶縁層101、102上にそれぞれ、導体層110、120が形成される。なお、エッチングは、湿式に限られず、乾式であってもよい。その結果、コア部Cの第1面F1上に、絶縁層101及び導体層110から構成される第1ビルドアップ部B1が形成され、コア部Cの第2面F2上に、絶縁層102及び導体層120から構成される第2ビルドアップ部B2が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1010、1011に代えて、スパッタ膜等をシード層として用いてもよい。

【0101】

続けて、図5のステップS17で、絶縁層101、102上にそれぞれ、開口部11aを有するソルダーレジスト11、開口部12aを有するソルダーレジスト12を形成する(図1参照)。導体層110、120はそれぞれ、開口部11a、12aに位置する所定の部位(パッドP1、P2等)を除いて、ソルダーレジスト11、12で覆われる。ソルダーレジスト11及び12は、例えばスクリーン印刷、スプレーコーティング、ロールコーティング、又はラミネート等により、形成することができる。

【0102】

続けて、スパッタリング等により、導体層110、120上、詳しくはソルダーレジスト11、12に覆われないパッドP1、P2(図1参照)の表面にそれぞれ、例えばNi/Au膜からなる耐食層を形成する。また、OSP処理を行うことにより、有機保護膜からなる耐食層を形成してもよい。

【0103】

以上の工程により、本実施形態の配線板10(図1)が完成する。その後、必要があれば、電子部品200の電気テスト(容量値及び絶縁性などのチェック)を行う。

【0104】

本実施形態の製造方法は、配線板10の製造に適している。こうした製造方法であれば、低コストで、良好な配線板10が得られると考えられる。

【0105】

本実施形態の配線板10は、例えば電子部品又は他の配線板と電気的に接続することができる。例えば半田等により、配線板10のパッドP2に、電子部品200とは別の電子部品(例えばICチップ)を実装することができる。また、パッドP1により、配線板10を他の配線板(例えばマザーボード)に実装することができる。本実施形態の配線板10は、例えば携帯電話の回路基板として用いることができる。

【0106】

(実施形態2)

本発明の実施形態2について、上記実施形態1との相違点を中心に説明する。なおここでは、上記図1等に示した要素と同一の要素には各々同一の符号を付し、既に説明した共通の部分、すなわち説明が重複する部分については、その説明を省略又は簡略化する。

【0107】

本実施形態に係る配線板20は、図18に示すように、砂時計状(鼓状)のスルーホール導体300bを有する。具体的には、コア部Cにスルーホール300aが形成され、スルーホール300a内に導体(例えば銅めっき)が充填されることにより、スルーホール導体300bが形成される。スルーホール導体300bは、最小幅となる括れ部300dを有し、コア部Cの第1面F1及び第2面F2の各々から括れ部300dに向かって幅が狭くなるようにテーパしている。コア部Cの第1面F1上の導体層301とコア部Cの第2面F2上の導体層302とは、スルーホール導体300bを介して、互いに電気的に接続される。孔312aは導体層301(詳しくは、スルーホール導体300bの直上)に至り、孔322aは導体層302(詳しくはスルーホール導体300bの直上)に至る。

【0108】

本実施形態では、電子部品200及びビア導体401b、402b、311bが、電源ラインを構成する。また、本実施形態では、ビア導体312b、322b及びスルーホール導体300bは、いずれもフィルド導体であり、これらがZ方向にスタックされることで、フィルドスタックSが形成される。そして、フィルドスタックSが信号ラインを構成する。

【0109】

本実施形態に係る配線板20の図3及び図4中に示す各寸法の好ましい値の一例を示す。

【0110】

キャビティR10の長手方向の幅D1は約680μmであり、キャビティR10の短手方向の幅D2は約380μmである。電子部品200の長手方向の幅D11は約600μmであり、電子部品200の短手方向の幅D12は約300μmである。電極210の上部210aもしくは下部210c、又は、電極220の上部220aもしくは下部220cの幅D13は、約230μmである。

【0111】

ビア導体401b及び402bの幅(最大直径)はそれぞれ約60μmであり、ビア導体401bとビア導体402bとのピッチD5は、約420μmである。

【0112】

コア部Cの厚さは約200μmであり、電子部品200の厚さ(電極も含めた厚さ)は約150μm〜330μmの範囲にある。絶縁層101及び102の厚さはそれぞれ約30μmであり、内層の導体層301、302の厚さはそれぞれ約20μmであり、外層の導体層110、120の厚さはそれぞれ約15μmであり、ソルダーレジスト11及び12の厚さはそれぞれ約15μmである。そして、配線板10全体の厚さは約360μmである。また、内層の導体層301、302のL/Sはそれぞれ約25/25μmであり、外層の導体層110、120のL/Sはそれぞれ約15/15μmである。導体パターン301a及び301bの各々の形状及び寸法は、例えば約380μm(図4中の幅D30)×約450μm(図4中の幅D33)の矩形状である。なお、導体パターン301aはビア導体401bのランドに相当し、導体パターン301bはビア導体402bのランドに相当する。

【0113】

本実施形態の配線板20は、各導体層(導体層301、302、110、120)の形成を除けば、例えば実施形態1で説明した製造方法(図5)に準ずる製造方法によって製造することができる。以下、本実施形態に係る各導体層の形成方法について説明する。なお、本実施形態では、各導体層が、セミアディティブ(SAP)法により形成される。

【0114】

実施形態1と同様にして、積層板(絶縁層100a、100b、金属箔1002、1005、及び電子部品200)をプレスで一体化した後(図6A〜図10参照)、図19Aに示すように、例えばCO2レーザを用いて、Z1側からレーザを金属箔1002に照射することにより孔1007a、401a、402aを形成し、Z2側からレーザを金属箔1005に照射することにより孔1007bを形成する。孔1007aと孔1007bとは、X−Y平面において略同じ位置に形成され、最終的にはつながって、絶縁層100a及び100bを貫通するスルーホール300aとなる。レーザでスルーホール300aを形成する場合には、スルーホール300a(詳しくは、孔1007a)と孔401a、402aとを同時に形成することが好ましい。ただしこれに限られず、スルーホール300a(詳しくは、孔1007a)と孔401a、402aとは別々に形成してもよい。

【0115】

スルーホール300aの形状は、スルーホール導体300bに対応し、砂時計状(鼓状)である。孔1007aと孔1007bとの境界は括れ部300d(図19B参照)に相当する。Z1側からのレーザ照射とZ2側からのレーザ照射とは、同時に行っても、片面ずつ行ってもよい。スルーホール300a及び孔401a、402aを形成した後には、デスミア(クリーニング)を行うことが好ましい。デスミアにより、不要な導通(ショート)が抑制される。また、レーザ光の吸収効率を高めるため、レーザ照射に先立って金属箔1002及び1005の表面を黒化処理してもよい。なお、スルーホール300aの形成は、湿式又は乾式エッチングなど、レーザ以外の方法で行ってもよい。ただし、レーザ加工であれば、微細な加工をし易い。

【0116】

続けて、例えば化学めっき法により、積層板の表面、すなわち金属箔1002、1005上、スルーホール300a内、及び孔401a、402a内にそれぞれ、例えば銅の無電解めっき膜1006を形成する(図19B参照)。なお、無電解めっきに先立って、例えば浸漬により、パラジウム等からなる触媒を、絶縁層100a及び100bの表面に吸着させてもよい。

【0117】

続けて、リソグラフィ技術又は印刷等により、第1面F1側の主面(無電解めっき膜1006上)に、開口部2001aを有するめっきレジスト2001を、また、第2面F2側の主面(無電解めっき膜1006上)に、開口部2002aを有するめっきレジスト2002を、それぞれ形成する(図16参照)。開口部2001a、2002aはそれぞれ、導体層301、302(図19C参照)に対応したパターンを有する。

【0118】

続けて、図19Bに示すように、例えばパターンめっき法により、めっきレジスト2001、2002の開口部2001a、2002aに、それぞれ例えば銅の電解めっき1007を形成する。具体的には、陽極にめっきする材料である銅を接続し、陰極に被めっき材である無電解めっき膜1006(シード層)を接続して、めっき液に浸漬する。そして、両極間に直流の電圧を印加して電流を流し、無電解めっき膜1006の表面に銅を析出させる。これにより、スルーホール300aに無電解めっき膜1006及び電解めっき1007が充填され、スルーホール導体300bが形成される。そしてその結果、絶縁層100a及び100bと、スルーホール導体300bと、を有するコア部Cが形成される。また、孔401a、402aの各々に無電解めっき膜1006及び電解めっき1007が充填され、ビア導体401b、402bが形成される。

【0119】

その後、例えば所定の剥離液により、めっきレジスト2001及び2002を除去し、続けて不要な無電解めっき膜1006及び金属箔1002、1005を除去することにより、図19Cに示すように、コア部Cの第1面F1上に導体層301が形成され、コア部Cの第2面F2上に導体層302が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1006に代えて、スパッタ膜等をシード層として用いてもよい。

【0120】

続けて、実施形態1と同様にして、絶縁層101、102、金属箔1008、1009、及び孔311a、312a、322aを形成した後、例えば化学めっき法により、積層板の表面、すなわち金属箔1008、1009上及び孔311a、312a、322a内にそれぞれ、例えば銅の無電解めっき膜1010、1011を形成する(図20A参照)。なお、無電解めっきに先立って、例えば浸漬により、パラジウム等からなる触媒を、絶縁層101、102の表面に吸着させてもよい。

【0121】

続けて、リソグラフィ技術又は印刷等により、第1面F1側の主面(無電解めっき膜1010上)に、開口部2003aを有するめっきレジスト2003を、また、第2面F2側の主面(無電解めっき膜1011上)に、開口部2004aを有するめっきレジスト2004を、それぞれ形成する(図20A参照)。開口部2003a、2004aはそれぞれ、導体層110、120(図1)に対応したパターンを有する。

【0122】

続けて、図20Aに示すように、例えばパターンめっき法により、めっきレジスト2003、2004の開口部2003a、2004aに、それぞれ例えば銅の電解めっき1012、1013を形成する。具体的には、陽極にめっきする材料である銅を接続し、陰極に被めっき材である無電解めっき膜1010、1011(シード層)を接続して、めっき液に浸漬する。そして、両極間に直流の電圧を印加して電流を流し、無電解めっき膜1010、1011の表面に銅を析出させる。これにより、孔311a及び312a、孔322aに、それぞれ電解めっき1012、1013が充填され、例えば銅のめっきからなるビア導体311b、312b、322bが形成される。

【0123】

その後、例えば所定の剥離液により、めっきレジスト2003及び2004を除去し、続けて不要な無電解めっき膜1010、1011及び金属箔1008、1009を除去することにより、図20Bに示すように、導体層110及び120が形成される。その結果、コア部Cの第1面F1上に、絶縁層101及び導体層110から構成される第1ビルドアップ部B1が形成され、コア部Cの第2面F2上に、絶縁層102及び導体層120から構成される第2ビルドアップ部B2が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1010、1011に代えて、スパッタ膜等をシード層として用いてもよい。

【0124】

本実施形態の製造方法によれば、配線板20(図18)を製造することができる。本実施形態の製造方法は、配線板20の製造に適している。こうした製造方法であれば、低コストで、良好な配線板20が得られる。また、実施形態1と同様の構成及び処理については、本実施形態でも、前述した実施形態1の効果に準ずる効果が得られる。

【0125】

(他の実施形態)

図21Aに示すように、導体パターン301a、301bの3辺が、隙間R1の直上に配置されてもよい。

【0126】

面状の導体パターン301a又は301bが、電子部品200の電極210又は220の4辺全ての直上に配置され、ひいては電極210又は220全域の直上に配置されることは必須ではない。例えば図21Bに示すように、導体層301が電極210の内側端E12(詳しくは、第1端E13から第2端E14までの全域)の直上に導体パターンを有していなくてもよい。また、導体層301が電極220の内側端E22(詳しくは、その一部)の直上に導体パターンを有していなくてもよい。導体層301が、電極210又は220の外側の縁の少なくとも一部の直上に面状の導体パターン301a又は301bを有していれば、電子部品内蔵配線板における電気的接続の信頼性を高めることが可能になる。なお、外側の縁の直上に面状の導体パターンを形成する場合、面状の導体パターンが外側の縁の直上に跨って形成されるのが好ましい態様である。

【0127】

第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21はそれぞれ、電子部品200の端面と一致しなくてもよい。例えば図22Aに示すように、第1端E13、E23及び第2端E14、E24が、電子部品200の端面よりも内側(電子部品200の直上)に位置してもよい。また、例えば図22Bに示すように、第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21がそれぞれ、電子部品200の端面よりも内側(電子部品200の直上)に位置してもよい。図22A及び図22Bのいずれに示す例でも、電極210、220の外側の縁(外側端E11及びE21、第1端E13及びE23、及び第2端E14及びE24)は、電子部品200の外縁(4辺)近傍に位置している。こうした構成においても、導体層301が、電極210又は220の外側の縁の直上に面状の導体パターン301a又は301bを有することで、電子部品200の電極210又は220と金属箔1002とが接触し易い電子部品200の外縁近傍(図7A及び図7B参照)におけるエッチングによる損傷等が抑制されることになる。

【0128】

配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの形状は任意であり、これらの平面形状は、例えば図23Aに示すように、略正方形等の四角形であってもよく、例えば図23B又は図23Cに示すように、略十字形又は略正多角星形など、中心から放射状に直線を引いた形(複数の羽根を放射状に配置した形)であってもよく、その他、略真円、略楕円、又は略三角形等であってもよい。なお、多角形の角の形状は任意であり、例えば略直角でも、鋭角でも、鈍角でも、丸みを帯びていてもよい。

【0129】

電子部品200及びキャビティR10の形状は任意である。例えば図24に示すように、キャビティR10の開口形状が略楕円であってもよい。電子部品200の主面の形状及びキャビティR10の開口形状はそれぞれ、略真円であってもよく、また、略正方形、略正六角形、略正八角形など、略長方形以外の略多角形であってもよい。なお、多角形の角の形状は任意であり、例えば略直角でも、鋭角でも、鈍角でも、丸みを帯びていてもよい。

【0130】

上記各実施形態では、電子部品200の主面の形状が略長方形(D11>D12)であり、電極210及び220が電子部品200の長手方向に並んでいる(図3参照)。しかしこれに限定されず、電子部品200の主面の形状は、例えば正方形(D11=D12)であってもよい。

【0131】

上記各実施形態では、キャビティR10(電子部品200の収容スペース)に電子部品200を1つのみ有する配線板10を示したが、これに限られない。例えばキャビティR10に複数の電子部品200を有する配線板であってもよい。複数の電子部品200は、積層方向(Z方向)に並べて配置しても、X方向又はY方向に並べて配置してもよい。また、1つの配線板に複数のキャビティR10を形成してもよい。

【0132】

上記各実施形態では、電子部品200の電極210、220にそれぞれ1つずつのビア導体401b、402bが接続される例を示したが、ビア導体401b及び402bの数は任意である。例えば図25に示すように、電子部品200の1つの電極(電極210又は220)が、複数(例えば2つ)のビア導体(ビア導体401b又は402b)を介して、1つのビア導体のランド(導体パターン301a又は301b)と接続されてもよい。この場合、電極:ビア導体:ビアランド=1:複数:1となる。

【0133】

上記各実施形態では、コア部Cの両側に導体層を有する両面配線板(配線板10)を示したが、これに限られない。例えば図26に示すように、コア部C(例えば絶縁性を有する基板100)の片側のみに第1ビルドアップ部B1(導体層110を含む)を有する片面配線板であってもよい。

【0134】

上記各実施形態では、コア部Cが絶縁層100a及び100bの2層構造を有するが、これに限定されない。例えば図26に示すように、コア部Cは1つの基板から構成されてもよい。

【0135】

例えば図26に示されるように、キャビティR10(電子部品200の収容スペース)は、基板100を貫通しない孔(凹部)であってもよい。

【0136】

上記各実施形態では、コア部Cの両側に、それぞれ1層の第1ビルドアップ部B1及び第2ビルドアップ部B2を有する配線板10を示したが、これに限られない。コア部Cの片側に2層以上のビルドアップ部を有する配線板であってもよい。

【0137】

電子部品200の電極の形状は、U字形状に限定されず、例えば図27に示すように、各実施形態に係る電極210、220の下部210c、220c(又は上部210a、220a)がないL字形状であってもよく、あるいは図28に示すように、平板状の電極対(電極200a及び200b)でコンデンサ本体201を挟んでもよい。

【0138】

電子部品200の種類は、MLCCに限られず任意である。電子部品200はコンデンサに限られず、例えば図29に示すように、チップ抵抗であってもよい。図29に示すチップ抵抗は基板201aを有し、さらに基板201a上に、電極200aと、抵抗部201bと、電極200bと、を有する。電子部品200は受動部品にも限られず、IC(集積回路)等からなる能動部品であってもよい。

【0139】

配線板10の構成、及びその構成要素の種類、性能、寸法、材質、形状、層数、又は配置等は、本発明の趣旨を逸脱しない範囲において任意に変更することができる。

【0140】

例えば配線板におけるスルーホール導体又は各ビア導体は、フィルド導体に限られず、例えばコンフォーマル導体であってもよい。例えば図30に示すように、ビア導体401b、402bがコンフォーマル導体であってもよい。

【0141】

配線板の製造工程は、上記図5に示した順序や内容に限定されるものではなく、本発明の趣旨を逸脱しない範囲において任意に順序や内容を変更することができる。また、用途等に応じて、必要ない工程を割愛してもよい。

【0142】

上記各実施形態では、キャリア1001(支持材)上に接着層400を形成した後、その接着層400上に電子部品200を設けるようにしたが(図6C及び図6D参照)、これに限られず、接着層400が塗布された電子部品200を、キャリア1001(支持材)上に設けるようにしてもよい。

【0143】

配線板10における各導体層の形成方法は任意である。例えばパネルめっき法、パターンめっき法、フルアディティブ法、セミアディティブ法、サブトラクティブ法、転写法、及びテンティング法のいずれか1つ、又はこれらの2以上を任意に組み合わせた方法で、導体層を形成してもよい。

【0144】

また、レーザに代えて、湿式又は乾式のエッチングで加工してもよい。エッチングで加工する場合には、予め除去したくない部分をレジスト等で保護しておくことが好ましいと考えられる。

【0145】

上記各実施形態や変形例等は、任意に組み合わせることができる。用途等に応じて適切な組み合わせを選ぶことが好ましいと考えられる。例えば図21A〜図22Bのいずれかに示した構造を、図23A〜図30のいずれかに示した構造に適用してもよい。

【0146】

以上、本発明の実施形態について説明したが、設計上の都合やその他の要因によって必要となる様々な修正や組み合わせは、「請求項」に記載されている発明や「発明を実施するための形態」に記載されている具体例に対応する発明の範囲に含まれると理解されるべきである。

【産業上の利用可能性】

【0147】

本発明に係る電子部品内蔵配線板は、携帯電話などの回路基板に適している。本発明に係る電子部品内蔵配線板の製造方法は、そうした配線板の製造に適している。

【符号の説明】

【0148】

10 配線板

11、12 ソルダーレジスト

11a、12a 開口部

100 基板

100a、100b 絶縁層

100c 絶縁体

101、102 絶縁層

110、120 導体層

200 電子部品

200a、200b 電極

201 コンデンサ本体

201a 基板

201b 抵抗部

210、220 電極

210a、220a 上部

210b、220b 側部

210c、220c 下部

211〜214 導体層

221〜224 導体層

231〜239 誘電層

300a スルーホール

300b スルーホール導体

300c 絶縁体

300d 括れ部

301 導体層

301a〜301d 導体パターン

302 導体層

311a、312a、322a 孔

311b、312b、322b ビア導体

400 接着層

401a、402a 孔

401b、402b ビア導体

1001 キャリア

1002、1005 金属箔

1003、1004 孔

1006 膜

1007a、1007b 孔

1008、1009 金属箔

1010、1011 無電解めっき膜

1012、1013 電解めっき

2001〜2004 めっきレジスト

2001a〜2004a 開口部

C コア部

S フィルドスタック

B1 第1ビルドアップ部

B2 第2ビルドアップ部

E11、E21 外側端

E12、E22 内側端

E13、E23 第1端

E14、E24 第2端

F1 第1面

F2 第2面

F3 第3面

F4 第4面

F10 壁面

P0 接触箇所

P1 パッド

P2 パッド

R10 キャビティ

R21 直上領域

R22 直上領域

R31 領域

R32 領域

【技術分野】

【0001】

本発明は、電子部品内蔵配線板及びその製造方法に関する。

【背景技術】

【0002】

特許文献1及び特許文献2にはそれぞれ、電極を有する電子部品と、その電子部品上に形成された絶縁層と、その絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、そのビア導体を介して電子部品の電極に電気的に接続される導体層と、を有する電子部品内蔵配線板が開示されている。

【先行技術文献】

【特許文献】

【0003】

【特許文献1】国際公開第2008/155967号

【特許文献2】特開2003−309373号公報

【発明の概要】

【発明が解決しようとする課題】

【0004】

近年、少なくとも片面に導体膜(例えば銅箔)を有する支持材を用いて、その導体膜上に、絶縁性の接着層を介して、電子部品(例えばコンデンサ)を固定し、その電子部品を、支持材に固定されたままコア基板の開口部に配置する電子部品内蔵配線板の製造方法が提案されている。こうした製造方法は、ビア導体等の位置精度を高める上で有効であると考えられる。しかしながら、この方法で、特許文献1又は特許文献2に記載される電子部品内蔵配線板を製造しようとすると、その製造過程において電子部品の電極が損傷する可能性があり、完成した電子部品内蔵配線板の電気的接続について高い信頼性を得ることは困難になる(詳しくは、後述する)。

【0005】

本発明は、こうした実情に鑑みてなされたものであり、電子部品内蔵配線板における電気的接続の信頼性を高めることを目的とする。

【課題を解決するための手段】

【0006】

本発明に係る電子部品内蔵配線板は、収容部を有する基板と、前記収容部に収容され、電極を有する電子部品と、前記電子部品上に形成された絶縁層と、前記絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、前記ビア導体を介して前記電極に電気的に接続される導体層と、を有する電子部品内蔵配線板であって、前記導体層は、前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する。

【0007】

前記導体層は、前記電子部品の外縁近傍における前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、ことが好ましい。

【0008】

前記面状の導体パターンは、前記ビア導体のランドである、ことが好ましい。

【0009】

前記電子部品は、一端近傍に第1電極を、他端近傍に第2電極をそれぞれ有し、前記面状の導体パターンは、前記電子部品の前記一端及び前記他端の少なくとも一方の直上に位置する、ことが好ましい。

【0010】

前記第1電極及び前記第2電極は、前記電子部品の長手方向に並んでいる、ことが好ましい。

【0011】

前記導体層は、前記一端又は前記他端から、前記電子部品の内側及び外側へそれぞれ少なくとも50μmまでの領域に、前記面状の導体パターンを有する、ことが好ましい。

【0012】

前記導体層は、前記電極全域の直上に前記面状の導体パターンを有する、ことが好ましい。

【0013】

前記電極は、前記電子部品の側面と上面と下面とに形成される、ことが好ましい。

【0014】

前記電極の1つが、複数の前記ビア導体を介して、前記ビア導体の1つのランドと接続される、ことが好ましい。

【0015】

前記絶縁層の少なくとも一部は、接着材料からなる、ことが好ましい。

【0016】

前記電子部品は、コンデンサからなる、ことが好ましい。

【0017】

前記面状の導体パターンは、エッチングによりパターニングされる、ことが好ましい。

【0018】

前記面状の導体パターンは、金属箔を含む、ことが好ましい。

【0019】

前記電子部品は、前記電子部品内蔵配線板のコア部に形成された開口部に配置される、ことが好ましい。

【0020】

前記ビアホールは、前記開口部における前記絶縁層に形成される、ことが好ましい。

【0021】

前記コア部上に導体層を有し、前記電極に電気的に接続される導体層は、前記コア部上の導体層と同一の層にある、ことが好ましい。

【0022】

本発明に係る電子部品内蔵配線板の製造方法は、電極を有する電子部品を準備することと、前記電子部品上に絶縁層を形成することと、前記絶縁層にビアホールを形成することと、前記ビアホール内にビア導体を形成することと、前記電極の外側の縁の直上に、少なくとも一箇所で前記ビア導体を介して前記電極に電気的に接続される面状の導体パターンを形成することと、を含む。

【0023】

前記面状の導体パターンを、サブトラクティブ法により形成する、ことが好ましい。

【0024】

前記絶縁層の形成は、少なくとも片面に導体膜を有する支持材を準備することと、前記導体膜上に、絶縁性の接着層を介して、前記電子部品を固定することと、開口部を有する絶縁基板を準備することと、前記接着層により固定された状態の前記電子部品を、前記絶縁基板の前記開口部に配置することと、前記電子部品から前記支持材を取り外すことと、を含む、ことが好ましい。

【発明の効果】

【0025】

本発明によれば、電子部品内蔵配線板における電気的接続の信頼性を高めることが可能になる。

【図面の簡単な説明】

【0026】

【図1】本発明の実施形態1に係る電子部品内蔵配線板の断面図である。

【図2】本発明の実施形態1に係る電子部品内蔵配線板に内蔵される電子部品(コンデンサ)の断面図である。

【図3】本発明の実施形態1に係る電子部品内蔵配線板において、キャビティに収容された電子部品(コンデンサ)を示す平面図である。

【図4】本発明の実施形態1に係る電子部品内蔵配線板において、ビア導体を介して電子部品(コンデンサ)の電極に電気的に接続される導体パターンを示す平面図である。

【図5】本発明の実施形態1に係る電子部品内蔵配線板の製造方法を示すフローチャートである。

【図6A】図5に示す製造方法において、片面に導体膜を有する支持材を準備する工程を説明するための図である。

【図6B】図5に示す製造方法において、支持材の導体膜に孔を形成する工程を説明するための図である。

【図6C】図5に示す製造方法において、支持材の導体膜上に接着層を形成する工程を説明するための図である。

【図6D】図5に示す製造方法において、支持材上に、絶縁性の接着層を介して、電子部品を固定する工程を説明するための図である。

【図7A】図6Dの工程により支持材上に固定された電子部品を示す図である。

【図7B】電子部品の電極表面における、支持材上の導体膜と接触し易い領域を示す図である。

【図8】図5に示す製造方法において、コア部を形成する第1の工程を説明するための図である。

【図9】図5に示す製造方法において、コア部を形成する第2の工程を説明するための図である。

【図10】図5に示す製造方法において、コア部を形成する第3の工程を説明するための図である。

【図11A】図5に示す製造方法において、コア部を形成する第4の工程を説明するための図である。

【図11B】図5に示す製造方法において、コア部を形成する第5の工程を説明するための図である。

【図12A】図5に示す製造方法において、コア部を形成する第6の工程を説明するための図である。

【図12B】図5に示す製造方法において、コア部上の導体層をパターニングする工程を説明するための図である。

【図13】比較例に係る電子部品内蔵配線板において、ビア導体を介して電子部品(コンデンサ)の電極に電気的に接続される導体パターンを示す平面図である。

【図14】図5に示す製造方法において、ビルドアップの第1の工程を説明するための図である。

【図15】図14の工程の後の第2の工程を説明するための図である。

【図16】図15の工程の後の第3の工程を説明するための図である。

【図17】図16の工程の後の第4の工程を説明するための図である。

【図18】本発明の実施形態2に係る電子部品内蔵配線板の断面図である。

【図19A】本発明の実施形態2に係る第1の導体層の形成方法の第1の工程を説明するための図である。

【図19B】図19Aの工程の後の第2の工程を説明するための図である。

【図19C】図19Bの工程の後の第3の工程を説明するための図である。

【図20A】本発明の実施形態2に係る第2の導体層の形成方法の第1の工程を説明するための図である。

【図20B】図20Aの工程の後の第2の工程を説明するための図である。

【図21A】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第1の別例を示す図である。

【図21B】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第2の別例を示す図である。

【図22A】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第3の別例を示す図である。

【図22B】本発明の実施形態において、ビア導体を介して電子部品の電極に電気的に接続される導体パターンの第4の別例を示す図である。

【図23A】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての正四角形を示す図である。

【図23B】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての十字形を示す図である。

【図23C】本発明の実施形態において、配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの平面形状の別例としての正多角星形を示す図である。

【図24】本発明の実施形態において、電子部品及びキャビティの形状の別例を示す図である。

【図25】本発明の実施形態において、電子部品(コンデンサ)の電極に電気的に接続されるビア導体の数を変更した別例を示す図である。

【図26】本発明の他の実施形態において、片面配線板を示す図である。

【図27】本発明の実施形態において、電子部品の第1の別例を示す図である。

【図28】本発明の実施形態において、電子部品の第2の別例を示す図である。

【図29】本発明の実施形態において、電子部品の第3の別例を示す図である。

【図30】本発明の他の実施形態において、電子部品の電極に電気的に接続されるビア導体がコンフォーマル導体である電子部品内蔵配線板を示す図である。

【発明を実施するための形態】

【0027】

以下、本発明の実施形態について、図面を参照しつつ詳細に説明する。なお、図中、矢印Z1、Z2は、それぞれ配線板の主面(表裏面)の法線方向に相当する配線板の積層方向(又は配線板の厚み方向)を指す。一方、矢印X1、X2及びY1、Y2は、それぞれ積層方向に直交する方向(又は各層の側方)を指す。配線板の主面は、X−Y平面となる。また、配線板の側面は、X−Z平面又はY−Z平面となる。

【0028】

相反する法線方向を向いた2つの主面を、第1面又は第3面(Z1側の面)、第2面又は第4面(Z2側の面)という。積層方向において、コアに近い側を下層(又は内層側)、コアから遠い側を上層(又は外層側)という。また、X−Y平面において、電子部品(より詳しくはその重心)から離れる側を外側といい、電子部品に近づく側を内側という。直上は、Z方向(Z1側又はZ2側)を意味する。平面形状は、特に指定がなければ、X−Y平面の形状を意味する。

【0029】

導体層は、一乃至複数の導体パターンで構成される層である。導体層は、電気回路を構成する導体パターン、例えば配線(グランドも含む)、パッド、又はランド等を含む場合もあれば、電気回路を構成しない平面状の導体パターン(以下、ベタパターンという)等を含む場合もある。

【0030】

開口部には、孔や溝のほか、切欠や切れ目等も含まれる。孔は貫通孔に限られず、非貫通の孔も含めて、孔という。孔には、ビアホール及びスルーホールが含まれる。以下、ビアホール内(壁面又は底面)に形成される導体をビア導体といい、スルーホール内(壁面)に形成される導体をスルーホール導体という。

【0031】

めっきには、電解めっき等の湿式めっきのほか、PVD(Physical Vapor Deposition)やCVD(Chemical Vapor Deposition)等の乾式めっきも含まれる。

【0032】

「準備すること」には、材料や部品を購入して自ら製造することのほかに、完成品を購入して使用することなども含まれる。

【0033】

電子部品が開口部に配置されることには、電子部品の全体が開口部に完全に収容されることのほか、電子部品の一部のみが開口部に配置されることも含まれる。

【0034】

以下、本発明を具体化した実施形態について、図面を参照しつつ詳細に説明する。

【0035】

(実施形態1)

本実施形態に係る配線板10は、図1に示すように、コア部Cと、第1ビルドアップ部B1と、第2ビルドアップ部B2と、電子部品200と、ソルダーレジスト11、12と、を有する。配線板10は、電子部品内蔵配線板であり、例えば矩形板状のリジッド配線板からなる。ただしこれに限られず、配線板10は、フレキシブル配線板であってもよい。以下、コア部Cの表裏面(2つの主面)の一方を第1面F1、他方を第2面F2という。また、電子部品200の表裏面(2つの主面)のうち、第1面F1と同じ方向を向く面を第3面F3といい、他方を第4面F4という。

【0036】

コア部Cは、絶縁層100aと、絶縁層100bと、スルーホール導体300bと、から構成される。絶縁層100aには貫通孔が形成されており、絶縁層100bが、その貫通孔の一方の開口を塞いでいる。これにより、コア部Cには、絶縁層100aを貫通する孔からなるキャビティR10が形成される。キャビティR10は、電子部品200が収容される開口部に相当する。

【0037】

コア部Cの第1面F1上には、導体層301及び第1ビルドアップ部B1が形成され、コア部Cの第2面F2上には、導体層302及び第2ビルドアップ部B2が形成される。第1ビルドアップ部B1は、絶縁層101(層間絶縁層)と、導体層110と、から構成され、第2ビルドアップ部B2は、絶縁層102(層間絶縁層)と、導体層120と、から構成される。電子部品200は、配線板10に内蔵される。第1ビルドアップ部B1、第2ビルドアップ部B2上にはそれぞれ、ソルダーレジスト11、12が形成される。

【0038】

コア部Cにはスルーホール300aが形成され、スルーホール300aの壁面に導体(例えば銅めっき)が形成されることにより、スルーホール導体300b(コンフォーマル導体)が形成される。また、スルーホール300aにおけるスルーホール導体300bの内側には、絶縁体300cが充填される。コア部Cの第1面F1上の導体層301とコア部Cの第2面F2上の導体層302とは、スルーホール導体300bを介して、互いに電気的に接続される。本実施形態では、スルーホール300aの形状が略円柱である。すなわち、スルーホール300aは、略一定の幅を有する。本実施形態では、絶縁体300cが、上層の絶縁層101(詳しくは樹脂絶縁層)を構成する絶縁材料(詳しくは樹脂)からなる。ただしこれに限られず、絶縁体300cは、別途用意した任意の絶縁材料からなってもよい。

【0039】

電子部品200は、キャビティR10に配置されることにより、絶縁層100aの側方(X方向又はY方向)に位置する。本実施形態では、電子部品200の略全体がキャビティR10に完全に収容される。しかしこれに限られず、電子部品200の一部のみがキャビティR10に配置されてもよい。本実施形態では、電子部品200の第3面F3が、接着層400で覆われている。また、キャビティR10における電子部品200と絶縁層100aとの隙間R1には、接着層400及び絶縁体100cが充填されている。本実施形態では、電子部品200の表面が、接着層400及び絶縁体100cにより完全に覆われている。これにより、電子部品200が、接着層400及び絶縁体100cで保護されるとともに、所定の位置に固定される。

【0040】

本実施形態では、接着層400が、例えばNCP(非導電性液状ポリマー)等の絶縁性接着材料からなる。すなわち、本実施形態では、電子部品200上に、接着材料からなる絶縁層(接着層400)が形成されている。接着層400は、例えば製造工程において電子部品200を一時的にキャリア(支持材)に固定するために用いられる(図6C及び図6D参照)。

【0041】

本実施形態では、絶縁体100cが、コア部Cの絶縁層100b(詳しくは樹脂絶縁層)を構成する絶縁材料(詳しくは樹脂)からなる(図9参照)。ただしこれに限られず、絶縁体100cは、別途用意した任意の絶縁材料からなってもよい。

【0042】

絶縁層101は、コア部Cの第1面F1上に形成され、絶縁層102は、コア部Cの第2面F2上に形成される。そして、キャビティR10(孔)の開口のうち、絶縁層100bによって塞がれていない側の開口は絶縁層101によって塞がれる。

【0043】

絶縁層101上には導体層110が形成され、絶縁層102上には導体層120が形成される。本実施形態では、導体層110及び120が、最外層となる。ただしこれに限られず、より多くの層間絶縁層及び導体層を積層してもよい。

【0044】

導体層110は、第1面F1側の最外の導体層となり、導体層120は、第2面F2側の最外の導体層となる。導体層110、120上にはそれぞれ、ソルダーレジスト11、12が形成される。ただし、ソルダーレジスト11、12にはそれぞれ、開口部11a、12aが形成されている。このため、導体層110の所定の部位(開口部11aに位置する部位)は、ソルダーレジスト11に覆われず露出しており、パッドP1となる。また、導体層120の所定の部位(開口部12aに位置する部位)は、パッドP2となる。パッドP1は、例えば他の配線板と電気的に接続するための外部接続端子となり、パッドP2は、例えば電子部品を実装するための外部接続端子となる。ただしこれに限られず、パッドP1、P2の用途は任意である。

【0045】

本実施形態では、パッドP1、P2が、その表面に、例えばNi/Au膜からなる耐食層を有する。耐食層は、スパッタリング等により形成することができる。また、OSP(Organic Solderability Preservative)処理を行うことにより、有機保護膜からなる耐食層を形成してもよい。なお、耐食層は必須の構成ではなく、必要がなければ割愛してもよい。

【0046】

電子部品200の第3面F3を覆う接着層400(キャビティR10における接着層400)には、孔401a及び402a(それぞれビアホール)が形成される。孔401aは電子部品200の電極210に至り、孔402aは電子部品200の電極220に至る。孔401a、402a内にそれぞれ導体(例えば銅のめっき)が充填されることにより、各孔内の導体がそれぞれ、ビア導体401b、402b(それぞれフィルド導体)となる。キャビティR10における接着層400に孔401a、402a(ビアホール)を形成することで、配線板10(電子部品内蔵配線板)を薄型化し易くなる。

【0047】

電子部品200の電極210と導体層301とは、ビア導体401bを介して、互いに電気的に接続され、また、電子部品200の電極220と導体層301とは、ビア導体402bを介して、互いに電気的に接続される。本実施形態では、接着層400上の導体層(電極210、220に電気的に接続される導体層)は、コア部C上に導体層と同一の層(導体層301)にある。これにより、配線板10(電子部品内蔵配線板)を薄型化し易くなる。

【0048】

絶縁層101には孔311a及び312a(それぞれビアホール)が形成され、絶縁層102には孔322a(ビアホール)が形成される。孔311aは導体層301(詳しくは、電極210、220に電気的に接続される導体パターン)に至り、孔312aは導体層301に至り、孔322aは導体層302に至る。孔311a、312a、322a内にそれぞれ導体(例えば銅のめっき)が充填されることにより、各孔内の導体がそれぞれ、ビア導体311b、312b、322b(それぞれフィルド導体)となる。ビア導体311b、312b、322bの形状はそれぞれ、例えばコア部Cに向かって幅が狭くなるテーパ円柱(円錐台)である。

【0049】

導体層301と導体層110とは、ビア導体311b、312bを介して、互いに電気的に接続され、また、導体層302と導体層120とは、ビア導体322bを介して、互いに電気的に接続される。

【0050】

本実施形態では、電子部品200及びビア導体401b、402b、311bが、電源ラインを構成し、ビア導体312b、322b及びスルーホール導体300bが、信号ラインを構成する。また、本実施形態において、ビア導体312b、322bは、いずれもフィルド導体であり、スルーホール導体300bはコンフォーマル導体である。

【0051】

電子部品200は、例えば図2に示すように、チップ型のMLCC(積層セラミック・コンデンサ)であり、コンデンサ本体201と、面状の電極210及び220と、を有する。電極210及び220は、電子部品200の長手方向(X方向)に並んでいる。コンデンサ本体201は、複数の誘電層231〜239と複数の導体層211〜214及び221〜224とが交互に積層されて構成される。誘電層231〜239はそれぞれ、例えばセラミックからなり、導体層211〜214は電極210と電気的に接続され、導体層221〜224は電極220と電気的に接続される。

【0052】

電極210及び220は、コンデンサ本体201の両端部にそれぞれ形成されている。詳しくは、本実施形態では、電極210及び220がそれぞれU字状の断面形状(X−Z平面)を有し、電子部品200の側面と上面と下面とに形成される。コンデンサ本体201は、下面(第4面F4側の面)から、側面、そして上面(第3面F3側の面)にかけて、電極210及び220で覆われる。以下、電極210のうち、コンデンサ本体201の上面を覆う部分を上部210aといい、コンデンサ本体201の側面を覆う部分を側部210bといい、コンデンサ本体201の下面を覆う部分を下部210cという。また、電極220のうち、コンデンサ本体201の上面を覆う部分を上部220aといい、コンデンサ本体201の側面を覆う部分を側部220bといい、コンデンサ本体201の下面を覆う部分を下部220cという。本実施形態では、電極210の上部210aがビア導体401bに電気的に接続され、電極220の上部220aがビア導体402bに電気的に接続される。

【0053】

電極210と電極220との間に位置するコンデンサ本体201の中央部は、図2に示されるように、電極210、220に覆われず、誘電層231、239(セラミック)が露出するため、比較的強度が弱くなる。しかし、電子部品200が配線板10に実装(内蔵)された状態においては、コンデンサ本体201の中央部は接着層400又は絶縁体100c等で覆われるため(図1参照)、それらの絶縁材料(樹脂等)により、コンデンサ本体201が保護されると考えられる。

【0054】

絶縁層100a及び100bはそれぞれ、例えばガラスクロス(心材)にエポキシ樹脂を含浸させたもの(以下、ガラエポという)からなる。心材は、主材料(本実施形態ではエポキシ樹脂)よりも熱膨張率の小さい材料である。心材としては、例えばガラス繊維(例えばガラス布又はガラス不織布)、アラミド繊維(例えばアラミド不織布)、又はシリカフィラー等の無機材料が好ましいと考えられる。ただし、絶縁層100a及び100bの材料はそれぞれ、基本的に任意であり、心材を含まない樹脂であってもよい。例えばエポキシ樹脂に代えて、ポリエステル樹脂、ビスマレイミドトリアジン樹脂(BT樹脂)、イミド樹脂(ポリイミド)、フェノール樹脂、又はアリル化フェニレンエーテル樹脂(A−PPE樹脂)等を用いてもよい。各絶縁層は、異種材料からなる複数の層から構成されていてもよい。

【0055】

本実施形態では、絶縁層101、102の各々が、例えばガラエポからなる。ただしこれに限定されず、例えば絶縁層101、102は心材を含まない樹脂からなってもよい。また、絶縁層101、102の材料は、基本的に任意である。例えばエポキシ樹脂に代えて、ポリエステル樹脂、ビスマレイミドトリアジン樹脂(BT樹脂)、イミド樹脂(ポリイミド)、フェノール樹脂、又はアリル化フェニレンエーテル樹脂(A−PPE樹脂)等を用いてもよい。各絶縁層は、異種材料からなる複数の層から構成されていてもよい。

【0056】

導体層301、302、110、120はそれぞれ、例えば銅箔及び銅めっき等から構成される(後述の図12A及び図16参照)。各導体層は、例えば電気回路(例えば電子部品200を含む電気回路)を構成する配線、ランド、及び配線板10の強度を高めるためのベタパターンなどを有する。

【0057】

配線板10における各導体層及び各ビア導体の材料は、導体であれば任意であり、金属でも非金属でもよい。各導体層及び各ビア導体は、異種材料からなる複数の層から構成されていてもよい。

【0058】

図3に、電子部品200がコア部CのキャビティR10に収容された状態を示す。

【0059】

キャビティR10の開口形状は、例えば略長方形である。電子部品200の形状は、例えば矩形板状であり、電子部品200の主面の形状は、例えば略長方形である。すなわち、電子部品200の外縁は4辺で構成される。本実施形態では、電子部品200がキャビティR10に対応した平面形状(例えば略同じ大きさの相似形)を有する。

【0060】

ここで、図3中に示す各寸法の好ましい値の一例を示す。

【0061】

キャビティR10の長手方向の幅D1は約1080μmであり、キャビティR10の短手方向の幅D2は約580μmである。電子部品200の長手方向の幅D11は約1000μmであり、電子部品200の短手方向の幅D12は約500μmである。電子部品200とキャビティR10との隙間の長手方向の幅D3は、約40μm(クリアランスは2倍の約80μm)であり、電子部品200とキャビティR10との隙間の短手方向の幅D4は、約40μm(クリアランスは2倍の約80μm)である。電極210の上部210aもしくは下部210c、又は、電極220の上部220aもしくは下部220cの幅D13は、約250μmである。

【0062】

ビア導体401b及び402bの幅(最大直径)はそれぞれ約60μmであり、ビア導体401bとビア導体402bとのピッチD5は、約800μmである。

【0063】

コア部Cの厚さは約200μmであり、電子部品200の厚さ(電極も含めた厚さ)は約150μm〜330μmの範囲にある。絶縁層101及び102の厚さはそれぞれ約60μmであり、各導体層の厚さは約25μmであり、ソルダーレジスト11及び12の厚さはそれぞれ約20μmである。そして、配線板10全体の厚さは約460μmである。また、各導体層のL(ライン)/S(スペース)は約60/60μmである。

【0064】

図4に、導体層301のうち、電子部品200に電気的に接続される導体パターン301a〜301dを示す。図4に示されるように、導体パターン301a及び301bはそれぞれ面状の導体パターンであり、導体パターン301c及び301dはそれぞれ線状の導体パターンである。本実施形態では、導体層301が、サブトラクティブ法により形成される(後述の図8〜図12B参照)。導体パターン301a〜301dはそれぞれ、金属箔(例えば銅箔)を含み(後述の図12A参照)、エッチングによりパターニングされる(後述の図12B参照)。ただしこれに限られず、導体パターン301a〜301dの材質及び製造方法は任意である。

【0065】

本実施形態では、絶縁層100a上に、例えば導体パターン301a及び301bが形成される。導体パターン301a及び301bの各々の形状及び寸法は、例えば約420μm(図4中の幅D30)×約670μm(図4中の幅D33)の矩形状である。ここで、導体パターン301aはビア導体401bのランドに相当し、導体パターン301bはビア導体402bのランドに相当する。

【0066】

電極210は、第1端E13から第2端E14までの幅(本実施形態では、図3に示す電子部品200の幅D12と同じ)をもって、外側端E11から内側端E12まで形成される。また、電極220は、第1端E23から第2端E24までの幅(本実施形態では、図3に示す電子部品200の幅D12と同じ)をもって、外側端E21から内側端E22まで形成される。本実施形態では、第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21がそれぞれ、電子部品200の端面(側面)、すなわち外縁と一致する。ただし、これらが一致することは必須ではない(後述の図21A及び図21B参照)。

【0067】

図4中、電極210の外側端E11から導体パターン301aの外側端までの寸法D31は、例えば約50μm以上である。また、図4中、電極210の外側端E11から導体パターン301aの内側端までの寸法D32は、例えば約50μm以上である。すなわち、本実施形態では、導体層301が、電子部品200の一端(外側端E11)から、電子部品200の内側及び外側へそれぞれ少なくとも50μmまでの領域に、面状の導体パターン301aを有する。

【0068】

なお、ここでは導体パターン301aについてのみ言及したが、導体パターン301bについても同様である。すなわち、導体層301は、電子部品200の他端(外側端E21)から、電子部品200の内側及び外側へそれぞれ少なくとも50μmまでの領域に、面状の導体パターン301bを有する。

【0069】

導体パターン301a(ビア導体401bのランド)は、絶縁層100a上において電極210の上部210aの直上領域R21の全部を含む領域に形成され、導体パターン301b(ビア導体402bのランド)は、絶縁層100a上において電極220の上部220aの直上領域R22の全部を含む領域に形成される。より詳しくは、導体パターン301aは、X方向(電子部品200の長手方向)の一側においては電極210の内側端E12よりも内側(X2側)まで形成され、X方向の他側においてはキャビティR10の壁面F10よりも外側(X1側)まで形成される。また、導体パターン301aは、Y方向(電子部品200の短手方向)の両側においてそれぞれ、キャビティR10の壁面F10よりも外側まで形成される。さらに、導体パターン301bは、X方向(電子部品200の長手方向)の一側においては電極220の内側端E22よりも内側(X1側)まで形成され、X方向の他側においてはキャビティR10の壁面F10よりも外側(X2側)まで形成される。また、導体パターン301bは、Y方向(電子部品200の短手方向)の両側においてそれぞれ、キャビティR10の壁面F10よりも外側まで形成される。

【0070】

本実施形態では、電子部品200が、一端(外側端E11)近傍に電極210(第1電極)を、他端(外側端E21)近傍に電極220(第2電極)をそれぞれ有する。これら電極210及び220は、電子部品200の長手方向(X方向)に並んでいる。そして、導体層301は、電子部品200の電極210、220の各々の外側の縁(詳しくは、その全部)の直上に面状の導体パターン301a、301bを有する。電極210の外側の縁とは、電極210、220の縁(4辺)のうち、外側を向いている外側端E11、第1端E13、及び第2端E14の3辺(内側を向いている内側端E12を除く3辺)をいい、電極220の外側の縁とは、電極220の縁(4辺)のうち、外側を向いている外側端E21、第1端E23、及び第2端E24の3辺(内側を向いている内側端E22を除く3辺)をいう。また、本実施形態では、これら3辺が、電子部品200の外縁と一致する。すなわち、導体パターン301aは、電子部品200の外縁の直上に位置し、導体パターン301bは、電子部品200の外縁の直上に位置する。

【0071】

本実施形態では、導体パターン301aが、電極210の外側端E11及び内側端E12(詳しくは、それぞれ第1端E13から第2端E14までの全域)の直上に位置する。そして、導体パターン301aの内側(X2側)の1辺を除く3辺(X1、Y1、Y2側の3辺)は、キャビティR10の外側に位置し、隙間R1を跨いでいる。また、導体パターン301bは、電極220の外側端E21及び内側端E22(詳しくは、それぞれ第1端E23から第2端E24までの全域)の直上に位置する。そして、導体パターン301bの内側(X1側)の1辺を除く3辺(X2、Y1、Y2側の3辺)は、キャビティR10の外側に位置し、隙間R1を跨いでいる。ただしこれに限られず、導体パターン301a、301bの上記各3辺は、隙間R1の直上に配置されてもよい(後述の図21A参照)。

【0072】

本実施形態では、導体パターン301aが電極210全域の直上に位置し、導体パターン301bが電極220全域の直上に位置する。ただしこれに限られず、導体パターン301a又は301bが電極210又は220全域の直上に配置されることは必須ではない(後述の図21B参照)。

【0073】

導体パターン301aは、ビア導体401bを介して、電子部品200の電極210と電気的に接続され、導体パターン301bは、ビア導体402bを介して、電子部品200の電極220と電気的に接続される(図1参照)。そして、導体パターン301aは導体パターン301c(配線)と電気的に接続され、また、導体パターン301bは導体パターン301d(配線)と電気的に接続される。導体パターン301a、301bはそれぞれ、導体パターン301c、301dを介して、例えば導体層301の図示しない他の導体パターンと電気的に接続される。なお、導体パターン301a〜301dはそれぞれ、導体層301に含まれる導体パターンであり、例えば導体層301のパターニングにより同時に形成される(後述の図12A及び図12B参照)。本実施形態では、導体パターン301aと導体パターン301c(配線)、また、導体パターン301bと導体パターン301d(配線)がそれぞれ、一体的に形成される。

【0074】

以下、図5等を参照して、配線板10の製造方法について説明する。図5は、本実施形態に係る配線板10の製造方法の概略的な内容及び手順を示すフローチャートである。なお、説明の便宜上、製造途中の配線板は、いずれの工程においても積層板と称す。

【0075】

ステップS11では、図6Aに示すように、片面に金属箔1002(導体膜)を有するキャリア1001(例えば金属箔付き支持板)を準備する。キャリア1001は、アルミニウム等の導電材料又は絶縁性ポリマー等の絶縁材料からなる。金属箔1002は、例えば銅箔からなる。

【0076】

その後、図6Bに示すように、例えばUVレーザにより、金属箔1002を貫通してキャリア1001に達するような孔1003、1004を形成する。孔1003、1004により、キャリア1001に窪みが形成される。本実施形態では、孔1003、1004がアライメントマークとして機能する。これにより、孔401a及び402aを形成する際に(後述の図11A参照)、孔401a及び402aと電子部品200の電極210及び220との位置合わせが容易になる。

【0077】

続けて、図5のステップS12で、キャリア1001(支持材)上に接着層を形成する。具体的には、図6Cに示すように、例えばNCPコーティングにより、金属箔1002上(詳しくは、キャリア1001の中央部)に、接着層400を形成する。これにより、孔1003及び1004にそれぞれ、接着層400が充填される。

【0078】

続けて、図5のステップS13で、接着層400上に、電子部品200を配置する。

【0079】

具体的には、図6Dに示すように、電極210及び220を有する電子部品200を準備し、電子部品200を接着層400上に載置した後、例えば加圧及び加熱を行う。これにより、接着層400が硬化し、金属箔1002上に、絶縁性の接着層400を介して、電子部品200が固定される。電子部品200の電極210、220はそれぞれ、孔1003、1004上に配置される。

【0080】

この際、電子部品200は、キャリア1001の主面に平行な角度で固定されるとは限らない。例えば図7Aに示すように、電子部品200が、キャリア1001の主面に対して角度θ1だけ傾いて固定されることも考えられる。この場合、電子部品200の電極210又は220が、接着層400(絶縁体)を介さずに、キャリア1001上の金属箔1002と直接接触することがある。図7Aの例では、接触箇所P0において電子部品200の電極210と金属箔1002とが接触しており、接触箇所P0は、外側端E11近傍に配置される。電子部品200は、長手方向に傾き易く、電子部品200の電極210又は220と金属箔1002とは、図7B中に示す電子部品200の長手方向の両端(外側端E11及びE21)近傍の領域R31及びR32で接触し易い。

【0081】

続けて、図5のステップS14で、コア部を形成する。

【0082】

具体的には、図8に示すように、キャビティR10(孔)を有する絶縁層100a(絶縁基板)を、金属箔1002上に配置する。これにより、接着層400により固定された状態の電子部品200が、絶縁層100aのキャビティR10に配置される。電子部品200は、絶縁層100aにより包囲される。また、絶縁層100a上及び電子部品200の第4面F4上に、半硬化の状態で絶縁層100bを配置する。絶縁層100aは、例えば完全に硬化したガラエポからなり、絶縁層100bは、例えばガラエポのプリプレグからなる。さらに、絶縁層100b上に、金属箔1005を配置する。金属箔1005は、例えば銅箔からなる。

【0083】

続けて、図9に示すように、絶縁層100bを半硬化の状態でプレスすることにより、絶縁層100bから樹脂を流出させてキャビティR10へ流し込む。これにより、キャビティR10における絶縁層100a(絶縁基板)と電子部品200との隙間R1に絶縁体100c(絶縁層100bを構成する樹脂)が充填される。

【0084】

キャビティR10に絶縁体100cが充填されたら、例えば加熱により、その充填樹脂(絶縁体100c)を硬化させる。その後、図10に示すように、電子部品200からキャリア1001(支持材)を取り外す。

【0085】

続けて、図11Aに示すように、例えばZ1側からレーザを金属箔1002に照射することにより、接着層400に孔401a、402aを形成する。なお、レーザ光の吸収効率を高めるため、レーザ照射に先立って金属箔1002の表面を黒化処理してもよい。

【0086】

続けて、図11Bに示すように、例えばドリルを用いて、積層板に穴を開ける。これにより、絶縁層100a及び100bを貫通するスルーホール300aが形成される。

【0087】

なお、スルーホール300a及び孔401a、402aを形成した後には、デスミア(クリーニング)を行うことが好ましい。デスミアにより、不要な導通(ショート)が抑制される。

【0088】

続けて、例えばパネルめっき法により、図12Aに示すように、積層板の表面、すなわち金属箔1002、1005上、スルーホール300aの壁面、及び孔401a、402a内にそれぞれ、無電解めっき膜1006及び電解めっき1007を形成する。具体的には、まず、例えば化学めっき法により例えば銅の無電解めっき膜1006を形成して、続けてめっき液を用いて、無電解めっき膜1006をシード層として、例えば銅の電解めっき1007を形成する。これにより、スルーホール300aの壁面に無電解めっき膜1006及び電解めっき1007が形成され、スルーホール導体300bが形成される。そしてその結果、絶縁層100a及び100bと、スルーホール導体300bと、を有するコア部Cが形成される。また、孔401a、402aの各々に無電解めっき膜1006及び電解めっき1007が充填されることにより、ビア導体401b、402bが形成される。

【0089】

続けて、図5のステップS15で、例えばエッチングレジスト及びエッチング液を用いて、コア部Cの第1面F1上及び第2面F2上に形成された各導体層のパターニングを行う。具体的には、導体層301、302に対応したパターンを有するエッチングレジストで各導体層を覆い、各導体層の、エッチングレジストで覆われない部分(エッチングレジストの開口部で露出する部位)を、エッチングで除去する。これにより、図12Bに示すように、コア部Cの第1面F1、第2面F2上にそれぞれ、導体層301、302が形成される。なお、エッチングは、湿式に限られず、乾式であってもよい。

【0090】

本実施形態では、導体層301が、電子部品200の電極210、220の各々の外側の縁の直上に面状の導体パターン301a、301b(図4参照)を有する。また、導体パターン301aが、電子部品200の外縁の直上に位置し、導体パターン301bが、電子部品200の外縁の直上に位置する。このため、上記導体層301のパターニングのためのエッチングにおいて、電子部品200の電極210、220の損傷等を抑制することが可能になる。以下、比較例を用いて、このことについてさらに説明する。

【0091】

図13に、比較例を示す。なお、図13に示す比較例において、本実施形態に係る配線板10の要素と対応する要素には、便宜上、配線板10の要素(図1、図4等を参照)と同一の符号を付している。

【0092】

図13に示す比較例では、電子部品200の電極210、220に接続されるビア導体401b、402bのランド(面状の導体パターン301a、301b)が小さくなっており、導体層301は、電極210の外側端E11及び電極220の外側端E21の直上に面状の導体パターン301a、301bを有さない。これにより、電子部品200の電極210又は220と金属箔1002とが接触し易い領域R31及びR32(図7A及び図7B参照)の少なくとも一部(詳しくは、その直上領域)には、導体パターン301a、301bが形成されないことになる。この場合、上記導体層301のパターニングのためのエッチングにおいては、領域R31又はR32にある導体もエッチングで除去することになるため、電子部品200の電極210又は220と金属箔1002との接触箇所P0(図7A)にエッチングが行われる可能性が高くなる。そして、接触箇所P0にエッチングが行われると、電子部品200の電極210又は220と金属箔1002との境界(図7A参照)でエッチングが止まらず、電極210又は220までエッチングされてしまう懸念がある。

【0093】

この点、本実施形態に係る配線板10では、導体層301が、電子部品200の一端(外側端E11)から電子部品200の内側へ少なくとも50μmまでの領域(詳しくは、その直上領域)に面状の導体パターン301aを有し、電子部品200の他端(外側端E21)から電子部品200の内側へ少なくとも50μmまでの領域(詳しくは、その直上領域)に面状の導体パターン301bを有する。ここで、電子部品200の一端(外側端E11)又は他端(外側端E21)から電子部品200の内側へ50μmまでの領域は、領域R31又はR32に相当し、この領域では、電子部品200の電極210又は220と金属箔1002とが接触し易いと考えられる(図7A及び図7B参照)。

【0094】

本実施形態に係る配線板10では、導体層301が、電子部品200の一端(外側端E11)又は他端(外側端E21)から電子部品200の内側へ50μmまでの領域、すなわち領域R31、R32(詳しくは、その直上領域)にそれぞれ、面状の導体パターン301a、301bを有するため(図7A及び図7B参照)、上記導体層301のパターニングのためのエッチング(図12B参照)において、領域R31、R32にある導体をエッチングせずに残存させることになる。このため、電子部品200の電極210又は220と金属箔1002との接触箇所P0(図7A)にエッチングが行われる可能性は低くなる。接触箇所P0以外の部分では、電子部品200の電極210又は220と金属箔1002との間に接着層400が存在し(図7A参照)、接着層400は絶縁体であるため、導体(例えば銅)用のエッチング液に対する耐性を高くし易い。このため、接触箇所P0以外の部分にエッチングが行われた場合には、電子部品200の電極210又は220と金属箔1002との間(特に接着層400)でエッチングが止まり易くなると考えられる。これにより、製造過程における電子部品200の電極210、220の損傷等が抑制されるようになり、ひいては配線板10の電気的信頼性を高めることが可能になる。その結果、配線板10の歩留まりが向上すると考えられる。

【0095】

なお、領域R31、R32の中でも特に電子部品200の電極210又は220と金属箔1002とが接触し易い箇所は、電子部品200の電極210又は220の外側の縁の直上であると考えられる。このため、導体層301が、少なくとも電子部品200の電極210又は220の外側の縁の直上に面状の導体パターン301a、301bを有していれば、製造過程における電子部品200の電極210、220の損傷等が抑制されるようになり、ひいては配線板10の電気的信頼性を高めることが可能になると考えられる。

【0096】

続けて、図5のステップS16で、コア部Cの両面にビルドアップを行う。

【0097】

具体的には、図14に示すように、コア部Cの第1面F1上及び導体層301上に絶縁層101を配置し、コア部Cの第2面F2上及び導体層302上に絶縁層102を配置する。さらに、絶縁層101上に金属箔1008を配置し、絶縁層102上に金属箔1009を配置する。絶縁層101及び102はそれぞれ、例えばガラエポのプリプレグからなる。そして、半硬化状態の絶縁層101及び102をコア部C及び導体層301、302に接着させ、プレスする。これにより、図15に示すように、絶縁層101及び102の各々を構成する樹脂(絶縁体300c)が流出して、スルーホール300aにおけるスルーホール導体300bの内側に充填される。また、プレスと同時に又はプレスの後に、積層板を加熱して絶縁層101、102の各々を硬化させる。両面の絶縁層101、102の硬化を同時に行うことにより、コア部Cの反りを抑制し易くなる。

【0098】

続けて、例えばレーザにより、絶縁層101及び金属箔1008に孔311a及び312a(それぞれビアホール)を形成し、絶縁層102及び金属箔1009に孔322a(ビアホール)を形成する(図16参照)。孔311a及び312aの各々は絶縁層101及び金属箔1008を貫通し、孔322aは絶縁層102及び金属箔1009を貫通する。そして、孔311a及び312aの各々は導体層301に至り、孔322aは導体層302に至る。より詳しくは、孔311aは面状の導体パターン301a、301b(図4)に至る。その後、必要に応じて、デスミアを行う。

【0099】

続けて、例えばパネルめっき法により、図16に示すように、積層板の表面、すなわち金属箔1008、1009上及び孔311a、312a、322a内にそれぞれ、例えば銅の無電解めっき膜1010、1011及び電解めっき1012、1013を形成する。具体的には、まず、例えば化学めっき法により例えば銅の無電解めっき膜1010、1011を形成して、続けてめっき液を用いて、無電解めっき膜1010、1011をシード層として、例えば銅の電解めっき1012、1013を形成する。これにより、孔311a及び312a、孔322aに、それぞれ電解めっき1012、1013が充填され、例えば銅のめっきからなるビア導体311b、312b、322bが形成される。

【0100】

続けて、例えばエッチングレジスト及びエッチング液を用いて、絶縁層101、102上に形成された各導体層のパターニングを行う。具体的には、導体層110、120に対応したパターンを有するエッチングレジストで各導体層を覆い、各導体層の、エッチングレジストで覆われない部分(エッチングレジストの開口部で露出する部位)を、エッチングで除去する。これにより、図17に示すように、絶縁層101、102上にそれぞれ、導体層110、120が形成される。なお、エッチングは、湿式に限られず、乾式であってもよい。その結果、コア部Cの第1面F1上に、絶縁層101及び導体層110から構成される第1ビルドアップ部B1が形成され、コア部Cの第2面F2上に、絶縁層102及び導体層120から構成される第2ビルドアップ部B2が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1010、1011に代えて、スパッタ膜等をシード層として用いてもよい。

【0101】

続けて、図5のステップS17で、絶縁層101、102上にそれぞれ、開口部11aを有するソルダーレジスト11、開口部12aを有するソルダーレジスト12を形成する(図1参照)。導体層110、120はそれぞれ、開口部11a、12aに位置する所定の部位(パッドP1、P2等)を除いて、ソルダーレジスト11、12で覆われる。ソルダーレジスト11及び12は、例えばスクリーン印刷、スプレーコーティング、ロールコーティング、又はラミネート等により、形成することができる。

【0102】

続けて、スパッタリング等により、導体層110、120上、詳しくはソルダーレジスト11、12に覆われないパッドP1、P2(図1参照)の表面にそれぞれ、例えばNi/Au膜からなる耐食層を形成する。また、OSP処理を行うことにより、有機保護膜からなる耐食層を形成してもよい。

【0103】

以上の工程により、本実施形態の配線板10(図1)が完成する。その後、必要があれば、電子部品200の電気テスト(容量値及び絶縁性などのチェック)を行う。

【0104】

本実施形態の製造方法は、配線板10の製造に適している。こうした製造方法であれば、低コストで、良好な配線板10が得られると考えられる。

【0105】

本実施形態の配線板10は、例えば電子部品又は他の配線板と電気的に接続することができる。例えば半田等により、配線板10のパッドP2に、電子部品200とは別の電子部品(例えばICチップ)を実装することができる。また、パッドP1により、配線板10を他の配線板(例えばマザーボード)に実装することができる。本実施形態の配線板10は、例えば携帯電話の回路基板として用いることができる。

【0106】

(実施形態2)

本発明の実施形態2について、上記実施形態1との相違点を中心に説明する。なおここでは、上記図1等に示した要素と同一の要素には各々同一の符号を付し、既に説明した共通の部分、すなわち説明が重複する部分については、その説明を省略又は簡略化する。

【0107】

本実施形態に係る配線板20は、図18に示すように、砂時計状(鼓状)のスルーホール導体300bを有する。具体的には、コア部Cにスルーホール300aが形成され、スルーホール300a内に導体(例えば銅めっき)が充填されることにより、スルーホール導体300bが形成される。スルーホール導体300bは、最小幅となる括れ部300dを有し、コア部Cの第1面F1及び第2面F2の各々から括れ部300dに向かって幅が狭くなるようにテーパしている。コア部Cの第1面F1上の導体層301とコア部Cの第2面F2上の導体層302とは、スルーホール導体300bを介して、互いに電気的に接続される。孔312aは導体層301(詳しくは、スルーホール導体300bの直上)に至り、孔322aは導体層302(詳しくはスルーホール導体300bの直上)に至る。

【0108】

本実施形態では、電子部品200及びビア導体401b、402b、311bが、電源ラインを構成する。また、本実施形態では、ビア導体312b、322b及びスルーホール導体300bは、いずれもフィルド導体であり、これらがZ方向にスタックされることで、フィルドスタックSが形成される。そして、フィルドスタックSが信号ラインを構成する。

【0109】

本実施形態に係る配線板20の図3及び図4中に示す各寸法の好ましい値の一例を示す。

【0110】

キャビティR10の長手方向の幅D1は約680μmであり、キャビティR10の短手方向の幅D2は約380μmである。電子部品200の長手方向の幅D11は約600μmであり、電子部品200の短手方向の幅D12は約300μmである。電極210の上部210aもしくは下部210c、又は、電極220の上部220aもしくは下部220cの幅D13は、約230μmである。

【0111】

ビア導体401b及び402bの幅(最大直径)はそれぞれ約60μmであり、ビア導体401bとビア導体402bとのピッチD5は、約420μmである。

【0112】

コア部Cの厚さは約200μmであり、電子部品200の厚さ(電極も含めた厚さ)は約150μm〜330μmの範囲にある。絶縁層101及び102の厚さはそれぞれ約30μmであり、内層の導体層301、302の厚さはそれぞれ約20μmであり、外層の導体層110、120の厚さはそれぞれ約15μmであり、ソルダーレジスト11及び12の厚さはそれぞれ約15μmである。そして、配線板10全体の厚さは約360μmである。また、内層の導体層301、302のL/Sはそれぞれ約25/25μmであり、外層の導体層110、120のL/Sはそれぞれ約15/15μmである。導体パターン301a及び301bの各々の形状及び寸法は、例えば約380μm(図4中の幅D30)×約450μm(図4中の幅D33)の矩形状である。なお、導体パターン301aはビア導体401bのランドに相当し、導体パターン301bはビア導体402bのランドに相当する。

【0113】

本実施形態の配線板20は、各導体層(導体層301、302、110、120)の形成を除けば、例えば実施形態1で説明した製造方法(図5)に準ずる製造方法によって製造することができる。以下、本実施形態に係る各導体層の形成方法について説明する。なお、本実施形態では、各導体層が、セミアディティブ(SAP)法により形成される。

【0114】

実施形態1と同様にして、積層板(絶縁層100a、100b、金属箔1002、1005、及び電子部品200)をプレスで一体化した後(図6A〜図10参照)、図19Aに示すように、例えばCO2レーザを用いて、Z1側からレーザを金属箔1002に照射することにより孔1007a、401a、402aを形成し、Z2側からレーザを金属箔1005に照射することにより孔1007bを形成する。孔1007aと孔1007bとは、X−Y平面において略同じ位置に形成され、最終的にはつながって、絶縁層100a及び100bを貫通するスルーホール300aとなる。レーザでスルーホール300aを形成する場合には、スルーホール300a(詳しくは、孔1007a)と孔401a、402aとを同時に形成することが好ましい。ただしこれに限られず、スルーホール300a(詳しくは、孔1007a)と孔401a、402aとは別々に形成してもよい。

【0115】

スルーホール300aの形状は、スルーホール導体300bに対応し、砂時計状(鼓状)である。孔1007aと孔1007bとの境界は括れ部300d(図19B参照)に相当する。Z1側からのレーザ照射とZ2側からのレーザ照射とは、同時に行っても、片面ずつ行ってもよい。スルーホール300a及び孔401a、402aを形成した後には、デスミア(クリーニング)を行うことが好ましい。デスミアにより、不要な導通(ショート)が抑制される。また、レーザ光の吸収効率を高めるため、レーザ照射に先立って金属箔1002及び1005の表面を黒化処理してもよい。なお、スルーホール300aの形成は、湿式又は乾式エッチングなど、レーザ以外の方法で行ってもよい。ただし、レーザ加工であれば、微細な加工をし易い。

【0116】

続けて、例えば化学めっき法により、積層板の表面、すなわち金属箔1002、1005上、スルーホール300a内、及び孔401a、402a内にそれぞれ、例えば銅の無電解めっき膜1006を形成する(図19B参照)。なお、無電解めっきに先立って、例えば浸漬により、パラジウム等からなる触媒を、絶縁層100a及び100bの表面に吸着させてもよい。

【0117】

続けて、リソグラフィ技術又は印刷等により、第1面F1側の主面(無電解めっき膜1006上)に、開口部2001aを有するめっきレジスト2001を、また、第2面F2側の主面(無電解めっき膜1006上)に、開口部2002aを有するめっきレジスト2002を、それぞれ形成する(図16参照)。開口部2001a、2002aはそれぞれ、導体層301、302(図19C参照)に対応したパターンを有する。

【0118】

続けて、図19Bに示すように、例えばパターンめっき法により、めっきレジスト2001、2002の開口部2001a、2002aに、それぞれ例えば銅の電解めっき1007を形成する。具体的には、陽極にめっきする材料である銅を接続し、陰極に被めっき材である無電解めっき膜1006(シード層)を接続して、めっき液に浸漬する。そして、両極間に直流の電圧を印加して電流を流し、無電解めっき膜1006の表面に銅を析出させる。これにより、スルーホール300aに無電解めっき膜1006及び電解めっき1007が充填され、スルーホール導体300bが形成される。そしてその結果、絶縁層100a及び100bと、スルーホール導体300bと、を有するコア部Cが形成される。また、孔401a、402aの各々に無電解めっき膜1006及び電解めっき1007が充填され、ビア導体401b、402bが形成される。

【0119】

その後、例えば所定の剥離液により、めっきレジスト2001及び2002を除去し、続けて不要な無電解めっき膜1006及び金属箔1002、1005を除去することにより、図19Cに示すように、コア部Cの第1面F1上に導体層301が形成され、コア部Cの第2面F2上に導体層302が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1006に代えて、スパッタ膜等をシード層として用いてもよい。

【0120】

続けて、実施形態1と同様にして、絶縁層101、102、金属箔1008、1009、及び孔311a、312a、322aを形成した後、例えば化学めっき法により、積層板の表面、すなわち金属箔1008、1009上及び孔311a、312a、322a内にそれぞれ、例えば銅の無電解めっき膜1010、1011を形成する(図20A参照)。なお、無電解めっきに先立って、例えば浸漬により、パラジウム等からなる触媒を、絶縁層101、102の表面に吸着させてもよい。

【0121】

続けて、リソグラフィ技術又は印刷等により、第1面F1側の主面(無電解めっき膜1010上)に、開口部2003aを有するめっきレジスト2003を、また、第2面F2側の主面(無電解めっき膜1011上)に、開口部2004aを有するめっきレジスト2004を、それぞれ形成する(図20A参照)。開口部2003a、2004aはそれぞれ、導体層110、120(図1)に対応したパターンを有する。

【0122】

続けて、図20Aに示すように、例えばパターンめっき法により、めっきレジスト2003、2004の開口部2003a、2004aに、それぞれ例えば銅の電解めっき1012、1013を形成する。具体的には、陽極にめっきする材料である銅を接続し、陰極に被めっき材である無電解めっき膜1010、1011(シード層)を接続して、めっき液に浸漬する。そして、両極間に直流の電圧を印加して電流を流し、無電解めっき膜1010、1011の表面に銅を析出させる。これにより、孔311a及び312a、孔322aに、それぞれ電解めっき1012、1013が充填され、例えば銅のめっきからなるビア導体311b、312b、322bが形成される。

【0123】

その後、例えば所定の剥離液により、めっきレジスト2003及び2004を除去し、続けて不要な無電解めっき膜1010、1011及び金属箔1008、1009を除去することにより、図20Bに示すように、導体層110及び120が形成される。その結果、コア部Cの第1面F1上に、絶縁層101及び導体層110から構成される第1ビルドアップ部B1が形成され、コア部Cの第2面F2上に、絶縁層102及び導体層120から構成される第2ビルドアップ部B2が形成される。なお、電解めっきのためのシード層は無電解めっき膜に限られず、無電解めっき膜1010、1011に代えて、スパッタ膜等をシード層として用いてもよい。

【0124】

本実施形態の製造方法によれば、配線板20(図18)を製造することができる。本実施形態の製造方法は、配線板20の製造に適している。こうした製造方法であれば、低コストで、良好な配線板20が得られる。また、実施形態1と同様の構成及び処理については、本実施形態でも、前述した実施形態1の効果に準ずる効果が得られる。

【0125】

(他の実施形態)

図21Aに示すように、導体パターン301a、301bの3辺が、隙間R1の直上に配置されてもよい。

【0126】

面状の導体パターン301a又は301bが、電子部品200の電極210又は220の4辺全ての直上に配置され、ひいては電極210又は220全域の直上に配置されることは必須ではない。例えば図21Bに示すように、導体層301が電極210の内側端E12(詳しくは、第1端E13から第2端E14までの全域)の直上に導体パターンを有していなくてもよい。また、導体層301が電極220の内側端E22(詳しくは、その一部)の直上に導体パターンを有していなくてもよい。導体層301が、電極210又は220の外側の縁の少なくとも一部の直上に面状の導体パターン301a又は301bを有していれば、電子部品内蔵配線板における電気的接続の信頼性を高めることが可能になる。なお、外側の縁の直上に面状の導体パターンを形成する場合、面状の導体パターンが外側の縁の直上に跨って形成されるのが好ましい態様である。

【0127】

第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21はそれぞれ、電子部品200の端面と一致しなくてもよい。例えば図22Aに示すように、第1端E13、E23及び第2端E14、E24が、電子部品200の端面よりも内側(電子部品200の直上)に位置してもよい。また、例えば図22Bに示すように、第1端E13及びE23、第2端E14及びE24、並びに外側端E11及びE21がそれぞれ、電子部品200の端面よりも内側(電子部品200の直上)に位置してもよい。図22A及び図22Bのいずれに示す例でも、電極210、220の外側の縁(外側端E11及びE21、第1端E13及びE23、及び第2端E14及びE24)は、電子部品200の外縁(4辺)近傍に位置している。こうした構成においても、導体層301が、電極210又は220の外側の縁の直上に面状の導体パターン301a又は301bを有することで、電子部品200の電極210又は220と金属箔1002とが接触し易い電子部品200の外縁近傍(図7A及び図7B参照)におけるエッチングによる損傷等が抑制されることになる。

【0128】

配線板におけるスルーホール導体、各ビア導体、又はこれらのランドの形状は任意であり、これらの平面形状は、例えば図23Aに示すように、略正方形等の四角形であってもよく、例えば図23B又は図23Cに示すように、略十字形又は略正多角星形など、中心から放射状に直線を引いた形(複数の羽根を放射状に配置した形)であってもよく、その他、略真円、略楕円、又は略三角形等であってもよい。なお、多角形の角の形状は任意であり、例えば略直角でも、鋭角でも、鈍角でも、丸みを帯びていてもよい。

【0129】

電子部品200及びキャビティR10の形状は任意である。例えば図24に示すように、キャビティR10の開口形状が略楕円であってもよい。電子部品200の主面の形状及びキャビティR10の開口形状はそれぞれ、略真円であってもよく、また、略正方形、略正六角形、略正八角形など、略長方形以外の略多角形であってもよい。なお、多角形の角の形状は任意であり、例えば略直角でも、鋭角でも、鈍角でも、丸みを帯びていてもよい。

【0130】

上記各実施形態では、電子部品200の主面の形状が略長方形(D11>D12)であり、電極210及び220が電子部品200の長手方向に並んでいる(図3参照)。しかしこれに限定されず、電子部品200の主面の形状は、例えば正方形(D11=D12)であってもよい。

【0131】

上記各実施形態では、キャビティR10(電子部品200の収容スペース)に電子部品200を1つのみ有する配線板10を示したが、これに限られない。例えばキャビティR10に複数の電子部品200を有する配線板であってもよい。複数の電子部品200は、積層方向(Z方向)に並べて配置しても、X方向又はY方向に並べて配置してもよい。また、1つの配線板に複数のキャビティR10を形成してもよい。

【0132】

上記各実施形態では、電子部品200の電極210、220にそれぞれ1つずつのビア導体401b、402bが接続される例を示したが、ビア導体401b及び402bの数は任意である。例えば図25に示すように、電子部品200の1つの電極(電極210又は220)が、複数(例えば2つ)のビア導体(ビア導体401b又は402b)を介して、1つのビア導体のランド(導体パターン301a又は301b)と接続されてもよい。この場合、電極:ビア導体:ビアランド=1:複数:1となる。

【0133】

上記各実施形態では、コア部Cの両側に導体層を有する両面配線板(配線板10)を示したが、これに限られない。例えば図26に示すように、コア部C(例えば絶縁性を有する基板100)の片側のみに第1ビルドアップ部B1(導体層110を含む)を有する片面配線板であってもよい。

【0134】

上記各実施形態では、コア部Cが絶縁層100a及び100bの2層構造を有するが、これに限定されない。例えば図26に示すように、コア部Cは1つの基板から構成されてもよい。

【0135】

例えば図26に示されるように、キャビティR10(電子部品200の収容スペース)は、基板100を貫通しない孔(凹部)であってもよい。

【0136】

上記各実施形態では、コア部Cの両側に、それぞれ1層の第1ビルドアップ部B1及び第2ビルドアップ部B2を有する配線板10を示したが、これに限られない。コア部Cの片側に2層以上のビルドアップ部を有する配線板であってもよい。

【0137】

電子部品200の電極の形状は、U字形状に限定されず、例えば図27に示すように、各実施形態に係る電極210、220の下部210c、220c(又は上部210a、220a)がないL字形状であってもよく、あるいは図28に示すように、平板状の電極対(電極200a及び200b)でコンデンサ本体201を挟んでもよい。

【0138】

電子部品200の種類は、MLCCに限られず任意である。電子部品200はコンデンサに限られず、例えば図29に示すように、チップ抵抗であってもよい。図29に示すチップ抵抗は基板201aを有し、さらに基板201a上に、電極200aと、抵抗部201bと、電極200bと、を有する。電子部品200は受動部品にも限られず、IC(集積回路)等からなる能動部品であってもよい。

【0139】

配線板10の構成、及びその構成要素の種類、性能、寸法、材質、形状、層数、又は配置等は、本発明の趣旨を逸脱しない範囲において任意に変更することができる。

【0140】

例えば配線板におけるスルーホール導体又は各ビア導体は、フィルド導体に限られず、例えばコンフォーマル導体であってもよい。例えば図30に示すように、ビア導体401b、402bがコンフォーマル導体であってもよい。

【0141】

配線板の製造工程は、上記図5に示した順序や内容に限定されるものではなく、本発明の趣旨を逸脱しない範囲において任意に順序や内容を変更することができる。また、用途等に応じて、必要ない工程を割愛してもよい。

【0142】

上記各実施形態では、キャリア1001(支持材)上に接着層400を形成した後、その接着層400上に電子部品200を設けるようにしたが(図6C及び図6D参照)、これに限られず、接着層400が塗布された電子部品200を、キャリア1001(支持材)上に設けるようにしてもよい。

【0143】

配線板10における各導体層の形成方法は任意である。例えばパネルめっき法、パターンめっき法、フルアディティブ法、セミアディティブ法、サブトラクティブ法、転写法、及びテンティング法のいずれか1つ、又はこれらの2以上を任意に組み合わせた方法で、導体層を形成してもよい。

【0144】

また、レーザに代えて、湿式又は乾式のエッチングで加工してもよい。エッチングで加工する場合には、予め除去したくない部分をレジスト等で保護しておくことが好ましいと考えられる。

【0145】

上記各実施形態や変形例等は、任意に組み合わせることができる。用途等に応じて適切な組み合わせを選ぶことが好ましいと考えられる。例えば図21A〜図22Bのいずれかに示した構造を、図23A〜図30のいずれかに示した構造に適用してもよい。

【0146】

以上、本発明の実施形態について説明したが、設計上の都合やその他の要因によって必要となる様々な修正や組み合わせは、「請求項」に記載されている発明や「発明を実施するための形態」に記載されている具体例に対応する発明の範囲に含まれると理解されるべきである。

【産業上の利用可能性】

【0147】

本発明に係る電子部品内蔵配線板は、携帯電話などの回路基板に適している。本発明に係る電子部品内蔵配線板の製造方法は、そうした配線板の製造に適している。

【符号の説明】

【0148】

10 配線板

11、12 ソルダーレジスト

11a、12a 開口部

100 基板

100a、100b 絶縁層

100c 絶縁体

101、102 絶縁層

110、120 導体層

200 電子部品

200a、200b 電極

201 コンデンサ本体

201a 基板

201b 抵抗部

210、220 電極

210a、220a 上部

210b、220b 側部

210c、220c 下部

211〜214 導体層

221〜224 導体層

231〜239 誘電層

300a スルーホール

300b スルーホール導体

300c 絶縁体

300d 括れ部

301 導体層

301a〜301d 導体パターン

302 導体層

311a、312a、322a 孔

311b、312b、322b ビア導体

400 接着層

401a、402a 孔

401b、402b ビア導体

1001 キャリア

1002、1005 金属箔

1003、1004 孔

1006 膜

1007a、1007b 孔

1008、1009 金属箔

1010、1011 無電解めっき膜

1012、1013 電解めっき

2001〜2004 めっきレジスト

2001a〜2004a 開口部

C コア部

S フィルドスタック

B1 第1ビルドアップ部

B2 第2ビルドアップ部

E11、E21 外側端

E12、E22 内側端

E13、E23 第1端

E14、E24 第2端

F1 第1面

F2 第2面

F3 第3面

F4 第4面

F10 壁面

P0 接触箇所

P1 パッド

P2 パッド

R10 キャビティ

R21 直上領域

R22 直上領域

R31 領域

R32 領域

【特許請求の範囲】

【請求項1】

収容部を有する基板と、

前記収容部に収容され、電極を有する電子部品と、

前記電子部品上に形成された絶縁層と、

前記絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、

前記ビア導体を介して前記電極に電気的に接続される導体層と、

を有する電子部品内蔵配線板において、

前記導体層は、前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、

ことを特徴とする電子部品内蔵配線板。

【請求項2】

前記導体層は、前記電子部品の外縁近傍における前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、

ことを特徴とする請求項1に記載の電子部品内蔵配線板。

【請求項3】

前記面状の導体パターンは、前記ビア導体のランドである、

ことを特徴とする請求項1又は2に記載の電子部品内蔵配線板。

【請求項4】

前記電子部品は、一端近傍に第1電極を、他端近傍に第2電極をそれぞれ有し、

前記面状の導体パターンは、前記電子部品の前記一端及び前記他端の少なくとも一方の直上に位置する、

ことを特徴とする請求項1乃至3のいずれか一項に記載の電子部品内蔵配線板。

【請求項5】

前記第1電極及び前記第2電極は、前記電子部品の長手方向に並んでいる、

ことを特徴とする請求項4に記載の電子部品内蔵配線板。

【請求項6】

前記導体層は、前記一端又は前記他端から、前記電子部品の内側及び外側へそれぞれ少なくとも50μmまでの領域に、前記面状の導体パターンを有する、

ことを特徴とする請求項4又は5に記載の電子部品内蔵配線板。

【請求項7】

前記導体層は、前記電極全域の直上に前記面状の導体パターンを有する、

ことを特徴とする請求項1乃至6のいずれか一項に記載の電子部品内蔵配線板。

【請求項8】

前記電極は、前記電子部品の側面と上面と下面とに形成される、

ことを特徴とする請求項1乃至7のいずれか一項に記載の電子部品内蔵配線板。

【請求項9】

前記電極の1つが、複数の前記ビア導体を介して、前記ビア導体の1つのランドと接続される、

ことを特徴とする請求項3乃至8のいずれか一項に記載の電子部品内蔵配線板。

【請求項10】

前記絶縁層の少なくとも一部は、接着材料からなる、

ことを特徴とする請求項1乃至9のいずれか一項に記載の電子部品内蔵配線板。

【請求項11】

前記電子部品は、コンデンサからなる、

ことを特徴とする請求項1乃至10のいずれか一項に記載の電子部品内蔵配線板。

【請求項12】

前記面状の導体パターンは、エッチングによりパターニングされる、

ことを特徴とする請求項1乃至11のいずれか一項に記載の電子部品内蔵配線板。

【請求項13】

前記面状の導体パターンは、金属箔を含む、

ことを特徴とする請求項1乃至12のいずれか一項に記載の電子部品内蔵配線板。

【請求項14】

前記電子部品は、前記電子部品内蔵配線板のコア部に形成された開口部に配置される、

ことを特徴とする請求項1乃至13のいずれか一項に記載の電子部品内蔵配線板。

【請求項15】

前記ビアホールは、前記開口部における前記絶縁層に形成される、

ことを特徴とする請求項14に記載の電子部品内蔵配線板。

【請求項16】

前記コア部上に導体層を有し、

前記電極に電気的に接続される導体層は、前記コア部上の導体層と同一の層にある、

ことを特徴とする請求項15に記載の電子部品内蔵配線板。

【請求項17】

電極を有する電子部品を準備することと、

前記電子部品上に絶縁層を形成することと、

前記絶縁層にビアホールを形成することと、

前記ビアホール内にビア導体を形成することと、

前記電極の外側の縁の直上に、少なくとも一箇所で前記ビア導体を介して前記電極に電気的に接続される面状の導体パターンを形成することと、

を含む、電子部品内蔵配線板の製造方法。

【請求項18】

前記面状の導体パターンを、サブトラクティブ法により形成する、

ことを特徴とする請求項17に記載の電子部品内蔵配線板の製造方法。

【請求項19】

前記絶縁層の形成は、

少なくとも片面に導体膜を有する支持材を準備することと、

前記導体膜上に、絶縁性の接着層を介して、前記電子部品を固定することと、

開口部を有する絶縁基板を準備することと、

前記接着層により固定された状態の前記電子部品を、前記絶縁基板の前記開口部に配置することと、

前記電子部品から前記支持材を取り外すことと、

を含む、

ことを特徴とする請求項17又は18に記載の電子部品内蔵配線板の製造方法。

【請求項1】

収容部を有する基板と、

前記収容部に収容され、電極を有する電子部品と、

前記電子部品上に形成された絶縁層と、

前記絶縁層に形成されたビアホール内に導体が形成されてなるビア導体と、

前記ビア導体を介して前記電極に電気的に接続される導体層と、

を有する電子部品内蔵配線板において、

前記導体層は、前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、

ことを特徴とする電子部品内蔵配線板。

【請求項2】

前記導体層は、前記電子部品の外縁近傍における前記電極の少なくとも1つの外側の縁の直上に面状の導体パターンを有する、

ことを特徴とする請求項1に記載の電子部品内蔵配線板。

【請求項3】

前記面状の導体パターンは、前記ビア導体のランドである、

ことを特徴とする請求項1又は2に記載の電子部品内蔵配線板。

【請求項4】

前記電子部品は、一端近傍に第1電極を、他端近傍に第2電極をそれぞれ有し、

前記面状の導体パターンは、前記電子部品の前記一端及び前記他端の少なくとも一方の直上に位置する、

ことを特徴とする請求項1乃至3のいずれか一項に記載の電子部品内蔵配線板。

【請求項5】

前記第1電極及び前記第2電極は、前記電子部品の長手方向に並んでいる、

ことを特徴とする請求項4に記載の電子部品内蔵配線板。

【請求項6】

前記導体層は、前記一端又は前記他端から、前記電子部品の内側及び外側へそれぞれ少なくとも50μmまでの領域に、前記面状の導体パターンを有する、

ことを特徴とする請求項4又は5に記載の電子部品内蔵配線板。

【請求項7】

前記導体層は、前記電極全域の直上に前記面状の導体パターンを有する、

ことを特徴とする請求項1乃至6のいずれか一項に記載の電子部品内蔵配線板。

【請求項8】

前記電極は、前記電子部品の側面と上面と下面とに形成される、

ことを特徴とする請求項1乃至7のいずれか一項に記載の電子部品内蔵配線板。

【請求項9】

前記電極の1つが、複数の前記ビア導体を介して、前記ビア導体の1つのランドと接続される、

ことを特徴とする請求項3乃至8のいずれか一項に記載の電子部品内蔵配線板。

【請求項10】

前記絶縁層の少なくとも一部は、接着材料からなる、

ことを特徴とする請求項1乃至9のいずれか一項に記載の電子部品内蔵配線板。

【請求項11】

前記電子部品は、コンデンサからなる、

ことを特徴とする請求項1乃至10のいずれか一項に記載の電子部品内蔵配線板。

【請求項12】

前記面状の導体パターンは、エッチングによりパターニングされる、

ことを特徴とする請求項1乃至11のいずれか一項に記載の電子部品内蔵配線板。

【請求項13】

前記面状の導体パターンは、金属箔を含む、

ことを特徴とする請求項1乃至12のいずれか一項に記載の電子部品内蔵配線板。

【請求項14】

前記電子部品は、前記電子部品内蔵配線板のコア部に形成された開口部に配置される、

ことを特徴とする請求項1乃至13のいずれか一項に記載の電子部品内蔵配線板。

【請求項15】

前記ビアホールは、前記開口部における前記絶縁層に形成される、

ことを特徴とする請求項14に記載の電子部品内蔵配線板。

【請求項16】

前記コア部上に導体層を有し、

前記電極に電気的に接続される導体層は、前記コア部上の導体層と同一の層にある、

ことを特徴とする請求項15に記載の電子部品内蔵配線板。

【請求項17】

電極を有する電子部品を準備することと、

前記電子部品上に絶縁層を形成することと、

前記絶縁層にビアホールを形成することと、

前記ビアホール内にビア導体を形成することと、

前記電極の外側の縁の直上に、少なくとも一箇所で前記ビア導体を介して前記電極に電気的に接続される面状の導体パターンを形成することと、

を含む、電子部品内蔵配線板の製造方法。

【請求項18】

前記面状の導体パターンを、サブトラクティブ法により形成する、

ことを特徴とする請求項17に記載の電子部品内蔵配線板の製造方法。

【請求項19】

前記絶縁層の形成は、

少なくとも片面に導体膜を有する支持材を準備することと、

前記導体膜上に、絶縁性の接着層を介して、前記電子部品を固定することと、

開口部を有する絶縁基板を準備することと、

前記接着層により固定された状態の前記電子部品を、前記絶縁基板の前記開口部に配置することと、

前記電子部品から前記支持材を取り外すことと、

を含む、

ことを特徴とする請求項17又は18に記載の電子部品内蔵配線板の製造方法。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図6C】

【図6D】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12A】

【図12B】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図20A】

【図20B】

【図21A】

【図21B】

【図22A】

【図22B】

【図23A】

【図23B】

【図23C】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【図2】

【図3】

【図4】

【図5】

【図6A】

【図6B】

【図6C】

【図6D】

【図7A】

【図7B】

【図8】

【図9】

【図10】

【図11A】

【図11B】

【図12A】

【図12B】

【図13】

【図14】

【図15】

【図16】

【図17】

【図18】

【図19A】

【図19B】

【図19C】

【図20A】

【図20B】

【図21A】

【図21B】

【図22A】

【図22B】

【図23A】

【図23B】

【図23C】

【図24】

【図25】

【図26】

【図27】

【図28】

【図29】

【図30】

【公開番号】特開2012−204831(P2012−204831A)

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願番号】特願2012−36724(P2012−36724)

【出願日】平成24年2月22日(2012.2.22)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

【公開日】平成24年10月22日(2012.10.22)

【国際特許分類】

【出願日】平成24年2月22日(2012.2.22)

【出願人】(000000158)イビデン株式会社 (856)

【Fターム(参考)】

[ Back to top ]