電気回路

【課題】 定電流電源からの駆動電力の遮断直後や駆動電力の供給中における機能素子の着脱によって機能素子が破壊や劣化することを抑制する。

【解決手段】出力端と基準電位端との間に静電容量を含む定電流電源1と着脱自在な機能素子2とを電気的に接続する電気回路において、機能素子2を介して定電流電源1の出力端に接続される第1回路端及び定電流電源1の基準電位端に接続される第2回路端を含み、機能素子2の装着された接続状態から機能素子2の抜脱された非接続状態への移行に応じて回路端間のインピーダンスを非接続時インピーダンスにまで増加させ、接続状態移行に応じて回路端間のインピーダンスを接続時インピーダンスにまで減少させる素子破壊防止回路10を含む構成とする。

【解決手段】出力端と基準電位端との間に静電容量を含む定電流電源1と着脱自在な機能素子2とを電気的に接続する電気回路において、機能素子2を介して定電流電源1の出力端に接続される第1回路端及び定電流電源1の基準電位端に接続される第2回路端を含み、機能素子2の装着された接続状態から機能素子2の抜脱された非接続状態への移行に応じて回路端間のインピーダンスを非接続時インピーダンスにまで増加させ、接続状態移行に応じて回路端間のインピーダンスを接続時インピーダンスにまで減少させる素子破壊防止回路10を含む構成とする。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、定電流電源と定電流電源からの電力で駆動する着脱自在な機能素子とを接続する電気回路において、機能素子の着脱に応じた機能素子の破壊を防止する電気回路に関する。

【背景技術】

【0002】

従来の典型的な発光装置において、LEDを点灯させるために、定電圧電源に抵抗とLEDを直列に接続して、抵抗によってLEDに流れる電流を調整したり、図12(A)に示されたように定電圧電源1とLED2との間に電流制限回路を直列に接続して、電流制限回路によってLEDに流れる電流を調整したりしていた。しかし、このように、抵抗や電流制限回路を直列に接続するとLEDの通常駆動時に挿入した抵抗や電流制限回路が負荷となり、エネルギー損失を発生させていた。

【0003】

近年になり、LEDの高輝度化が進み、従来の表示用のLEDとは異なり、大電流で駆動する必要が生じてきた。このように大電流で駆動される場合には、従来の典型的な発光装置と同様の構成とすれば、挿入される抵抗や電流制限回路による負荷に基づくエネルギー損失が増大する。このようなエネルギー損失を低減すると共に小型化を促進するために、定電圧電源に代えて定電流電源が用いられることが増えてきた。

【0004】

なお、従来の一般的な電源には、安定した電圧や電流を供給するためや、ノイズ等による変動を低減するために、基準電位端と出力端との間にコンデンサが設けられている(例えば、特許文献1参照)。このコンデンサには、定電流電源の作動中にはコンデンサの容量と定電流電源の出力電圧に応じた電荷が蓄積される。なお、作動停止後であっても自然放電によって電荷が完全に放出されるまでは、電荷が蓄積されている。

【0005】

一般的な定電流電源1からの電力によってLED2を点灯させる従来の典型的な発光装置では、図12(B)に示されたように、定電流電源1とLED2とが配線で接続されている。このような場合には、コンデンサC1に電荷が蓄積されている状態において、LED2が装着されるとLED2が破損したり、劣化したりする。これは、電流制限回路からは所定の電流値の電流しか供給されないが、コンデンサC1に蓄積されている電荷はLED2を装着する際に瞬時に放電されるために、瞬間的に極めて大きな電流(瞬時電流)となって流れるからである。

【0006】

【特許文献1】特開2004−119078号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

LEDの破壊や劣化を防止するためには、定電流電源の作動を停止させてから所定の時間だけ待ってから行えばよい。しかし、大電流で駆動するLEDの場合、コンデンサC1に蓄積される電荷量も倍増し、自然放電の完了を待つのは現実的な解決策ではなくなってきた。また、非常灯等の緊急事態の発生を報知するための発光装置においては、その監視を行っている機器等が稼働している限りにおいて、安全確保のために決して非常灯を消灯することはできない。したがって、非常灯を構成する全部又は一部のLEDの交換のためにそれらの機器等を停止することは避けなければならず、定電流電源を作動させたままでLEDの交換をできる装置が熱望されていた。また、複数の発色のLEDを多数配置して図形や模様や画像を形成させる場合には、発光色や配置場所を目視で確認しながら作業できるように、定電流電源を作動させたままでLEDを交換できる装置が熱望されていた。

【0008】

上記においてはコンデンサが出力端と基準電位端との間を接続している場合について説明したが、出力端と基準電位端との間に静電容量を有する定電流電源の全般についても同様である。また、上記においては発光装置の場合について説明したが、定電流電源によって駆動される着脱自在な機能素子を備える電気機器の一般についても同様である。

【0009】

そこで、本発明に係る電気回路では、定電流電源からの電力遮断直後や電力供給中における機能素子の着脱によって機能素子が破壊や劣化することを防止すると共に、機能素子の通常駆動時におけるインピーダンスの増加を抑制する。

【課題を解決するための手段】

【0010】

上記の課題を解決するために、本発明に係る電気回路は、

出力端と基準電位端と間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記機能素子を介して前記定電流電源の前記出力端に接続される第1回路端及び前記定電流電源の前記基準電位端に接続される第2回路端を含む素子破壊防止回路を備え、

前記素子破壊防止回路が、

前記機能素子の抜脱により前記第1回路端と前記定電流電源の前記出力端とが電気的に接続されていない状態を非接続状態とし、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴としている。

【発明の効果】

【0011】

本発明に係る電気回路であれば、容量素子の蓄積電荷の放電は、接続状態への状態移行の直後において第1回路端と前記第2回路端との間のインピーダンスが接続時インピーダンスへ完全に変化し終える前(実質的に非接続時インピーダンスの場合)に開始されるために、放電に基づく放電電流が急峻に変化することを抑制できる。これによって、一般的な定電流電源からの電力供給の遮断直後や電力供給中における機能素子の着脱によって機能素子が破損されたり、劣化したりすることを抑制できる。また、機能素子が装着され、機能素子が通常状態で駆動している場合には、第1回路端と前記第2回路端との間のインピーダンスが低インピーダンス(接続時インピーダンス)に変化した素子破壊防止回路を介して電力が供給されるために、素子破壊防止回路の負荷によるエネルギー損失を低減できる。

【発明を実施するための最良の形態】

【0012】

本発明に係る電気機器の最良の形態について説明する。なお、本発明の概念的な構成について説明した後に、具体的な構成について図面を参照しながら説明する。

【0013】

本発明に係る電気回路は、出力端と基準電位端との間に静電容量を含む定電流電源と、定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、機能素子を介して定電流電源の前記出力端に接続される第1回路端及び定電流電源の基準電位端に接続される第2回路端を含む素子破壊防止回路を備えている。機能素子の抜脱により第1回路端と定電流電源の出力端とが電気的に接続されていない状態を「非接続状態」と称し、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を「接続状態」と称する。

【0014】

「基準電位」とは、定電流電源と素子破壊防止回路とで電圧の基準となる共通の電位であって、通常、接地電位である。また、「定電流電源の基準電位端に接続され」とは、具体的に配線によって接続されている場合に限らず、定電流電源と素子破壊防止回路とが個別に接地されていてもよいことを意味する。

【0015】

素子破壊防止回路は、接続状態から非接続状態への状態移行に応じて、第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させる。また、素子破壊防止回路は、非接続状態から接続状態への状態移行に応じて、第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続インピーダンスより低い接続時インピーダンスにまで減少させる。ここで、「自己整合的に」とは、機能素子の装着以外の人的操作をすることなく回路状態、例えば、所定の箇所の電圧値や所定の箇所の電流値に応じて決定されることを意味する。なお、静電容量に蓄積された電荷の放電は、接続状態への状態移行の直後において、第1回路端と前記第2回路端との間のインピーダンスが接続時インピーダンスへ変化し終える前(実質的に非接続時インピーダンス)に開始される。

【0016】

素子破壊防止回路としては、例えば、機能素子の装着時における電気機器の内部抵抗を自己整合的に機能素子の通常の駆動状態の場合よりも大きくする回路や、放電自体を緩やかにさせる回路や、それらの組合せ回路が挙げられる。

【0017】

素子破壊防止回路がない場合には、定電流電源が非作動状態であっても蓄積電荷の少なくとも一部は瞬時に放電されるために、放電電流の時間変化は極めて時間幅の狭い尖塔(ピーク)波形となり、その最大値(ピーク値)は定常駆動状態における駆動電流値を遥かに越える値となる。しかし、その場合の放電量(移動電荷量)は、素子破壊防止回路の有無に関わらず、概ね、蓄積電荷量や機能素子の駆動電圧に応じた一定量であるために、電気機器の内部抵抗を大きくしたり、緩やかに放電させたりすれば、放電電流のピーク値が低減される。これによって、過剰な電流が流れることによる機能素子の破壊や破損を抑制できることとなる。また、定電流電源が作動状態であれば、素子破壊防止回路を除く電源回路からの供給電流に放電電流が重畳して更に大きな値となるために、素子破壊防止回路における放電電流の低減率を大きくする必要がある。

【0018】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記制御端の電圧を制御する電圧依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0019】

「スイッチング素子」とは、少なくとも2つの異なる抵抗値を選択的に発現できる素子を意味し、2値選択する素子であってもよいし、多値選択する素子であってもよいし、連続的に変化する値をとる素子であってもよい。スイッチング素子としては、例えば、トランジスタ等の電気作用によって抵抗値を制御できる素子や、フォトカプラ等の光作用によって抵抗値を制御できる素子や、磁気作用によって抵抗値を制御できる素子が挙げられる。「電流流入端」とは、電流が流入する端子(電子が流出する端子)であって、トランジスタの場合であればドレイン端やコレクタ端を意味する。「電流流出端」とは、電流が流出する端子(電子が流入する端子)であって、トランジスタの場合であればソース端やエミッタ端を意味する。また、「制御端」とは、電流流入端と電流流出端との間の抵抗値を変更するための電流信号又は電圧信号が入力される端子であり、トランジスタの場合であればゲート端やベース端を意味する。

【0020】

この構成であれば、第1回路端と第2回路端との間のインピーダンスをスイッチング素子による抵抗値の制御によって変化させるために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを変化させることができる。また、スイッチング素子の電流流入端の電圧の変化に基づいて抵抗値を制御するために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを自己整合的に制御できる。

【0021】

前記素子破壊防止回路が、

前記機能素子に接続された電流流入端と、前記定電流電源の前記基準電位端に接続された電流流出端と、前記電流流入端と前記電流流出端との間の抵抗値を制御する制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端へ流入する電流の変化に基づいて、前記制御端の電圧を制御する電流依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0022】

この構成であれば、第1回路端と第2回路端との間のインピーダンスをスイッチング素子による抵抗値の制御によって変化させるために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを変化させることができる。また、第1回路端に流入する電流の変化に基づいて抵抗値を制御するために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを自己整合的に制御できる。

【0023】

前記素子破壊防止回路が、前記接続状態への状態移行に応じて前記第1回路端と前記第2回路端との間のインピーダンスを前記接続時インピーダンスより低いインピーダンスに変化させる低インピーダンス化促進回路を更に含む構成であることが好ましい。具体的には、例えば、前記接続状態への状態移行に応じて前記スイッチング素子の前記電流流入端と前記電流流出端との間の抵抗を前記接続時抵抗値より低い抵抗値にまで変化させる無抵抗化回路を更に含む構成が挙げられる。

【0024】

この構成であれば、機能素子の通常の駆動時における素子破壊防止回路に起因する負荷の増加を更に抑制できる。更に、その負荷の増加を実質的に防止することもできる。

【0025】

前記素子破壊防止回路が、前記非接続状態への状態移行に伴う前記第1回路端と前記第2回路端との間のインピーダンスの変化を高速化する高インピーダンス化促進回路を更に含む構成であることが好ましい。具体的には、例えば、前記非接続状態への状態移行に伴う前記スイッチング素子の前記電流流入端と前記電流流出端との間の抵抗の変化を高速化する高抵抗化促進回路を更に含む構成が挙げられる。

【0026】

この構成であれば、非接続状態へ移行した場合に第1回路端と第2回路端との間のインピーダンス(電流流入端と電流流出端との間の抵抗)を高速で高インピーダンス化(高抵抗化)できるために、具体的には、スイッチング素子の完全なオフ状態への移行を高速で行えるために、短期間において接続状態への移行や非接続状態への移行が繰り返されたとしても機能素子の破壊や劣化を抑制できる。これによって、機能素子の着脱時におけるチャタリングや不測の着脱の繰り返しに起因する破壊や劣化も抑制できる。

【0027】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記機能素子の装着過程において前記定電流電源の前記出力端に接続される付加回路端を更に含み、

前記非接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0028】

この構成であれば、機能素子の通常の駆動時における素子破壊防止回路に起因する負荷の増加を更に抑制できる。更に、その負荷の増加を実質的に防止することもできる。

【0029】

ここで、本発明に係る素子破壊防止回路の具体的な形態について、図面を参照しながら説明する。なお、以下においては、機能素子がLEDである場合を一例として挙げて、その種々の形態について説明する。

【0030】

〔実施形態1〕

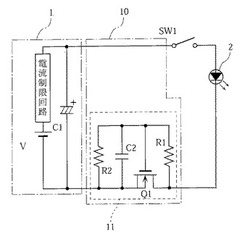

実施形態1の素子破壊防止回路について説明する。図1は、実施形態1に係る素子破壊防止回路の一例を表す回路図である。図1には、素子破壊防止回路10と共に定電流電源1及びLED2も示されている。なお、図1において、スイッチSW1は、LED2とは別に設けられたスイッチ素子ではなく、LED2の接続状態と非接続状態との間の移行を表すための仮想的なスイッチである。例えば、定電流電源1の出力端(上側配線端)と電気的に接続された第1入出力端子及び第2入出力端子を含み、LED2を着脱自在に固定するソケット(図示せず)と、LED2とで構成されており、LED2をソケットに装着することによって第1入出力端子と第2入出力端子とが電気的に接続され、LED2をソケットから抜脱することによってそれらの端子間が電気的に断絶される場合が挙げられる。したがって、スイッチSW1がオン状態である場合は、LED2が素子破壊防止回路10に電気的に接続されている接続状態を意味し、オフ状態である場合には、LED2が素子破壊防止回路10に電気的に接続されていない非接続状態を意味する。以下の各種の実施形態におけるスイッチSW1についても同様とする。

【0031】

素子破壊防止回路10の説明に先立ち、定電流電源1及びLED2について説明する。定電流電源1は、図1に示されたように、起電力回路としての直流電源Vと、直流電源Vと直列に接続され、直流電源Vから供給される電流を所定の最大電流値以下に制限する電流制限回路と、直列に接続された直流電源V及び電流制限回路に対して並列に接続された電解コンデンサC1(〔静電容量〕の一種)とを含んでいる。直流電源Vの低電位側は接地されている。定電流電源1がオン状態(電力供給状態)である場合には、電解コンデンサC1にはその容量と定電流電源1の出力電圧V0(接地電位に対する電位差)の電圧値(例えば、30〔V(ボルト)〕)とに応じた電荷(〔蓄積電荷〕)が蓄積されている。また、定電流電源1のオフ状態(電力供給停止状態)においても、自然放電によって蓄積電荷は減衰するものの、オフ状態への移行から長時間に渡り電荷が蓄積されている。LED2は、所定の駆動閾電圧値VF(例えば、20〔V〕)以上の電圧が印加された場合に発光し、その発光輝度は供給される電流値が大きくなるについて大きくなる。なお、定格最大電流値(例えば、5〔A(アンペア)〕)を超える電流が供給されるとLED2自体が破壊されて発光しなくなったり、その一部が損傷して正常な発光ができなくなったりする。直流電源Vの起電圧は駆動閾電圧値VF以上であり、電流制限回路からの出力電流I0の電流値(例えば、1〔A〕)は、LED2の定格最大電流値よりも小さい値である。電界コンデンサC1は、LED2の定常駆動状態において、直流電源Vや電流制限回路の出力電圧V0や出力電流I0等が急激に変動をしたとしてもその影響を緩和して、定電流電源1からの出力電圧がLED2の駆動閾電圧値VF以下になることやその出力電流I0がLED2の定格最大電流値を越えて大きくなることを抑制している。また、LED2の抜脱による接続状態から非接続状態への移行に伴うフライバック電流による直流電源Vや電流制限回路の破壊や破損を抑制している。なお、図1には、定電流電源1の出力端と基準電位端との間に電界コンデンサC1が設けられている場合が示されているが、電界コンデンサC1等の容量素子が実際には接続されておらず、直流電源Vや電流制限回路に静電容量が内在している場合であってもよい。また、図1には、起電力回路として直流電源Vが設けられている場合が示されているが、外部から供給される交流電力を直流電力に変換する起電力回路であってもよいし、外部から供給される直流電力を所定の電圧等に変換する起電力回路であってもよい。

【0032】

素子破壊防止回路10は、図1に示されたように、定電流電源1と反対側のLED2のカソード端と定電流電源1の接地電位端(下側配線端;〔基準電位端〕の一種)とを接続する過渡電流抑制回路11のみで構成されている。過渡電流抑制回路11は、LED2と電界トランジスタQ1のドレイン端(〔電流流入端〕及び〔第1回路端〕の一種)の電圧に基づいて、接続状態への移行後における過渡電流の急激な変化を抑制する。ここで、「接続状態への移行後における過渡電流」とは、LED2の装着による接続状態への移行後であって定常状態に至るまでの過渡期においてLED2に流れる電流を意味する。過渡電流は、定電流電源1がオン状態である場合には、電流制限回路を介して直流電源Vから供給される電流(以下、「基本電流」と称す)と電解コンデンサC1の放電に起因する電流(「放電電流」)との総和電流であり、定電流電源1がオフ状態(電力供給停止状態)である場合には、電解コンデンサC1の放電に起因する電流と同一である。なお、以下においては、定電流電源1のオン状態におけるLED2の装着によるLED2の破壊や劣化を防止できる場合には、定電流電源1のオフ状態におけるLED2の装着によるLED2の破壊や劣化は直流電源Vから供給される電流の影響がないために確実に防止できるために、定電流電源1のオン状態においてLED2を装着する場合についてのみ詳細に説明する。

【0033】

過渡電流抑制回路11は、電界効果トランジスタQ1(「スイッチング素子」の一種)と、過渡電流を抑制すると共に電界効果トランジスタQ1のゲート端(〔制御端〕の一種)の電圧を制御するゲート制御回路(「電圧依存型のスイッチング制御回路」の一種)とで構成されている。電界効果トランジスタQ1のドレイン端(〔電流流入端〕の一種)はLED2と接続され、ソース端(〔電流流出端〕の一種)は接地電位端と接続されている。ゲート制御回路は、電界効果トランジスタQ1のゲート端とLED2の一端とを接続する抵抗R1と、ゲート端と接地電位端とを接続するコンデンサC2と、ゲート端と接地電位端とを接続する抵抗R2とを含んでいる。抵抗R1及びコンデンサC2は、主に、過渡電流を抑制すると共に電界効果トランジスタQ1のオン状態への移行を制御する回路部を構成し、抵抗R2は、主に、電界効果トランジスタQ1のオフ状態への移行を制御する回路部を構成する。

【0034】

ここで、素子破壊抑制回路10(過渡電流抑制回路11)の動作について説明する。図2は、素子破壊抑制回路10の動作の一例を定性的に表すタイミングチャートであり、図2(A)がLED2に流れる電流の時間推移を表し、図2(B)がコンデンサC2の端子間電圧の時間推移を表し、図2(C)が電界効果トランジスタQ1のソース・ドレイン間抵抗の時間推移を表している。なお、図2においては、LED2の装着に応じて非接続状態から接続状態へ移行する場合の動作のみが示されている。また、図2(A)には、参考のために、過渡電流抑制回路11を設けない場合にLEDに流れる電流の時間推移が一点鎖線で示されている。これらは、後述する他の実施形態において参照するタイミングチャートにおいても同様である。

【0035】

まず、LED2の抜脱によって、図1に示されたように定電流電源1がオン状態であり、かつLED2の抜脱によって非接続状態(SW1のオフ状態)に移行してから所定の時間の経過後である非接続状態の定常期において、電解コンデンサC1の電圧は定電流電源1の出力電圧V0の電圧値と同一であり、コンデンサC2の両端電圧VC2の電圧値はVn〔V〕(Vn=0)であり、電界効果トランジスタQ1がオフ状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRn〔Ω(オーム)〕である。一方、定電流電源1がオン状態であり、かつLED2の装着によって接続状態(SW1のオン状態)に移行してから所定の時間の経過後である接続状態の定常期において、電解コンデンサC1の電圧は定電流電源1の出力電圧値と同一のV0〔V〕であり、コンデンサC2の両端電圧VC2の電圧値はVs〔V〕であり、電界効果トランジスタQ1がオン状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRs〔Ω〕である。

【0036】

LED2の装着が開始されて、非接続状態から接続状態へ移行すると(時刻t0)、電界効果トランジスタQ1のソース端及びドレイン端との間が開放されている場合に相当する接続移行直後閉回路に、直流電源Vに起因する基本電流及び電解コンデンサC1に起因する放電電流とを含む過渡電流の供給が開始される。

【0037】

過渡電流の供給が開始されたとしても、接続移行直後閉回路において直列に接続された抵抗R1及びコンデンサC2によって、LED2に流れる過渡電流の急激な増加が抑制されることになる。したがって、接続状態への移行直後において、図2(A)に示されたように、過渡電流ILEDの電流値は微少値In〔A〕である。なお、過渡電流抑制回路11がなくLED2のカソード端が定電流電源1の接地電位端に接続されている場合には、図2(A)に一点鎖線で示されたように、LED2の定常駆動時における出力電流I0の電流値Is〔A〕(例えば、Is=1)を遥かに越える電流値を最大値Im〔A〕(例えば、Im=28)とする尖塔波形の瞬時電流が流れる。

【0038】

接続状態への移行からの時間の経過に伴って、図2(B)に示されたように、過渡電流によってコンデンサC2が充電されることとなり、コンデンサC2の電圧VC2がVn〔V〕からVs〔V〕まで徐々に増加する(時刻ts)。その後、コンデンサC2の電圧VC2はVs〔V〕を維持する。

【0039】

また、この充電に応じて電界効果トランジスタQ1のゲート電圧(コンデンサC2の電圧VC2と同じ)が増加することによって、図2(C)に示されたように、ソース・ドレイン間の抵抗値が、Rn〔Ω〕からRs〔Ω〕まで徐々に減少する(時刻ts)。その後、ソース・ドレイン間の抵抗値はRs〔Ω〕を維持する。なお、電界効果トランジスタQ1のゲート電圧が所定の閾電圧を越えるまでは、実質的にソース・ドレイン間抵抗RQ1の抵抗値は減少を始めない。

【0040】

過渡電流ILEDの電流値は、図2(A)に示されたように、過渡期の初期段階においては、過渡電流ILEDの供給開始の後に抵抗R2を介した電流路が形成されると共にその電流路を介して流れる過渡電流ILEDの分流成分がコンデンサC2の電圧VC2の増加に伴って増加するために、In〔A〕から微増する。なお、この初期段階においては、電界効果トランジスタQ1はオフ状態を維持しているために、ソース・ドレイン間抵抗RQ1の抵抗値は直列に接続された抵抗R1と抵抗R2との合成抵抗値よりも遥かに大きいために、過渡電流ILEDの電流路として殆ど機能しない。しかし、その後、コンデンサC2の電圧VC2の増加に伴うソース・ドレイン間抵抗RQ1の抵抗値が抵抗R1と抵抗R2との合成抵抗値よりも小さくなると、過渡電流ILEDの電流路として電界効果トランジスタQ1を介した電流路が抵抗R1及び抵抗R2を介した電流路よりも支配的になり、図2(A)に示されたように、ソース・ドレイン間抵抗RQ1の抵抗値の急峻な減少に応じてIs〔A〕まで急峻に増加する(時刻ts)。その後、LED2には電流値がIs〔A〕である定常電流が供給される。

【0041】

LED2に定常電流が供給されている接続状態の定常期においては、実質的に、過渡電流抑制回路11に代えて抵抗R1及び抵抗R2の合成抵抗よりも遥かに小さい抵抗値Rs〔Ω〕の抵抗をLED2と定電流電源1の接地電位端との間に設けた場合に相当する閉回路が形成される。

【0042】

一方、LED2の抜脱が開始されて接続状態から非接続状態へ移行すると、コンデンサC2が抵抗R2を介して放電を開始する。この放電によって、コンデンサC2の電圧VC2がVs〔V〕からVn(=0)〔V〕に減少し、その後はVn〔V〕を維持する。また、コンデンサC2の両端電位VC2の減少に伴う電界効果トランジスタQ1のゲート電圧の電圧値の減少に応じて、ソース・ドレイン間抵抗RQ1の抵抗値が、Rs〔Ω〕からRn〔Ω〕に増加し、その後はRn〔Ω〕を維持する。

【0043】

本形態の素子破壊防止回路10(過渡電流抑制回路11)であれば、LED2の装着による接続状態への移行後の過渡期の初期において、過渡電流の主電流路として、直列に接続された抵抗R1及びコンデンサC2を介する電流路が形成されること、及び、その後の過渡電流の主電流路となっていく電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値が序々に減少していくことによって、急激な過渡電流の変化を抑制でき、LED2の定格最大電流値、実質的に接続状態の定常期の電流値Is〔A〕を越える瞬時電流が流れることを防止できる。これによって、定電流電源1が電力供給状態である場合にLED2を着脱したとしてもLED2が破損や劣化することを防止できる。また、LED2の装着による接続状態への移行後の定常期において、定常電流の主電流路として、オン状態である電界効果トランジスタQ1のソース・ドレイン間を介する電流路が形成されることによって、通常のLED2の駆動における素子破壊防止回路10自体による負荷の増大を抑制できる。これによって、消費電力の増大や発熱等も抑制できる。過渡電流の主経路の形成や定常電流の主電流路の形成が、素子破壊防止回路10自体の回路状態に基づいて、具体的には、電界効果トランジスタQ1とLED2との素子間の電圧に応じた電界効果トランジスタQ1の制御に基づいて自動的に行われるために、LED2の交換等においてその着脱作業以外の人為的な作業を行う必要がなくなる。更に、過渡電流の急激な変化を抑制するためのコンデンサC2を電界効果トランジスタQ1のゲート電圧の制御に援用することによって、素子破壊防止回路10の回路構成を簡素化できる。

【0044】

上記においては、過渡電流抑制回路11が電界効果トランジスタQ1、抵抗R1、抵抗R2及びコンデンサC1で構成される場合について説明したが、接続状態の定常期における定常電流の主電流路がオン状態の電界効果トランジスタQ1を介する電流路となり、接続状態の過渡期の少なくとも初期において、過渡電流の主電流路が電界効果トランジスタQ1以外の経路であって少なくとも抵抗素子を介する電流路となる構成であってもよい。また、上記においては、コンデンサC2を過渡電流の急峻な変化を防止するための回路を構成する一部の素子と、電界効果トランジスタQ1のゲート電圧を制御するための回路との一部を構成する素子として兼用して回路構成の簡素化を図ったが各回路で個別にコンデンサを含む構成であってもよい。

【0045】

〔実施形態2〕

実施形態2に係る素子破壊防止回路は、実施形態1に係る素子破壊防止回路10よりも接続状態の定常期における素子破壊防止回路自身による負荷を低減できる構成である。図3は、実施形態2に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路20は、無抵抗化回路22を含むこと以外は、上記の実施形態1における素子破壊防止回路10(図1参照)と同一の構成である。以下においては、実施形態1と同一の構成部分については同一の参照符号を付すこととし、その詳細な説明は省略する。

【0046】

素子破壊防止回路20は、定常接続状態における電界効果トランジスタQ1のゲート電圧の電圧値を更に増加させてソース・ドレイン間抵抗の抵抗値を低下させて、実質的に無抵抗化する無抵抗化回路22(〔低インピーダンス化促進回路〕の一種:「電圧依存型のスイッチング制御回路」の一部の一種)を更に含んでいる。本形態においては、電界効果トランジスタQ1のオン状態への移行制御は、抵抗R1及びコンデンサC2からなる回路部と無抵抗化回路22との双方の援用によって行われる。

【0047】

無抵抗化回路22は、定電流電源1の出力端と接地電位端とを接続するように直列に配置されたツェナーダイオードZD1、抵抗R3及び抵抗R4を含む回路部と、出力端と接地電位端とを接続するように直列に配置された抵抗R5、抵抗R6及びトランジスタQ2、抵抗R5と抵抗6との素子間と接地電位端とを接続するツェナーダイオードZD2、抵抗6とトランジスタQ2との素子間と電界効果トランジスタQ1のゲート端とを接続するダイオードD1を含む回路部とで構成されている。トランジスタQ2のエミッタ端は抵抗R2と接続され、ベース端は抵抗R3と抵抗R4との素子間と接続されている。ツェナーダイオードZD1、抵抗R3及び抵抗R4を含む回路部は、主に、出力電圧V0の変化に応じてトランジスタQ2のオン状態とオフ状態との間の状態移行を制御する。他の回路部は、主に、トランジスタQ2のオフ状態への移行に応じて、電界効果トランジスタQ1のからオン状態への状態移行を制御する回路部を構成する。

【0048】

図3に示された非接続状態の定常状態において、電解コンデンサC1の両端電圧は定電流電源1の出力電圧V0の電圧値と同一であり、コンデンサC2の端子間電圧VC2の電圧値はVn〔V〕(Vn=0)であり、電界効果トランジスタQ1がオフ状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRn〔Ω(オーム)〕である。また、ツェナーダイオードZD1はブレークスルー電圧を維持しており、トランジスタQ2は出力電圧V0からツェナーダイオードZD1のブレークスルー電圧を減じた電圧を抵抗R3及び抵抗R4で抵抗分割した抵抗R3と抵抗R4との素子間の電圧値によってオン状態を維持している。

【0049】

一方、定電流電源1がオン状態であり、かつLED2の装着によって接続状態(SW1のオン状態)に移行してから所定の時間の経過後である接続状態の定常期において、電解コンデンサC1の両端電圧は定電流電源1の出力電圧値と同一のV0〔V〕であり、コンデンサC2の両端電圧VC2の電圧値はVs〔V〕であり、電界効果トランジスタQ1がオン状態であってそのソース・ドレイン間抵抗の実効的な抵抗値はRs’〔Ω(オーム)〕である。また、ツェナーダイオードZD1を介しての電流や、トランジスタQ2を介しての電流や、ダイオードD1を介しての電流は実質的に遮断されている。なお、このような非接続状態や接続状態の定常期の動作が実現されるように各種の回路素子は選択されている。

【0050】

ここで、図4は、素子破壊防止回路20の動作の一例を定性的に表すタイミングチャートであり、図4(A)がLEDに流れる電流の時間推移を表し、図4(B)がコンデンサC2の端子間電圧の時間推移を表し、図4(C)が電界効果トランジスタのソース・ドレイン間抵抗の時間推移を表している。

【0051】

LED2の装着が開始されて非接続状態から接続状態へ移行すると(時刻t0)、過渡電流ILEDの供給が開始されるが、上記の実施形態1の場合と同様の動作原理によってLED2に流れる過渡電流ILEDの急激な増加が抑制されることになる。接続状態への移行からの時間の経過に伴って、図4(B)に示されたように、過渡電流ILEDによってコンデンサC2が充電されることとなり、コンデンサC2の両端電圧VC2がVn〔V〕からVs〔V〕まで徐々に増加する(時刻ts)。また、この充電に応じて電界効果トランジスタQ1のゲート電圧(コンデンサC2の両端電圧VC2と同じ)の電圧値が増加することによって、図4(C)に示されたように、ソース・ドレイン間抵抗RQ1の抵抗値がRn〔Ω〕からRs〔Ω〕まで減少する(時刻ts)。ここまでの過渡現象は、上記の実施形態1の場合と定性的に同一である。

【0052】

ソース・ドレイン間抵抗RQ1の抵抗値の減少に伴って、定電流電源1の外部の合成抵抗が低下するために、出力電圧V0の電圧値が減少する。なお、このとき、電界効果トランジスタQ1のソース・ドレイン間の電圧は、電界効果トランジスタQ1がオン状態を保持できるソース・ゲート間の電圧と同一なるまで減少する。この出力電圧V0の電圧値の減少に伴って、その電圧値がツェナーダイオードZD1のブレークスルー電圧値よりも小さくなり、出力端からツェナーダイオードZD1への電流が遮断される(時刻ts)。この遮断によって、抵抗R3と抵抗R4との素子間の電圧が実質的に接地電位となり、トランジスタQ2がオフ状態へ移行する。この移行によって、図4(B)に示されたように、抵抗R5、抵抗R6及びダイオードD1を介して供給される電流によってコンデンサC2が更に充電されて、コンデンサC2の両端電圧VC2がVs’〔V〕まで更に増加する(時刻ts’)。その後、コンデンサC2の電圧VC2はVs’〔V〕に維持される。また、この充電によって、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値はRs’〔Ω〕(Rs≒0)まで減少する(時刻ts’)。その後、ソース・ドレイン間の抵抗RQ1はRs’〔Ω〕に維持される。なお、過渡電流ILEDの電流値の変化は、上記の実施形態1の場合と定性的に同一である。

【0053】

本形態に係る素子破壊防止回路20であれば、上記の実施形態1の素子破壊防止回路10の場合に比べて、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値を更に低下させることができるために、通常のLED2の駆動における素子破壊防止回路20に起因する負荷の増大を更に良好に抑制できる。また、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値を実質的に0〔Ω〕にできるために、素子破壊防止回路20を設けない従来の構成(図12(B)参照)と比べて、素子破壊防止回路20に起因する負荷の増加を極めて良好に抑制できることとなる。

【0054】

上記においては、図3に示された無抵抗化回路22によって接続状態の定常期における電界効果トランジスタQ1のゲート電圧を無抵抗化回路22を設けない場合よりも高い電圧値に制御する場合について説明したが、ゲート電圧の電圧値を高い電圧値に制御できる構成であればいかなる構成であってもよい。

【0055】

〔実施形態3〕

実施形態3に係る素子破壊防止回路40は、LED(機能素子)の装着や抜脱の際において接続状態から非接続状態への移行やその逆の移行が微少時間間隔で複数回発生したとしても、その装着や抜脱の際に機能素子が破壊や劣化することを防止できる構成である。図5は、実施形態3に係る素子破壊防止回路の一例を表す回路図である。図5に示された本形態の素子破壊防止回路40は、高抵抗化促進回路43(〔高インピーダンス化促進回路〕の一種:「電圧依存型のスイッチング制御回路」の一部の一種)を含むこと以外は、上記の実施形態2における素子破壊防止回路20(図3参照)と同一の構成である。以下においては、実施形態2と同一の構成部分については同一の参照符号を付すこととし、その詳細な説明は省略する。

【0056】

高抵抗化促進回路43は、主に、過渡電流抑制回路11におけるコンデンサC2を強制的に放電させるための回路である。本形態においては、電界効果トランジスタQ1のオフ状態への移行制御は、抵抗R2からなる回路部と高抵抗化促進回路43との双方の援用によって行われる。具体的には、高抵抗化促進回路43は、LED2と接続される過渡電流抑制回路11の回路端の電圧に基づいて、過渡電流抑制回路11における抵抗R2によってコンデンサC2を放電させるよりも高速にその放電を行わせる回路である。

【0057】

LED2と接続される過渡電流抑制回路11の回路端と定電流電源1の接地電位端とを接続するように直列に配置された抵抗R10及び抵抗R8からなる回路部と、無抵抗化回路22の抵抗R5と抵抗R6との素子間と接地電位端とを接続するように直列に配置され、抵抗R8と抵抗R10との素子間の電圧に応じて制御されるトランジスタQ3及び抵抗R7からなる回路部と、抵抗R7とトランジスタQ3との素子間と接地電位端とを接続するように直列に配置されたコンデンサC3及び抵抗R9からなる回路部と、無抵抗化回路22のダイオードD1のカソード端(抵抗R1と抵抗R2との素子間)と接地電位端とを接続し、コンデンサC3と抵抗R9との素子間の電圧に応じて制御されるトランジスタQ4からなる回路部とで構成されている。トランジスタQ3のコレクタ端は抵抗R7に接続され、エミッタ端は定電流電源1の接地電位端に接続され、ベース端は抵抗R10と抵抗R8との素子間に接続されている。トランジスタQ4のコレクタ端はダイオードD1と過渡電流抑制回路11におけるコンデンサC2との素子間に接続されている。

【0058】

図5に示された非接続状態の定常期において、トランジスタQ3はオフ状態であり、また、トランジスタQ3がオフ状態であるためにトランジスタQ4もオフ状態である。その他の回路状態は、実施形態2の場合と同様である。一方、接続状態の定常期において、トランジスタQ3はオン状態であり、また、トランジスタQ4もオフ状態である。また、非接続状態における定電流電源1の出力電圧V0の電圧値は、接続状態の場合よりも大きい。

【0059】

接続状態から非接続状態に移行すると、抵抗R1や抵抗R10を介しての電流が遮断される。抵抗R1を介しての電流の遮断によってコンデンサC2が抵抗R2を介して放電を開始する。なお、抵抗R2を介しては緩やかに放電が進行する。一方、抵抗R10を介しての電流の遮断によって、トランジスタQ3のベース電圧が実質的に接地電位となり、トランジスタQ3がオフ状態に移行する。トランジスタQ3がオフ状態へ移行することにより、トランジスタQ4がオン状態へ移行し、トランジスタQ4(コレクタ端及びエミッタ端の間)を介してコンデンサC2の放電が開始される。なお、トランジスタQ4のコレクタ・エミッタ間抵抗RQ1は、抵抗R2よりも遥かに小さいために、コンデンサC2の放電を高速に行える。但し、コンデンサC3が存在するために、トランジスタQ4のオン状態は一時的であり、一旦オン状態へ移行した後に再度オフ状態へ自動的に移行する。更に詳しくは、コンデンサC3で直流成分を遮断しているのでLED2の有無による出力電圧V0の変化分が抵抗R5及び抵抗R7を通してコンデンサC3からトランジスタQ4のベース端に流れ、トランジスタQ4をオン状態に移行させる。出力電圧V0の変化がなくなると、抵抗R5、抵抗R7及びコンデンサC3からの電流がなくなるのでトランジスタQ4はオフ状態へ移行する。これによって、接続状態から非接続状態に状態移行した瞬間の出力電圧V0の変化の間だけトランジスタQ4がオン状態となり、非接続状態であっても出力電圧V0が安定した場合や、接続状態においてはオフ状態を維持している。

【0060】

逆に、非接続状態から接続状態に移行すると、出力電圧V0が低下すると共に、抵抗R1及び抵抗R10を介して過渡電流の供給が開始される。抵抗R10を流れる過渡電流の分流が増加するとトランジスタQ3のベース電圧が上昇し、過渡電流の分流の電流値が所定の電流値を超えると、トランジスタQ3がオン状態へ移行する。トランジスタQ3のオン状態への移行に応じてコンデンサC3が実質的に完全に放電し、この放電に伴ってトランジスタQ4のベース電圧が実質的に接地電位となる。これによって、トランジスタQ4が確実にオフ状態へと移行することとなる。これによって、上記の実施形態2と同様に接続状態への移行後の動作が実行される。

【0061】

ここで、LED2の装着の際に一旦接続状態に移行した後に、接続状態から非接続状態へ移行し、その後の短時間の間に再度接続状態に移行する場合について説明する。高抵抗化促進回路43を設けていないときには、接続状態への移行によって電界効果トランジスタQ1がオン状態へ移行し、その後、非接続状態へ移行したもののコンデンサC2の放電が電界効果トランジスタQ1をオフ状態に移行させるために十分な時間が確保されていない場合には、再度接続状態へ移行した際に電界効果トランジスタQ1がオン状態でLED2が接続されることとなり、その接続状態への移行の際に過渡電流の急峻な増加を十分に抑制できないことも考えられる。しかし、本形態であれば、非接続状態へ移行した場合に高速でコンデンサC2の放電が行え、つまり、電界効果トランジスタQ1の完全なオフ状態への移行を高速で行えるために、上記のような状況下であってもLED2の破壊や劣化を抑制できる。

【0062】

本形態に係る素子破壊防止回路40であれば、上記の実施形態2の素子破壊防止回路20の場合に比べて、LEDの着脱時におけるチャタリングや着脱の繰り返しによるLED2の破壊や劣化を抑制できる。

【0063】

上記においては、コンデンサC2の放電を過渡電流抑制回路11と高抵抗化促進回路43とを併用して行う場合について説明したが、高抵抗化促進回路43のみにおいてコンデンサC2の放電を制御する構成とすることもできる。この場合、過渡電流抑制回路11における抵抗R2はなくてもよい。また、図6に示された素子破壊防止回路50のように、抵抗R2を設けず、電界効果トランジスタQ1の制御を高精度で行うために、第1回路端と抵抗R1との間にダイオードD2を設けたり、第1回路端と電界効果トランジスタQ1のドレイン端との間に補正抵抗R11を設けたりしてもよい。

【0064】

上記においては、高抵抗化促進回路43によって接続状態から非接続状態への移行の際にコンデンサC2の放電を高速化する場合について説明したが、本発明に係る高抵抗化促進回路は、スイッチング素子(電界効果トランジスタQ1)のオン状態からオフ状態への移行を高速化できる構成であればいかなる構成であってもよい。

【0065】

〔実施形態4〕

実施形態4に係る素子破壊防止回路は、上記の実施形態1〜3の場合と同様に電圧に基づいてスイッチング素子(電界効果トランジスタQ1)を制御する構成である。図7は、実施形態4に係る素子破壊防止回路の一例を表す回路図である。

【0066】

図7に示された素子破壊防止回路60では、接続状態へ移行すると、まず、過渡電流が抵抗R12を介して流れる。なお、抵抗R12を介して流れる電流は微少値であり、これによって、過渡電流の急激な変化を抑制している。また、LED2のカソード端における電圧の変化に応じて、トランジスタQ4がオン状態へ移行する。トランジスタQ4がオン状態へ移行すると、抵抗R14とトランジスタQ4のコレクタ端との間の電圧が低下して、トランジスタQ5のベース電圧が実質的に接地電位となり、トランジスタQ5がオフ状態へ移行する。これによって、抵抗R15、抵抗R16及びコンデンサC4で構成される回路における抵抗R15と抵抗R16との素子間電圧がなだらかに増加する。これに応じて、電界効果トランジスタQ1のゲート電圧が増加し、所定の値を超えると、電界効果トランジスタQ1がオン状態に移行する。その後、接続状態の定常期となる。

【0067】

逆に、非接続状態へ移行すると、抵抗R13及び抵抗R12を流れる電流が遮断され、トランジスタQ4のベース電圧が実質的に接地電位となる。これによって、トランジスタQ4がオフ状態に移行する。また、トランジスタQ4のオフ移行に応じてトランジスタQ5がオン状態に移行し、その後、非接続状態の定常期となる。

【0068】

上記の構成であっても、実質的に上記の実施形態1〜3と同様の効果を奏することとなる。

【0069】

〔実施形態5〕

実施形態5に係る素子破壊防止回路は、上記の実施形態1〜4の場合と異なり、電流に基づいてスイッチング素子を制御する構成である。図8は、実施形態5に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路70は、図8に示されたように、電界効果トランジスタQ1(〔スイッチング素子〕)と、電界効果トランジスタQ1以外の素子で構成された、電界効果トランジスタQ1のゲート電圧を制御するゲート制御回路(〔電流依存型のゲート制御回路〕の一種)とで構成されている。なお、素子破壊防止回路70において、過渡電流抑制回路71は、上述の過渡電流抑制回路11(図1参照)と同様に、主に、過渡電流を抑制すると共に、電界効果トランジスタQ1のオン状態への移行及びオフ状態への状態移行の基本制御を行う回路である。また、高抵抗化促進回路73(〔高インピーダンス化促進回路〕の一種)は、上述の高抵抗化促進回路43(図5参照)と同様に、電界効果トランジスタQ1のオフ状態への状態移行を高速化する回路である。

【0070】

図8に示された非接続状態の定常状態において、トランジスタQ7はオフ状態であり、出力電圧V0の抵抗R21及び抵抗R19により分圧された電圧がトランジスタQ6のベース端に印加されることによってトランジスタQ6はオン状態であり、トランジスタQ6がオン状態であることによってトランジスタQ1がオフ状態である。

【0071】

非接続状態から接続状態へ移行する(t0)と、図9(D)に示されたように、トランジスタQ1がオフ状態であるために、R18及びR20に過渡電流が流れ始める。抵抗R18や抵抗R20を介して過渡電流が流れ出すために過渡電流の急峻な増加を低減できる。過渡電流の増加に伴い抵抗R18における降下電圧が増加し、これに伴ってトランジスタQ7のベース電圧が増加する。ベース電圧が増加して所定の電圧値以上となると、トランジスタQ7がオン状態に移行する。トランジスタQ7のオン状態への移行に伴って、図9(A)に示されたようにトランジスタQ6のベース電圧(抵抗R19の電圧VR19と同じ)の電圧値が実質的にV1〔V〕から接地電位(V0〔V〕)となり、トランジスタQ6がオフ状態に移行する。トランジスタQ6のオフ状態への移行によって、抵抗R1を介してコンデンサC2の充電が開始されて、図9(C)に示されたように、コンデンサC2の両端電圧VC2が増加する。なお、トランジスタQ6がオン状態である場合には、抵抗R1を流れる電流は実質的にトランジスタQ6のみを介して流れる。図9(D)に示されたように、電界効果トランジスタQ1のゲート電圧(コンデンサC2の両端電圧VC2と同じ)が増加して、そのゲート電圧が所定の電圧以上となると電界効果トランジスタQ1がオン状態に移行し、電界効果トランジスタQ1のオン状態への移行後は、そのゲート電圧の増加に伴って電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値がRs’〔Ω〕まで減少する。

【0072】

本形態の素子破壊防止回路70であれば、LED2の装着による接続状態への移行後の過渡期の初期において、過渡電流の主電流路として、抵抗R18及び抵抗20を介する電流路が形成されること、及び、その後の、過渡電流の主電流路となっていく電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値が徐々減少していくことによって、急峻な過渡電流の変化を抑制でき、LED2の定格最大電流値、実質的に接続状態の定常期の電流値Is〔A〕を越える瞬時電流が流れることを防止できる。これによって、定電流電源1が電力供給状態である場合にLED2を着脱したとしてもLED2が破損や劣化することを防止できる。また、LED2の装着による接続状態への移行後の定常期において、定常電流の主電流路として、オン状態である電界効果トランジスタQ1のソース・ドレイン間を介する電流路が形成されることによって、通常のLED2の駆動における素子破壊防止回路70による負荷の増大を抑制できる。これによって、消費電力の増大や発熱等も抑制できる。過渡電流の主経路の形成や定常電流の主電流路の形成が、素子破壊防止回路70の回路状態に基づいて、具体的には、LED2からの出力電流に応じた電界効果トランジスタQ1の制御に基づいて自動的に行われるために、LED2の交換等においてその着脱作業以外の人為的な作業を行う必要がなくなる。

【0073】

上記においては、過渡電流抑制回路が電界効果トランジスタQ1、抵抗R1、抵抗R2及びコンデンサC2で構成される場合について説明したが、接続状態の定常期における定常電流の主電流路がオン状態の電界効果トランジスタQ1を介する電流路となり、接続状態の過渡期の少なくとも初期において、過渡電流の主電流路が電界効果トランジスタQ1以外の経路であって少なくとも抵抗素子を介する電流路となる構成であってもよい。また、上記においては、コンデンサC2を過渡電流の急峻な変化を防止するための回路を構成する一部の素子と、電界効果トランジスタQ1のゲート電圧を制御するための回路との一部を構成する素子として兼用して回路構成の簡素化を図ったが各回路で個別にコンデンサを含む構成であってもよい。

【0074】

〔実施形態6〕

実施形態6に係る素子破壊防止回路は、機構的な接続状態の変化を援用して過渡電流を抑制する構成である。図10は、実施形態6に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路80は、過渡電流抑制回路81のみで構成されている。過渡電流抑制回路81は、図10に示されたように、電界効果トランジスタQ1(〔スイッチング素子〕)と、電界効果トランジスタQ1以外の素子で構成され、電界効果トランジスタQ1のゲート電圧を制御するゲート制御回路(〔電圧依存型のゲート制御回路〕の一種)とで構成されている。なお、素子破壊防止回路80において、過渡電流抑制回路81は、上述の過渡電流抑制回路11(図1参照)と同様に、主に、過渡電流を抑制すると共に、電界効果トランジスタQ1のオン状態への移行及びオフ状態への状態移行の制御を行う回路である。なお、過渡電流抑制回路11(図1参照)の電界効果トランジスタQ1のゲート電圧を実質的に制御することとなるコンデンサC2への電流供給路を構成する抵抗R1を別接点P4とした構成である。

【0075】

LED2の装着が開始されると、まず、接点P2と接点P4が接触する(t0)。その後、接点P1と接点P3が接触して(t0’)、LED2の装着が完了する。接点P2と接点P4とが接触すると、抵抗R1及びコンデンサC2を介して過渡電流が流れ、図11(B)に示されたように、コンデンサC2への充電が開始される。抵抗R1及びコンデンサC2を介して過渡電流が流れ出すために過渡電流の急峻な増加を低減できる。その後に、接点P1と接点P3との接触によって非接続状態から接続状態へ状態移行する。なお、この状態移行においては、既に、過渡電流の流れる閉回路が形成されているために瞬時電流の影響はほとんどない。その後の動作は、図11(A)〜(C)に示されたように、上記の実施形態1における過渡現象と定性的に同一である。なお、素子破壊防止回路80の抵抗R1の一端(電界効果トランジスタQ1のゲート端に接続されている側と反対側)がLED2のアノード端に接続されているため、抵抗R1の一端がLEDのカソード端に接続されている素子破壊防止回路10(図1参照)に比べて、電界効果トランジスタQ1のゲート電圧を高くすることができ、それによりソース・ドレイン間抵抗RQ1を低くすることができる。

【0076】

上記においては、接点P2と接点P4とが接触した後に、接点P1と接点P3とが接触する場合について説明したが、接点P1と接点P3とを先に接触させて、その後、接点P2と接点P4とを接触させる構成であってもよい。この場合においても、上記の場合と定性的に同一の制御が行え、実質的に同一の効果を奏する。また、接点P2と接点P4との接触を、接点P1と接点P3との接触と実質的に同時に行ってもよい。この場合においても、上記の場合と定性的に同一の制御が行え、実質的に同一の効果を奏する。

【0077】

上記の実施形態1〜6においては、機能素子が、LEDである場合について説明したが、他の発光素子であってもよい。更に、機能素子は、発光素子に限らず各種の発光以外の他の機能を発現する電気素子であってもよい。

【0078】

また、上記の実施形態1〜6においては、素子破壊防止回路が機能素子の2次側(LEDのカソード側)に配置されている場合について説明したが、機能素子の1次側(LEDのアノード側)に配置される構成であっても構わない。

【0079】

上記においては、素子破壊防止回路について説明したが、本発明においては、素子破壊防止回路を内蔵する各種の電気機器であってもよい。具体的には、例えば、素子破壊防止回路を含み、一般的な定電流電源と一般的な電気機器との間に接続して電気機器に含まれる機能素子を着脱自在にさせるアダプタや、素子破壊防止回路と定電流電源とを一体化した電源装置や、素子破壊防止回路と機能素子とを一体化した電気機器や、素子破壊防止回路と定電流電源及び機能素子とを一体化させた電気機器が挙げられる。なお、機能素子が大電流で駆動される大電流型機能素子である場合に本発明の効果が大きくなる。したがって、電気機器としては、大電流型LEDを備えたLED照明、LEDライト、LED看板、LED表示灯であることが好ましい。

【産業上の利用可能性】

【0080】

本発明は、定電流電源と機能素子を備えた電気機器とを接続するアダプタ、定電流電源装置、発光素子等の機能素子を備えた電気機器、例えば、広域や狭域を照らす照明機器(照明、ライト)、文字や図形や模様や画像や映像を表示する表示機器(看板、表示灯、画像表示装置)等の発光装置に利用できる。

【図面の簡単な説明】

【0081】

【図1】実施形態1に係る素子破壊防止回路の一例を表す回路図。

【図2】実施形態1に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図3】実施形態2に係る素子破壊防止回路の一例を表す回路図。

【図4】実施形態2に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図5】実施形態3に係る素子破壊防止回路の一例を表す回路図。

【図6】実施形態3に係る素子破壊防止回路の変形例を表す回路図。

【図7】実施形態4に係る素子破壊防止回路の一例を表す回路図。

【図8】実施形態5に係る素子破壊防止回路の一例を表す回路図。

【図9】実施形態5に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図10】実施形態6に係る素子破壊防止回路の一例を表す回路図。

【図11】実施形態6に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図12】(A)が定電圧電源を用いた従来の典型的なLED装置の電気的な構成を表し、(B)が定電流電源を用いた従来の典型的なLED装置の電気的な構成を表す回路図。

【符号の説明】

【0082】

1: 定電流電源

2: LED(機能素子)

10,20,40,50,60,70,80: 素子破壊防止回路

11,31,71,81: 過渡電流抑制回路

22: 無抵抗化回路(低インピーダンス化促進回路)

43,73: 高抵抗化促進回路(高インピーダンス化促進回路)

Q1: 電界効果トランジスタ(スイッチング素子)

【技術分野】

【0001】

本発明は、定電流電源と定電流電源からの電力で駆動する着脱自在な機能素子とを接続する電気回路において、機能素子の着脱に応じた機能素子の破壊を防止する電気回路に関する。

【背景技術】

【0002】

従来の典型的な発光装置において、LEDを点灯させるために、定電圧電源に抵抗とLEDを直列に接続して、抵抗によってLEDに流れる電流を調整したり、図12(A)に示されたように定電圧電源1とLED2との間に電流制限回路を直列に接続して、電流制限回路によってLEDに流れる電流を調整したりしていた。しかし、このように、抵抗や電流制限回路を直列に接続するとLEDの通常駆動時に挿入した抵抗や電流制限回路が負荷となり、エネルギー損失を発生させていた。

【0003】

近年になり、LEDの高輝度化が進み、従来の表示用のLEDとは異なり、大電流で駆動する必要が生じてきた。このように大電流で駆動される場合には、従来の典型的な発光装置と同様の構成とすれば、挿入される抵抗や電流制限回路による負荷に基づくエネルギー損失が増大する。このようなエネルギー損失を低減すると共に小型化を促進するために、定電圧電源に代えて定電流電源が用いられることが増えてきた。

【0004】

なお、従来の一般的な電源には、安定した電圧や電流を供給するためや、ノイズ等による変動を低減するために、基準電位端と出力端との間にコンデンサが設けられている(例えば、特許文献1参照)。このコンデンサには、定電流電源の作動中にはコンデンサの容量と定電流電源の出力電圧に応じた電荷が蓄積される。なお、作動停止後であっても自然放電によって電荷が完全に放出されるまでは、電荷が蓄積されている。

【0005】

一般的な定電流電源1からの電力によってLED2を点灯させる従来の典型的な発光装置では、図12(B)に示されたように、定電流電源1とLED2とが配線で接続されている。このような場合には、コンデンサC1に電荷が蓄積されている状態において、LED2が装着されるとLED2が破損したり、劣化したりする。これは、電流制限回路からは所定の電流値の電流しか供給されないが、コンデンサC1に蓄積されている電荷はLED2を装着する際に瞬時に放電されるために、瞬間的に極めて大きな電流(瞬時電流)となって流れるからである。

【0006】

【特許文献1】特開2004−119078号公報

【発明の開示】

【発明が解決しようとする課題】

【0007】

LEDの破壊や劣化を防止するためには、定電流電源の作動を停止させてから所定の時間だけ待ってから行えばよい。しかし、大電流で駆動するLEDの場合、コンデンサC1に蓄積される電荷量も倍増し、自然放電の完了を待つのは現実的な解決策ではなくなってきた。また、非常灯等の緊急事態の発生を報知するための発光装置においては、その監視を行っている機器等が稼働している限りにおいて、安全確保のために決して非常灯を消灯することはできない。したがって、非常灯を構成する全部又は一部のLEDの交換のためにそれらの機器等を停止することは避けなければならず、定電流電源を作動させたままでLEDの交換をできる装置が熱望されていた。また、複数の発色のLEDを多数配置して図形や模様や画像を形成させる場合には、発光色や配置場所を目視で確認しながら作業できるように、定電流電源を作動させたままでLEDを交換できる装置が熱望されていた。

【0008】

上記においてはコンデンサが出力端と基準電位端との間を接続している場合について説明したが、出力端と基準電位端との間に静電容量を有する定電流電源の全般についても同様である。また、上記においては発光装置の場合について説明したが、定電流電源によって駆動される着脱自在な機能素子を備える電気機器の一般についても同様である。

【0009】

そこで、本発明に係る電気回路では、定電流電源からの電力遮断直後や電力供給中における機能素子の着脱によって機能素子が破壊や劣化することを防止すると共に、機能素子の通常駆動時におけるインピーダンスの増加を抑制する。

【課題を解決するための手段】

【0010】

上記の課題を解決するために、本発明に係る電気回路は、

出力端と基準電位端と間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記機能素子を介して前記定電流電源の前記出力端に接続される第1回路端及び前記定電流電源の前記基準電位端に接続される第2回路端を含む素子破壊防止回路を備え、

前記素子破壊防止回路が、

前記機能素子の抜脱により前記第1回路端と前記定電流電源の前記出力端とが電気的に接続されていない状態を非接続状態とし、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴としている。

【発明の効果】

【0011】

本発明に係る電気回路であれば、容量素子の蓄積電荷の放電は、接続状態への状態移行の直後において第1回路端と前記第2回路端との間のインピーダンスが接続時インピーダンスへ完全に変化し終える前(実質的に非接続時インピーダンスの場合)に開始されるために、放電に基づく放電電流が急峻に変化することを抑制できる。これによって、一般的な定電流電源からの電力供給の遮断直後や電力供給中における機能素子の着脱によって機能素子が破損されたり、劣化したりすることを抑制できる。また、機能素子が装着され、機能素子が通常状態で駆動している場合には、第1回路端と前記第2回路端との間のインピーダンスが低インピーダンス(接続時インピーダンス)に変化した素子破壊防止回路を介して電力が供給されるために、素子破壊防止回路の負荷によるエネルギー損失を低減できる。

【発明を実施するための最良の形態】

【0012】

本発明に係る電気機器の最良の形態について説明する。なお、本発明の概念的な構成について説明した後に、具体的な構成について図面を参照しながら説明する。

【0013】

本発明に係る電気回路は、出力端と基準電位端との間に静電容量を含む定電流電源と、定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、機能素子を介して定電流電源の前記出力端に接続される第1回路端及び定電流電源の基準電位端に接続される第2回路端を含む素子破壊防止回路を備えている。機能素子の抜脱により第1回路端と定電流電源の出力端とが電気的に接続されていない状態を「非接続状態」と称し、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を「接続状態」と称する。

【0014】

「基準電位」とは、定電流電源と素子破壊防止回路とで電圧の基準となる共通の電位であって、通常、接地電位である。また、「定電流電源の基準電位端に接続され」とは、具体的に配線によって接続されている場合に限らず、定電流電源と素子破壊防止回路とが個別に接地されていてもよいことを意味する。

【0015】

素子破壊防止回路は、接続状態から非接続状態への状態移行に応じて、第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させる。また、素子破壊防止回路は、非接続状態から接続状態への状態移行に応じて、第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続インピーダンスより低い接続時インピーダンスにまで減少させる。ここで、「自己整合的に」とは、機能素子の装着以外の人的操作をすることなく回路状態、例えば、所定の箇所の電圧値や所定の箇所の電流値に応じて決定されることを意味する。なお、静電容量に蓄積された電荷の放電は、接続状態への状態移行の直後において、第1回路端と前記第2回路端との間のインピーダンスが接続時インピーダンスへ変化し終える前(実質的に非接続時インピーダンス)に開始される。

【0016】

素子破壊防止回路としては、例えば、機能素子の装着時における電気機器の内部抵抗を自己整合的に機能素子の通常の駆動状態の場合よりも大きくする回路や、放電自体を緩やかにさせる回路や、それらの組合せ回路が挙げられる。

【0017】

素子破壊防止回路がない場合には、定電流電源が非作動状態であっても蓄積電荷の少なくとも一部は瞬時に放電されるために、放電電流の時間変化は極めて時間幅の狭い尖塔(ピーク)波形となり、その最大値(ピーク値)は定常駆動状態における駆動電流値を遥かに越える値となる。しかし、その場合の放電量(移動電荷量)は、素子破壊防止回路の有無に関わらず、概ね、蓄積電荷量や機能素子の駆動電圧に応じた一定量であるために、電気機器の内部抵抗を大きくしたり、緩やかに放電させたりすれば、放電電流のピーク値が低減される。これによって、過剰な電流が流れることによる機能素子の破壊や破損を抑制できることとなる。また、定電流電源が作動状態であれば、素子破壊防止回路を除く電源回路からの供給電流に放電電流が重畳して更に大きな値となるために、素子破壊防止回路における放電電流の低減率を大きくする必要がある。

【0018】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記制御端の電圧を制御する電圧依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0019】

「スイッチング素子」とは、少なくとも2つの異なる抵抗値を選択的に発現できる素子を意味し、2値選択する素子であってもよいし、多値選択する素子であってもよいし、連続的に変化する値をとる素子であってもよい。スイッチング素子としては、例えば、トランジスタ等の電気作用によって抵抗値を制御できる素子や、フォトカプラ等の光作用によって抵抗値を制御できる素子や、磁気作用によって抵抗値を制御できる素子が挙げられる。「電流流入端」とは、電流が流入する端子(電子が流出する端子)であって、トランジスタの場合であればドレイン端やコレクタ端を意味する。「電流流出端」とは、電流が流出する端子(電子が流入する端子)であって、トランジスタの場合であればソース端やエミッタ端を意味する。また、「制御端」とは、電流流入端と電流流出端との間の抵抗値を変更するための電流信号又は電圧信号が入力される端子であり、トランジスタの場合であればゲート端やベース端を意味する。

【0020】

この構成であれば、第1回路端と第2回路端との間のインピーダンスをスイッチング素子による抵抗値の制御によって変化させるために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを変化させることができる。また、スイッチング素子の電流流入端の電圧の変化に基づいて抵抗値を制御するために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを自己整合的に制御できる。

【0021】

前記素子破壊防止回路が、

前記機能素子に接続された電流流入端と、前記定電流電源の前記基準電位端に接続された電流流出端と、前記電流流入端と前記電流流出端との間の抵抗値を制御する制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端へ流入する電流の変化に基づいて、前記制御端の電圧を制御する電流依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0022】

この構成であれば、第1回路端と第2回路端との間のインピーダンスをスイッチング素子による抵抗値の制御によって変化させるために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを変化させることができる。また、第1回路端に流入する電流の変化に基づいて抵抗値を制御するために、簡便かつ確実に第1回路端と第2回路端との間のインピーダンスを自己整合的に制御できる。

【0023】

前記素子破壊防止回路が、前記接続状態への状態移行に応じて前記第1回路端と前記第2回路端との間のインピーダンスを前記接続時インピーダンスより低いインピーダンスに変化させる低インピーダンス化促進回路を更に含む構成であることが好ましい。具体的には、例えば、前記接続状態への状態移行に応じて前記スイッチング素子の前記電流流入端と前記電流流出端との間の抵抗を前記接続時抵抗値より低い抵抗値にまで変化させる無抵抗化回路を更に含む構成が挙げられる。

【0024】

この構成であれば、機能素子の通常の駆動時における素子破壊防止回路に起因する負荷の増加を更に抑制できる。更に、その負荷の増加を実質的に防止することもできる。

【0025】

前記素子破壊防止回路が、前記非接続状態への状態移行に伴う前記第1回路端と前記第2回路端との間のインピーダンスの変化を高速化する高インピーダンス化促進回路を更に含む構成であることが好ましい。具体的には、例えば、前記非接続状態への状態移行に伴う前記スイッチング素子の前記電流流入端と前記電流流出端との間の抵抗の変化を高速化する高抵抗化促進回路を更に含む構成が挙げられる。

【0026】

この構成であれば、非接続状態へ移行した場合に第1回路端と第2回路端との間のインピーダンス(電流流入端と電流流出端との間の抵抗)を高速で高インピーダンス化(高抵抗化)できるために、具体的には、スイッチング素子の完全なオフ状態への移行を高速で行えるために、短期間において接続状態への移行や非接続状態への移行が繰り返されたとしても機能素子の破壊や劣化を抑制できる。これによって、機能素子の着脱時におけるチャタリングや不測の着脱の繰り返しに起因する破壊や劣化も抑制できる。

【0027】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記機能素子の装着過程において前記定電流電源の前記出力端に接続される付加回路端を更に含み、

前記非接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる構成であることが好ましい。

【0028】

この構成であれば、機能素子の通常の駆動時における素子破壊防止回路に起因する負荷の増加を更に抑制できる。更に、その負荷の増加を実質的に防止することもできる。

【0029】

ここで、本発明に係る素子破壊防止回路の具体的な形態について、図面を参照しながら説明する。なお、以下においては、機能素子がLEDである場合を一例として挙げて、その種々の形態について説明する。

【0030】

〔実施形態1〕

実施形態1の素子破壊防止回路について説明する。図1は、実施形態1に係る素子破壊防止回路の一例を表す回路図である。図1には、素子破壊防止回路10と共に定電流電源1及びLED2も示されている。なお、図1において、スイッチSW1は、LED2とは別に設けられたスイッチ素子ではなく、LED2の接続状態と非接続状態との間の移行を表すための仮想的なスイッチである。例えば、定電流電源1の出力端(上側配線端)と電気的に接続された第1入出力端子及び第2入出力端子を含み、LED2を着脱自在に固定するソケット(図示せず)と、LED2とで構成されており、LED2をソケットに装着することによって第1入出力端子と第2入出力端子とが電気的に接続され、LED2をソケットから抜脱することによってそれらの端子間が電気的に断絶される場合が挙げられる。したがって、スイッチSW1がオン状態である場合は、LED2が素子破壊防止回路10に電気的に接続されている接続状態を意味し、オフ状態である場合には、LED2が素子破壊防止回路10に電気的に接続されていない非接続状態を意味する。以下の各種の実施形態におけるスイッチSW1についても同様とする。

【0031】

素子破壊防止回路10の説明に先立ち、定電流電源1及びLED2について説明する。定電流電源1は、図1に示されたように、起電力回路としての直流電源Vと、直流電源Vと直列に接続され、直流電源Vから供給される電流を所定の最大電流値以下に制限する電流制限回路と、直列に接続された直流電源V及び電流制限回路に対して並列に接続された電解コンデンサC1(〔静電容量〕の一種)とを含んでいる。直流電源Vの低電位側は接地されている。定電流電源1がオン状態(電力供給状態)である場合には、電解コンデンサC1にはその容量と定電流電源1の出力電圧V0(接地電位に対する電位差)の電圧値(例えば、30〔V(ボルト)〕)とに応じた電荷(〔蓄積電荷〕)が蓄積されている。また、定電流電源1のオフ状態(電力供給停止状態)においても、自然放電によって蓄積電荷は減衰するものの、オフ状態への移行から長時間に渡り電荷が蓄積されている。LED2は、所定の駆動閾電圧値VF(例えば、20〔V〕)以上の電圧が印加された場合に発光し、その発光輝度は供給される電流値が大きくなるについて大きくなる。なお、定格最大電流値(例えば、5〔A(アンペア)〕)を超える電流が供給されるとLED2自体が破壊されて発光しなくなったり、その一部が損傷して正常な発光ができなくなったりする。直流電源Vの起電圧は駆動閾電圧値VF以上であり、電流制限回路からの出力電流I0の電流値(例えば、1〔A〕)は、LED2の定格最大電流値よりも小さい値である。電界コンデンサC1は、LED2の定常駆動状態において、直流電源Vや電流制限回路の出力電圧V0や出力電流I0等が急激に変動をしたとしてもその影響を緩和して、定電流電源1からの出力電圧がLED2の駆動閾電圧値VF以下になることやその出力電流I0がLED2の定格最大電流値を越えて大きくなることを抑制している。また、LED2の抜脱による接続状態から非接続状態への移行に伴うフライバック電流による直流電源Vや電流制限回路の破壊や破損を抑制している。なお、図1には、定電流電源1の出力端と基準電位端との間に電界コンデンサC1が設けられている場合が示されているが、電界コンデンサC1等の容量素子が実際には接続されておらず、直流電源Vや電流制限回路に静電容量が内在している場合であってもよい。また、図1には、起電力回路として直流電源Vが設けられている場合が示されているが、外部から供給される交流電力を直流電力に変換する起電力回路であってもよいし、外部から供給される直流電力を所定の電圧等に変換する起電力回路であってもよい。

【0032】

素子破壊防止回路10は、図1に示されたように、定電流電源1と反対側のLED2のカソード端と定電流電源1の接地電位端(下側配線端;〔基準電位端〕の一種)とを接続する過渡電流抑制回路11のみで構成されている。過渡電流抑制回路11は、LED2と電界トランジスタQ1のドレイン端(〔電流流入端〕及び〔第1回路端〕の一種)の電圧に基づいて、接続状態への移行後における過渡電流の急激な変化を抑制する。ここで、「接続状態への移行後における過渡電流」とは、LED2の装着による接続状態への移行後であって定常状態に至るまでの過渡期においてLED2に流れる電流を意味する。過渡電流は、定電流電源1がオン状態である場合には、電流制限回路を介して直流電源Vから供給される電流(以下、「基本電流」と称す)と電解コンデンサC1の放電に起因する電流(「放電電流」)との総和電流であり、定電流電源1がオフ状態(電力供給停止状態)である場合には、電解コンデンサC1の放電に起因する電流と同一である。なお、以下においては、定電流電源1のオン状態におけるLED2の装着によるLED2の破壊や劣化を防止できる場合には、定電流電源1のオフ状態におけるLED2の装着によるLED2の破壊や劣化は直流電源Vから供給される電流の影響がないために確実に防止できるために、定電流電源1のオン状態においてLED2を装着する場合についてのみ詳細に説明する。

【0033】

過渡電流抑制回路11は、電界効果トランジスタQ1(「スイッチング素子」の一種)と、過渡電流を抑制すると共に電界効果トランジスタQ1のゲート端(〔制御端〕の一種)の電圧を制御するゲート制御回路(「電圧依存型のスイッチング制御回路」の一種)とで構成されている。電界効果トランジスタQ1のドレイン端(〔電流流入端〕の一種)はLED2と接続され、ソース端(〔電流流出端〕の一種)は接地電位端と接続されている。ゲート制御回路は、電界効果トランジスタQ1のゲート端とLED2の一端とを接続する抵抗R1と、ゲート端と接地電位端とを接続するコンデンサC2と、ゲート端と接地電位端とを接続する抵抗R2とを含んでいる。抵抗R1及びコンデンサC2は、主に、過渡電流を抑制すると共に電界効果トランジスタQ1のオン状態への移行を制御する回路部を構成し、抵抗R2は、主に、電界効果トランジスタQ1のオフ状態への移行を制御する回路部を構成する。

【0034】

ここで、素子破壊抑制回路10(過渡電流抑制回路11)の動作について説明する。図2は、素子破壊抑制回路10の動作の一例を定性的に表すタイミングチャートであり、図2(A)がLED2に流れる電流の時間推移を表し、図2(B)がコンデンサC2の端子間電圧の時間推移を表し、図2(C)が電界効果トランジスタQ1のソース・ドレイン間抵抗の時間推移を表している。なお、図2においては、LED2の装着に応じて非接続状態から接続状態へ移行する場合の動作のみが示されている。また、図2(A)には、参考のために、過渡電流抑制回路11を設けない場合にLEDに流れる電流の時間推移が一点鎖線で示されている。これらは、後述する他の実施形態において参照するタイミングチャートにおいても同様である。

【0035】

まず、LED2の抜脱によって、図1に示されたように定電流電源1がオン状態であり、かつLED2の抜脱によって非接続状態(SW1のオフ状態)に移行してから所定の時間の経過後である非接続状態の定常期において、電解コンデンサC1の電圧は定電流電源1の出力電圧V0の電圧値と同一であり、コンデンサC2の両端電圧VC2の電圧値はVn〔V〕(Vn=0)であり、電界効果トランジスタQ1がオフ状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRn〔Ω(オーム)〕である。一方、定電流電源1がオン状態であり、かつLED2の装着によって接続状態(SW1のオン状態)に移行してから所定の時間の経過後である接続状態の定常期において、電解コンデンサC1の電圧は定電流電源1の出力電圧値と同一のV0〔V〕であり、コンデンサC2の両端電圧VC2の電圧値はVs〔V〕であり、電界効果トランジスタQ1がオン状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRs〔Ω〕である。

【0036】

LED2の装着が開始されて、非接続状態から接続状態へ移行すると(時刻t0)、電界効果トランジスタQ1のソース端及びドレイン端との間が開放されている場合に相当する接続移行直後閉回路に、直流電源Vに起因する基本電流及び電解コンデンサC1に起因する放電電流とを含む過渡電流の供給が開始される。

【0037】

過渡電流の供給が開始されたとしても、接続移行直後閉回路において直列に接続された抵抗R1及びコンデンサC2によって、LED2に流れる過渡電流の急激な増加が抑制されることになる。したがって、接続状態への移行直後において、図2(A)に示されたように、過渡電流ILEDの電流値は微少値In〔A〕である。なお、過渡電流抑制回路11がなくLED2のカソード端が定電流電源1の接地電位端に接続されている場合には、図2(A)に一点鎖線で示されたように、LED2の定常駆動時における出力電流I0の電流値Is〔A〕(例えば、Is=1)を遥かに越える電流値を最大値Im〔A〕(例えば、Im=28)とする尖塔波形の瞬時電流が流れる。

【0038】

接続状態への移行からの時間の経過に伴って、図2(B)に示されたように、過渡電流によってコンデンサC2が充電されることとなり、コンデンサC2の電圧VC2がVn〔V〕からVs〔V〕まで徐々に増加する(時刻ts)。その後、コンデンサC2の電圧VC2はVs〔V〕を維持する。

【0039】

また、この充電に応じて電界効果トランジスタQ1のゲート電圧(コンデンサC2の電圧VC2と同じ)が増加することによって、図2(C)に示されたように、ソース・ドレイン間の抵抗値が、Rn〔Ω〕からRs〔Ω〕まで徐々に減少する(時刻ts)。その後、ソース・ドレイン間の抵抗値はRs〔Ω〕を維持する。なお、電界効果トランジスタQ1のゲート電圧が所定の閾電圧を越えるまでは、実質的にソース・ドレイン間抵抗RQ1の抵抗値は減少を始めない。

【0040】

過渡電流ILEDの電流値は、図2(A)に示されたように、過渡期の初期段階においては、過渡電流ILEDの供給開始の後に抵抗R2を介した電流路が形成されると共にその電流路を介して流れる過渡電流ILEDの分流成分がコンデンサC2の電圧VC2の増加に伴って増加するために、In〔A〕から微増する。なお、この初期段階においては、電界効果トランジスタQ1はオフ状態を維持しているために、ソース・ドレイン間抵抗RQ1の抵抗値は直列に接続された抵抗R1と抵抗R2との合成抵抗値よりも遥かに大きいために、過渡電流ILEDの電流路として殆ど機能しない。しかし、その後、コンデンサC2の電圧VC2の増加に伴うソース・ドレイン間抵抗RQ1の抵抗値が抵抗R1と抵抗R2との合成抵抗値よりも小さくなると、過渡電流ILEDの電流路として電界効果トランジスタQ1を介した電流路が抵抗R1及び抵抗R2を介した電流路よりも支配的になり、図2(A)に示されたように、ソース・ドレイン間抵抗RQ1の抵抗値の急峻な減少に応じてIs〔A〕まで急峻に増加する(時刻ts)。その後、LED2には電流値がIs〔A〕である定常電流が供給される。

【0041】

LED2に定常電流が供給されている接続状態の定常期においては、実質的に、過渡電流抑制回路11に代えて抵抗R1及び抵抗R2の合成抵抗よりも遥かに小さい抵抗値Rs〔Ω〕の抵抗をLED2と定電流電源1の接地電位端との間に設けた場合に相当する閉回路が形成される。

【0042】

一方、LED2の抜脱が開始されて接続状態から非接続状態へ移行すると、コンデンサC2が抵抗R2を介して放電を開始する。この放電によって、コンデンサC2の電圧VC2がVs〔V〕からVn(=0)〔V〕に減少し、その後はVn〔V〕を維持する。また、コンデンサC2の両端電位VC2の減少に伴う電界効果トランジスタQ1のゲート電圧の電圧値の減少に応じて、ソース・ドレイン間抵抗RQ1の抵抗値が、Rs〔Ω〕からRn〔Ω〕に増加し、その後はRn〔Ω〕を維持する。

【0043】

本形態の素子破壊防止回路10(過渡電流抑制回路11)であれば、LED2の装着による接続状態への移行後の過渡期の初期において、過渡電流の主電流路として、直列に接続された抵抗R1及びコンデンサC2を介する電流路が形成されること、及び、その後の過渡電流の主電流路となっていく電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値が序々に減少していくことによって、急激な過渡電流の変化を抑制でき、LED2の定格最大電流値、実質的に接続状態の定常期の電流値Is〔A〕を越える瞬時電流が流れることを防止できる。これによって、定電流電源1が電力供給状態である場合にLED2を着脱したとしてもLED2が破損や劣化することを防止できる。また、LED2の装着による接続状態への移行後の定常期において、定常電流の主電流路として、オン状態である電界効果トランジスタQ1のソース・ドレイン間を介する電流路が形成されることによって、通常のLED2の駆動における素子破壊防止回路10自体による負荷の増大を抑制できる。これによって、消費電力の増大や発熱等も抑制できる。過渡電流の主経路の形成や定常電流の主電流路の形成が、素子破壊防止回路10自体の回路状態に基づいて、具体的には、電界効果トランジスタQ1とLED2との素子間の電圧に応じた電界効果トランジスタQ1の制御に基づいて自動的に行われるために、LED2の交換等においてその着脱作業以外の人為的な作業を行う必要がなくなる。更に、過渡電流の急激な変化を抑制するためのコンデンサC2を電界効果トランジスタQ1のゲート電圧の制御に援用することによって、素子破壊防止回路10の回路構成を簡素化できる。

【0044】

上記においては、過渡電流抑制回路11が電界効果トランジスタQ1、抵抗R1、抵抗R2及びコンデンサC1で構成される場合について説明したが、接続状態の定常期における定常電流の主電流路がオン状態の電界効果トランジスタQ1を介する電流路となり、接続状態の過渡期の少なくとも初期において、過渡電流の主電流路が電界効果トランジスタQ1以外の経路であって少なくとも抵抗素子を介する電流路となる構成であってもよい。また、上記においては、コンデンサC2を過渡電流の急峻な変化を防止するための回路を構成する一部の素子と、電界効果トランジスタQ1のゲート電圧を制御するための回路との一部を構成する素子として兼用して回路構成の簡素化を図ったが各回路で個別にコンデンサを含む構成であってもよい。

【0045】

〔実施形態2〕

実施形態2に係る素子破壊防止回路は、実施形態1に係る素子破壊防止回路10よりも接続状態の定常期における素子破壊防止回路自身による負荷を低減できる構成である。図3は、実施形態2に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路20は、無抵抗化回路22を含むこと以外は、上記の実施形態1における素子破壊防止回路10(図1参照)と同一の構成である。以下においては、実施形態1と同一の構成部分については同一の参照符号を付すこととし、その詳細な説明は省略する。

【0046】

素子破壊防止回路20は、定常接続状態における電界効果トランジスタQ1のゲート電圧の電圧値を更に増加させてソース・ドレイン間抵抗の抵抗値を低下させて、実質的に無抵抗化する無抵抗化回路22(〔低インピーダンス化促進回路〕の一種:「電圧依存型のスイッチング制御回路」の一部の一種)を更に含んでいる。本形態においては、電界効果トランジスタQ1のオン状態への移行制御は、抵抗R1及びコンデンサC2からなる回路部と無抵抗化回路22との双方の援用によって行われる。

【0047】

無抵抗化回路22は、定電流電源1の出力端と接地電位端とを接続するように直列に配置されたツェナーダイオードZD1、抵抗R3及び抵抗R4を含む回路部と、出力端と接地電位端とを接続するように直列に配置された抵抗R5、抵抗R6及びトランジスタQ2、抵抗R5と抵抗6との素子間と接地電位端とを接続するツェナーダイオードZD2、抵抗6とトランジスタQ2との素子間と電界効果トランジスタQ1のゲート端とを接続するダイオードD1を含む回路部とで構成されている。トランジスタQ2のエミッタ端は抵抗R2と接続され、ベース端は抵抗R3と抵抗R4との素子間と接続されている。ツェナーダイオードZD1、抵抗R3及び抵抗R4を含む回路部は、主に、出力電圧V0の変化に応じてトランジスタQ2のオン状態とオフ状態との間の状態移行を制御する。他の回路部は、主に、トランジスタQ2のオフ状態への移行に応じて、電界効果トランジスタQ1のからオン状態への状態移行を制御する回路部を構成する。

【0048】

図3に示された非接続状態の定常状態において、電解コンデンサC1の両端電圧は定電流電源1の出力電圧V0の電圧値と同一であり、コンデンサC2の端子間電圧VC2の電圧値はVn〔V〕(Vn=0)であり、電界効果トランジスタQ1がオフ状態であってそのソース・ドレイン間抵抗RQ1の抵抗値はRn〔Ω(オーム)〕である。また、ツェナーダイオードZD1はブレークスルー電圧を維持しており、トランジスタQ2は出力電圧V0からツェナーダイオードZD1のブレークスルー電圧を減じた電圧を抵抗R3及び抵抗R4で抵抗分割した抵抗R3と抵抗R4との素子間の電圧値によってオン状態を維持している。

【0049】

一方、定電流電源1がオン状態であり、かつLED2の装着によって接続状態(SW1のオン状態)に移行してから所定の時間の経過後である接続状態の定常期において、電解コンデンサC1の両端電圧は定電流電源1の出力電圧値と同一のV0〔V〕であり、コンデンサC2の両端電圧VC2の電圧値はVs〔V〕であり、電界効果トランジスタQ1がオン状態であってそのソース・ドレイン間抵抗の実効的な抵抗値はRs’〔Ω(オーム)〕である。また、ツェナーダイオードZD1を介しての電流や、トランジスタQ2を介しての電流や、ダイオードD1を介しての電流は実質的に遮断されている。なお、このような非接続状態や接続状態の定常期の動作が実現されるように各種の回路素子は選択されている。

【0050】

ここで、図4は、素子破壊防止回路20の動作の一例を定性的に表すタイミングチャートであり、図4(A)がLEDに流れる電流の時間推移を表し、図4(B)がコンデンサC2の端子間電圧の時間推移を表し、図4(C)が電界効果トランジスタのソース・ドレイン間抵抗の時間推移を表している。

【0051】

LED2の装着が開始されて非接続状態から接続状態へ移行すると(時刻t0)、過渡電流ILEDの供給が開始されるが、上記の実施形態1の場合と同様の動作原理によってLED2に流れる過渡電流ILEDの急激な増加が抑制されることになる。接続状態への移行からの時間の経過に伴って、図4(B)に示されたように、過渡電流ILEDによってコンデンサC2が充電されることとなり、コンデンサC2の両端電圧VC2がVn〔V〕からVs〔V〕まで徐々に増加する(時刻ts)。また、この充電に応じて電界効果トランジスタQ1のゲート電圧(コンデンサC2の両端電圧VC2と同じ)の電圧値が増加することによって、図4(C)に示されたように、ソース・ドレイン間抵抗RQ1の抵抗値がRn〔Ω〕からRs〔Ω〕まで減少する(時刻ts)。ここまでの過渡現象は、上記の実施形態1の場合と定性的に同一である。

【0052】

ソース・ドレイン間抵抗RQ1の抵抗値の減少に伴って、定電流電源1の外部の合成抵抗が低下するために、出力電圧V0の電圧値が減少する。なお、このとき、電界効果トランジスタQ1のソース・ドレイン間の電圧は、電界効果トランジスタQ1がオン状態を保持できるソース・ゲート間の電圧と同一なるまで減少する。この出力電圧V0の電圧値の減少に伴って、その電圧値がツェナーダイオードZD1のブレークスルー電圧値よりも小さくなり、出力端からツェナーダイオードZD1への電流が遮断される(時刻ts)。この遮断によって、抵抗R3と抵抗R4との素子間の電圧が実質的に接地電位となり、トランジスタQ2がオフ状態へ移行する。この移行によって、図4(B)に示されたように、抵抗R5、抵抗R6及びダイオードD1を介して供給される電流によってコンデンサC2が更に充電されて、コンデンサC2の両端電圧VC2がVs’〔V〕まで更に増加する(時刻ts’)。その後、コンデンサC2の電圧VC2はVs’〔V〕に維持される。また、この充電によって、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値はRs’〔Ω〕(Rs≒0)まで減少する(時刻ts’)。その後、ソース・ドレイン間の抵抗RQ1はRs’〔Ω〕に維持される。なお、過渡電流ILEDの電流値の変化は、上記の実施形態1の場合と定性的に同一である。

【0053】

本形態に係る素子破壊防止回路20であれば、上記の実施形態1の素子破壊防止回路10の場合に比べて、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値を更に低下させることができるために、通常のLED2の駆動における素子破壊防止回路20に起因する負荷の増大を更に良好に抑制できる。また、電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値を実質的に0〔Ω〕にできるために、素子破壊防止回路20を設けない従来の構成(図12(B)参照)と比べて、素子破壊防止回路20に起因する負荷の増加を極めて良好に抑制できることとなる。

【0054】

上記においては、図3に示された無抵抗化回路22によって接続状態の定常期における電界効果トランジスタQ1のゲート電圧を無抵抗化回路22を設けない場合よりも高い電圧値に制御する場合について説明したが、ゲート電圧の電圧値を高い電圧値に制御できる構成であればいかなる構成であってもよい。

【0055】

〔実施形態3〕

実施形態3に係る素子破壊防止回路40は、LED(機能素子)の装着や抜脱の際において接続状態から非接続状態への移行やその逆の移行が微少時間間隔で複数回発生したとしても、その装着や抜脱の際に機能素子が破壊や劣化することを防止できる構成である。図5は、実施形態3に係る素子破壊防止回路の一例を表す回路図である。図5に示された本形態の素子破壊防止回路40は、高抵抗化促進回路43(〔高インピーダンス化促進回路〕の一種:「電圧依存型のスイッチング制御回路」の一部の一種)を含むこと以外は、上記の実施形態2における素子破壊防止回路20(図3参照)と同一の構成である。以下においては、実施形態2と同一の構成部分については同一の参照符号を付すこととし、その詳細な説明は省略する。

【0056】

高抵抗化促進回路43は、主に、過渡電流抑制回路11におけるコンデンサC2を強制的に放電させるための回路である。本形態においては、電界効果トランジスタQ1のオフ状態への移行制御は、抵抗R2からなる回路部と高抵抗化促進回路43との双方の援用によって行われる。具体的には、高抵抗化促進回路43は、LED2と接続される過渡電流抑制回路11の回路端の電圧に基づいて、過渡電流抑制回路11における抵抗R2によってコンデンサC2を放電させるよりも高速にその放電を行わせる回路である。

【0057】

LED2と接続される過渡電流抑制回路11の回路端と定電流電源1の接地電位端とを接続するように直列に配置された抵抗R10及び抵抗R8からなる回路部と、無抵抗化回路22の抵抗R5と抵抗R6との素子間と接地電位端とを接続するように直列に配置され、抵抗R8と抵抗R10との素子間の電圧に応じて制御されるトランジスタQ3及び抵抗R7からなる回路部と、抵抗R7とトランジスタQ3との素子間と接地電位端とを接続するように直列に配置されたコンデンサC3及び抵抗R9からなる回路部と、無抵抗化回路22のダイオードD1のカソード端(抵抗R1と抵抗R2との素子間)と接地電位端とを接続し、コンデンサC3と抵抗R9との素子間の電圧に応じて制御されるトランジスタQ4からなる回路部とで構成されている。トランジスタQ3のコレクタ端は抵抗R7に接続され、エミッタ端は定電流電源1の接地電位端に接続され、ベース端は抵抗R10と抵抗R8との素子間に接続されている。トランジスタQ4のコレクタ端はダイオードD1と過渡電流抑制回路11におけるコンデンサC2との素子間に接続されている。

【0058】

図5に示された非接続状態の定常期において、トランジスタQ3はオフ状態であり、また、トランジスタQ3がオフ状態であるためにトランジスタQ4もオフ状態である。その他の回路状態は、実施形態2の場合と同様である。一方、接続状態の定常期において、トランジスタQ3はオン状態であり、また、トランジスタQ4もオフ状態である。また、非接続状態における定電流電源1の出力電圧V0の電圧値は、接続状態の場合よりも大きい。

【0059】

接続状態から非接続状態に移行すると、抵抗R1や抵抗R10を介しての電流が遮断される。抵抗R1を介しての電流の遮断によってコンデンサC2が抵抗R2を介して放電を開始する。なお、抵抗R2を介しては緩やかに放電が進行する。一方、抵抗R10を介しての電流の遮断によって、トランジスタQ3のベース電圧が実質的に接地電位となり、トランジスタQ3がオフ状態に移行する。トランジスタQ3がオフ状態へ移行することにより、トランジスタQ4がオン状態へ移行し、トランジスタQ4(コレクタ端及びエミッタ端の間)を介してコンデンサC2の放電が開始される。なお、トランジスタQ4のコレクタ・エミッタ間抵抗RQ1は、抵抗R2よりも遥かに小さいために、コンデンサC2の放電を高速に行える。但し、コンデンサC3が存在するために、トランジスタQ4のオン状態は一時的であり、一旦オン状態へ移行した後に再度オフ状態へ自動的に移行する。更に詳しくは、コンデンサC3で直流成分を遮断しているのでLED2の有無による出力電圧V0の変化分が抵抗R5及び抵抗R7を通してコンデンサC3からトランジスタQ4のベース端に流れ、トランジスタQ4をオン状態に移行させる。出力電圧V0の変化がなくなると、抵抗R5、抵抗R7及びコンデンサC3からの電流がなくなるのでトランジスタQ4はオフ状態へ移行する。これによって、接続状態から非接続状態に状態移行した瞬間の出力電圧V0の変化の間だけトランジスタQ4がオン状態となり、非接続状態であっても出力電圧V0が安定した場合や、接続状態においてはオフ状態を維持している。

【0060】

逆に、非接続状態から接続状態に移行すると、出力電圧V0が低下すると共に、抵抗R1及び抵抗R10を介して過渡電流の供給が開始される。抵抗R10を流れる過渡電流の分流が増加するとトランジスタQ3のベース電圧が上昇し、過渡電流の分流の電流値が所定の電流値を超えると、トランジスタQ3がオン状態へ移行する。トランジスタQ3のオン状態への移行に応じてコンデンサC3が実質的に完全に放電し、この放電に伴ってトランジスタQ4のベース電圧が実質的に接地電位となる。これによって、トランジスタQ4が確実にオフ状態へと移行することとなる。これによって、上記の実施形態2と同様に接続状態への移行後の動作が実行される。

【0061】

ここで、LED2の装着の際に一旦接続状態に移行した後に、接続状態から非接続状態へ移行し、その後の短時間の間に再度接続状態に移行する場合について説明する。高抵抗化促進回路43を設けていないときには、接続状態への移行によって電界効果トランジスタQ1がオン状態へ移行し、その後、非接続状態へ移行したもののコンデンサC2の放電が電界効果トランジスタQ1をオフ状態に移行させるために十分な時間が確保されていない場合には、再度接続状態へ移行した際に電界効果トランジスタQ1がオン状態でLED2が接続されることとなり、その接続状態への移行の際に過渡電流の急峻な増加を十分に抑制できないことも考えられる。しかし、本形態であれば、非接続状態へ移行した場合に高速でコンデンサC2の放電が行え、つまり、電界効果トランジスタQ1の完全なオフ状態への移行を高速で行えるために、上記のような状況下であってもLED2の破壊や劣化を抑制できる。

【0062】

本形態に係る素子破壊防止回路40であれば、上記の実施形態2の素子破壊防止回路20の場合に比べて、LEDの着脱時におけるチャタリングや着脱の繰り返しによるLED2の破壊や劣化を抑制できる。

【0063】

上記においては、コンデンサC2の放電を過渡電流抑制回路11と高抵抗化促進回路43とを併用して行う場合について説明したが、高抵抗化促進回路43のみにおいてコンデンサC2の放電を制御する構成とすることもできる。この場合、過渡電流抑制回路11における抵抗R2はなくてもよい。また、図6に示された素子破壊防止回路50のように、抵抗R2を設けず、電界効果トランジスタQ1の制御を高精度で行うために、第1回路端と抵抗R1との間にダイオードD2を設けたり、第1回路端と電界効果トランジスタQ1のドレイン端との間に補正抵抗R11を設けたりしてもよい。

【0064】

上記においては、高抵抗化促進回路43によって接続状態から非接続状態への移行の際にコンデンサC2の放電を高速化する場合について説明したが、本発明に係る高抵抗化促進回路は、スイッチング素子(電界効果トランジスタQ1)のオン状態からオフ状態への移行を高速化できる構成であればいかなる構成であってもよい。

【0065】

〔実施形態4〕

実施形態4に係る素子破壊防止回路は、上記の実施形態1〜3の場合と同様に電圧に基づいてスイッチング素子(電界効果トランジスタQ1)を制御する構成である。図7は、実施形態4に係る素子破壊防止回路の一例を表す回路図である。

【0066】

図7に示された素子破壊防止回路60では、接続状態へ移行すると、まず、過渡電流が抵抗R12を介して流れる。なお、抵抗R12を介して流れる電流は微少値であり、これによって、過渡電流の急激な変化を抑制している。また、LED2のカソード端における電圧の変化に応じて、トランジスタQ4がオン状態へ移行する。トランジスタQ4がオン状態へ移行すると、抵抗R14とトランジスタQ4のコレクタ端との間の電圧が低下して、トランジスタQ5のベース電圧が実質的に接地電位となり、トランジスタQ5がオフ状態へ移行する。これによって、抵抗R15、抵抗R16及びコンデンサC4で構成される回路における抵抗R15と抵抗R16との素子間電圧がなだらかに増加する。これに応じて、電界効果トランジスタQ1のゲート電圧が増加し、所定の値を超えると、電界効果トランジスタQ1がオン状態に移行する。その後、接続状態の定常期となる。

【0067】

逆に、非接続状態へ移行すると、抵抗R13及び抵抗R12を流れる電流が遮断され、トランジスタQ4のベース電圧が実質的に接地電位となる。これによって、トランジスタQ4がオフ状態に移行する。また、トランジスタQ4のオフ移行に応じてトランジスタQ5がオン状態に移行し、その後、非接続状態の定常期となる。

【0068】

上記の構成であっても、実質的に上記の実施形態1〜3と同様の効果を奏することとなる。

【0069】

〔実施形態5〕

実施形態5に係る素子破壊防止回路は、上記の実施形態1〜4の場合と異なり、電流に基づいてスイッチング素子を制御する構成である。図8は、実施形態5に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路70は、図8に示されたように、電界効果トランジスタQ1(〔スイッチング素子〕)と、電界効果トランジスタQ1以外の素子で構成された、電界効果トランジスタQ1のゲート電圧を制御するゲート制御回路(〔電流依存型のゲート制御回路〕の一種)とで構成されている。なお、素子破壊防止回路70において、過渡電流抑制回路71は、上述の過渡電流抑制回路11(図1参照)と同様に、主に、過渡電流を抑制すると共に、電界効果トランジスタQ1のオン状態への移行及びオフ状態への状態移行の基本制御を行う回路である。また、高抵抗化促進回路73(〔高インピーダンス化促進回路〕の一種)は、上述の高抵抗化促進回路43(図5参照)と同様に、電界効果トランジスタQ1のオフ状態への状態移行を高速化する回路である。

【0070】

図8に示された非接続状態の定常状態において、トランジスタQ7はオフ状態であり、出力電圧V0の抵抗R21及び抵抗R19により分圧された電圧がトランジスタQ6のベース端に印加されることによってトランジスタQ6はオン状態であり、トランジスタQ6がオン状態であることによってトランジスタQ1がオフ状態である。

【0071】

非接続状態から接続状態へ移行する(t0)と、図9(D)に示されたように、トランジスタQ1がオフ状態であるために、R18及びR20に過渡電流が流れ始める。抵抗R18や抵抗R20を介して過渡電流が流れ出すために過渡電流の急峻な増加を低減できる。過渡電流の増加に伴い抵抗R18における降下電圧が増加し、これに伴ってトランジスタQ7のベース電圧が増加する。ベース電圧が増加して所定の電圧値以上となると、トランジスタQ7がオン状態に移行する。トランジスタQ7のオン状態への移行に伴って、図9(A)に示されたようにトランジスタQ6のベース電圧(抵抗R19の電圧VR19と同じ)の電圧値が実質的にV1〔V〕から接地電位(V0〔V〕)となり、トランジスタQ6がオフ状態に移行する。トランジスタQ6のオフ状態への移行によって、抵抗R1を介してコンデンサC2の充電が開始されて、図9(C)に示されたように、コンデンサC2の両端電圧VC2が増加する。なお、トランジスタQ6がオン状態である場合には、抵抗R1を流れる電流は実質的にトランジスタQ6のみを介して流れる。図9(D)に示されたように、電界効果トランジスタQ1のゲート電圧(コンデンサC2の両端電圧VC2と同じ)が増加して、そのゲート電圧が所定の電圧以上となると電界効果トランジスタQ1がオン状態に移行し、電界効果トランジスタQ1のオン状態への移行後は、そのゲート電圧の増加に伴って電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値がRs’〔Ω〕まで減少する。

【0072】

本形態の素子破壊防止回路70であれば、LED2の装着による接続状態への移行後の過渡期の初期において、過渡電流の主電流路として、抵抗R18及び抵抗20を介する電流路が形成されること、及び、その後の、過渡電流の主電流路となっていく電界効果トランジスタQ1のソース・ドレイン間抵抗RQ1の抵抗値が徐々減少していくことによって、急峻な過渡電流の変化を抑制でき、LED2の定格最大電流値、実質的に接続状態の定常期の電流値Is〔A〕を越える瞬時電流が流れることを防止できる。これによって、定電流電源1が電力供給状態である場合にLED2を着脱したとしてもLED2が破損や劣化することを防止できる。また、LED2の装着による接続状態への移行後の定常期において、定常電流の主電流路として、オン状態である電界効果トランジスタQ1のソース・ドレイン間を介する電流路が形成されることによって、通常のLED2の駆動における素子破壊防止回路70による負荷の増大を抑制できる。これによって、消費電力の増大や発熱等も抑制できる。過渡電流の主経路の形成や定常電流の主電流路の形成が、素子破壊防止回路70の回路状態に基づいて、具体的には、LED2からの出力電流に応じた電界効果トランジスタQ1の制御に基づいて自動的に行われるために、LED2の交換等においてその着脱作業以外の人為的な作業を行う必要がなくなる。

【0073】

上記においては、過渡電流抑制回路が電界効果トランジスタQ1、抵抗R1、抵抗R2及びコンデンサC2で構成される場合について説明したが、接続状態の定常期における定常電流の主電流路がオン状態の電界効果トランジスタQ1を介する電流路となり、接続状態の過渡期の少なくとも初期において、過渡電流の主電流路が電界効果トランジスタQ1以外の経路であって少なくとも抵抗素子を介する電流路となる構成であってもよい。また、上記においては、コンデンサC2を過渡電流の急峻な変化を防止するための回路を構成する一部の素子と、電界効果トランジスタQ1のゲート電圧を制御するための回路との一部を構成する素子として兼用して回路構成の簡素化を図ったが各回路で個別にコンデンサを含む構成であってもよい。

【0074】

〔実施形態6〕

実施形態6に係る素子破壊防止回路は、機構的な接続状態の変化を援用して過渡電流を抑制する構成である。図10は、実施形態6に係る素子破壊防止回路の一例を表す回路図である。本形態の素子破壊防止回路80は、過渡電流抑制回路81のみで構成されている。過渡電流抑制回路81は、図10に示されたように、電界効果トランジスタQ1(〔スイッチング素子〕)と、電界効果トランジスタQ1以外の素子で構成され、電界効果トランジスタQ1のゲート電圧を制御するゲート制御回路(〔電圧依存型のゲート制御回路〕の一種)とで構成されている。なお、素子破壊防止回路80において、過渡電流抑制回路81は、上述の過渡電流抑制回路11(図1参照)と同様に、主に、過渡電流を抑制すると共に、電界効果トランジスタQ1のオン状態への移行及びオフ状態への状態移行の制御を行う回路である。なお、過渡電流抑制回路11(図1参照)の電界効果トランジスタQ1のゲート電圧を実質的に制御することとなるコンデンサC2への電流供給路を構成する抵抗R1を別接点P4とした構成である。

【0075】

LED2の装着が開始されると、まず、接点P2と接点P4が接触する(t0)。その後、接点P1と接点P3が接触して(t0’)、LED2の装着が完了する。接点P2と接点P4とが接触すると、抵抗R1及びコンデンサC2を介して過渡電流が流れ、図11(B)に示されたように、コンデンサC2への充電が開始される。抵抗R1及びコンデンサC2を介して過渡電流が流れ出すために過渡電流の急峻な増加を低減できる。その後に、接点P1と接点P3との接触によって非接続状態から接続状態へ状態移行する。なお、この状態移行においては、既に、過渡電流の流れる閉回路が形成されているために瞬時電流の影響はほとんどない。その後の動作は、図11(A)〜(C)に示されたように、上記の実施形態1における過渡現象と定性的に同一である。なお、素子破壊防止回路80の抵抗R1の一端(電界効果トランジスタQ1のゲート端に接続されている側と反対側)がLED2のアノード端に接続されているため、抵抗R1の一端がLEDのカソード端に接続されている素子破壊防止回路10(図1参照)に比べて、電界効果トランジスタQ1のゲート電圧を高くすることができ、それによりソース・ドレイン間抵抗RQ1を低くすることができる。

【0076】

上記においては、接点P2と接点P4とが接触した後に、接点P1と接点P3とが接触する場合について説明したが、接点P1と接点P3とを先に接触させて、その後、接点P2と接点P4とを接触させる構成であってもよい。この場合においても、上記の場合と定性的に同一の制御が行え、実質的に同一の効果を奏する。また、接点P2と接点P4との接触を、接点P1と接点P3との接触と実質的に同時に行ってもよい。この場合においても、上記の場合と定性的に同一の制御が行え、実質的に同一の効果を奏する。

【0077】

上記の実施形態1〜6においては、機能素子が、LEDである場合について説明したが、他の発光素子であってもよい。更に、機能素子は、発光素子に限らず各種の発光以外の他の機能を発現する電気素子であってもよい。

【0078】

また、上記の実施形態1〜6においては、素子破壊防止回路が機能素子の2次側(LEDのカソード側)に配置されている場合について説明したが、機能素子の1次側(LEDのアノード側)に配置される構成であっても構わない。

【0079】

上記においては、素子破壊防止回路について説明したが、本発明においては、素子破壊防止回路を内蔵する各種の電気機器であってもよい。具体的には、例えば、素子破壊防止回路を含み、一般的な定電流電源と一般的な電気機器との間に接続して電気機器に含まれる機能素子を着脱自在にさせるアダプタや、素子破壊防止回路と定電流電源とを一体化した電源装置や、素子破壊防止回路と機能素子とを一体化した電気機器や、素子破壊防止回路と定電流電源及び機能素子とを一体化させた電気機器が挙げられる。なお、機能素子が大電流で駆動される大電流型機能素子である場合に本発明の効果が大きくなる。したがって、電気機器としては、大電流型LEDを備えたLED照明、LEDライト、LED看板、LED表示灯であることが好ましい。

【産業上の利用可能性】

【0080】

本発明は、定電流電源と機能素子を備えた電気機器とを接続するアダプタ、定電流電源装置、発光素子等の機能素子を備えた電気機器、例えば、広域や狭域を照らす照明機器(照明、ライト)、文字や図形や模様や画像や映像を表示する表示機器(看板、表示灯、画像表示装置)等の発光装置に利用できる。

【図面の簡単な説明】

【0081】

【図1】実施形態1に係る素子破壊防止回路の一例を表す回路図。

【図2】実施形態1に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図3】実施形態2に係る素子破壊防止回路の一例を表す回路図。

【図4】実施形態2に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図5】実施形態3に係る素子破壊防止回路の一例を表す回路図。

【図6】実施形態3に係る素子破壊防止回路の変形例を表す回路図。

【図7】実施形態4に係る素子破壊防止回路の一例を表す回路図。

【図8】実施形態5に係る素子破壊防止回路の一例を表す回路図。

【図9】実施形態5に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図10】実施形態6に係る素子破壊防止回路の一例を表す回路図。

【図11】実施形態6に係る素子破壊防止回路の動作の一例を定性的に表すタイミングチャート。

【図12】(A)が定電圧電源を用いた従来の典型的なLED装置の電気的な構成を表し、(B)が定電流電源を用いた従来の典型的なLED装置の電気的な構成を表す回路図。

【符号の説明】

【0082】

1: 定電流電源

2: LED(機能素子)

10,20,40,50,60,70,80: 素子破壊防止回路

11,31,71,81: 過渡電流抑制回路

22: 無抵抗化回路(低インピーダンス化促進回路)

43,73: 高抵抗化促進回路(高インピーダンス化促進回路)

Q1: 電界効果トランジスタ(スイッチング素子)

【特許請求の範囲】

【請求項1】

出力端と基準電位端との間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記機能素子を介して前記定電流電源の前記出力端に接続される第1回路端及び前記定電流電源の前記基準電位端に接続される第2回路端を含む素子破壊防止回路を備え、

前記素子破壊防止回路が、

前記機能素子の抜脱により前記第1回路端と前記定電流電源の前記出力端とが電気的に接続されていない状態を非接続状態とし、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴とする電気回路。

【請求項2】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記制御端の電圧を制御する電圧依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項3】

前記素子破壊防止回路が、

前記機能素子に接続された電流流入端と、前記定電流電源の前記基準電位端に接続された電流流出端と、前記電流流入端と前記電流流出端との間の抵抗値を制御する制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端へ流入する電流の変化に基づいて、前記制御端の電圧を制御する電流依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項4】

前記素子破壊防止回路が、前記接続状態への状態移行に応じて前記第1回路端と前記第2回路端との間のインピーダンスを前記接続時インピーダンスより低いインピーダンスにまで変化させる低インピーダンス化促進回路を更に含む請求項2に記載の電気回路。

【請求項5】

前記素子破壊防止回路が、前記非接続状態への状態移行に伴う前記第1回路端と前記第2回路端との間のインピーダンスの変化を高速化する高インピーダンス化促進回路を更に含む請求項2〜4のいずれか一項に記載の電気回路。

【請求項6】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記機能素子の装着過程において前記定電流電源の前記出力端に接続される付加回路端を更に含み、

前記非接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項7】

出力端と基準電位端との間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記定電流電源と前記機能素子との間に設けられた素子破壊防止回路を備え、

前記機能素子が装着されていない状態を非接続状態とし、前記機能素子が装着されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記素子破壊防止回路の第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴とする電気回路。

【請求項1】

出力端と基準電位端との間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記機能素子を介して前記定電流電源の前記出力端に接続される第1回路端及び前記定電流電源の前記基準電位端に接続される第2回路端を含む素子破壊防止回路を備え、

前記素子破壊防止回路が、

前記機能素子の抜脱により前記第1回路端と前記定電流電源の前記出力端とが電気的に接続されていない状態を非接続状態とし、前記機能素子の装着により前記第1回路端と前記出力端とが電気的に接続されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴とする電気回路。

【請求項2】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記制御端の電圧を制御する電圧依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記スイッチング素子の前記電流流入端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項3】

前記素子破壊防止回路が、

前記機能素子に接続された電流流入端と、前記定電流電源の前記基準電位端に接続された電流流出端と、前記電流流入端と前記電流流出端との間の抵抗値を制御する制御端とを備えるスイッチング素子と、

前記スイッチング素子の前記電流流入端へ流入する電流の変化に基づいて、前記制御端の電圧を制御する電流依存型のスイッチング制御回路と、

を含み、

前記スイッチング制御回路が、

前記非接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記第1回路端に流入する電流の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項4】

前記素子破壊防止回路が、前記接続状態への状態移行に応じて前記第1回路端と前記第2回路端との間のインピーダンスを前記接続時インピーダンスより低いインピーダンスにまで変化させる低インピーダンス化促進回路を更に含む請求項2に記載の電気回路。

【請求項5】

前記素子破壊防止回路が、前記非接続状態への状態移行に伴う前記第1回路端と前記第2回路端との間のインピーダンスの変化を高速化する高インピーダンス化促進回路を更に含む請求項2〜4のいずれか一項に記載の電気回路。

【請求項6】

前記素子破壊防止回路が、

前記機能素子に接続される電流流入端と、前記定電流電源の前記基準電位端と接続される電流流出端と、前記電流流入端と前記電流流出端との間の抵抗を変化させる制御端とを備えるスイッチング素子と、

前記機能素子の装着過程において前記定電流電源の前記出力端に接続される付加回路端を更に含み、

前記非接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記接続状態における所定の接続時抵抗値から前記接続時抵抗値より大きい所定の非接続時抵抗値に変化させ、

前記接続状態への状態移行に応じた前記付加回路端の電圧の変化に基づいて、前記電流流入端と前記電流流出端との間の抵抗を前記非接続時抵抗値から前記接続時抵抗値に変化させる請求項1に記載の電気回路。

【請求項7】

出力端と基準電位端との間に静電容量を含む定電流電源と、前記定電流電源からの電力に基づいて所定の機能を発現する着脱自在な機能素子とを電気的に接続する電気回路であって、

前記定電流電源と前記機能素子との間に設けられた素子破壊防止回路を備え、

前記機能素子が装着されていない状態を非接続状態とし、前記機能素子が装着されている状態を接続状態として、

前記接続状態から前記非接続状態への状態移行に応じて、前記素子破壊防止回路の第1回路端と第2回路端との間のインピーダンスを自己整合的に非接続時インピーダンスにまで増加させ、

前記非接続状態から前記接続状態への状態移行に応じて、前記第1回路端と前記第2回路端との間のインピーダンスを自己整合的に前記非接続インピーダンスより低い接続時インピーダンスにまで減少させることを特徴とする電気回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図12】

【公開番号】特開2009−182266(P2009−182266A)

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願番号】特願2008−21978(P2008−21978)

【出願日】平成20年1月31日(2008.1.31)

【出願人】(000000309)IDEC株式会社 (188)

【Fターム(参考)】

【公開日】平成21年8月13日(2009.8.13)

【国際特許分類】

【出願日】平成20年1月31日(2008.1.31)

【出願人】(000000309)IDEC株式会社 (188)

【Fターム(参考)】

[ Back to top ]