電気短パルス発生装置およびそれを用いた光パルス発生装置

【課題】ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供する。

【解決手段】バイアス電圧Vbが重畳された正弦波信号Sを発生させる発振手段と、正弦波信号Sの周波数を分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号Pを生成する分周手段と、パルス信号Pを所定の遅延量だけ遅延させる遅延手段と、遅延されたパルス信号Pに応じて、正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Piを生成するゲート手段と、入力パルス信号Piのパルス幅を圧縮した出力パルス信号Poを出力する非線形伝送線路と、を備える。

【解決手段】バイアス電圧Vbが重畳された正弦波信号Sを発生させる発振手段と、正弦波信号Sの周波数を分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号Pを生成する分周手段と、パルス信号Pを所定の遅延量だけ遅延させる遅延手段と、遅延されたパルス信号Pに応じて、正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Piを生成するゲート手段と、入力パルス信号Piのパルス幅を圧縮した出力パルス信号Poを出力する非線形伝送線路と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、電気短パルス発生装置およびそれを用いた光パルス発生装置に係り、特に、非線形伝送線路を備えた電気短パルス発生装置およびそれを用いた光パルス発生装置に関する。

【背景技術】

【0002】

従来より、電気短パルス発生装置として、ステップリカバリダイオード(SRD:Step Recovery Diode)を用いたものが知られている。SRDには、例えば正弦波が印加されるようになっている。SRDは、印加された正弦波が逆バイアス状態のときに電荷を蓄積し、順バイアス状態になった瞬間に放電して、正弦波の周波数と同じ繰返し周波数の電気短パルスを発生させるように動作する。

【0003】

しかしながら、単にパルス幅が狭いだけではなく、ジッタの少ない電気短パルスが求められる計測機器においては、上記の電気短パルス発生装置が出力する電気短パルスはその要求に十分に応えられるものではなかった。

【0004】

そこで、非線形伝送線路(NLTL:Non-Linear Transmission Line)を備えたコムジェネレータが提案された(例えば、特許文献1参照)。NLTLは、コプレーナ線路等の伝送線路に、半導体微細加工技術により複数個の非線形素子を所定の間隔で装加した構造を有している。NLTLは、伝送線路に並列に配置される非線形素子の容量変化を利用することにより、入力された正弦波の立ち上がり時間を徐々に短縮して、急峻な立ち上がり特性を有するとともに、ジッタの少ないパルス信号を出力することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7612629号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、例えば200MHzよりも低い周波数の正弦波をNLTLに入力すると、[発明を実施するための形態]でシミュレーション結果を示すように、その出力信号のパルス幅は入力の正弦波と同程度になり、入力された正弦波がほぼそのままの波形で出力される。このため、特許文献1に開示されたようなコムジェネレータは、特に10〜50MHzのような低い繰返し周波数の電気短パルスを発生させることができず、この周波数域を計測範囲に含む計測機器に適用することができないという課題を有していた。

【0007】

本発明は、このような従来の課題を解決するためになされたものであって、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の請求項1の電気短パルス発生装置は、バイアス電圧が重畳された正弦波信号を発生させる発振手段と、前記正弦波信号の周波数を分周して、該正弦波信号の1周期分の時間幅に等しいパルス幅を有する第1のパルス信号を生成する分周手段と、前記第1のパルス信号を所定の遅延量だけ遅延させる遅延手段と、前記遅延手段により遅延された第1のパルス信号に応じて、前記発振手段から発生された前記正弦波信号を透過あるいは遮断することにより、第2のパルス信号を生成するゲート手段と、前記第2のパルス信号が入力され、入力された該第2のパルス信号のパルス幅を圧縮した第3のパルス信号を出力する非線形伝送線路と、を備える構成を有している。

【0009】

この構成により、局所的に正弦波信号の周波数を維持したまま、繰返し周波数を低減したパルス信号をNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることができる。

【0010】

また、本発明の請求項2の電気短パルス発生装置は、前記遅延手段が、前記遅延された第1のパルス信号の立ち上がりのタイミングと、前記正弦波信号のピーク点とを同期させる前記遅延量を設定する構成を有している。

この構成により、再現性の高い電気短パルスを発生させることができる。

【0011】

また、本発明の請求項3の光パルス発生装置は、前記電気短パルス発生装置と、前記電気短パルス発生装置から出力された前記第3のパルス信号により駆動されて光パルスを発生させるレーザ光源と、を備える構成を有している。

【0012】

この構成により、電気短パルス発生装置から出力された狭いパルス幅の出力パルス信号でレーザ光源を駆動することにより、さらに狭いパルス幅の光パルスを出力することができる。

【発明の効果】

【0013】

本発明は、局所的に正弦波信号の周波数を維持したまま、繰返し周波数を低減したパルス信号をNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供するものである。

【図面の簡単な説明】

【0014】

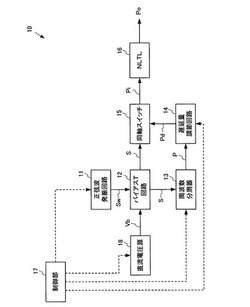

【図1】第1の実施形態に係る電気短パルス発生装置の構成を示すブロック図

【図2】正弦波信号、パルス信号、遅延パルス信号、入力パルス信号のタイミングチャート

【図3】NLTLの概略構成を示す模式図およびNLTLの等価回路図

【図4】入力パルス信号の電圧波形を示すグラフ

【図5】入力パルス信号および出力パルス信号の電圧波形を示すグラフ

【図6】出力パルス信号の電圧波形の時間軸を拡大したグラフ

【図7】遅延量が異なる3種類の遅延パルス信号により生成された入力パルス信号の電圧波形を示すグラフ

【図8】正弦波信号、遅延パルス信号のタイミングチャート

【図9】3種類の遅延パルス信号および入力パルス信号に対応した出力パルス信号の電圧波形を示すグラフ

【図10】比較例のシミュレーション結果を示すグラフ

【図11】第2の実施形態に係る光パルス発生装置の構成を示すブロック図

【発明を実施するための形態】

【0015】

以下、本発明に係る電気短パルス発生装置およびそれを用いた光パルス発生装置の実施形態について図面を用いて説明する。なお、本明細書においてパルス幅とは、パルス波形の半値全幅(FWHM:Full Width at Half Maximum)を指すものとする。

【0016】

(第1の実施形態)

図1は本実施形態に係る電気短パルス発生装置10の構成を示すブロック図である。図1に示すように、本実施形態に係る電気短パルス発生装置10は、正弦波Swを発生させる正弦波発振回路11と、正弦波発振回路11から出力された正弦波Swにバイアス電圧Vbを重畳して出力するバイアスT回路12と、バイアスT回路12から出力された正弦波信号S(以下、バイアス電圧Vbが重畳された正弦波Swを正弦波信号と記す)の周波数fを分周比Rで分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号P(第1のパルス信号)を生成する周波数分周器13と、を備える。

【0017】

また、電気短パルス発生装置10は、周波数分周器13から出力されたパルス信号Pを遅延量(遅延時間)Δtだけ遅延させる遅延量調節回路14と、遅延量調節回路14により遅延量Δtだけ遅延されたパルス信号(以下、遅延パルス信号Pdと記す)に応じて、バイアスT回路12から出力された正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Pi(第2のパルス信号)を生成する同軸スイッチ15と、入力パルス信号Piが入力され、入力された入力パルス信号Piのパルス幅を圧縮した出力パルス信号Po(第3のパルス信号)を出力する非線形伝送線路(NLTL)16と、を備える。

【0018】

さらに、電気短パルス発生装置10は、正弦波発振回路11と、遅延量調節回路14との同期を取るための制御信号を出力する制御部17と、バイアスT回路12にバイアス電圧Vbを供給する直流電圧源18と、を備える。

【0019】

制御部17は、正弦波Swおよび正弦波信号Sの周期T、振幅および位相を制御する制御信号を正弦波発振回路11へ、正弦波信号Sのバイアス電圧Vbを制御する制御信号を直流電圧源18へ、分周比Rを制御する制御信号を周波数分周器13へ、遅延量Δtを制御する制御信号を遅延量調節回路14へそれぞれ出力するようになっている。

【0020】

なお、図1に示した電気短パルス発生装置10の構成においては、正弦波発振回路11、バイアスT回路12、直流電圧源18および制御部17は発振手段を構成し、周波数分周器13および制御部17は分周手段を構成し、遅延量調節回路14および制御部17は遅延手段を構成し、同軸スイッチ15はゲート手段を構成している。

【0021】

周波数分周器13は、周期的なパルス信号が入力された場合、その周波数の1/Nの周波数のパルス信号を出力するものであり、PLD(Programmable Logic Device)等で構成されるものである。

【0022】

同軸スイッチ15は、例えば、複数の入力ポートを有するRFオン/オフスイッチからなり、遅延量調節回路14から出力された遅延パルス信号Pdによりスイッチングされる。即ち、同軸スイッチ15は、その入力ポートに入力される遅延パルス信号Pdがオフとなるタイミングでは、入力された正弦波信号Sを遮断して零ボルト(0V)の電圧をNLTL16側に出力し、一方、遅延パルス信号Pdがオンとなるタイミングでは、入力された正弦波信号Sをその周期Tの時間幅で透過させてNLTL16側に出力するようになっている。

【0023】

なお、同軸スイッチ15は、遅延パルス信号Pd用の入力ポート以外の入力ポートに直流電圧を入力させる構成であってもよい。この場合は、例えば、バイアスT回路12を省略し、正弦波発振回路11からの正弦波Swを周波数分周器13に直接出力させるとともに、直流電圧源18から直接バイアス電圧Vbを同軸スイッチ15に入力させる構成が可能である。

【0024】

また、ゲート手段として、同軸スイッチ15の代わりにアッテネータを用いてもよい。この場合、アッテネータは、遅延パルス信号Pdがオフとなるタイミングで正弦波信号Sを吸収し、遅延パルス信号Pdがオンとなるタイミングで正弦波信号Sを透過させるように機能する。

【0025】

図2は、正弦波信号S、パルス信号P、遅延パルス信号Pd、入力パルス信号Piのタイミングチャートである。バイアスT回路12から出力された正弦波信号Sは、不図示の分波器で分波されて周波数分周器13および同軸スイッチ15に入力される。周波数分周器13は、入力された正弦波信号Sの周期をカウントし、例えば10周期ごとに1つのパルスを有するパルス信号Pを出力する。なお、パルス信号Pおよび遅延パルス信号Pdの各パルスは矩形状であるものとする。

【0026】

パルス信号Pは遅延量調節回路14に入力される。遅延量調節回路14は、制御部17からの制御信号に従い、パルス信号Pを遅延量Δtだけ遅延させて、正弦波信号Sと同期を取った遅延パルス信号Pdを出力する。

【0027】

遅延パルス信号Pdは同軸スイッチ15に入力される。同軸スイッチ15は、遅延パルス信号Pdがオンとなるタイミングで、バイアスT回路12から出力された正弦波信号Sをその周期Tの時間幅で切り取ることにより、入力パルス信号Piを生成する。即ち、入力パルス信号Piは、局所的に正弦波信号Sの周波数fを維持したまま、繰返し周波数fRが低減されたパルス信号であると言える。

【0028】

図3(a)は、NLTL16の概略構成を示す模式図である。NLTL16は、伝送線路16aと、伝送線路16aに並列接続される1組の逆バイアスダイオード16bと、からなる単位回路を直列に接続してなるものである。また、図3(b)はNLTL16の等価回路図である。

【0029】

伝送線路16aとしては、例えば、ストリップ線路、マイクロストリップ線路、コプレーナ線路等が用いられる。逆バイアスダイオード16bとしては、例えば、ショットキーダイオードが用いられる。また、逆バイアスダイオード16bの代わりに、共鳴トンネルダイオードを用いてもよい。

【0030】

本発明者は、図3(b)に示した等価回路をモデルとしてNLTL16のシミュレーションを行った。ここで、図3(b)に示した等価回路は、逆バイアスダイオード16bへの印加電圧Vn(n=1,2,・・・,N)に依存するN個の容量Cn(Vn)、インダクタンスLn、信号入力側のインダクタンスLD、信号出力側の負荷抵抗RLからなる。各インダクタンスLnには電流Inが流れるものとする。NLTL16の非線形性は[数1]に示す容量Cn(Vn)の電圧依存性を介して導入される。ここで、C0,nは零電圧(Vn=0)時の逆バイアスダイオード16bの容量、V0は逆バイアスダイオード16bの障壁電圧である。

【数1】

【0031】

各単位回路におけるインダクタンスLn、容量Cn(Vn)、電流Inおよび印加電圧Vnの関係は[数2]、[数3]で表わされる。

【数2】

【数3】

【0032】

図3に示したNLTL16に、電圧VD(t)の入力パルス信号Piを入力した場合に、負荷抵抗RLから出力される出力パルス信号Poの電圧VL(t)=RLIN(t)は、[数2]、[数3]から導かれる[数4]をRunge-Kutta法により数値積分することにより算出できる。

【数4】

【0033】

上述のように構成されたNLTL16において、単位回路ごとの遮断周波数Fnを信号入力側から等比数列的に増加させることで効率の良いパルス圧縮を実現できることが従来から知られている。ここで、遮断周波数Fnは容量Cn(Vn)とインダクタンスLnで[数5]のように決定される。

【数5】

【0034】

遮断周波数Fnを等比数列的に増加させる一手段として、伝送線路16aの線路導体の幅を狭めて容量C0,nを減少させ、容量C0,nの装加間隔を短縮してインダクタンスLnを減少させる方法がある。[表1]にシミュレーション条件をまとめる。

【表1】

【0035】

[表1]に示す条件下で、[数6]に示す電圧VD(t)の入力パルス信号PiをNLTL16に入力する。既に述べたように、fは正弦波信号Sの周波数、Rは周波数fの分周比である。また、周期T=1/fである。

【数6】

【0036】

例えば、周波数fが500MHz(T=2ns)で、分周比Rが10の場合には、[数6]で示される電圧VD(t)は、図4のグラフ中の実線で示すようなものとなる。即ち、入力パルス信号Piは、500MHzの周波数fを1/10の50MHzに低減した繰返し周波数fRを有し、バイアス電圧Vbが−3V、振幅が3Vの信号である。

【0037】

図5に入力パルス信号Piの電圧VD(t)および出力パルス信号Poの電圧VL(t)の波形をそれぞれ破線と実線で示す。また、図6に出力パルス信号Poの電圧VL(t)の波形の時間軸の拡大図を示す。出力パルス信号Poのパルス幅(FWHM)は67psとなり、入力電圧VD(t)の約7%(67/1000)まで圧縮されていることが分かる。

【0038】

本シミュレーション結果は、分周比R(=10)で周波数f(=500MHz)を低減した繰返し周波数fR(=50MHz)の入力パルス信号Piにより、[表1]に示す諸元を有するNLTL16において高効率のパルス圧縮を実現可能であることを示している。

【0039】

以下、正弦波信号Sと遅延パルス信号Pdとの同期の取り方について考察する。図7は、遅延量Δtが異なる3種類の遅延パルス信号Pdにより生成された入力パルス信号Piの波形を示すグラフである。図8は正弦波信号Sと遅延パルス信号Pdのタイミングチャートであり、図8(a)は図7の破線a、図8(b)は図7の点線b、図8(c)は図7の実線cの入力パルス信号Piに対応している。

【0040】

また、図9は上記の3種類の遅延パルス信号Pdおよび入力パルス信号Piに対応した出力パルス信号Poの波形を示すグラフである。[表2]に正弦波信号Sの波形を表わす式、出力パルス信号Poのパルス幅(ps)および波高(V)をまとめる。

【表2】

【0041】

実線cの出力パルス信号Poのパルス幅は、破線aの出力パルス信号Poのパルス幅の約2/3程度となる。また、入力パルス信号Piの上昇時間tr(図7)が破線aの1/2である点線bの入力パルス信号Piに関しては、さらなるパルス幅の短縮と波高の増大が認められる。

【0042】

即ち、遅延量Δtを制御して正弦波信号Sと遅延パルス信号Pdとの同期の取り方を変化させることにより、出力パルス信号Poのパルス幅が可変となることが分かる。

【0043】

しかしながら、破線aおよび点線bの入力パルス信号Piを生成するように正弦波信号Sと遅延パルス信号Pdとの同期を取る場合には、両者が所望の同期点から僅かにでも外れると(両者に小さな非同期が生じると)出力パルス信号Poの波形の再現性が損なわれやすいという問題があることを本発明者は確認している。このことを考慮に入れると、安定性の高い出力パルス信号Poを得るためには、遅延パルス信号Pdの立ち上がりのタイミングと、正弦波信号Sのピーク点(図7の0Vの点)とを同期させた実線cの入力パルス信号Piを生成するように遅延量Δtを設定することが好ましい。

【0044】

ここで、本発明の比較例として、従来のコムジェネレータのように正弦波信号Sを直接NLTL16に入力させた場合のシミュレーション結果を示す。このシミュレーションでは、正弦波信号Sの周波数fが、NLTL16の信号入力側の遮断周波数F1(=1GHz)よりも低いとした。正弦波信号S(入力信号)とNLTL16からの出力信号のパルス幅の変化は[表3]に示すようになった。また、出力信号の波形は図10に示すようになった。

【表3】

【0045】

[表3]および図10に示すように、入力信号のパルス幅に対して、出力信号のパルス幅は、いずれの周波数fについても圧縮されず、出力信号がほぼ正弦波であることが分かる。また、周波数fが低いほど、出力信号のパルス幅が入力信号のパルス幅から増大(4〜9%)することが認められる。

【0046】

特に、[表2]に示した繰返し周波数fRが50MHzの出力パルス信号Poのパルス幅と比較して、[表3]に示した繰返し周波数fが50MHzの出力信号のパルス幅は、100倍程度も広いことが分かる。

【0047】

上記のシミュレーション結果から、正弦波をNLTLの入力信号とした場合には、50MHzのような低い周波数において100ps以下のパルス幅の出力パルス信号を生成することができないことが確認できる。

【0048】

さらに、上記のシミュレーション結果から推測すると、本実施形態に係る電気短パルス発生装置10においても、100ps以下の狭いパルス幅の出力パルス信号Poを得るためには、正弦波信号Sの周波数fについても200MHz以下とすることは好ましくないと考えられる。

【0049】

以上説明したように、本実施形態に係る電気短パルス発生装置は、本質的にジッタの少ない正弦波信号を局所的にその周波数を維持したまま、繰返し周波数を低減してNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることができる。

【0050】

(第2の実施形態)

第1の実施形態に係る電気短パルス発生装置を備えた光パルス発生装置の実施形態について図11を用いて説明する。図11は本実施形態に係る光パルス発生装置の構成を示すブロック図である。

【0051】

即ち、本実施形態に係る光パルス発生装置20は、出力パルス信号Poを出力する電気短パルス発生装置10と、電気短パルス発生装置10から出力された出力パルス信号Po(電圧信号)をパルス電流信号Ipに変換する電圧電流変換器21と、電圧電流変換器21から出力されたパルス電流信号Ipにバイアス電流Ibを重畳して出力するバイアスT回路22と、バイアスT回路22から出力された入力パルス電流信号Ii(以下、バイアス電流Ibが重畳されたパルス電流信号Ipを入力パルス電流信号と記す)により駆動されて光パルスLpを発生させるレーザ光源23と、バイアスT回路22にバイアス電流Ibを供給する直流電流源24と、を備える。

【0052】

レーザ光源23は、例えば、単一の縦モードで発振する分布帰還型(DFB:Distributed-FeedBack)レーザであり、入力パルス電流信号Iiを用いた直接変調によって、入力パルス電流信号Iiよりも狭いパルス幅の光パルスLpを発生させるようになっている。

【0053】

光パルスLpの繰返し周波数は、入力パルス電流信号Iiの繰返し周波数を変化させることにより制御可能である。即ち、電気短パルス発生装置10における正弦波信号Sの周波数f、および、周波数fの分周比Rを変えることにより、光パルスLpの繰返し周波数を制御することができる。

【0054】

以上説明したように、本実施形態に係る光パルス発生装置は、電気短パルス発生装置10から出力された狭いパルス幅の出力パルス信号でレーザ光源を駆動することにより、さらに狭いパルス幅の光パルスを出力することができる。

【符号の説明】

【0055】

10 電気短パルス発生装置

11 正弦波発振回路

12、22 バイアスT回路

13 周波数分周器

14 遅延量調節回路

15 同軸スイッチ

16 NLTL(非線形伝送線路)

16a 伝送線路

16b 逆バイアスダイオード

17 制御部

18 直流電圧源

20 光パルス発生装置

21 電圧電流変換器

23 レーザ光源

24 直流電流源

【技術分野】

【0001】

本発明は、電気短パルス発生装置およびそれを用いた光パルス発生装置に係り、特に、非線形伝送線路を備えた電気短パルス発生装置およびそれを用いた光パルス発生装置に関する。

【背景技術】

【0002】

従来より、電気短パルス発生装置として、ステップリカバリダイオード(SRD:Step Recovery Diode)を用いたものが知られている。SRDには、例えば正弦波が印加されるようになっている。SRDは、印加された正弦波が逆バイアス状態のときに電荷を蓄積し、順バイアス状態になった瞬間に放電して、正弦波の周波数と同じ繰返し周波数の電気短パルスを発生させるように動作する。

【0003】

しかしながら、単にパルス幅が狭いだけではなく、ジッタの少ない電気短パルスが求められる計測機器においては、上記の電気短パルス発生装置が出力する電気短パルスはその要求に十分に応えられるものではなかった。

【0004】

そこで、非線形伝送線路(NLTL:Non-Linear Transmission Line)を備えたコムジェネレータが提案された(例えば、特許文献1参照)。NLTLは、コプレーナ線路等の伝送線路に、半導体微細加工技術により複数個の非線形素子を所定の間隔で装加した構造を有している。NLTLは、伝送線路に並列に配置される非線形素子の容量変化を利用することにより、入力された正弦波の立ち上がり時間を徐々に短縮して、急峻な立ち上がり特性を有するとともに、ジッタの少ないパルス信号を出力することができる。

【先行技術文献】

【特許文献】

【0005】

【特許文献1】米国特許第7612629号明細書

【発明の概要】

【発明が解決しようとする課題】

【0006】

しかしながら、例えば200MHzよりも低い周波数の正弦波をNLTLに入力すると、[発明を実施するための形態]でシミュレーション結果を示すように、その出力信号のパルス幅は入力の正弦波と同程度になり、入力された正弦波がほぼそのままの波形で出力される。このため、特許文献1に開示されたようなコムジェネレータは、特に10〜50MHzのような低い繰返し周波数の電気短パルスを発生させることができず、この周波数域を計測範囲に含む計測機器に適用することができないという課題を有していた。

【0007】

本発明は、このような従来の課題を解決するためになされたものであって、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供することを目的とする。

【課題を解決するための手段】

【0008】

上記課題を解決するために、本発明の請求項1の電気短パルス発生装置は、バイアス電圧が重畳された正弦波信号を発生させる発振手段と、前記正弦波信号の周波数を分周して、該正弦波信号の1周期分の時間幅に等しいパルス幅を有する第1のパルス信号を生成する分周手段と、前記第1のパルス信号を所定の遅延量だけ遅延させる遅延手段と、前記遅延手段により遅延された第1のパルス信号に応じて、前記発振手段から発生された前記正弦波信号を透過あるいは遮断することにより、第2のパルス信号を生成するゲート手段と、前記第2のパルス信号が入力され、入力された該第2のパルス信号のパルス幅を圧縮した第3のパルス信号を出力する非線形伝送線路と、を備える構成を有している。

【0009】

この構成により、局所的に正弦波信号の周波数を維持したまま、繰返し周波数を低減したパルス信号をNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることができる。

【0010】

また、本発明の請求項2の電気短パルス発生装置は、前記遅延手段が、前記遅延された第1のパルス信号の立ち上がりのタイミングと、前記正弦波信号のピーク点とを同期させる前記遅延量を設定する構成を有している。

この構成により、再現性の高い電気短パルスを発生させることができる。

【0011】

また、本発明の請求項3の光パルス発生装置は、前記電気短パルス発生装置と、前記電気短パルス発生装置から出力された前記第3のパルス信号により駆動されて光パルスを発生させるレーザ光源と、を備える構成を有している。

【0012】

この構成により、電気短パルス発生装置から出力された狭いパルス幅の出力パルス信号でレーザ光源を駆動することにより、さらに狭いパルス幅の光パルスを出力することができる。

【発明の効果】

【0013】

本発明は、局所的に正弦波信号の周波数を維持したまま、繰返し周波数を低減したパルス信号をNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることが可能な電気短パルス発生装置およびそれを用いた光パルス発生装置を提供するものである。

【図面の簡単な説明】

【0014】

【図1】第1の実施形態に係る電気短パルス発生装置の構成を示すブロック図

【図2】正弦波信号、パルス信号、遅延パルス信号、入力パルス信号のタイミングチャート

【図3】NLTLの概略構成を示す模式図およびNLTLの等価回路図

【図4】入力パルス信号の電圧波形を示すグラフ

【図5】入力パルス信号および出力パルス信号の電圧波形を示すグラフ

【図6】出力パルス信号の電圧波形の時間軸を拡大したグラフ

【図7】遅延量が異なる3種類の遅延パルス信号により生成された入力パルス信号の電圧波形を示すグラフ

【図8】正弦波信号、遅延パルス信号のタイミングチャート

【図9】3種類の遅延パルス信号および入力パルス信号に対応した出力パルス信号の電圧波形を示すグラフ

【図10】比較例のシミュレーション結果を示すグラフ

【図11】第2の実施形態に係る光パルス発生装置の構成を示すブロック図

【発明を実施するための形態】

【0015】

以下、本発明に係る電気短パルス発生装置およびそれを用いた光パルス発生装置の実施形態について図面を用いて説明する。なお、本明細書においてパルス幅とは、パルス波形の半値全幅(FWHM:Full Width at Half Maximum)を指すものとする。

【0016】

(第1の実施形態)

図1は本実施形態に係る電気短パルス発生装置10の構成を示すブロック図である。図1に示すように、本実施形態に係る電気短パルス発生装置10は、正弦波Swを発生させる正弦波発振回路11と、正弦波発振回路11から出力された正弦波Swにバイアス電圧Vbを重畳して出力するバイアスT回路12と、バイアスT回路12から出力された正弦波信号S(以下、バイアス電圧Vbが重畳された正弦波Swを正弦波信号と記す)の周波数fを分周比Rで分周して、正弦波信号Sの1周期Tの時間幅に等しいパルス幅を有するパルス信号P(第1のパルス信号)を生成する周波数分周器13と、を備える。

【0017】

また、電気短パルス発生装置10は、周波数分周器13から出力されたパルス信号Pを遅延量(遅延時間)Δtだけ遅延させる遅延量調節回路14と、遅延量調節回路14により遅延量Δtだけ遅延されたパルス信号(以下、遅延パルス信号Pdと記す)に応じて、バイアスT回路12から出力された正弦波信号Sを透過あるいは遮断することにより、入力パルス信号Pi(第2のパルス信号)を生成する同軸スイッチ15と、入力パルス信号Piが入力され、入力された入力パルス信号Piのパルス幅を圧縮した出力パルス信号Po(第3のパルス信号)を出力する非線形伝送線路(NLTL)16と、を備える。

【0018】

さらに、電気短パルス発生装置10は、正弦波発振回路11と、遅延量調節回路14との同期を取るための制御信号を出力する制御部17と、バイアスT回路12にバイアス電圧Vbを供給する直流電圧源18と、を備える。

【0019】

制御部17は、正弦波Swおよび正弦波信号Sの周期T、振幅および位相を制御する制御信号を正弦波発振回路11へ、正弦波信号Sのバイアス電圧Vbを制御する制御信号を直流電圧源18へ、分周比Rを制御する制御信号を周波数分周器13へ、遅延量Δtを制御する制御信号を遅延量調節回路14へそれぞれ出力するようになっている。

【0020】

なお、図1に示した電気短パルス発生装置10の構成においては、正弦波発振回路11、バイアスT回路12、直流電圧源18および制御部17は発振手段を構成し、周波数分周器13および制御部17は分周手段を構成し、遅延量調節回路14および制御部17は遅延手段を構成し、同軸スイッチ15はゲート手段を構成している。

【0021】

周波数分周器13は、周期的なパルス信号が入力された場合、その周波数の1/Nの周波数のパルス信号を出力するものであり、PLD(Programmable Logic Device)等で構成されるものである。

【0022】

同軸スイッチ15は、例えば、複数の入力ポートを有するRFオン/オフスイッチからなり、遅延量調節回路14から出力された遅延パルス信号Pdによりスイッチングされる。即ち、同軸スイッチ15は、その入力ポートに入力される遅延パルス信号Pdがオフとなるタイミングでは、入力された正弦波信号Sを遮断して零ボルト(0V)の電圧をNLTL16側に出力し、一方、遅延パルス信号Pdがオンとなるタイミングでは、入力された正弦波信号Sをその周期Tの時間幅で透過させてNLTL16側に出力するようになっている。

【0023】

なお、同軸スイッチ15は、遅延パルス信号Pd用の入力ポート以外の入力ポートに直流電圧を入力させる構成であってもよい。この場合は、例えば、バイアスT回路12を省略し、正弦波発振回路11からの正弦波Swを周波数分周器13に直接出力させるとともに、直流電圧源18から直接バイアス電圧Vbを同軸スイッチ15に入力させる構成が可能である。

【0024】

また、ゲート手段として、同軸スイッチ15の代わりにアッテネータを用いてもよい。この場合、アッテネータは、遅延パルス信号Pdがオフとなるタイミングで正弦波信号Sを吸収し、遅延パルス信号Pdがオンとなるタイミングで正弦波信号Sを透過させるように機能する。

【0025】

図2は、正弦波信号S、パルス信号P、遅延パルス信号Pd、入力パルス信号Piのタイミングチャートである。バイアスT回路12から出力された正弦波信号Sは、不図示の分波器で分波されて周波数分周器13および同軸スイッチ15に入力される。周波数分周器13は、入力された正弦波信号Sの周期をカウントし、例えば10周期ごとに1つのパルスを有するパルス信号Pを出力する。なお、パルス信号Pおよび遅延パルス信号Pdの各パルスは矩形状であるものとする。

【0026】

パルス信号Pは遅延量調節回路14に入力される。遅延量調節回路14は、制御部17からの制御信号に従い、パルス信号Pを遅延量Δtだけ遅延させて、正弦波信号Sと同期を取った遅延パルス信号Pdを出力する。

【0027】

遅延パルス信号Pdは同軸スイッチ15に入力される。同軸スイッチ15は、遅延パルス信号Pdがオンとなるタイミングで、バイアスT回路12から出力された正弦波信号Sをその周期Tの時間幅で切り取ることにより、入力パルス信号Piを生成する。即ち、入力パルス信号Piは、局所的に正弦波信号Sの周波数fを維持したまま、繰返し周波数fRが低減されたパルス信号であると言える。

【0028】

図3(a)は、NLTL16の概略構成を示す模式図である。NLTL16は、伝送線路16aと、伝送線路16aに並列接続される1組の逆バイアスダイオード16bと、からなる単位回路を直列に接続してなるものである。また、図3(b)はNLTL16の等価回路図である。

【0029】

伝送線路16aとしては、例えば、ストリップ線路、マイクロストリップ線路、コプレーナ線路等が用いられる。逆バイアスダイオード16bとしては、例えば、ショットキーダイオードが用いられる。また、逆バイアスダイオード16bの代わりに、共鳴トンネルダイオードを用いてもよい。

【0030】

本発明者は、図3(b)に示した等価回路をモデルとしてNLTL16のシミュレーションを行った。ここで、図3(b)に示した等価回路は、逆バイアスダイオード16bへの印加電圧Vn(n=1,2,・・・,N)に依存するN個の容量Cn(Vn)、インダクタンスLn、信号入力側のインダクタンスLD、信号出力側の負荷抵抗RLからなる。各インダクタンスLnには電流Inが流れるものとする。NLTL16の非線形性は[数1]に示す容量Cn(Vn)の電圧依存性を介して導入される。ここで、C0,nは零電圧(Vn=0)時の逆バイアスダイオード16bの容量、V0は逆バイアスダイオード16bの障壁電圧である。

【数1】

【0031】

各単位回路におけるインダクタンスLn、容量Cn(Vn)、電流Inおよび印加電圧Vnの関係は[数2]、[数3]で表わされる。

【数2】

【数3】

【0032】

図3に示したNLTL16に、電圧VD(t)の入力パルス信号Piを入力した場合に、負荷抵抗RLから出力される出力パルス信号Poの電圧VL(t)=RLIN(t)は、[数2]、[数3]から導かれる[数4]をRunge-Kutta法により数値積分することにより算出できる。

【数4】

【0033】

上述のように構成されたNLTL16において、単位回路ごとの遮断周波数Fnを信号入力側から等比数列的に増加させることで効率の良いパルス圧縮を実現できることが従来から知られている。ここで、遮断周波数Fnは容量Cn(Vn)とインダクタンスLnで[数5]のように決定される。

【数5】

【0034】

遮断周波数Fnを等比数列的に増加させる一手段として、伝送線路16aの線路導体の幅を狭めて容量C0,nを減少させ、容量C0,nの装加間隔を短縮してインダクタンスLnを減少させる方法がある。[表1]にシミュレーション条件をまとめる。

【表1】

【0035】

[表1]に示す条件下で、[数6]に示す電圧VD(t)の入力パルス信号PiをNLTL16に入力する。既に述べたように、fは正弦波信号Sの周波数、Rは周波数fの分周比である。また、周期T=1/fである。

【数6】

【0036】

例えば、周波数fが500MHz(T=2ns)で、分周比Rが10の場合には、[数6]で示される電圧VD(t)は、図4のグラフ中の実線で示すようなものとなる。即ち、入力パルス信号Piは、500MHzの周波数fを1/10の50MHzに低減した繰返し周波数fRを有し、バイアス電圧Vbが−3V、振幅が3Vの信号である。

【0037】

図5に入力パルス信号Piの電圧VD(t)および出力パルス信号Poの電圧VL(t)の波形をそれぞれ破線と実線で示す。また、図6に出力パルス信号Poの電圧VL(t)の波形の時間軸の拡大図を示す。出力パルス信号Poのパルス幅(FWHM)は67psとなり、入力電圧VD(t)の約7%(67/1000)まで圧縮されていることが分かる。

【0038】

本シミュレーション結果は、分周比R(=10)で周波数f(=500MHz)を低減した繰返し周波数fR(=50MHz)の入力パルス信号Piにより、[表1]に示す諸元を有するNLTL16において高効率のパルス圧縮を実現可能であることを示している。

【0039】

以下、正弦波信号Sと遅延パルス信号Pdとの同期の取り方について考察する。図7は、遅延量Δtが異なる3種類の遅延パルス信号Pdにより生成された入力パルス信号Piの波形を示すグラフである。図8は正弦波信号Sと遅延パルス信号Pdのタイミングチャートであり、図8(a)は図7の破線a、図8(b)は図7の点線b、図8(c)は図7の実線cの入力パルス信号Piに対応している。

【0040】

また、図9は上記の3種類の遅延パルス信号Pdおよび入力パルス信号Piに対応した出力パルス信号Poの波形を示すグラフである。[表2]に正弦波信号Sの波形を表わす式、出力パルス信号Poのパルス幅(ps)および波高(V)をまとめる。

【表2】

【0041】

実線cの出力パルス信号Poのパルス幅は、破線aの出力パルス信号Poのパルス幅の約2/3程度となる。また、入力パルス信号Piの上昇時間tr(図7)が破線aの1/2である点線bの入力パルス信号Piに関しては、さらなるパルス幅の短縮と波高の増大が認められる。

【0042】

即ち、遅延量Δtを制御して正弦波信号Sと遅延パルス信号Pdとの同期の取り方を変化させることにより、出力パルス信号Poのパルス幅が可変となることが分かる。

【0043】

しかしながら、破線aおよび点線bの入力パルス信号Piを生成するように正弦波信号Sと遅延パルス信号Pdとの同期を取る場合には、両者が所望の同期点から僅かにでも外れると(両者に小さな非同期が生じると)出力パルス信号Poの波形の再現性が損なわれやすいという問題があることを本発明者は確認している。このことを考慮に入れると、安定性の高い出力パルス信号Poを得るためには、遅延パルス信号Pdの立ち上がりのタイミングと、正弦波信号Sのピーク点(図7の0Vの点)とを同期させた実線cの入力パルス信号Piを生成するように遅延量Δtを設定することが好ましい。

【0044】

ここで、本発明の比較例として、従来のコムジェネレータのように正弦波信号Sを直接NLTL16に入力させた場合のシミュレーション結果を示す。このシミュレーションでは、正弦波信号Sの周波数fが、NLTL16の信号入力側の遮断周波数F1(=1GHz)よりも低いとした。正弦波信号S(入力信号)とNLTL16からの出力信号のパルス幅の変化は[表3]に示すようになった。また、出力信号の波形は図10に示すようになった。

【表3】

【0045】

[表3]および図10に示すように、入力信号のパルス幅に対して、出力信号のパルス幅は、いずれの周波数fについても圧縮されず、出力信号がほぼ正弦波であることが分かる。また、周波数fが低いほど、出力信号のパルス幅が入力信号のパルス幅から増大(4〜9%)することが認められる。

【0046】

特に、[表2]に示した繰返し周波数fRが50MHzの出力パルス信号Poのパルス幅と比較して、[表3]に示した繰返し周波数fが50MHzの出力信号のパルス幅は、100倍程度も広いことが分かる。

【0047】

上記のシミュレーション結果から、正弦波をNLTLの入力信号とした場合には、50MHzのような低い周波数において100ps以下のパルス幅の出力パルス信号を生成することができないことが確認できる。

【0048】

さらに、上記のシミュレーション結果から推測すると、本実施形態に係る電気短パルス発生装置10においても、100ps以下の狭いパルス幅の出力パルス信号Poを得るためには、正弦波信号Sの周波数fについても200MHz以下とすることは好ましくないと考えられる。

【0049】

以上説明したように、本実施形態に係る電気短パルス発生装置は、本質的にジッタの少ない正弦波信号を局所的にその周波数を維持したまま、繰返し周波数を低減してNLTLに入力させることにより、ジッタが少なく、従来よりも繰返し周波数が低い電気短パルスを発生させることができる。

【0050】

(第2の実施形態)

第1の実施形態に係る電気短パルス発生装置を備えた光パルス発生装置の実施形態について図11を用いて説明する。図11は本実施形態に係る光パルス発生装置の構成を示すブロック図である。

【0051】

即ち、本実施形態に係る光パルス発生装置20は、出力パルス信号Poを出力する電気短パルス発生装置10と、電気短パルス発生装置10から出力された出力パルス信号Po(電圧信号)をパルス電流信号Ipに変換する電圧電流変換器21と、電圧電流変換器21から出力されたパルス電流信号Ipにバイアス電流Ibを重畳して出力するバイアスT回路22と、バイアスT回路22から出力された入力パルス電流信号Ii(以下、バイアス電流Ibが重畳されたパルス電流信号Ipを入力パルス電流信号と記す)により駆動されて光パルスLpを発生させるレーザ光源23と、バイアスT回路22にバイアス電流Ibを供給する直流電流源24と、を備える。

【0052】

レーザ光源23は、例えば、単一の縦モードで発振する分布帰還型(DFB:Distributed-FeedBack)レーザであり、入力パルス電流信号Iiを用いた直接変調によって、入力パルス電流信号Iiよりも狭いパルス幅の光パルスLpを発生させるようになっている。

【0053】

光パルスLpの繰返し周波数は、入力パルス電流信号Iiの繰返し周波数を変化させることにより制御可能である。即ち、電気短パルス発生装置10における正弦波信号Sの周波数f、および、周波数fの分周比Rを変えることにより、光パルスLpの繰返し周波数を制御することができる。

【0054】

以上説明したように、本実施形態に係る光パルス発生装置は、電気短パルス発生装置10から出力された狭いパルス幅の出力パルス信号でレーザ光源を駆動することにより、さらに狭いパルス幅の光パルスを出力することができる。

【符号の説明】

【0055】

10 電気短パルス発生装置

11 正弦波発振回路

12、22 バイアスT回路

13 周波数分周器

14 遅延量調節回路

15 同軸スイッチ

16 NLTL(非線形伝送線路)

16a 伝送線路

16b 逆バイアスダイオード

17 制御部

18 直流電圧源

20 光パルス発生装置

21 電圧電流変換器

23 レーザ光源

24 直流電流源

【特許請求の範囲】

【請求項1】

バイアス電圧が重畳された正弦波信号を発生させる発振手段(11、12、17、18)と、

前記正弦波信号の周波数を分周して、該正弦波信号の1周期分の時間幅に等しいパルス幅を有する第1のパルス信号を生成する分周手段(13、17)と、

前記第1のパルス信号を所定の遅延量だけ遅延させる遅延手段(14、17)と、

前記遅延手段により遅延された第1のパルス信号に応じて、前記発振手段から発生された前記正弦波信号を透過あるいは遮断することにより、第2のパルス信号を生成するゲート手段(15)と、

前記第2のパルス信号が入力され、入力された該第2のパルス信号のパルス幅を圧縮した第3のパルス信号を出力する非線形伝送線路(16)と、を備える電気短パルス発生装置。

【請求項2】

前記遅延手段が、前記遅延された第1のパルス信号の立ち上がりのタイミングと、前記正弦波信号のピーク点とを同期させる前記遅延量を設定することを特徴とする請求項1に記載の電気短パルス発生装置。

【請求項3】

請求項1または請求項2に記載の電気短パルス発生装置(10)と、前記電気短パルス発生装置から出力された前記第3のパルス信号により駆動されて光パルスを発生させるレーザ光源(23)と、を備える光パルス発生装置。

【請求項1】

バイアス電圧が重畳された正弦波信号を発生させる発振手段(11、12、17、18)と、

前記正弦波信号の周波数を分周して、該正弦波信号の1周期分の時間幅に等しいパルス幅を有する第1のパルス信号を生成する分周手段(13、17)と、

前記第1のパルス信号を所定の遅延量だけ遅延させる遅延手段(14、17)と、

前記遅延手段により遅延された第1のパルス信号に応じて、前記発振手段から発生された前記正弦波信号を透過あるいは遮断することにより、第2のパルス信号を生成するゲート手段(15)と、

前記第2のパルス信号が入力され、入力された該第2のパルス信号のパルス幅を圧縮した第3のパルス信号を出力する非線形伝送線路(16)と、を備える電気短パルス発生装置。

【請求項2】

前記遅延手段が、前記遅延された第1のパルス信号の立ち上がりのタイミングと、前記正弦波信号のピーク点とを同期させる前記遅延量を設定することを特徴とする請求項1に記載の電気短パルス発生装置。

【請求項3】

請求項1または請求項2に記載の電気短パルス発生装置(10)と、前記電気短パルス発生装置から出力された前記第3のパルス信号により駆動されて光パルスを発生させるレーザ光源(23)と、を備える光パルス発生装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図9】

【図10】

【図11】

【公開番号】特開2012−151746(P2012−151746A)

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願番号】特願2011−9941(P2011−9941)

【出願日】平成23年1月20日(2011.1.20)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

【公開日】平成24年8月9日(2012.8.9)

【国際特許分類】

【出願日】平成23年1月20日(2011.1.20)

【出願人】(000000572)アンリツ株式会社 (838)

【Fターム(参考)】

[ Back to top ]