電源供給回路

【課題】低消費電流化が達成できる電源供給回路の提供。

【解決手段】対象機器の負荷に電力を供給する電源供給回路であり、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータと、メインボルテージレギュレータに接続され対象機器が動作しないとき対象機器の負荷にメインボルテージレギュレータの供給電力よりも少ない電力を供給する低消費ボルテージレギュレータと、負荷に供給される電流値を監視し、設定した電流値以下であるときメインボルテージレギュレータの動作を切り、前記電流値が設定した前記設定電流よりも低くなるとメインボルテージレギュレータを動作させる低消費ボルテージレギュレータ動作監視回路とを有する。

【解決手段】対象機器の負荷に電力を供給する電源供給回路であり、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータと、メインボルテージレギュレータに接続され対象機器が動作しないとき対象機器の負荷にメインボルテージレギュレータの供給電力よりも少ない電力を供給する低消費ボルテージレギュレータと、負荷に供給される電流値を監視し、設定した電流値以下であるときメインボルテージレギュレータの動作を切り、前記電流値が設定した前記設定電流よりも低くなるとメインボルテージレギュレータを動作させる低消費ボルテージレギュレータ動作監視回路とを有する。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は電源供給回路に係わり、特に負荷電流を検出して通常消費で負荷過渡特性と電源リップル除去特性が良好なメインボルテージレギュレータ(VR)と、スタンバイ用の低消費ボルテージレギュレータ(低消費VR)の同時動作か低消費VRのみかの切替を自動的に行う電源供給回路に関する。

【背景技術】

【0002】

各種電子機器において、回路の低消費電流化のため、通常消費のメインボルテージレギュレータと、スタンバイ用の低消費ボルテージレギュレータとを有する電源供給回路が知られている(例えば、特許文献1)。そして、メインボルテージレギュレータと低消費ボルテージレギュレータの切り替え(オン・オフ動作)は、電子機器に内蔵されるマイクロコントローラ(CPU)等のコンピュータによるイネーブル(EN)信号によって制御されている。

【0003】

また、ボルテージレギュレータ(VR)の切り替えの他の手段としては、負荷電流に応じた消費電流制御を行う電流可変型の電源供給回路も知られている(例えば、特許文献2)。

【0004】

【特許文献1】特開2001−69677号公報

【特許文献2】特開2000−66745号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

メインボルテージレギュレータと低消費ボルテージレギュレータを自動的に切り替える手段では、切替時点で予測されるボルテージレギュレータ(VR)出力電流変動に応じて予めEN制御する必要があり、実質スタンバイ状態が明確である機器でしか有効性が無い。何時負荷変動するか不明な場合、低消費ボルテージレギュレータを適用できない。

【0006】

従来の負荷電流に応じた消費電流制御ボルテージレギュレータ回路(電源供給回路)は、1つのボルテージレギュレータで軽負荷時に低消費化するものであるが、消費電流の変化に応じた特性変動が大きく、消費電流の最大から最小格差が大きい程良好な特性を満足させる設計定数を得ることが非常に困難であった。

【0007】

本発明の目的は、低消費電流化が達成できる電源供給回路を提供することにある。

本発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面からあきらかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記のとおりである。

(1)電源供給回路は、

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの前記出力端子と第1基準電圧(電源)端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧(グランド)端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧(例えば、3.0V)を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第2の端子から前記第1の設定電圧よりも高い第2の設定電圧(例えば、3.1V)を出力する低消費ボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の出力トランジスタを最大に駆動する電位であるかを検出する低消費ボルテージレギュレータ動作検出回路を有し、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第2の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続されるとともに、対象機器の負荷に接続される端子となり、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの反転入力端子には基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオペアンプの非反転入力端子が接続され、

前記メインボルテージレギュレータの消費電力(例えば、3.0Vでメインボルテージレギュレータは100μA消費)に比較して前記低消費ボルテージレギュレータの消費電力(例えば、3.1Vで低消費ボルテージレギュレータは5μAの消費)が小さく構成されていることを特徴とする。

【0009】

前記低消費ボルテージレギュレータの第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源によって前記メインボルテージレギュレータの前記第1の設定電圧と前記低消費ボルテージレギュレータの前記第2の設定電圧とが切り替わる構成である。前記低消費ボルテージレギュレータの前記第2の設定電圧(例えば3.1V)は前記メインボルテージレギュレータの前記第1の設定電圧(例えば3.0V)より高く(例えば0.1V)設定されており、前記低消費ボルテージレギュレータの電流源電流設定値未満では前記低消費ボルテージレギュレータの前記第2の設定電圧を出力するが、電流源電流設定値以上ではこの電圧を出力せず、電流源電流設定値以上の電流を出力する前記メインボルテージレギュレータの前記第1の設定電圧に切り替わる構成となっている。

【0010】

前記メインボルテージレギュレータの負荷過渡特性(例えば200μA〜100mA負荷変動時に電圧降下が50mV未満)と電源リップル除去率(例えば30mA負荷、1kHzで60db以上)は前記低消費ボルテージレギュレータより良好な特性であり、高負荷時(例えば200μA以上)に電圧変動が少なく負荷に対し安定に電力を供給することができる。前記メインボルテージレギュレータの前記低消費ボルテージレギュレータより良好な特性は、前記低消費ボルテージレギュレータより大きい消費電流で最適化した回路定数により主に応答速度の向上の結果実現する。負荷電流が小さい場合(例えば200μA未満)は前記高負荷時に比較して負荷変動量が小さいため(例えば200μA未満)特性が前記メインボルテージレギュレータより劣る(例えば負荷過渡特性200μA〜100mA負荷変動時に電圧降下が50mV以上、電源リップル除去率30mA負荷、1kHzで60db未満)を適用し、自己の消費電流を低減する(例えば200μA以上の負荷時の消費電流はメインボルテージレギュレータの消費電流100μA+低消費ボルテージレギュレータの消費電流5μA=105μA、200μA未満の負荷時の消費電流は低消費ボルテージレギュレータのみの消費電流5μA)。

【0011】

また、低消費ボルテージレギュレータ動作検出回路により低消費ボルテージレギュレータの前記第2の設定電圧(例えば3.1V)以下であるかを検出し、前記メインボルテージレギュレータのオン、オフ制御を行う構成である。

【0012】

前記切替電圧(3.1V)に到達した状態では、前記低消費ボルテージレギュレータの前記定電流源の動作によって、前記第2の出力トランジスタには、出力設定電圧以上の電圧が与えられる。前記オペアンプの動作によって出力設定電圧を維持するため前記出力トランジスタの制御端子には前記第2の出力トランジスタをオンする電圧が最大では無い電位(オペアンプが出力できる最低電圧が0Vの場合0Vより高い電位)で印加される。前記低消費ボルテージレギュレータ動作検出回路では、前記出力トランジスタの制御端子が最大にオンする電位では無いことを検出し前記メインボルテージレギュレータをオフし、

前記切替電圧(3.1V)よりも低くなった状態では、前記低消費ボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタを最大でオンする状態となり、前記低消費ボルテージレギュレータ動作検出回路は前記メインボルテージレギュレータをオンする。

【0013】

(2)電源供給回路は、

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの出力端子と第1基準電圧(電源)端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧(グランド)端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧(例えば、3.0V)を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第1の端子から前記第1の設定電圧よりも高い第2の設定電圧(例えば、3.1V)を出力するシャントボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第1のオペアンプの出力端子に接続され、前記第1のオペアンプの出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路と、

前記第1基準電圧端子と前記第2基準電圧端子との間に電流源及びトランジスタが直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの出力端子に接続され、前記第2のオペアンプの出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路と、

前記メインボルテージレギュレータ動作検出回路及び前記シャントボルテージレギュレータ動作検出回路の検出出力を入力し、前記第1のオン・オフ用トランジスタ及び前記第2のオン・オフ用トランジスタの制御端子に出力するORゲートとを有し、

前記シャントボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続され、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの非反転入力端子には基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオン・オフの反転入力端子が接続され、

前記メインボルテージレギュレータの消費電力(例えば、3.0Vで100mAの負荷電流時にメインボルテージレギュレータは100μA消費)に比較して前記シャントボルテージレギュレータの消費電力(例えば、3.1Vで4μAの負荷電流時にシャントボルテージレギュレータは5μAの消費)が小さく構成されていることを特徴とする。

【0014】

また、前記対象機器の負荷が減少し前記シャントボルテージレギュレータの前記電流源を流れる電流の電流値が電流源電流以下になると前記電流源が電圧を上昇させて前記第1の設定電圧よりも高い切替電圧(例えば、3.1V)にするように構成され、

前記切替電圧(3.1V)に到達した状態では、前記メインボルテージレギュレータの前記第1のオペアンプの出力電圧は前記第1の出力トランジスタをオンしない状態となり、前記シャントボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタをオンする状態となり、前記ORゲートは前記メインボルテージレギュレータをオフし、

前記切替電圧(3.1V)よりも低くなった状態では、前記シャントボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタをオフする状態となり、前記ORゲートは前記メインボルテージレギュレータをオンする。

【発明の効果】

【0015】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

前記(1)の手段によれば、(a)対象機器が動作する高負荷のときは、メインボルテージレギュレータが動作して対象機器に電力(第1の設定電圧3.0Vで100mA)を供給する。このとき第2の低消費ボルテージレギュレータは最大出力電流(例えば電流源電流200μA)を供給しているが、電流源の動作によって電圧降下が生じ第1の設定電圧になる。対象機器が動作しなくなると負荷が減少し、前記第2の低消費ボルテージレギュレータによって電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達し、尚且つ電流源の電流供給能力を上回った場合第2のオペアンプ出力は第2のトランジスタを最大限にオンする電位(例えば出力トランジスタがPMOSである場合、オペアンプの能力に応じた0Vに近い低い電位)から上昇(出力設定電圧から出力トランジスタの閾値の差分に近づく)に転ずる。この状態を低消費ボルテージレギュレータ動作検出回路によって検出し、メインボルテージレギュレータの電力供給を停止する。このとき電流源からメインボルテージレギュレータよりも低出力の電力(3.1Vで200μA未満)が負荷に供給される。また、電流値が切替電圧(3.1V)よりも低くなると、低消費ボルテージレギュレータ動作検出回路によってメインボルテージレギュレータはオンし、再び電力(第1の設定電圧3.0Vで100mA)を対象機器に供給するようになる。この結果、対象機器が低消費ボルテージレギュレータ供給電流(例えば3.1V、200μA)より大きな負荷時はメインボルテージレギュレータと低消費ボルテージレギュレータ両方の動作電流を消費する。(例えばメインボルテージレギュレータ消費電流が100μA、低消費ボルテージレギュレータ消費電流が5μA、合計105μA)対象機器が低消費ボルテージレギュレータ供給電流(例えば200μA)より小さな負荷時はメインボルテージレギュレータが動作を停止し、低消費ボルテージレギュレータの消費電流(例えば5μA)のみとなり消費電流の低減が図れる(負荷電流がメインボルテージレギュレータを停止させない場合に比べ100μAの消費低減効果を持つ)。

【0016】

(b)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、本発明の電源供給回路の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ及び低消費ボルテージレギュレータ)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、本発明では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0017】

(c)本発明の電源供給回路においては、低消費時の低消費ボルテージレギュレータの電圧(第2の設定電圧)をメインボルテージレギュレータの電圧(第1の設定電圧)よりも、若干高く(例えば0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0018】

(d)本発明の電源供給回路は、要素回路が比較的単純であるので製品の小型化が可能である。

(e)本発明の電源供給回路ではEN制御が不要となる利点がある。

【0019】

前記(2)の手段によれば、(a)対象機器が動作する高負荷のときは、メインボルテージレギュレータが動作して対象機器に電力(第1の設定電圧3.0Vで100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源を流れる電流の電流値が電流源設定電流以下になると電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達すると、ORゲートによってメインボルテージレギュレータをオフし電力供給を停止する。このとき電流源からメインボルテージレギュレータよりも低出力の電力(3.1Vで5μA未満)が負荷に供給される。また、電流値が切替電圧(3.1V)よりも低くなると、ORゲートによってメインボルテージレギュレータはオンし、再び電力(第1の設定電圧3.0Vで100mA)を対象機器に供給するようになる。この結果、対象機器が電流源電流(例えば5μA)より大きな負荷時はメインボルテージレギュレータとシャントボルテージレギュレータ両方の動作電流を消費する。(例えばメインシャントレギュレータ消費電流が100μA、シャントレギュレータ消費電流が5μA、合計105μA)対象機器が電流源設定電流(例えば5μA)より小さな負荷時はメインボルテージレギュレータが動作を停止し、シャントボルテージレギュレータの消費電流(例えば5μA)のみとなり消費電流の低減が図れる。負荷電流が電流源設定電流より小さい場合は、シャントボルテージレギュレータによって余剰電流がグランドに引き抜かれるので、その場合見かけ上消費電力と等価であり、負荷電流がゼロの場合電流源電流全てとシャントレギュレータ消費電流を加算した値が回路消費電流になる。(例えば負荷電流0の場合、電流源電流5μAとシャントボルテージレギュレータ消費5μAを加算し消費電流10μAである。メインボルテージレギュレータを停止させない場合に比べ95μAの消費低減効果を持つ。)消費電流低減を目的として本発明を適用する場合、電流源電流とシャントボルテージレギュレータ消費電流を加算した値が、メインボルテージレギュレータの消費電流を下回る必要がある。

【0020】

(b)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、本発明の電源供給回路の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ及びシャントボルテージレギュレータ)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、本発明では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0021】

(c)本発明の電源供給回路においては、低消費時のシャントボルテージレギュレータの電圧(第2の設定電圧)をメインボルテージレギュレータの電圧(第1の設定電圧)よりも、若干高く(例えば0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0022】

(d)本発明の電源供給回路は、要素回路が比較的単純であるので製品の小型化が可能である。

(e)本発明の電源供給回路ではEN制御が不要となる利点がある。

【発明を実施するための最良の形態】

【0023】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【実施例1】

【0024】

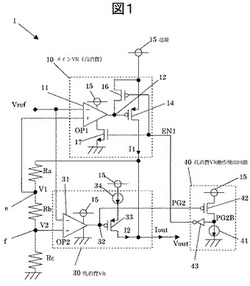

図1乃至図3は本発明の実施例1である電源供給回路に係わる図である。図1は電源供給回路を示す回路図、図2は電源供給回路の機能を示すブロック図、図3は電源供給回路の動作を示す動作表である。

【0025】

図1の回路図に示すように、電源供給回路1は、メインボルテージレギュレータ(メインVR)10、低消費ボルテージレギュレータ(低消費VR)30、低消費ボルテージレギュレータ動作検出回路40で構成されている。

【0026】

メインボルテージレギュレータ(メインVR)10は、第1のオペアンプ11と、第1のオペアンプ11の出力端子12に制御端子を介して接続される第1の出力トランジスタ14を有している。第1の出力トランジスタ14は、例えば、PMOSである。第1のオペアンプ11の出力端子12と電源15間には第1のオン・オフ用トランジスタ16が接続されている。第1のオン・オフ用トランジスタ16は、例えば、PMOSである。第1のオペアンプ11の負の電源端子とグランドとの間には第2のオン・オフ用トランジスタ17が接続されている。第2のオン・オフ用トランジスタ17は、例えば、NMOSである。メインVR10は第1の出力トランジスタ14の第2の端子(ドレイン電極)から第1の設定電圧を出力する。このときの電流量はI1である。

【0027】

低消費ボルテージレギュレータ(低消費VR)30は、第2のオペアンプ31と、第2のオペアンプ31の出力端子32に制御端子を介して接続される第2の出力トランジスタ33を有している。第2の出力トランジスタ33は、例えば、PMOSである。第2の出力トランジスタ33の第2の端子(ドレイン電極)はメインVR10の第1の出力トランジスタ14の第2の端子(ドレイン電極)に接続されている。また、電源15と低消費VR30の第2の出力トランジスタ33の第1の端子(ソース電極)間には電流源34が接続されている。電流源34の動作によって低消費ボルテージレギュレータの出力電流の最大値が設定される。低消費ボルテージレギュレータの電流量はI2である。

【0028】

第1のオペアンプ11の反転入力端子及び第2のオペアンプ31の反転入力端子には基準電位(Vref)が印加される。また、メインVR10の第1の出力トランジスタ14の第2の端子とグランドとの間には直列に3個の抵抗Ra,Rb,Rcが接続されている。そして、抵抗Raと抵抗Rbとの間のノードeと第1のオペアンプ11の非反転入力端子が接続されている。また、抵抗Rbと抵抗Rcとの間のノードfと第2のオペアンプ31の非反転入力端子が接続されている。

【0029】

参照電圧(Vref)を1.5V、電源15を5.0V、第1の設定電圧を3.0V、切替電圧を3.1Vに設定した場合、各電子部品の特性は適宜選択され、メインVR10が動作するときは、出力電圧Voutは3.0Vとなり、消費電流はメインVR100μAと低消費VR5μAを合計し105μAになるように構成されている。また、メインVRが動作しないときは、出力電圧Voutは3.1Vとなり、消費電流は低消費VR5μAとなる。

【0030】

一方、電流源34の動作によって、その設定電流と負荷電流の大小によって第2の出力トランジスタ33の第1の端子に印加される電位が変化する。第2のオペアンプによって出力電圧設定値を超えないよう制御されるため、この電位を監視(検出)することで結果的に定電流源の電流値と出力電流の大小が判定可能である。これを利用し、設定電流以上か未満かを検出する低消費ボルテージレギュレータ動作検出回路(低消費VR動作検出回路)40が設けられている。

【0031】

低消費VR動作検出回路40は電源15とグランドとの間に電流源41及びトランジスタ42が直列に接続されている。トランジスタ42の第2の接続端子が電流源41に接続されている。トランジスタ42は、例えば、PMOSトランジスタであり、制御端子が第2のオペアンプ31の出力端子32に接続され、第2のオペアンプ31の出力が第2の出力トランジスタ33を最大出力電流で駆動できる電圧以上か未満か(オペアンプの能力に応じた0Vに近い低い電位であるか、出力設定電圧から出力トランジスタの閾値の差分に近く上昇したか)をトランジスタ42の制御端子に入力される信号PG2に基づいて検出するようになっている。低消費VR動作検出回路40のトランジスタ42の第2の端子(ドレイン電極)から検出信号PG2Bが出力される。これをインバーター回路43で極性反転した信号がメインVR制御EN1信号である。

【0032】

この電源供給回路1においては、対象機器の負荷が減少し低消費VR30の出力電流I2の電流値がI1より大きい場合電圧を上昇させて第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)にするように構成されている。この結果、切替電圧(3.1V)に到達した状態では、第2の出力トランジスタ33から出力電圧Voutが3.1Vとなり、出力電流I2(低消費VRの電流供給能力200μA以下となる)が電力を対象機器の負荷に出力することになる。負荷電流が低消費VRの最大電流供給能力(200μA)より小さくなった場合は、第2のオペアンプ31の出力は上昇に転じる。この上昇結果を低消費VR動作検出回路で検出しEN1信号にてメインVRをオフする。

【0033】

また、負荷電流の増加によって低消費VRの電流供給能力を超えると第2のオペアンプ31の出力は第2の出力トランジスタ33を最大電流で駆動する電位に降下するため、低消費VR動作検出回路40によってメインVRをオンする。負荷電流が200μAより大きい場合、電流に比例して電圧降下が発生する。更に電流が増加し、メインVRの第1の設定電圧3.0Vに近づいた場合、第1の出力トランジスタ14から主に出力電流が供給され出力電圧Vout=3.0Vが保たれる。結果、メインVRの能力に応じた電力を対象機器の負荷に出力することになる。

【0034】

つぎに、実施例の電源供給回路1によって出力される電圧の関係式を示す。

メインVR側の出力電圧VoutはVVR1とする。オペアンプの動作によってVref=V1の関係が成り立つ。

メインVR側のV1は次式で与えられる。

【0035】

【数1】

また、メインVR側のVoutは次式で与えられる。

【0036】

【数2】

低消費VR側の出力電圧VoutはVVR2とする。オペアンプの動作によってVref=V2が成り立つ。

低消費VR側のV2は次式で与えられる。

【0037】

【数3】

また、低消費VR側のVoutは次式で与えられる。

【0038】

【数4】

とすると、[数2]にRa=Rb+Rcを代入し、

【0039】

【数5】

を得る。

[数4]にRa=Rb+Rcを代入し、

【0040】

【数6】

を代入し

【0041】

【数7】

を得る。

VoutをVVR1−VVR2とした場合[数5]及び[数6]から

【0042】

【数8】

となる。

よって、VVR2はVVR1より(1/15)・Vref高い。

【0043】

図3は既に説明した実施例1の電源供給回路1の出力電流Iout,出力電圧Vout及びイネーブル信号EN1の高負荷時と低負荷時の状態を示す動作表である。

【0044】

また、実施例1の電源供給回路は、図2に示すように、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータ(メインVR)10と、メインVR10に接続され対象機器が動作しないとき対象機器の負荷にメインVR10の供給電力よりも少ない電力を供給する。電流値を検出(監視)し、前記電流値が設定した設定電流(例えば、200μA)以下に減少したときメインVR10の動作を切り、前記電流値が設定した前記設定電流よりも大きくなるとメインVR10を動作させる低消費ボルテージレギュレータ(低消費VR)動作検出回路40とを有する構成になっている。

【0045】

図1において説明するならば、低消費VR動作検出回路40は、接続関係を有する各部、即ち、第1のオン・オフ用トランジスタ16、第2のオン・オフ用トランジスタ17、第1のオペアンプ11の出力端子12とを接続する配線、低消費VR動作検出回路40、低消費VR動作検出回路40と第2のオペアンプ31の出力端子32とを接続する配線によって構成される。

【0046】

図1の回路において用いるトランジスタは、各箇所でPMOS,NMOSのいずれでもよい。メインVRの第1の出力トランジスタ14と低消費VRの第2の出力トランジスタ33のPMOSとNMOSのタイプが図1と異なる場合、オペアンプの反転入力端子と非反転入力端子が逆転する。同様に低消費VR動作検出回路のトランジスタ42のPMOSとNMOSタイプが逆転する。しかし、メインVR10の第1の出力トランジスタ14をPMOSとし、低消費VR30の第2の出力トランジスタ33をPMOSとすることは、以下の点でメリットがある。即ち、PMOSとNMOSでは電源とグランドに対するゲート・ドレイン間電圧のかかり方が異なり、出力する電圧と電源電圧の電圧差が少なくて済む方がトランジスタサイズの低減につながり、また効率良く出力できる電圧範囲が広がる。

【0047】

また電流源34は、電源15の電圧が一定の場合、出力電圧Voutとの差分を電流設定値で割ることで求まる抵抗に置き換え可能である。この抵抗は、更に第2の出力トランジスタ33のオン抵抗(トランジスタサイズの調整や、閾値の調整)に置き換えることで電流源と等価の動作を実現可能である。

【0048】

一方、実施例1の電源供給回路は、以下の構成を有する。

【0049】

電源供給回路は、

前記メインボルテージレギュレータの出力できる電流より、前記低消費ボルテージレギュレータの出力できる電流が小さく構成され、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子と前記第1基準電圧端子間に接続された前記電流源により、前記第2の出力トランジスタの前記第2の端子からは、前記電流源設定電流値以上の電流を出力することがなく、前記電流源設定電流値を超えた負荷に対し前記第2の出力トランジスタの前記第2の端子の出力電圧が低消費ボルテージレギュレータの第2の設定電圧よりも降下するように構成され、

前記第2の出力トランジスタからの出力は、前記第2の出力トランジスタの前記第2の端子が前記第1の出力トランジスタの前記第2の端子に接続されることで、前記低消費ボルテージレギュレータの前記電流源設定電流値を超えた負荷電流を、前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子から供給されて出力し、

前記第2の出力トランジスタの出力電圧は、前記低消費ボルテージレギュレータの前記電流源設定電流値未満の負荷電流に対しては、前記低消費ボルテージレギュレータの第1の設定電圧になり、前記電流源設定電流値以上の負荷電流に対しては、前記メインボルテージレギュレータの第1の設定電圧から前記低消費ボルテージレギュレータの第2の設定電圧の間になるように構成されている。

【0050】

この構成によれば、出力電流量が同等で低消費電流である特許文献1等の従来回路に比較し、低消費VRの出力トランジスタサイズが小さくできるため半導体集積回路のレイアウト面積が低減できる。また、前記のように小さな出力トランジスタ(ゲート容量が小さい)で済むためこれを駆動するオペアンプの容量駆動能力が小さくてもスルーレートが確保でき、低消費で特性の良好な回路定数を容易に得られる効果がある。

【0051】

また、実施例1の電源供給回路は、以下の構成を有する。

【0052】

電源供給回路1は、

対象機器の負荷Ioutが減少し低消費ボルテージレギュレータ30の第2の出力トランジスタ33を流れる電流の電流値が電流源34の設定電流値以下になると低消費VR30の出力電圧Voutを上昇させてメインVR10の第1の設定電圧よりも高い切替電圧にするように構成され、

低消費VR30の第2のオペアンプ31の出力端子32の電圧は第2の出力トランジスタ33を負荷電流Ioutが電流源34の設定電流値未満になるとVoutを低消費VR30の第2の設定電圧に保つよう第2の出力トランジスタ33のゲート端子を制御するため、出力できる最低電圧ではない状態(例えば0V以上)となり、低消費VR動作検出回路40の出力信号EN1はメインVR10をオフし、負荷電流Ioutが低消費VR30の電流源34の設定電流値を上回る場合、出力電圧Voutは電流源34の動作で低消費VR30の第2の設定電圧よりも低くなり、低消費VRの第2のオペアンプ31の出力端子32は第2の出力トランジスタ33をオンするよう出力できる最低電圧を出力する状態(例えば0V)となり、低消費VR動作検出回路40はメインVR10をオンする構成になっている。

【0053】

この構成によれば、電流源の動作によって負荷電流に比例した電圧切り替えが連続的に行えるため、電圧切り替え時の電圧変動による負荷に接続される回路動作への影響が少ない。また回路が単純なため回路設計が容易である効果がある。

【0054】

また、実施例1の電源供給回路は、以下の構成を有する。

【0055】

電源供給回路1は、

メインVR10は前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給し、

低消費VR30は前記対象機器が動作しないとき前記対象機器の前記負荷にメインVR10の供給電力よりも少ない電力を供給し、

低消費VR動作検出回路40は、第2のオペアンプ31の出力端子32の電位を監視し、第2の出力トランジスタ33に対し最大電流を出力する電位ではない状態(例えば0V以上)のときメインVR10の動作を切り、負荷電流Ioutの増大によって第2の出力トランジスタ33が最大電流を出力する状態(例えば0V)のときメインVR10を動作させる構成になっている。

【0056】

この構成によれば、負荷の電力需要に応じ、少ない電力需要時は過大な電流能力を持ったボルテージレギュレータを切断するため、低消費電流なる効果がある。

【0057】

また、実施例1の電源供給回路は、以下の構成を有する。

【0058】

電源供給回路1は、

メインVR10は出力負荷過渡特性が200μA〜100mA負荷変動時に電圧降下が50mV未満となり、電源リップル除去特性が30mA負荷、1kHzで60db以上となるように構成され、

前記負荷の電流が電流源34の電流源設定電流以上のときは前記メインボルテージレギュレータを動作させ、

負荷電流Ioutが設定した電流源設定電流未満の場合は前記メインボルテージレギュレータを停止させる構成になっている。

【0059】

200μA〜100mA負荷変動時に電圧降下が50mV未満となる出力負荷過渡特性と、30mA負荷、1kHzで60db以上となる電源リップル除去特性は、第1のオペアンプ(OP1)11の消費電流に対して各回路定数を最適化することによって得られる。

【0060】

このような構成によれば、負荷電流が大きい場合は出力負荷過渡特性及び電源リップル除去特性が優れたメインボルテージレギュレータを動作させ、負荷電流が設定した電流値より小さい場合はメインボルテージレギュレータを停止させるため、回路消費電流の低減を図ることができる。

【0061】

また、実施例1の電源供給回路は、以下の構成を有する。

【0062】

電源供給回路1は、

前記メインボルテージレギュレータは負荷の電流Ioutが200μA以上のとき動作し、

前記メインボルテージレギュレータは負荷電流Ioutが200μA未満のとき停止する構成になっている。

【0063】

この構成によれば、外部EN制御が不要で、負荷状況に応じて自発的に低消費VRを選択しメインVRの消費電流を低減できる効果がある。

【0064】

また、実施例1の電源供給回路は、以下の構成を有する。

【0065】

電源供給回路1は、

負荷電流Ioutが低消費VR30の電流源34の電流源設定電流値以上の場合はメインVR10の第1の設定電圧を出力し、

負荷電流Ioutが電流源34の電流源設定電流値未満の場合はメインVRは停止し、低消費VR30の第2の設定電圧を出力し、

メインVR10の第1の設定電圧より、低消費VR30の第2の設定電圧が高くなっている。

【0066】

この構成によれば、メインVR10の第1の設定電圧より、低消費VR30の第2の設定電圧を高くすることで、急激な負荷増大時に負荷である回路動に支障が出る電圧に降下するまでの時間を伸ばすことができ、メインVR10が起動するまでの時間を得ることができるため出力電圧低下を減らすことができる。

【0067】

なお、実施例において、電流源34に代えて抵抗等(トランジスタサイズの調整や、閾値の調整)を用いても前記実施例同様の効果がある。抵抗を用いる場合、抵抗による電流は、例えば、電源電圧5.0Vで切り替え電流が200μAの場合9500Ω[(5.0−3.1)÷200μA]の抵抗を用いれば、前記実施例同様の効果を得ることができる。

【0068】

また、実施例1の回路を、対象機器が未使用で待機している場合に負荷電流が自ずと減少する論理回路やそれらを内蔵した携帯機器等の電源として適用した場合、自発的に電源回路電流を削減することができ、待機時電流低減が可能である。

【0069】

実施例1によればつぎのような効果を有する。

(1)対象機器が動作する高負荷のときは、メインボルテージレギュレータ10が動作して対象機器に電力(第1の設定電圧3.0Vで出力電流100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源34を流れる電流の電流値が電流源設定電流以下になると電流源34によって第2の出力トランジスタ33の第1の端子電圧が上昇する。電圧が上昇して第2の設定電圧(3.1V)よりも高い電圧に到達すると、第2のオペアンプ31の動作によって第2の出力トランジスタ33の制御電圧は第2のオペアンプ31の能力に応じた0Vに近い低い電位から、出力設定電圧から出力トランジスタの閾値の差分に近い電位に上昇する。これを低消費VR動作検出回路40で検出しメインボルテージレギュレータ10をオフし電力供給を停止する。このとき低消費ボルテージレギュレータ30によってメインボルテージレギュレータ10よりも高い出力の電圧(負荷電流200μA以下)が負荷に供給される。再び負荷電流値が低消費VR設定電流よりも大きくなると、電流源34によって第2の出力トランジスタ33の供給電圧が低下する。第2のオペアンプ31の動作によって出力電圧を設定電圧に近づけるように第2のオペアンプ31の能力に応じた0Vに近い低い電位を第2の出力トランジスタ33の制御端子に印加するので、これを低消費VR動作検出回路40で検出しメインボルテージレギュレータ10はオンし、再び電力(第1の設定電圧3.0Vで出力電流100mA)を対象機器に供給するようになる。この場合、メインボルテージレギュレータ10の回路消費電流が100μAと低消費ボルテージレギュレータ30の消費電流5μAを加算した105μAが回路消費電流である。この結果、対象機器が動作しないときは消費電流の低減が図れる。

【0070】

(2)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、実施例の電源供給回路1の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ10及び低消費ボルテージレギュレータ30)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、実施例では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0071】

(3)実施例の電源供給回路1においては、低消費時の低消費ボルテージレギュレータ30の電圧(第2の設定電圧)をメインボルテージレギュレータ10の電圧(第1の設定電圧)よりも、若干高く(例えば、0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0072】

(4)実施例の電源供給回路1は、要素回路が比較的単純であるので製品の小型化が可能である。

【0073】

(5)実施例の電源供給回路1ではEN制御が不要となる利点がある。

【0074】

(6)実施例の電源供給回路1では低負荷電流時(例えば200μA)に求められるボルテージレギュレータの低消費電流化と、高負荷電流時(例えば100mA)に求められるボルテージレギュレータの負荷過渡特性や電源リップル除去率の特性をそれぞれ最適化した2つのボルテージレギュレータを切り替えることで実現可能である。

【0075】

(7)実施例の電源供給回路1では電流源34と組み合わせることで、比較的容易に負荷電流値を検出することができる。

【0076】

(8)実施例の電源供給回路1では電流源34の電流源設定電流値を任意に設定することで容易に、メインボルテージレギュレータ10の切り替え電流値を可変可能である。

【0077】

(9)実施例の電源供給回路1では2つのボルテージレギュレータを使用するため、それぞれ任意の設定電圧とすることができ、負荷用途に応じた切り替え電圧を設定可能である。例えば、切り替え時の電圧降下を少なくしたい場合、メインボルテージレギュレータ10と低消費ボルテージレギュレータ30の第2の設定電圧差を増やすことで実現可能である。

【0078】

(10)実施例の電源供給回路1では電流源34と組み合わせることで、負荷電流に比例して出力電圧が連続的に切り替わるので、特許文献1等の従来回路に比較しレギュレータ切り替え時の電圧変動を回避できる。

【実施例2】

【0079】

図4乃至図6は本発明の実施例2である電源供給回路に係わる図である。図4は電源供給回路を示す回路図、図5は電源供給回路の機能を示すブロック図、図6は電源供給回路の動作を示す動作表である。

【0080】

実施例2の電源供給回路1Aは、図4の回路図に示すように、メインボルテージレギュレータ(メインVR)10、シャントボルテージレギュレータ(シャントVR)30A、メインボルテージレギュレータ動作検出回路50、シャントボルテージレギュレータ(シャントVR)動作検出回路60、及びORゲート70等で構成されている。

【0081】

メインボルテージレギュレータ10は、第1のオペアンプ11と、第1のオペアンプ11の出力端子12に制御端子を介して接続される第1の出力トランジスタ14を有している。第1の出力トランジスタ14は、例えば、PMOSである。第1のオペアンプ11の出力端子12と第1基準電圧端子(電源)15間には第1のオン・オフ用トランジスタ16が接続されている。第1のオン・オフ用トランジスタ16は、例えば、PMOSである。第1のオペアンプ11の負の電源端子とグランドとの間には第2のオン・オフ用トランジスタ17が接続されている。第2のオン・オフ用トランジスタ17は、例えば、NMOSである。メインVR10は第1の出力トランジスタ14の第2の端子(ドレイン電極)から第1の設定電圧を出力する。このときの電流量はI1である。

【0082】

シャントボルテージレギュレータ30Aは、第2のオペアンプ31と、第2のオペアンプ31の出力端子32に制御端子を介して接続される第2の出力トランジスタ33を有している。第2の出力トランジスタ33は、例えば、NMOSである。第2の出力トランジスタ33の第1の端子(ドレイン電極)はメインVR10の第1の出力トランジスタ14の第2の端子(ドレイン電極)に接続されている。また、バイパスとして電源15とシャントVR30Aの第2の出力トランジスタ33の第1の端子(ドレイン電極)間には電流源34が接続されている。また、第2の出力トランジスタ33の第1の端子(ドレイン電極)から所定の電力を出力する。また、第2の出力トランジスタ33の第2の端子はグランドに接続され、動作時I3なる電流が流れる。

【0083】

前記電流源34は、電源供給回路1Aが電力を供給する対象機器の負荷が減少し、電流源34を流れる電流の電流値(I2)が電流源電流以下になると電圧を上昇させて前記第1の設定電圧よりも高い切替電圧にする。

【0084】

第1のオペアンプ11の反転入力端子及び第2のオペアンプ31の非反転入力端子には基準電位(Vref)が印加される。また、メインVR10の第1の出力トランジスタ14の第2の端子とグランドとの間には直列に3個の抵抗Ra,Rb,Rcが接続されている。そして、抵抗Raと抵抗Rbとの間のノードeと第1のオペアンプ11の非反転入力端子が接続されている。また、抵抗Rbと抵抗Rcとの間のノードfと第2のオペアンプ31の反転入力端子が接続されている。

【0085】

参照電圧(Vref)を1.5V、電源15を5.0V、電流源電流を5μA、第1の設定電圧を3.0V、切替電圧を3.1Vに設定した場合、各電子部品の特性は適宜選択され、メインVR10が動作するときは、出力電圧Voutは3.0Vとなり、消費電流はメインVR100μAとシャントVR5μAを合計し105μAになるように構成されている。また、シャントVR30Aが動作するときは、出力電圧Voutは3.1Vとなり、消費電流はシャントVR5μAと電流源電流から負荷電流を引いた値を加算した電流になる。負荷電流が4μA時の回路消費は、電流源電流5μAからと負荷電流4μAを引いた1μAとシャントVRの5μAを加算し、合計回路電流6μAとなる。負荷電流がゼロの場合、電流源電流5μAとシャントVR5μAを加算した10μAが回路消費となる。

【0086】

一方、第1のオペアンプ11の出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路(メインVR動作検出回路)50、及び第2のオペアンプ31の出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路(シャントVR動作検出回路)60が設けられている。

【0087】

メインVR動作検出回路50は、電源15とグランドとの間にトランジスタ51及び電流源52が直列に接続されている。トランジスタ51の第2の端子が電流源52に接続されている。トランジスタ51は、例えば、PMOSトランジスタであり、制御端子が第1のオペアンプ11の出力端子12に接続され、第1のオペアンプ11の出力が第1の設定電圧以上か未満かをトランジスタ51の制御端子に入力される信号PGAに基づいて検出するようになっている。メインVR動作検出回路50のトランジスタ51の第2の接続端子(ドレイン電極)から検出信号PGABが出力される。

【0088】

シャントVR動作検出回路60は電源15とグランドとの間に電流源61及びトランジスタ62が直列に接続されている。トランジスタ62の第1の接続端子が電流源61に接続されている。トランジスタ62は、例えば、NMOSトランジスタであり、制御端子が第2のオペアンプ31の出力端子32に接続され、第2のオペアンプ31の出力が第2の設定電圧以上か未満かをトランジスタ62の制御端子に入力される信号NGAに基づいて検出するようになっている。シャントVR動作検出回路60のトランジスタ62の第1の端子(ドレイン電極)から検出信号NGABが出力される。

【0089】

他方、ORゲート70の入力端子の一方はメインVR動作検出回路50のトランジスタ51の第2の接続端子(ドレイン電極)に接続され、ORゲート70の入力端子の他方はシャントVR動作検出回路60のトランジスタ62の第1の接続端子(ドレイン電極)に接続されている。ORゲート70の出力端子はメインVR10の第1及び第2のオン・オフ用トランジスタ16,17の制御端子にそれぞれ接続され、イネーブル信号(EN)1を制御端子に印加する。

【0090】

この電源供給回路1Aにおいては、対象機器の負荷が減少しシャントVR30Aの電流源34を流れる電流I2の電流値が電流源設定電流以下になると電流源34は電圧を上昇させて第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)にするように構成されている。この結果、切替電圧(3.1V)に到達した状態では、メインVR10の第1のオペアンプ11の出力電圧は第1の出力トランジスタ14をオンしない状態となり、シャントVR30Aの第2のオペアンプ31の出力電圧は第2の出力トランジスタ33をオンする状態となり、ORゲート70はメインVR10をオフする。この結果、第2の出力トランジスタ33から出力電圧Voutが3.1Vとなり、電流源から出力電流Ioutが5μA以下となる電力を対象機器の負荷に出力することになる。

【0091】

また、負荷電流Iout2の電流値が電流源設定電流よりも多くなると、電流源34から供給されるVoutの電圧は下降する。出力電圧Voutが3.1Vよりも小さくなると、シャントVR30Aの第2のオペアンプ31の出力は第2の出力トランジスタ33をオフする状態となり、ORゲート70はメインVR10をオンする。負荷電流が5 μAより大きい場合、電流に比例して電圧降下が発生する。更に電流が増加し、メインVRの設定電圧3.0Vに近づいた場合、第1の出力トランジスタ14から主に出力電流が供給され出力電圧Vout=3.0Vが保たれる。結果、メインVRの能力に応じた電力を対象機器の負荷に出力することになる。

【0092】

つぎに、実施例の電源供給回路1AによってメインVR10をオン・オフ(ON・OFF)制御できることを示す。

【0093】

(1)I2設定値<Ioutの場合

メインVR側の出力電圧VoutはVVR1とする。オペアンプの動作によってVref=V1の関係が成り立つ。

メインVR側のV1は次式で与えられる。

【0094】

【数9】

また、メインVR側のVoutは次式で与えられる。

【0095】

【数10】

シャントVR側の出力電圧VoutはVVR2とする。オペアンプの動作によってVref=V2が成り立つ。

シャントVR側のV2は次式で与えられる。

【0096】

【数11】

また、シャントVR側のVoutは次式で与えられる。

【0097】

【数12】

とすると、[数10]にRa=Rb+Rcを代入し、

【0098】

【数13】

を得る。

[数12]にRa=Rb+Rcを代入し、

【0099】

【数14】

を代入し

【0100】

【数15】

を得る。

VoutをVVR1−VVR2とした場合[数13]及び[数14]から

【0101】

【数16】

となる。

よって、I3はVVR1より(1/15)・Vref高い時流れる。

【0102】

(2)I2設定値>Ioutの場合

Iout=(I1+I2)−I3に代入し、

I2>I1+I2−I3

I2+I3>I1+I2

I3>I1+I2−I2

I3>I1

よって、I1よりI3が支配的に作用することが分かる。I3はVVR2によって流れるため電圧はVVR2に近づく。

【0103】

I1が流れている場合

第1の出力トランジスタ14がオン(ON)の状態で、そのゲート電位であるPGA電位はメインVR動作検出回路50のPMOSトランジスタ51を同様にオン(ON)する。それによってPGAB電位は電源電位に近づき高く(H)なり、ORゲート70によりEN1は電源電位に近づき高く(H)なることでメインVR10は オン(ON)する。

【0104】

上記の場合か、I3が流れていない場合

第2の出力トランジスタ33がオフ(OFF)の状態で、そのゲート電位であるNGA電位はシャントVR動作検出回路60のNMOSトランジスタ62を同様にオフ(OFF)する。それによってNGAB電位は電源電位に近づき高く(H)なり、ORゲート70によりEN1は電源電位に近づき高く(H)なることでメインVR10はオン(ON)する。

【0105】

I1が少ない場合

第1の出力トランジスタ14がオフ(OFF)の状態で、そのゲート電位であるPGA電位はメインVR動作検出回路のPMOSトランジスタ51を同様にオフ(OFF)する。それによってPGABはグランド電位に近づき低く(L)なる。且つVoutが3.1Vに達している場合、NMOS33はオン(ON)する。そのゲート電位であるNGAはシャントVR動作検出回路60のNMOSトランジスタ62をオン(ON)する。それによりNGAB電位がグランド電位に近づき低い(L)電位となる。ORゲート70の両入力がグランドに近い低い(L)電位のためEN1はグランド電位に近づき低く(L)なり、オン・オフ用トランジスタ17がオフすることでメインVR10の回路電流をオフ(OFF)する。同時に第1のオン・オフ用トランジスタ16によって第1の出力トランジスタ14が動作しないようPGA電位を電源電位に近い高い電位(H)に固定する。

【0106】

以上、I2の設定値によってIoutを検出し、EN1を制御し、メインVRをオフまたはオン動作させることができる。

【0107】

図6は既に説明した実施例1の電源供給回路1Aの出力電流Iout,出力電圧Vout及びイネーブル信号EN1の高負荷時と低負荷時の状態を示す動作表である。

【0108】

また、実施例1の電源供給回路は、図5に示すように、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータ(メインVR)10と、メインVR10に接続され対象機器が動作しないとき対象機器の負荷にメインVR10の供給電力よりも少ない電力を供給する電圧切替回路75と、電圧切替回路75によって設定電圧(例えば3.1V)を超えないようにするシャントボルテージレギュレータ(シャントVR)30Aと、負荷に供給される電圧値を監視(検出)し、前記電圧値が設定した設定電圧(例えば、3.1V)に到達したときメインVR10の動作を切り、前記電圧値が設定した前記設定電圧よりも低くなるとメインVR10を動作させるメインボルテージレギュレータ(メインVR)EN動作監視回路74とを有する構成になっている。

【0109】

図4において説明するならば、メインVR動作監視回路74は、ORゲート70との接続関係を有する各部、即ち、ORゲート70、第1のオン・オフ用トランジスタ16、第2のオン・オフ用トランジスタ17、メインVR動作検出回路50、メインVR動作検出回路50と第1のオペアンプ11の出力端子12とを接続する配線、シャントVR動作検出回路60、シャントVR動作検出回路60と第2のオペアンプ31の出力端子32とを接続する配線によって構成される。

【0110】

図1の回路において用いるトランジスタは、各箇所でPMOS,NMOSのいずれでもよい。メインVRの第1の出力トランジスタ14とシャントVRの第2の出力トランジスタ33のPMOSとNMOSのタイプが図4と異なる場合、オペアンプの反転入力端子と非反転入力端子が逆転する。同様にメインVR動作検出回路のトランジスタ51とシャントVR動作検出回路のトランジスタ62のPMOSとNMOSタイプが逆転する。しかし、メインVR10の第1の出力トランジスタ14をPMOSとし、シャントVR30Aの第2の出力トランジスタ33をNMOSとすることは、以下の点でメリットがある。即ち、PMOSとNMOSでは電源とグランドに対するゲート・ドレイン間電圧のかかり方が異なり、出力する電圧と電源電圧の電圧差が少なくて済む方がトランジスタサイズの低減につながり、また効率良く出力できる電圧範囲が広がる。

【0111】

つぎに、実施例によればつぎのような効果を有する。

(1)対象機器が動作する高負荷のときは、メインボルテージレギュレータ10が動作して対象機器に電力(第1の設定電圧3.0Vで出力電流100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源34を流れる電流の電流値が電流源設定電流以下になると電流源34によって電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達すると、ORゲート70によってメインボルテージレギュレータ10をオフし電力供給を停止する。このときシャントボルテージレギュレータ30Aによってメインボルテージレギュレータ10よりも高い出力の電圧(3.1Vで負荷電流5μA以下)が負荷に供給される。負荷電流がゼロの場合、電流源34の電流5μAとシャントボルテージレギュレータ30Aの5μAを加算した10μAが回路消費電流となる。また、電流値が切替電圧(3.1V)よりも低くなると、ORゲート70によってメインボルテージレギュレータ10はオンし、再び電力(第1の設定電圧3.0Vで出力電流100mA)を対象機器に供給するようになる。この場合、メインボルテージレギュレータ10の回路消費電流が100μAとシャントボルテージレギュレータ30Aの消費電流5μAを加算した105μAが回路消費電流である。この結果、対象機器が動作しないときは消費電流の低減が図れる。

【0112】

(2)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、実施例2の電源供給回路1Aの場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ10及びシャントボルテージレギュレータ30A)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、実施例2では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0113】

(3)実施例2の電源供給回路1Aにおいては、低消費時のシャントボルテージレギュレータ30Aの電圧(第2の設定電圧)をメインボルテージレギュレータ10の電圧(第1の設定電圧)よりも、若干高く(例えば、0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0114】

(4)実施例2の電源供給回路1Aは、要素回路が比較的単純であるので製品の小型化が可能である。

(5)実施例2の電源供給回路1AではEN制御が不要となる利点がある。

【0115】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。実施例2において、電圧切替回路75を電流源34に代えて抵抗等の電流を流す機能であっても、前記実施例2同様の効果がある。この場合、抵抗等による電流は、例えば、電源電圧5.0Vで切り替え電流が5μAの場合1MΩの抵抗を用いれば良い。

【0116】

なお、本発明を機器が未使用で待機している場合に負荷電流が自ずと減少する論理回路やそれらを内蔵した携帯機器等の電源として適用した場合、自発的に電源回路電流を削減することができ、待機時電流低減が可能である。

【図面の簡単な説明】

【0117】

【図1】本発明の実施例1である電源供給回路を示す回路図である。

【図2】実施例1の電源供給回路の機能を示すブロック図である。

【図3】実施例1の電源供給回路の動作を示す動作表である。

【図4】本発明の実施例2である電源供給回路を示す回路図である。

【図5】実施例2の電源供給回路の機能を示すブロック図である。

【図6】実施例2の電源供給回路の動作を示す動作表である。

【符号の説明】

【0118】

1,1A…電源供給回路、10…メインボルテージレギュレータ(メインVR)、11…第1のオペアンプ、12…出力端子、14…第1の出力トランジスタ、15…電源、16…第1のオン・オフ用トランジスタ、17…第2のオン・オフ用トランジスタ、30…低消費ボルテージレギュレータ(低消費VR)、30A…シャントボルテージレギュレータ(シャントVR)、31…第2のオペアンプ、32…出力端子、33…第2の出力トランジスタ、34…電流源、40…低消費ボルテージレギュレータ動作検出回路(低消費VR動作検出回路)、41…電流源、42…トランジスタ、43…インバーター回路、50…メインボルテージレギュレータ動作検出回路(メインVR動作検出回路)、51…トランジスタ、52…電流源、60…シャントボルテージレギュレータ動作検出回路(シャントVR動作検出回路)、61…電流源、62…トランジスタ、70…ORゲート、74…メインVR動作監視回路、75…電圧切替回路。

【技術分野】

【0001】

本発明は電源供給回路に係わり、特に負荷電流を検出して通常消費で負荷過渡特性と電源リップル除去特性が良好なメインボルテージレギュレータ(VR)と、スタンバイ用の低消費ボルテージレギュレータ(低消費VR)の同時動作か低消費VRのみかの切替を自動的に行う電源供給回路に関する。

【背景技術】

【0002】

各種電子機器において、回路の低消費電流化のため、通常消費のメインボルテージレギュレータと、スタンバイ用の低消費ボルテージレギュレータとを有する電源供給回路が知られている(例えば、特許文献1)。そして、メインボルテージレギュレータと低消費ボルテージレギュレータの切り替え(オン・オフ動作)は、電子機器に内蔵されるマイクロコントローラ(CPU)等のコンピュータによるイネーブル(EN)信号によって制御されている。

【0003】

また、ボルテージレギュレータ(VR)の切り替えの他の手段としては、負荷電流に応じた消費電流制御を行う電流可変型の電源供給回路も知られている(例えば、特許文献2)。

【0004】

【特許文献1】特開2001−69677号公報

【特許文献2】特開2000−66745号公報

【発明の開示】

【発明が解決しようとする課題】

【0005】

メインボルテージレギュレータと低消費ボルテージレギュレータを自動的に切り替える手段では、切替時点で予測されるボルテージレギュレータ(VR)出力電流変動に応じて予めEN制御する必要があり、実質スタンバイ状態が明確である機器でしか有効性が無い。何時負荷変動するか不明な場合、低消費ボルテージレギュレータを適用できない。

【0006】

従来の負荷電流に応じた消費電流制御ボルテージレギュレータ回路(電源供給回路)は、1つのボルテージレギュレータで軽負荷時に低消費化するものであるが、消費電流の変化に応じた特性変動が大きく、消費電流の最大から最小格差が大きい程良好な特性を満足させる設計定数を得ることが非常に困難であった。

【0007】

本発明の目的は、低消費電流化が達成できる電源供給回路を提供することにある。

本発明の前記ならびにそのほかの目的と新規な特徴は、本明細書の記述および添付図面からあきらかになるであろう。

【課題を解決するための手段】

【0008】

本願において開示される発明のうち代表的なものの概要を簡単に説明すれば、下記のとおりである。

(1)電源供給回路は、

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの前記出力端子と第1基準電圧(電源)端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧(グランド)端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧(例えば、3.0V)を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第2の端子から前記第1の設定電圧よりも高い第2の設定電圧(例えば、3.1V)を出力する低消費ボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の出力トランジスタを最大に駆動する電位であるかを検出する低消費ボルテージレギュレータ動作検出回路を有し、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第2の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続されるとともに、対象機器の負荷に接続される端子となり、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの反転入力端子には基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオペアンプの非反転入力端子が接続され、

前記メインボルテージレギュレータの消費電力(例えば、3.0Vでメインボルテージレギュレータは100μA消費)に比較して前記低消費ボルテージレギュレータの消費電力(例えば、3.1Vで低消費ボルテージレギュレータは5μAの消費)が小さく構成されていることを特徴とする。

【0009】

前記低消費ボルテージレギュレータの第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源によって前記メインボルテージレギュレータの前記第1の設定電圧と前記低消費ボルテージレギュレータの前記第2の設定電圧とが切り替わる構成である。前記低消費ボルテージレギュレータの前記第2の設定電圧(例えば3.1V)は前記メインボルテージレギュレータの前記第1の設定電圧(例えば3.0V)より高く(例えば0.1V)設定されており、前記低消費ボルテージレギュレータの電流源電流設定値未満では前記低消費ボルテージレギュレータの前記第2の設定電圧を出力するが、電流源電流設定値以上ではこの電圧を出力せず、電流源電流設定値以上の電流を出力する前記メインボルテージレギュレータの前記第1の設定電圧に切り替わる構成となっている。

【0010】

前記メインボルテージレギュレータの負荷過渡特性(例えば200μA〜100mA負荷変動時に電圧降下が50mV未満)と電源リップル除去率(例えば30mA負荷、1kHzで60db以上)は前記低消費ボルテージレギュレータより良好な特性であり、高負荷時(例えば200μA以上)に電圧変動が少なく負荷に対し安定に電力を供給することができる。前記メインボルテージレギュレータの前記低消費ボルテージレギュレータより良好な特性は、前記低消費ボルテージレギュレータより大きい消費電流で最適化した回路定数により主に応答速度の向上の結果実現する。負荷電流が小さい場合(例えば200μA未満)は前記高負荷時に比較して負荷変動量が小さいため(例えば200μA未満)特性が前記メインボルテージレギュレータより劣る(例えば負荷過渡特性200μA〜100mA負荷変動時に電圧降下が50mV以上、電源リップル除去率30mA負荷、1kHzで60db未満)を適用し、自己の消費電流を低減する(例えば200μA以上の負荷時の消費電流はメインボルテージレギュレータの消費電流100μA+低消費ボルテージレギュレータの消費電流5μA=105μA、200μA未満の負荷時の消費電流は低消費ボルテージレギュレータのみの消費電流5μA)。

【0011】

また、低消費ボルテージレギュレータ動作検出回路により低消費ボルテージレギュレータの前記第2の設定電圧(例えば3.1V)以下であるかを検出し、前記メインボルテージレギュレータのオン、オフ制御を行う構成である。

【0012】

前記切替電圧(3.1V)に到達した状態では、前記低消費ボルテージレギュレータの前記定電流源の動作によって、前記第2の出力トランジスタには、出力設定電圧以上の電圧が与えられる。前記オペアンプの動作によって出力設定電圧を維持するため前記出力トランジスタの制御端子には前記第2の出力トランジスタをオンする電圧が最大では無い電位(オペアンプが出力できる最低電圧が0Vの場合0Vより高い電位)で印加される。前記低消費ボルテージレギュレータ動作検出回路では、前記出力トランジスタの制御端子が最大にオンする電位では無いことを検出し前記メインボルテージレギュレータをオフし、

前記切替電圧(3.1V)よりも低くなった状態では、前記低消費ボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタを最大でオンする状態となり、前記低消費ボルテージレギュレータ動作検出回路は前記メインボルテージレギュレータをオンする。

【0013】

(2)電源供給回路は、

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの出力端子と第1基準電圧(電源)端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧(グランド)端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧(例えば、3.0V)を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第1の端子から前記第1の設定電圧よりも高い第2の設定電圧(例えば、3.1V)を出力するシャントボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第1のオペアンプの出力端子に接続され、前記第1のオペアンプの出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路と、

前記第1基準電圧端子と前記第2基準電圧端子との間に電流源及びトランジスタが直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの出力端子に接続され、前記第2のオペアンプの出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路と、

前記メインボルテージレギュレータ動作検出回路及び前記シャントボルテージレギュレータ動作検出回路の検出出力を入力し、前記第1のオン・オフ用トランジスタ及び前記第2のオン・オフ用トランジスタの制御端子に出力するORゲートとを有し、

前記シャントボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続され、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの非反転入力端子には基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオン・オフの反転入力端子が接続され、

前記メインボルテージレギュレータの消費電力(例えば、3.0Vで100mAの負荷電流時にメインボルテージレギュレータは100μA消費)に比較して前記シャントボルテージレギュレータの消費電力(例えば、3.1Vで4μAの負荷電流時にシャントボルテージレギュレータは5μAの消費)が小さく構成されていることを特徴とする。

【0014】

また、前記対象機器の負荷が減少し前記シャントボルテージレギュレータの前記電流源を流れる電流の電流値が電流源電流以下になると前記電流源が電圧を上昇させて前記第1の設定電圧よりも高い切替電圧(例えば、3.1V)にするように構成され、

前記切替電圧(3.1V)に到達した状態では、前記メインボルテージレギュレータの前記第1のオペアンプの出力電圧は前記第1の出力トランジスタをオンしない状態となり、前記シャントボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタをオンする状態となり、前記ORゲートは前記メインボルテージレギュレータをオフし、

前記切替電圧(3.1V)よりも低くなった状態では、前記シャントボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタをオフする状態となり、前記ORゲートは前記メインボルテージレギュレータをオンする。

【発明の効果】

【0015】

本願において開示される発明のうち代表的なものによって得られる効果を簡単に説明すれば、下記のとおりである。

前記(1)の手段によれば、(a)対象機器が動作する高負荷のときは、メインボルテージレギュレータが動作して対象機器に電力(第1の設定電圧3.0Vで100mA)を供給する。このとき第2の低消費ボルテージレギュレータは最大出力電流(例えば電流源電流200μA)を供給しているが、電流源の動作によって電圧降下が生じ第1の設定電圧になる。対象機器が動作しなくなると負荷が減少し、前記第2の低消費ボルテージレギュレータによって電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達し、尚且つ電流源の電流供給能力を上回った場合第2のオペアンプ出力は第2のトランジスタを最大限にオンする電位(例えば出力トランジスタがPMOSである場合、オペアンプの能力に応じた0Vに近い低い電位)から上昇(出力設定電圧から出力トランジスタの閾値の差分に近づく)に転ずる。この状態を低消費ボルテージレギュレータ動作検出回路によって検出し、メインボルテージレギュレータの電力供給を停止する。このとき電流源からメインボルテージレギュレータよりも低出力の電力(3.1Vで200μA未満)が負荷に供給される。また、電流値が切替電圧(3.1V)よりも低くなると、低消費ボルテージレギュレータ動作検出回路によってメインボルテージレギュレータはオンし、再び電力(第1の設定電圧3.0Vで100mA)を対象機器に供給するようになる。この結果、対象機器が低消費ボルテージレギュレータ供給電流(例えば3.1V、200μA)より大きな負荷時はメインボルテージレギュレータと低消費ボルテージレギュレータ両方の動作電流を消費する。(例えばメインボルテージレギュレータ消費電流が100μA、低消費ボルテージレギュレータ消費電流が5μA、合計105μA)対象機器が低消費ボルテージレギュレータ供給電流(例えば200μA)より小さな負荷時はメインボルテージレギュレータが動作を停止し、低消費ボルテージレギュレータの消費電流(例えば5μA)のみとなり消費電流の低減が図れる(負荷電流がメインボルテージレギュレータを停止させない場合に比べ100μAの消費低減効果を持つ)。

【0016】

(b)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、本発明の電源供給回路の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ及び低消費ボルテージレギュレータ)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、本発明では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0017】

(c)本発明の電源供給回路においては、低消費時の低消費ボルテージレギュレータの電圧(第2の設定電圧)をメインボルテージレギュレータの電圧(第1の設定電圧)よりも、若干高く(例えば0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0018】

(d)本発明の電源供給回路は、要素回路が比較的単純であるので製品の小型化が可能である。

(e)本発明の電源供給回路ではEN制御が不要となる利点がある。

【0019】

前記(2)の手段によれば、(a)対象機器が動作する高負荷のときは、メインボルテージレギュレータが動作して対象機器に電力(第1の設定電圧3.0Vで100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源を流れる電流の電流値が電流源設定電流以下になると電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達すると、ORゲートによってメインボルテージレギュレータをオフし電力供給を停止する。このとき電流源からメインボルテージレギュレータよりも低出力の電力(3.1Vで5μA未満)が負荷に供給される。また、電流値が切替電圧(3.1V)よりも低くなると、ORゲートによってメインボルテージレギュレータはオンし、再び電力(第1の設定電圧3.0Vで100mA)を対象機器に供給するようになる。この結果、対象機器が電流源電流(例えば5μA)より大きな負荷時はメインボルテージレギュレータとシャントボルテージレギュレータ両方の動作電流を消費する。(例えばメインシャントレギュレータ消費電流が100μA、シャントレギュレータ消費電流が5μA、合計105μA)対象機器が電流源設定電流(例えば5μA)より小さな負荷時はメインボルテージレギュレータが動作を停止し、シャントボルテージレギュレータの消費電流(例えば5μA)のみとなり消費電流の低減が図れる。負荷電流が電流源設定電流より小さい場合は、シャントボルテージレギュレータによって余剰電流がグランドに引き抜かれるので、その場合見かけ上消費電力と等価であり、負荷電流がゼロの場合電流源電流全てとシャントレギュレータ消費電流を加算した値が回路消費電流になる。(例えば負荷電流0の場合、電流源電流5μAとシャントボルテージレギュレータ消費5μAを加算し消費電流10μAである。メインボルテージレギュレータを停止させない場合に比べ95μAの消費低減効果を持つ。)消費電流低減を目的として本発明を適用する場合、電流源電流とシャントボルテージレギュレータ消費電流を加算した値が、メインボルテージレギュレータの消費電流を下回る必要がある。

【0020】

(b)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、本発明の電源供給回路の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ及びシャントボルテージレギュレータ)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、本発明では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0021】

(c)本発明の電源供給回路においては、低消費時のシャントボルテージレギュレータの電圧(第2の設定電圧)をメインボルテージレギュレータの電圧(第1の設定電圧)よりも、若干高く(例えば0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0022】

(d)本発明の電源供給回路は、要素回路が比較的単純であるので製品の小型化が可能である。

(e)本発明の電源供給回路ではEN制御が不要となる利点がある。

【発明を実施するための最良の形態】

【0023】

以下、図面を参照して本発明の実施の形態を詳細に説明する。なお、発明の実施の形態を説明するための全図において、同一機能を有するものは同一符号を付け、その繰り返しの説明は省略する。

【実施例1】

【0024】

図1乃至図3は本発明の実施例1である電源供給回路に係わる図である。図1は電源供給回路を示す回路図、図2は電源供給回路の機能を示すブロック図、図3は電源供給回路の動作を示す動作表である。

【0025】

図1の回路図に示すように、電源供給回路1は、メインボルテージレギュレータ(メインVR)10、低消費ボルテージレギュレータ(低消費VR)30、低消費ボルテージレギュレータ動作検出回路40で構成されている。

【0026】

メインボルテージレギュレータ(メインVR)10は、第1のオペアンプ11と、第1のオペアンプ11の出力端子12に制御端子を介して接続される第1の出力トランジスタ14を有している。第1の出力トランジスタ14は、例えば、PMOSである。第1のオペアンプ11の出力端子12と電源15間には第1のオン・オフ用トランジスタ16が接続されている。第1のオン・オフ用トランジスタ16は、例えば、PMOSである。第1のオペアンプ11の負の電源端子とグランドとの間には第2のオン・オフ用トランジスタ17が接続されている。第2のオン・オフ用トランジスタ17は、例えば、NMOSである。メインVR10は第1の出力トランジスタ14の第2の端子(ドレイン電極)から第1の設定電圧を出力する。このときの電流量はI1である。

【0027】

低消費ボルテージレギュレータ(低消費VR)30は、第2のオペアンプ31と、第2のオペアンプ31の出力端子32に制御端子を介して接続される第2の出力トランジスタ33を有している。第2の出力トランジスタ33は、例えば、PMOSである。第2の出力トランジスタ33の第2の端子(ドレイン電極)はメインVR10の第1の出力トランジスタ14の第2の端子(ドレイン電極)に接続されている。また、電源15と低消費VR30の第2の出力トランジスタ33の第1の端子(ソース電極)間には電流源34が接続されている。電流源34の動作によって低消費ボルテージレギュレータの出力電流の最大値が設定される。低消費ボルテージレギュレータの電流量はI2である。

【0028】

第1のオペアンプ11の反転入力端子及び第2のオペアンプ31の反転入力端子には基準電位(Vref)が印加される。また、メインVR10の第1の出力トランジスタ14の第2の端子とグランドとの間には直列に3個の抵抗Ra,Rb,Rcが接続されている。そして、抵抗Raと抵抗Rbとの間のノードeと第1のオペアンプ11の非反転入力端子が接続されている。また、抵抗Rbと抵抗Rcとの間のノードfと第2のオペアンプ31の非反転入力端子が接続されている。

【0029】

参照電圧(Vref)を1.5V、電源15を5.0V、第1の設定電圧を3.0V、切替電圧を3.1Vに設定した場合、各電子部品の特性は適宜選択され、メインVR10が動作するときは、出力電圧Voutは3.0Vとなり、消費電流はメインVR100μAと低消費VR5μAを合計し105μAになるように構成されている。また、メインVRが動作しないときは、出力電圧Voutは3.1Vとなり、消費電流は低消費VR5μAとなる。

【0030】

一方、電流源34の動作によって、その設定電流と負荷電流の大小によって第2の出力トランジスタ33の第1の端子に印加される電位が変化する。第2のオペアンプによって出力電圧設定値を超えないよう制御されるため、この電位を監視(検出)することで結果的に定電流源の電流値と出力電流の大小が判定可能である。これを利用し、設定電流以上か未満かを検出する低消費ボルテージレギュレータ動作検出回路(低消費VR動作検出回路)40が設けられている。

【0031】

低消費VR動作検出回路40は電源15とグランドとの間に電流源41及びトランジスタ42が直列に接続されている。トランジスタ42の第2の接続端子が電流源41に接続されている。トランジスタ42は、例えば、PMOSトランジスタであり、制御端子が第2のオペアンプ31の出力端子32に接続され、第2のオペアンプ31の出力が第2の出力トランジスタ33を最大出力電流で駆動できる電圧以上か未満か(オペアンプの能力に応じた0Vに近い低い電位であるか、出力設定電圧から出力トランジスタの閾値の差分に近く上昇したか)をトランジスタ42の制御端子に入力される信号PG2に基づいて検出するようになっている。低消費VR動作検出回路40のトランジスタ42の第2の端子(ドレイン電極)から検出信号PG2Bが出力される。これをインバーター回路43で極性反転した信号がメインVR制御EN1信号である。

【0032】

この電源供給回路1においては、対象機器の負荷が減少し低消費VR30の出力電流I2の電流値がI1より大きい場合電圧を上昇させて第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)にするように構成されている。この結果、切替電圧(3.1V)に到達した状態では、第2の出力トランジスタ33から出力電圧Voutが3.1Vとなり、出力電流I2(低消費VRの電流供給能力200μA以下となる)が電力を対象機器の負荷に出力することになる。負荷電流が低消費VRの最大電流供給能力(200μA)より小さくなった場合は、第2のオペアンプ31の出力は上昇に転じる。この上昇結果を低消費VR動作検出回路で検出しEN1信号にてメインVRをオフする。

【0033】

また、負荷電流の増加によって低消費VRの電流供給能力を超えると第2のオペアンプ31の出力は第2の出力トランジスタ33を最大電流で駆動する電位に降下するため、低消費VR動作検出回路40によってメインVRをオンする。負荷電流が200μAより大きい場合、電流に比例して電圧降下が発生する。更に電流が増加し、メインVRの第1の設定電圧3.0Vに近づいた場合、第1の出力トランジスタ14から主に出力電流が供給され出力電圧Vout=3.0Vが保たれる。結果、メインVRの能力に応じた電力を対象機器の負荷に出力することになる。

【0034】

つぎに、実施例の電源供給回路1によって出力される電圧の関係式を示す。

メインVR側の出力電圧VoutはVVR1とする。オペアンプの動作によってVref=V1の関係が成り立つ。

メインVR側のV1は次式で与えられる。

【0035】

【数1】

また、メインVR側のVoutは次式で与えられる。

【0036】

【数2】

低消費VR側の出力電圧VoutはVVR2とする。オペアンプの動作によってVref=V2が成り立つ。

低消費VR側のV2は次式で与えられる。

【0037】

【数3】

また、低消費VR側のVoutは次式で与えられる。

【0038】

【数4】

とすると、[数2]にRa=Rb+Rcを代入し、

【0039】

【数5】

を得る。

[数4]にRa=Rb+Rcを代入し、

【0040】

【数6】

を代入し

【0041】

【数7】

を得る。

VoutをVVR1−VVR2とした場合[数5]及び[数6]から

【0042】

【数8】

となる。

よって、VVR2はVVR1より(1/15)・Vref高い。

【0043】

図3は既に説明した実施例1の電源供給回路1の出力電流Iout,出力電圧Vout及びイネーブル信号EN1の高負荷時と低負荷時の状態を示す動作表である。

【0044】

また、実施例1の電源供給回路は、図2に示すように、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータ(メインVR)10と、メインVR10に接続され対象機器が動作しないとき対象機器の負荷にメインVR10の供給電力よりも少ない電力を供給する。電流値を検出(監視)し、前記電流値が設定した設定電流(例えば、200μA)以下に減少したときメインVR10の動作を切り、前記電流値が設定した前記設定電流よりも大きくなるとメインVR10を動作させる低消費ボルテージレギュレータ(低消費VR)動作検出回路40とを有する構成になっている。

【0045】

図1において説明するならば、低消費VR動作検出回路40は、接続関係を有する各部、即ち、第1のオン・オフ用トランジスタ16、第2のオン・オフ用トランジスタ17、第1のオペアンプ11の出力端子12とを接続する配線、低消費VR動作検出回路40、低消費VR動作検出回路40と第2のオペアンプ31の出力端子32とを接続する配線によって構成される。

【0046】

図1の回路において用いるトランジスタは、各箇所でPMOS,NMOSのいずれでもよい。メインVRの第1の出力トランジスタ14と低消費VRの第2の出力トランジスタ33のPMOSとNMOSのタイプが図1と異なる場合、オペアンプの反転入力端子と非反転入力端子が逆転する。同様に低消費VR動作検出回路のトランジスタ42のPMOSとNMOSタイプが逆転する。しかし、メインVR10の第1の出力トランジスタ14をPMOSとし、低消費VR30の第2の出力トランジスタ33をPMOSとすることは、以下の点でメリットがある。即ち、PMOSとNMOSでは電源とグランドに対するゲート・ドレイン間電圧のかかり方が異なり、出力する電圧と電源電圧の電圧差が少なくて済む方がトランジスタサイズの低減につながり、また効率良く出力できる電圧範囲が広がる。

【0047】

また電流源34は、電源15の電圧が一定の場合、出力電圧Voutとの差分を電流設定値で割ることで求まる抵抗に置き換え可能である。この抵抗は、更に第2の出力トランジスタ33のオン抵抗(トランジスタサイズの調整や、閾値の調整)に置き換えることで電流源と等価の動作を実現可能である。

【0048】

一方、実施例1の電源供給回路は、以下の構成を有する。

【0049】

電源供給回路は、

前記メインボルテージレギュレータの出力できる電流より、前記低消費ボルテージレギュレータの出力できる電流が小さく構成され、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子と前記第1基準電圧端子間に接続された前記電流源により、前記第2の出力トランジスタの前記第2の端子からは、前記電流源設定電流値以上の電流を出力することがなく、前記電流源設定電流値を超えた負荷に対し前記第2の出力トランジスタの前記第2の端子の出力電圧が低消費ボルテージレギュレータの第2の設定電圧よりも降下するように構成され、

前記第2の出力トランジスタからの出力は、前記第2の出力トランジスタの前記第2の端子が前記第1の出力トランジスタの前記第2の端子に接続されることで、前記低消費ボルテージレギュレータの前記電流源設定電流値を超えた負荷電流を、前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子から供給されて出力し、

前記第2の出力トランジスタの出力電圧は、前記低消費ボルテージレギュレータの前記電流源設定電流値未満の負荷電流に対しては、前記低消費ボルテージレギュレータの第1の設定電圧になり、前記電流源設定電流値以上の負荷電流に対しては、前記メインボルテージレギュレータの第1の設定電圧から前記低消費ボルテージレギュレータの第2の設定電圧の間になるように構成されている。

【0050】

この構成によれば、出力電流量が同等で低消費電流である特許文献1等の従来回路に比較し、低消費VRの出力トランジスタサイズが小さくできるため半導体集積回路のレイアウト面積が低減できる。また、前記のように小さな出力トランジスタ(ゲート容量が小さい)で済むためこれを駆動するオペアンプの容量駆動能力が小さくてもスルーレートが確保でき、低消費で特性の良好な回路定数を容易に得られる効果がある。

【0051】

また、実施例1の電源供給回路は、以下の構成を有する。

【0052】

電源供給回路1は、

対象機器の負荷Ioutが減少し低消費ボルテージレギュレータ30の第2の出力トランジスタ33を流れる電流の電流値が電流源34の設定電流値以下になると低消費VR30の出力電圧Voutを上昇させてメインVR10の第1の設定電圧よりも高い切替電圧にするように構成され、

低消費VR30の第2のオペアンプ31の出力端子32の電圧は第2の出力トランジスタ33を負荷電流Ioutが電流源34の設定電流値未満になるとVoutを低消費VR30の第2の設定電圧に保つよう第2の出力トランジスタ33のゲート端子を制御するため、出力できる最低電圧ではない状態(例えば0V以上)となり、低消費VR動作検出回路40の出力信号EN1はメインVR10をオフし、負荷電流Ioutが低消費VR30の電流源34の設定電流値を上回る場合、出力電圧Voutは電流源34の動作で低消費VR30の第2の設定電圧よりも低くなり、低消費VRの第2のオペアンプ31の出力端子32は第2の出力トランジスタ33をオンするよう出力できる最低電圧を出力する状態(例えば0V)となり、低消費VR動作検出回路40はメインVR10をオンする構成になっている。

【0053】

この構成によれば、電流源の動作によって負荷電流に比例した電圧切り替えが連続的に行えるため、電圧切り替え時の電圧変動による負荷に接続される回路動作への影響が少ない。また回路が単純なため回路設計が容易である効果がある。

【0054】

また、実施例1の電源供給回路は、以下の構成を有する。

【0055】

電源供給回路1は、

メインVR10は前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給し、

低消費VR30は前記対象機器が動作しないとき前記対象機器の前記負荷にメインVR10の供給電力よりも少ない電力を供給し、

低消費VR動作検出回路40は、第2のオペアンプ31の出力端子32の電位を監視し、第2の出力トランジスタ33に対し最大電流を出力する電位ではない状態(例えば0V以上)のときメインVR10の動作を切り、負荷電流Ioutの増大によって第2の出力トランジスタ33が最大電流を出力する状態(例えば0V)のときメインVR10を動作させる構成になっている。

【0056】

この構成によれば、負荷の電力需要に応じ、少ない電力需要時は過大な電流能力を持ったボルテージレギュレータを切断するため、低消費電流なる効果がある。

【0057】

また、実施例1の電源供給回路は、以下の構成を有する。

【0058】

電源供給回路1は、

メインVR10は出力負荷過渡特性が200μA〜100mA負荷変動時に電圧降下が50mV未満となり、電源リップル除去特性が30mA負荷、1kHzで60db以上となるように構成され、

前記負荷の電流が電流源34の電流源設定電流以上のときは前記メインボルテージレギュレータを動作させ、

負荷電流Ioutが設定した電流源設定電流未満の場合は前記メインボルテージレギュレータを停止させる構成になっている。

【0059】

200μA〜100mA負荷変動時に電圧降下が50mV未満となる出力負荷過渡特性と、30mA負荷、1kHzで60db以上となる電源リップル除去特性は、第1のオペアンプ(OP1)11の消費電流に対して各回路定数を最適化することによって得られる。

【0060】

このような構成によれば、負荷電流が大きい場合は出力負荷過渡特性及び電源リップル除去特性が優れたメインボルテージレギュレータを動作させ、負荷電流が設定した電流値より小さい場合はメインボルテージレギュレータを停止させるため、回路消費電流の低減を図ることができる。

【0061】

また、実施例1の電源供給回路は、以下の構成を有する。

【0062】

電源供給回路1は、

前記メインボルテージレギュレータは負荷の電流Ioutが200μA以上のとき動作し、

前記メインボルテージレギュレータは負荷電流Ioutが200μA未満のとき停止する構成になっている。

【0063】

この構成によれば、外部EN制御が不要で、負荷状況に応じて自発的に低消費VRを選択しメインVRの消費電流を低減できる効果がある。

【0064】

また、実施例1の電源供給回路は、以下の構成を有する。

【0065】

電源供給回路1は、

負荷電流Ioutが低消費VR30の電流源34の電流源設定電流値以上の場合はメインVR10の第1の設定電圧を出力し、

負荷電流Ioutが電流源34の電流源設定電流値未満の場合はメインVRは停止し、低消費VR30の第2の設定電圧を出力し、

メインVR10の第1の設定電圧より、低消費VR30の第2の設定電圧が高くなっている。

【0066】

この構成によれば、メインVR10の第1の設定電圧より、低消費VR30の第2の設定電圧を高くすることで、急激な負荷増大時に負荷である回路動に支障が出る電圧に降下するまでの時間を伸ばすことができ、メインVR10が起動するまでの時間を得ることができるため出力電圧低下を減らすことができる。

【0067】

なお、実施例において、電流源34に代えて抵抗等(トランジスタサイズの調整や、閾値の調整)を用いても前記実施例同様の効果がある。抵抗を用いる場合、抵抗による電流は、例えば、電源電圧5.0Vで切り替え電流が200μAの場合9500Ω[(5.0−3.1)÷200μA]の抵抗を用いれば、前記実施例同様の効果を得ることができる。

【0068】

また、実施例1の回路を、対象機器が未使用で待機している場合に負荷電流が自ずと減少する論理回路やそれらを内蔵した携帯機器等の電源として適用した場合、自発的に電源回路電流を削減することができ、待機時電流低減が可能である。

【0069】

実施例1によればつぎのような効果を有する。

(1)対象機器が動作する高負荷のときは、メインボルテージレギュレータ10が動作して対象機器に電力(第1の設定電圧3.0Vで出力電流100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源34を流れる電流の電流値が電流源設定電流以下になると電流源34によって第2の出力トランジスタ33の第1の端子電圧が上昇する。電圧が上昇して第2の設定電圧(3.1V)よりも高い電圧に到達すると、第2のオペアンプ31の動作によって第2の出力トランジスタ33の制御電圧は第2のオペアンプ31の能力に応じた0Vに近い低い電位から、出力設定電圧から出力トランジスタの閾値の差分に近い電位に上昇する。これを低消費VR動作検出回路40で検出しメインボルテージレギュレータ10をオフし電力供給を停止する。このとき低消費ボルテージレギュレータ30によってメインボルテージレギュレータ10よりも高い出力の電圧(負荷電流200μA以下)が負荷に供給される。再び負荷電流値が低消費VR設定電流よりも大きくなると、電流源34によって第2の出力トランジスタ33の供給電圧が低下する。第2のオペアンプ31の動作によって出力電圧を設定電圧に近づけるように第2のオペアンプ31の能力に応じた0Vに近い低い電位を第2の出力トランジスタ33の制御端子に印加するので、これを低消費VR動作検出回路40で検出しメインボルテージレギュレータ10はオンし、再び電力(第1の設定電圧3.0Vで出力電流100mA)を対象機器に供給するようになる。この場合、メインボルテージレギュレータ10の回路消費電流が100μAと低消費ボルテージレギュレータ30の消費電流5μAを加算した105μAが回路消費電流である。この結果、対象機器が動作しないときは消費電流の低減が図れる。

【0070】

(2)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、実施例の電源供給回路1の場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ10及び低消費ボルテージレギュレータ30)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、実施例では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0071】

(3)実施例の電源供給回路1においては、低消費時の低消費ボルテージレギュレータ30の電圧(第2の設定電圧)をメインボルテージレギュレータ10の電圧(第1の設定電圧)よりも、若干高く(例えば、0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0072】

(4)実施例の電源供給回路1は、要素回路が比較的単純であるので製品の小型化が可能である。

【0073】

(5)実施例の電源供給回路1ではEN制御が不要となる利点がある。

【0074】

(6)実施例の電源供給回路1では低負荷電流時(例えば200μA)に求められるボルテージレギュレータの低消費電流化と、高負荷電流時(例えば100mA)に求められるボルテージレギュレータの負荷過渡特性や電源リップル除去率の特性をそれぞれ最適化した2つのボルテージレギュレータを切り替えることで実現可能である。

【0075】

(7)実施例の電源供給回路1では電流源34と組み合わせることで、比較的容易に負荷電流値を検出することができる。

【0076】

(8)実施例の電源供給回路1では電流源34の電流源設定電流値を任意に設定することで容易に、メインボルテージレギュレータ10の切り替え電流値を可変可能である。

【0077】

(9)実施例の電源供給回路1では2つのボルテージレギュレータを使用するため、それぞれ任意の設定電圧とすることができ、負荷用途に応じた切り替え電圧を設定可能である。例えば、切り替え時の電圧降下を少なくしたい場合、メインボルテージレギュレータ10と低消費ボルテージレギュレータ30の第2の設定電圧差を増やすことで実現可能である。

【0078】

(10)実施例の電源供給回路1では電流源34と組み合わせることで、負荷電流に比例して出力電圧が連続的に切り替わるので、特許文献1等の従来回路に比較しレギュレータ切り替え時の電圧変動を回避できる。

【実施例2】

【0079】

図4乃至図6は本発明の実施例2である電源供給回路に係わる図である。図4は電源供給回路を示す回路図、図5は電源供給回路の機能を示すブロック図、図6は電源供給回路の動作を示す動作表である。

【0080】

実施例2の電源供給回路1Aは、図4の回路図に示すように、メインボルテージレギュレータ(メインVR)10、シャントボルテージレギュレータ(シャントVR)30A、メインボルテージレギュレータ動作検出回路50、シャントボルテージレギュレータ(シャントVR)動作検出回路60、及びORゲート70等で構成されている。

【0081】

メインボルテージレギュレータ10は、第1のオペアンプ11と、第1のオペアンプ11の出力端子12に制御端子を介して接続される第1の出力トランジスタ14を有している。第1の出力トランジスタ14は、例えば、PMOSである。第1のオペアンプ11の出力端子12と第1基準電圧端子(電源)15間には第1のオン・オフ用トランジスタ16が接続されている。第1のオン・オフ用トランジスタ16は、例えば、PMOSである。第1のオペアンプ11の負の電源端子とグランドとの間には第2のオン・オフ用トランジスタ17が接続されている。第2のオン・オフ用トランジスタ17は、例えば、NMOSである。メインVR10は第1の出力トランジスタ14の第2の端子(ドレイン電極)から第1の設定電圧を出力する。このときの電流量はI1である。

【0082】

シャントボルテージレギュレータ30Aは、第2のオペアンプ31と、第2のオペアンプ31の出力端子32に制御端子を介して接続される第2の出力トランジスタ33を有している。第2の出力トランジスタ33は、例えば、NMOSである。第2の出力トランジスタ33の第1の端子(ドレイン電極)はメインVR10の第1の出力トランジスタ14の第2の端子(ドレイン電極)に接続されている。また、バイパスとして電源15とシャントVR30Aの第2の出力トランジスタ33の第1の端子(ドレイン電極)間には電流源34が接続されている。また、第2の出力トランジスタ33の第1の端子(ドレイン電極)から所定の電力を出力する。また、第2の出力トランジスタ33の第2の端子はグランドに接続され、動作時I3なる電流が流れる。

【0083】

前記電流源34は、電源供給回路1Aが電力を供給する対象機器の負荷が減少し、電流源34を流れる電流の電流値(I2)が電流源電流以下になると電圧を上昇させて前記第1の設定電圧よりも高い切替電圧にする。

【0084】

第1のオペアンプ11の反転入力端子及び第2のオペアンプ31の非反転入力端子には基準電位(Vref)が印加される。また、メインVR10の第1の出力トランジスタ14の第2の端子とグランドとの間には直列に3個の抵抗Ra,Rb,Rcが接続されている。そして、抵抗Raと抵抗Rbとの間のノードeと第1のオペアンプ11の非反転入力端子が接続されている。また、抵抗Rbと抵抗Rcとの間のノードfと第2のオペアンプ31の反転入力端子が接続されている。

【0085】

参照電圧(Vref)を1.5V、電源15を5.0V、電流源電流を5μA、第1の設定電圧を3.0V、切替電圧を3.1Vに設定した場合、各電子部品の特性は適宜選択され、メインVR10が動作するときは、出力電圧Voutは3.0Vとなり、消費電流はメインVR100μAとシャントVR5μAを合計し105μAになるように構成されている。また、シャントVR30Aが動作するときは、出力電圧Voutは3.1Vとなり、消費電流はシャントVR5μAと電流源電流から負荷電流を引いた値を加算した電流になる。負荷電流が4μA時の回路消費は、電流源電流5μAからと負荷電流4μAを引いた1μAとシャントVRの5μAを加算し、合計回路電流6μAとなる。負荷電流がゼロの場合、電流源電流5μAとシャントVR5μAを加算した10μAが回路消費となる。

【0086】

一方、第1のオペアンプ11の出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路(メインVR動作検出回路)50、及び第2のオペアンプ31の出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路(シャントVR動作検出回路)60が設けられている。

【0087】

メインVR動作検出回路50は、電源15とグランドとの間にトランジスタ51及び電流源52が直列に接続されている。トランジスタ51の第2の端子が電流源52に接続されている。トランジスタ51は、例えば、PMOSトランジスタであり、制御端子が第1のオペアンプ11の出力端子12に接続され、第1のオペアンプ11の出力が第1の設定電圧以上か未満かをトランジスタ51の制御端子に入力される信号PGAに基づいて検出するようになっている。メインVR動作検出回路50のトランジスタ51の第2の接続端子(ドレイン電極)から検出信号PGABが出力される。

【0088】

シャントVR動作検出回路60は電源15とグランドとの間に電流源61及びトランジスタ62が直列に接続されている。トランジスタ62の第1の接続端子が電流源61に接続されている。トランジスタ62は、例えば、NMOSトランジスタであり、制御端子が第2のオペアンプ31の出力端子32に接続され、第2のオペアンプ31の出力が第2の設定電圧以上か未満かをトランジスタ62の制御端子に入力される信号NGAに基づいて検出するようになっている。シャントVR動作検出回路60のトランジスタ62の第1の端子(ドレイン電極)から検出信号NGABが出力される。

【0089】

他方、ORゲート70の入力端子の一方はメインVR動作検出回路50のトランジスタ51の第2の接続端子(ドレイン電極)に接続され、ORゲート70の入力端子の他方はシャントVR動作検出回路60のトランジスタ62の第1の接続端子(ドレイン電極)に接続されている。ORゲート70の出力端子はメインVR10の第1及び第2のオン・オフ用トランジスタ16,17の制御端子にそれぞれ接続され、イネーブル信号(EN)1を制御端子に印加する。

【0090】

この電源供給回路1Aにおいては、対象機器の負荷が減少しシャントVR30Aの電流源34を流れる電流I2の電流値が電流源設定電流以下になると電流源34は電圧を上昇させて第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)にするように構成されている。この結果、切替電圧(3.1V)に到達した状態では、メインVR10の第1のオペアンプ11の出力電圧は第1の出力トランジスタ14をオンしない状態となり、シャントVR30Aの第2のオペアンプ31の出力電圧は第2の出力トランジスタ33をオンする状態となり、ORゲート70はメインVR10をオフする。この結果、第2の出力トランジスタ33から出力電圧Voutが3.1Vとなり、電流源から出力電流Ioutが5μA以下となる電力を対象機器の負荷に出力することになる。

【0091】

また、負荷電流Iout2の電流値が電流源設定電流よりも多くなると、電流源34から供給されるVoutの電圧は下降する。出力電圧Voutが3.1Vよりも小さくなると、シャントVR30Aの第2のオペアンプ31の出力は第2の出力トランジスタ33をオフする状態となり、ORゲート70はメインVR10をオンする。負荷電流が5 μAより大きい場合、電流に比例して電圧降下が発生する。更に電流が増加し、メインVRの設定電圧3.0Vに近づいた場合、第1の出力トランジスタ14から主に出力電流が供給され出力電圧Vout=3.0Vが保たれる。結果、メインVRの能力に応じた電力を対象機器の負荷に出力することになる。

【0092】

つぎに、実施例の電源供給回路1AによってメインVR10をオン・オフ(ON・OFF)制御できることを示す。

【0093】

(1)I2設定値<Ioutの場合

メインVR側の出力電圧VoutはVVR1とする。オペアンプの動作によってVref=V1の関係が成り立つ。

メインVR側のV1は次式で与えられる。

【0094】

【数9】

また、メインVR側のVoutは次式で与えられる。

【0095】

【数10】

シャントVR側の出力電圧VoutはVVR2とする。オペアンプの動作によってVref=V2が成り立つ。

シャントVR側のV2は次式で与えられる。

【0096】

【数11】

また、シャントVR側のVoutは次式で与えられる。

【0097】

【数12】

とすると、[数10]にRa=Rb+Rcを代入し、

【0098】

【数13】

を得る。

[数12]にRa=Rb+Rcを代入し、

【0099】

【数14】

を代入し

【0100】

【数15】

を得る。

VoutをVVR1−VVR2とした場合[数13]及び[数14]から

【0101】

【数16】

となる。

よって、I3はVVR1より(1/15)・Vref高い時流れる。

【0102】

(2)I2設定値>Ioutの場合

Iout=(I1+I2)−I3に代入し、

I2>I1+I2−I3

I2+I3>I1+I2

I3>I1+I2−I2

I3>I1

よって、I1よりI3が支配的に作用することが分かる。I3はVVR2によって流れるため電圧はVVR2に近づく。

【0103】

I1が流れている場合

第1の出力トランジスタ14がオン(ON)の状態で、そのゲート電位であるPGA電位はメインVR動作検出回路50のPMOSトランジスタ51を同様にオン(ON)する。それによってPGAB電位は電源電位に近づき高く(H)なり、ORゲート70によりEN1は電源電位に近づき高く(H)なることでメインVR10は オン(ON)する。

【0104】

上記の場合か、I3が流れていない場合

第2の出力トランジスタ33がオフ(OFF)の状態で、そのゲート電位であるNGA電位はシャントVR動作検出回路60のNMOSトランジスタ62を同様にオフ(OFF)する。それによってNGAB電位は電源電位に近づき高く(H)なり、ORゲート70によりEN1は電源電位に近づき高く(H)なることでメインVR10はオン(ON)する。

【0105】

I1が少ない場合

第1の出力トランジスタ14がオフ(OFF)の状態で、そのゲート電位であるPGA電位はメインVR動作検出回路のPMOSトランジスタ51を同様にオフ(OFF)する。それによってPGABはグランド電位に近づき低く(L)なる。且つVoutが3.1Vに達している場合、NMOS33はオン(ON)する。そのゲート電位であるNGAはシャントVR動作検出回路60のNMOSトランジスタ62をオン(ON)する。それによりNGAB電位がグランド電位に近づき低い(L)電位となる。ORゲート70の両入力がグランドに近い低い(L)電位のためEN1はグランド電位に近づき低く(L)なり、オン・オフ用トランジスタ17がオフすることでメインVR10の回路電流をオフ(OFF)する。同時に第1のオン・オフ用トランジスタ16によって第1の出力トランジスタ14が動作しないようPGA電位を電源電位に近い高い電位(H)に固定する。

【0106】

以上、I2の設定値によってIoutを検出し、EN1を制御し、メインVRをオフまたはオン動作させることができる。

【0107】

図6は既に説明した実施例1の電源供給回路1Aの出力電流Iout,出力電圧Vout及びイネーブル信号EN1の高負荷時と低負荷時の状態を示す動作表である。

【0108】

また、実施例1の電源供給回路は、図5に示すように、対象機器が動作するとき対象機器の負荷に電力を供給するメインボルテージレギュレータ(メインVR)10と、メインVR10に接続され対象機器が動作しないとき対象機器の負荷にメインVR10の供給電力よりも少ない電力を供給する電圧切替回路75と、電圧切替回路75によって設定電圧(例えば3.1V)を超えないようにするシャントボルテージレギュレータ(シャントVR)30Aと、負荷に供給される電圧値を監視(検出)し、前記電圧値が設定した設定電圧(例えば、3.1V)に到達したときメインVR10の動作を切り、前記電圧値が設定した前記設定電圧よりも低くなるとメインVR10を動作させるメインボルテージレギュレータ(メインVR)EN動作監視回路74とを有する構成になっている。

【0109】

図4において説明するならば、メインVR動作監視回路74は、ORゲート70との接続関係を有する各部、即ち、ORゲート70、第1のオン・オフ用トランジスタ16、第2のオン・オフ用トランジスタ17、メインVR動作検出回路50、メインVR動作検出回路50と第1のオペアンプ11の出力端子12とを接続する配線、シャントVR動作検出回路60、シャントVR動作検出回路60と第2のオペアンプ31の出力端子32とを接続する配線によって構成される。

【0110】

図1の回路において用いるトランジスタは、各箇所でPMOS,NMOSのいずれでもよい。メインVRの第1の出力トランジスタ14とシャントVRの第2の出力トランジスタ33のPMOSとNMOSのタイプが図4と異なる場合、オペアンプの反転入力端子と非反転入力端子が逆転する。同様にメインVR動作検出回路のトランジスタ51とシャントVR動作検出回路のトランジスタ62のPMOSとNMOSタイプが逆転する。しかし、メインVR10の第1の出力トランジスタ14をPMOSとし、シャントVR30Aの第2の出力トランジスタ33をNMOSとすることは、以下の点でメリットがある。即ち、PMOSとNMOSでは電源とグランドに対するゲート・ドレイン間電圧のかかり方が異なり、出力する電圧と電源電圧の電圧差が少なくて済む方がトランジスタサイズの低減につながり、また効率良く出力できる電圧範囲が広がる。

【0111】

つぎに、実施例によればつぎのような効果を有する。

(1)対象機器が動作する高負荷のときは、メインボルテージレギュレータ10が動作して対象機器に電力(第1の設定電圧3.0Vで出力電流100mA)を供給する。対象機器が動作しなくなると負荷が減少し、電流源34を流れる電流の電流値が電流源設定電流以下になると電流源34によって電圧が上昇する。電圧が上昇して第1の設定電圧(3.0V)よりも高い切替電圧(3.1V)に到達すると、ORゲート70によってメインボルテージレギュレータ10をオフし電力供給を停止する。このときシャントボルテージレギュレータ30Aによってメインボルテージレギュレータ10よりも高い出力の電圧(3.1Vで負荷電流5μA以下)が負荷に供給される。負荷電流がゼロの場合、電流源34の電流5μAとシャントボルテージレギュレータ30Aの5μAを加算した10μAが回路消費電流となる。また、電流値が切替電圧(3.1V)よりも低くなると、ORゲート70によってメインボルテージレギュレータ10はオンし、再び電力(第1の設定電圧3.0Vで出力電流100mA)を対象機器に供給するようになる。この場合、メインボルテージレギュレータ10の回路消費電流が100μAとシャントボルテージレギュレータ30Aの消費電流5μAを加算した105μAが回路消費電流である。この結果、対象機器が動作しないときは消費電流の低減が図れる。

【0112】

(2)特定の消費電流に設定したボルテージレギュレータの設計は、電流可変型より回路規模が小さく設計が容易である。複数の消費電流ボルテージレギュレータを組み合わせた場合、従来は切り替え信号を外部から入れる必要性があった。しかし、実施例2の電源供給回路1Aの場合、消費電流が異なるボルテージレギュレータ(メインボルテージレギュレータ10及びシャントボルテージレギュレータ30A)の切り替えを、消費電流の検出結果に基づいて自発的に実施するので、外部制御(EN)の必要がなくなる。また、実施例2では切り替えは消費電流の検出結果に基づいて瞬時に行われる構成、換言するならば、メインボルテージレギュレータ出力電流に感応した制御であることから消費電流の最小化が可能になるという効果がある。

【0113】

(3)実施例2の電源供給回路1Aにおいては、低消費時のシャントボルテージレギュレータ30Aの電圧(第2の設定電圧)をメインボルテージレギュレータ10の電圧(第1の設定電圧)よりも、若干高く(例えば、0.1V高く)してあるので、急激な負荷変動に対する電圧降下の影響を小さくできる。

【0114】

(4)実施例2の電源供給回路1Aは、要素回路が比較的単純であるので製品の小型化が可能である。

(5)実施例2の電源供給回路1AではEN制御が不要となる利点がある。

【0115】

以上本発明者によってなされた発明を実施例に基づき具体的に説明したが、本発明は上記実施例に限定されるものではなく、その要旨を逸脱しない範囲で種々変更可能であることはいうまでもない。実施例2において、電圧切替回路75を電流源34に代えて抵抗等の電流を流す機能であっても、前記実施例2同様の効果がある。この場合、抵抗等による電流は、例えば、電源電圧5.0Vで切り替え電流が5μAの場合1MΩの抵抗を用いれば良い。

【0116】

なお、本発明を機器が未使用で待機している場合に負荷電流が自ずと減少する論理回路やそれらを内蔵した携帯機器等の電源として適用した場合、自発的に電源回路電流を削減することができ、待機時電流低減が可能である。

【図面の簡単な説明】

【0117】

【図1】本発明の実施例1である電源供給回路を示す回路図である。

【図2】実施例1の電源供給回路の機能を示すブロック図である。

【図3】実施例1の電源供給回路の動作を示す動作表である。

【図4】本発明の実施例2である電源供給回路を示す回路図である。

【図5】実施例2の電源供給回路の機能を示すブロック図である。

【図6】実施例2の電源供給回路の動作を示す動作表である。

【符号の説明】

【0118】

1,1A…電源供給回路、10…メインボルテージレギュレータ(メインVR)、11…第1のオペアンプ、12…出力端子、14…第1の出力トランジスタ、15…電源、16…第1のオン・オフ用トランジスタ、17…第2のオン・オフ用トランジスタ、30…低消費ボルテージレギュレータ(低消費VR)、30A…シャントボルテージレギュレータ(シャントVR)、31…第2のオペアンプ、32…出力端子、33…第2の出力トランジスタ、34…電流源、40…低消費ボルテージレギュレータ動作検出回路(低消費VR動作検出回路)、41…電流源、42…トランジスタ、43…インバーター回路、50…メインボルテージレギュレータ動作検出回路(メインVR動作検出回路)、51…トランジスタ、52…電流源、60…シャントボルテージレギュレータ動作検出回路(シャントVR動作検出回路)、61…電流源、62…トランジスタ、70…ORゲート、74…メインVR動作監視回路、75…電圧切替回路。

【特許請求の範囲】

【請求項1】

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの前記出力端子と第1基準電圧端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第2の端子から前記第1の設定電圧よりも高い第2の設定電圧を出力する低消費ボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の出力トランジスタを最大に駆動する電位であるかを検出する低消費ボルテージレギュレータ動作検出回路を有し、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第2の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続されるとともに、対象機器の負荷に接続される端子となり、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの反転入力端子は基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と前記第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオペアンプの非反転入力端子が接続され、

前記メインボルテージレギュレータの出力電力に比較して前記低消費ボルテージレギュレータの出力電力が小さく構成されていることを特徴とする電源供給回路。

【請求項2】

前記低消費ボルテージレギュレータ動作検出回路の前記トランジスタはPMOSトランジスタで形成され、前記トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、前記トランジスタの前記第2の端子は前記電流源に接続され、前記トランジスタの前記第2の端子の信号を反転していることを特徴とする請求項1に記載の電源供給回路。

【請求項3】

前記メインボルテージレギュレータの出力できる電流より、前記低消費ボルテージレギュレータの出力できる電流が小さく構成され、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子と前記第1基準電圧端子間に接続された前記電流源により、前記第2の出力トランジスタの前記第2の端子からは、前記電流源設定電流値以上の電流を出力することがなく、前記電流源設定電流値を超えた負荷に対し前記第2の出力トランジスタの前記第2の端子の出力電圧が前記第2の設定電圧よりも降下するように構成され、

前記第2の出力トランジスタからの出力は、前記第2の出力トランジスタの前記第2の端子が前記第1の出力トランジスタの前記第2の端子に接続されることで、前記低消費ボルテージレギュレータの前記電流源設定電流値を超えた負荷電流を、前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子から供給することで前記メインボルテージレギュレータの前記第1の設定電圧を出力し、

前記第2の出力トランジスタの出力電圧は、前記低消費ボルテージレギュレータの前記電流源設定電流値以下の負荷電流に対しては、前記低消費ボルテージレギュレータの前記第2の設定電圧になり、前記電流源設定電流値以上の負荷電流に対しては、前記メインボルテージレギュレータの前記第1の設定電圧以上で前記低消費ボルテージレギュレータの前記第2の設定電圧未満になるように構成されていることを特徴とする請求項1に記載の電源供給回路。

【請求項4】

前記対象機器の負荷が減少し前記低消費ボルテージレギュレータの前記第2の出力トランジスタを流れる電流が前記電流源設定電流値未満になると前記低消費ボルテージレギュレータの前記第2の設定電圧を上昇させて出力電圧は前記メインボルテージレギュレータの前記第1の設定電圧よりも高い切替電圧にするように構成され、

前記低消費ボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタを負荷電流の減少に応じ電位が上がり、前記低消費ボルテージレギュレータ動作検出回路の出力は前記メインボルテージレギュレータをオフし、負荷電流が前記低消費ボルテージレギュレータの前記定電流源設定電流値以上の場合、前記第2のオペアンプの出力電位が下がり、前記低消費ボルテージレギュレータ動作検出回路は前記メインボルテージレギュレータをオンすることを特徴とする請求項1に記載の電源供給回路。

【請求項5】

前記メインボルテージレギュレータは前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給し、

前記低消費ボルテージレギュレータは前記対象機器が動作しないとき前記対象機器の前記負荷に前記メインボルテージレギュレータの供給電力よりも少ない電力を供給し、

前記低消費ボルテージレギュレータ動作検出回路は、前記第2のオペアンプが前記第2の出力トランジスタに対し最大電流を出力する電位より小さくなったとき前記メインボルテージレギュレータの動作を切り、前記負荷の電流の増大によって前記第2の出力トランジスタが最大電流を出力できる電位のとき前記メインボルテージレギュレータを動作させる構成になっていることを特徴とする請求項1に記載の電源供給回路。

【請求項6】

前記メインボルテージレギュレータは出力負荷過渡特性と、電源リップル除去特性が前記低消費ボルテージレギュレータより良好な特性となるように構成され、

前記負荷の電流が前記電流源設定電流値以上のときは前記メインボルテージレギュレータを動作させ、

前記負荷電流が前記電流源設定電流値未満の場合は前記メインボルテージレギュレータを停止させることを特徴とする請求項1に記載の電源供給回路。

【請求項7】

前記電流源設定電流値は200μAであることを特徴とする請求項6に記載の電源供給回路。

【請求項8】

前記負荷の電流が前記電流源設定電流値以上の場合は前記メインボルテージレギュレータは前記第1の設定電圧を出力し、

前記負荷の電流が前記電流源設定電流値未満の場合は前記メインボルテージレギュレータは停止し、前記低消費ボルテージレギュレータの前記第2の設定電圧を出力し、

前記メインボルテージレギュレータの前記第1の設定電圧より、前記低消費ボルテージレギュレータの前記第2の設定電圧が高くなっていることを特徴とする請求項1に記載の電源供給回路。

【請求項9】

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの出力端子と第1基準電圧端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの前記第1の端子から前記第1の設定電圧よりも高い第2の設定電圧を出力するシャントボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第1のオペアンプの前記出力端子に接続され、前記第1のオペアンプの出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路と、

前記第1基準電圧端子と前記第2基準電圧端子との間に電流源及びトランジスタが直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路と、

前記メインボルテージレギュレータ動作検出回路及び前記シャントボルテージレギュレータ動作検出回路の検出出力を入力し、前記第1のオン・オフ用トランジスタ及び前記第2のオン・オフ用トランジスタのそれぞれの制御端子に出力するORゲートとを有し、

前記シャントボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続され、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの非反転入力端子は基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオン・オフの反転入力端子が接続され、

前記メインボルテージレギュレータの出力電力に比較して前記シャントボルテージレギュレータの出力電力が小さく構成されていることを特徴とする電源供給回路。

【請求項10】

前記メインボルテージレギュレータ動作検出回路の前記トランジスタはPMOSトランジスタで形成され、前記第1の端子は前記第1基準電圧端子に接続され、

前記シャントボルテージレギュレータ動作検出回路の前記トランジスタはNMOSトランジスタで形成され、前記第1の端子は前記電流源に接続されていることを特徴とする請求項9に記載の電源供給回路。

【請求項11】

前記対象機器の負荷が減少し前記シャントボルテージレギュレータの前記電流源を流れる電流の電流値が電流源電流以下になると前記電流源は電圧を上昇させて前記第1の設定電圧よりも高い切替電圧にするように構成され、

前記切替電圧に到達した状態では、前記メインボルテージレギュレータの前記第1のオペアンプの出力電圧は前記第1の出力トランジスタをオンしない状態となり、前記シャントボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタをオンする状態となり、前記ORゲートは前記メインボルテージレギュレータをオフし、

前記切替電圧よりも低くなった状態では、前記シャントボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタをオフする状態となり、前記ORゲートは前記メインボルテージレギュレータをオンすることを特徴とする請求項9に記載の電源供給回路。

【請求項12】

前記第1の設定電圧はaVであり、前記切替電圧は(a+b)Vであることを特徴とする請求項11に記載の電源供給回路。

【請求項13】

対象機器の負荷に電力を供給する電源供給回路であり、

前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給するメインボルテージレギュレータと、

前記メインボルテージレギュレータに接続され前記対象機器が動作しないとき、もしくは設定した前記負荷電流以下のとき前記対象機器の前記負荷に前記メインボルテージレギュレータの供給電力よりも少ない電力を供給するシャントボルテージレギュレータと、

前記負荷に供給される電圧値を検出し、前記電圧値が設定した前記第2の設定電圧に到達したとき前記メインボルテージレギュレータの動作を切り、前記電圧値が設定した前記第2の設定電圧よりも低くなると前記メインボルテージレギュレータを動作させるメインボルテージレギュレータ動作検出回路とを有することを特徴とする電源供給回路。

【請求項1】

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの前記出力端子と第1基準電圧端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの第2の端子から前記第1の設定電圧よりも高い第2の設定電圧を出力する低消費ボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の出力トランジスタを最大に駆動する電位であるかを検出する低消費ボルテージレギュレータ動作検出回路を有し、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第2の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続されるとともに、対象機器の負荷に接続される端子となり、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの反転入力端子は基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と前記第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオペアンプの非反転入力端子が接続され、

前記メインボルテージレギュレータの出力電力に比較して前記低消費ボルテージレギュレータの出力電力が小さく構成されていることを特徴とする電源供給回路。

【請求項2】

前記低消費ボルテージレギュレータ動作検出回路の前記トランジスタはPMOSトランジスタで形成され、前記トランジスタの前記第1の端子は前記第1基準電圧端子に接続され、前記トランジスタの前記第2の端子は前記電流源に接続され、前記トランジスタの前記第2の端子の信号を反転していることを特徴とする請求項1に記載の電源供給回路。

【請求項3】

前記メインボルテージレギュレータの出力できる電流より、前記低消費ボルテージレギュレータの出力できる電流が小さく構成され、

前記低消費ボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子と前記第1基準電圧端子間に接続された前記電流源により、前記第2の出力トランジスタの前記第2の端子からは、前記電流源設定電流値以上の電流を出力することがなく、前記電流源設定電流値を超えた負荷に対し前記第2の出力トランジスタの前記第2の端子の出力電圧が前記第2の設定電圧よりも降下するように構成され、

前記第2の出力トランジスタからの出力は、前記第2の出力トランジスタの前記第2の端子が前記第1の出力トランジスタの前記第2の端子に接続されることで、前記低消費ボルテージレギュレータの前記電流源設定電流値を超えた負荷電流を、前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子から供給することで前記メインボルテージレギュレータの前記第1の設定電圧を出力し、

前記第2の出力トランジスタの出力電圧は、前記低消費ボルテージレギュレータの前記電流源設定電流値以下の負荷電流に対しては、前記低消費ボルテージレギュレータの前記第2の設定電圧になり、前記電流源設定電流値以上の負荷電流に対しては、前記メインボルテージレギュレータの前記第1の設定電圧以上で前記低消費ボルテージレギュレータの前記第2の設定電圧未満になるように構成されていることを特徴とする請求項1に記載の電源供給回路。

【請求項4】

前記対象機器の負荷が減少し前記低消費ボルテージレギュレータの前記第2の出力トランジスタを流れる電流が前記電流源設定電流値未満になると前記低消費ボルテージレギュレータの前記第2の設定電圧を上昇させて出力電圧は前記メインボルテージレギュレータの前記第1の設定電圧よりも高い切替電圧にするように構成され、

前記低消費ボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタを負荷電流の減少に応じ電位が上がり、前記低消費ボルテージレギュレータ動作検出回路の出力は前記メインボルテージレギュレータをオフし、負荷電流が前記低消費ボルテージレギュレータの前記定電流源設定電流値以上の場合、前記第2のオペアンプの出力電位が下がり、前記低消費ボルテージレギュレータ動作検出回路は前記メインボルテージレギュレータをオンすることを特徴とする請求項1に記載の電源供給回路。

【請求項5】

前記メインボルテージレギュレータは前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給し、

前記低消費ボルテージレギュレータは前記対象機器が動作しないとき前記対象機器の前記負荷に前記メインボルテージレギュレータの供給電力よりも少ない電力を供給し、

前記低消費ボルテージレギュレータ動作検出回路は、前記第2のオペアンプが前記第2の出力トランジスタに対し最大電流を出力する電位より小さくなったとき前記メインボルテージレギュレータの動作を切り、前記負荷の電流の増大によって前記第2の出力トランジスタが最大電流を出力できる電位のとき前記メインボルテージレギュレータを動作させる構成になっていることを特徴とする請求項1に記載の電源供給回路。

【請求項6】

前記メインボルテージレギュレータは出力負荷過渡特性と、電源リップル除去特性が前記低消費ボルテージレギュレータより良好な特性となるように構成され、

前記負荷の電流が前記電流源設定電流値以上のときは前記メインボルテージレギュレータを動作させ、

前記負荷電流が前記電流源設定電流値未満の場合は前記メインボルテージレギュレータを停止させることを特徴とする請求項1に記載の電源供給回路。

【請求項7】

前記電流源設定電流値は200μAであることを特徴とする請求項6に記載の電源供給回路。

【請求項8】

前記負荷の電流が前記電流源設定電流値以上の場合は前記メインボルテージレギュレータは前記第1の設定電圧を出力し、

前記負荷の電流が前記電流源設定電流値未満の場合は前記メインボルテージレギュレータは停止し、前記低消費ボルテージレギュレータの前記第2の設定電圧を出力し、

前記メインボルテージレギュレータの前記第1の設定電圧より、前記低消費ボルテージレギュレータの前記第2の設定電圧が高くなっていることを特徴とする請求項1に記載の電源供給回路。

【請求項9】

第1のオペアンプと、前記第1のオペアンプの出力端子に制御端子を介して接続される第1の出力トランジスタと、前記第1のオペアンプの出力端子と第1基準電圧端子間に接続される第1のオン・オフ用トランジスタと、前記第1のオペアンプの負の電源端子と第2基準電圧端子との間に接続される第2のオン・オフ用トランジスタとを有し、前記第1の出力トランジスタの第2の端子から第1の設定電圧を出力するメインボルテージレギュレータと、

第2のオペアンプと、前記第2のオペアンプの出力端子に制御端子を介して接続される第2の出力トランジスタと、前記第2の出力トランジスタの第1の端子と前記第1基準電圧端子間に接続される電流源とを有し、前記第2の出力トランジスタの前記第1の端子から前記第1の設定電圧よりも高い第2の設定電圧を出力するシャントボルテージレギュレータと、

前記第1基準電圧端子と前記第2基準電圧端子との間にトランジスタ及び電流源が直列に接続され、前記トランジスタの制御端子が前記第1のオペアンプの前記出力端子に接続され、前記第1のオペアンプの出力が前記第1の設定電圧以上か未満かを検出するメインボルテージレギュレータ動作検出回路と、

前記第1基準電圧端子と前記第2基準電圧端子との間に電流源及びトランジスタが直列に接続され、前記トランジスタの制御端子が前記第2のオペアンプの前記出力端子に接続され、前記第2のオペアンプの出力が前記第2の設定電圧以上か未満かを検出するシャントボルテージレギュレータ動作検出回路と、

前記メインボルテージレギュレータ動作検出回路及び前記シャントボルテージレギュレータ動作検出回路の検出出力を入力し、前記第1のオン・オフ用トランジスタ及び前記第2のオン・オフ用トランジスタのそれぞれの制御端子に出力するORゲートとを有し、

前記シャントボルテージレギュレータの前記第2の出力トランジスタの前記第1の端子は前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子に接続され、

前記第1のオペアンプの反転入力端子及び前記第2のオペアンプの非反転入力端子は基準電位が印加される端子に接続され、

前記メインボルテージレギュレータの前記第1の出力トランジスタの前記第2の端子と第2基準電圧端子との間には直列に3個の抵抗Ra,Rb,Rcが接続され、前記抵抗Raと抵抗Rbとの間のノードと前記第1のオペアンプの非反転入力端子が接続され、前記抵抗Rbと抵抗Rcとの間のノードと前記第2のオン・オフの反転入力端子が接続され、

前記メインボルテージレギュレータの出力電力に比較して前記シャントボルテージレギュレータの出力電力が小さく構成されていることを特徴とする電源供給回路。

【請求項10】

前記メインボルテージレギュレータ動作検出回路の前記トランジスタはPMOSトランジスタで形成され、前記第1の端子は前記第1基準電圧端子に接続され、

前記シャントボルテージレギュレータ動作検出回路の前記トランジスタはNMOSトランジスタで形成され、前記第1の端子は前記電流源に接続されていることを特徴とする請求項9に記載の電源供給回路。

【請求項11】

前記対象機器の負荷が減少し前記シャントボルテージレギュレータの前記電流源を流れる電流の電流値が電流源電流以下になると前記電流源は電圧を上昇させて前記第1の設定電圧よりも高い切替電圧にするように構成され、

前記切替電圧に到達した状態では、前記メインボルテージレギュレータの前記第1のオペアンプの出力電圧は前記第1の出力トランジスタをオンしない状態となり、前記シャントボルテージレギュレータの前記第2のオペアンプの出力電圧は前記第2の出力トランジスタをオンする状態となり、前記ORゲートは前記メインボルテージレギュレータをオフし、

前記切替電圧よりも低くなった状態では、前記シャントボルテージレギュレータの前記第2のオペアンプの出力は前記第2の出力トランジスタをオフする状態となり、前記ORゲートは前記メインボルテージレギュレータをオンすることを特徴とする請求項9に記載の電源供給回路。

【請求項12】

前記第1の設定電圧はaVであり、前記切替電圧は(a+b)Vであることを特徴とする請求項11に記載の電源供給回路。

【請求項13】

対象機器の負荷に電力を供給する電源供給回路であり、

前記対象機器が動作するとき前記対象機器の前記負荷に電力を供給するメインボルテージレギュレータと、

前記メインボルテージレギュレータに接続され前記対象機器が動作しないとき、もしくは設定した前記負荷電流以下のとき前記対象機器の前記負荷に前記メインボルテージレギュレータの供給電力よりも少ない電力を供給するシャントボルテージレギュレータと、

前記負荷に供給される電圧値を検出し、前記電圧値が設定した前記第2の設定電圧に到達したとき前記メインボルテージレギュレータの動作を切り、前記電圧値が設定した前記第2の設定電圧よりも低くなると前記メインボルテージレギュレータを動作させるメインボルテージレギュレータ動作検出回路とを有することを特徴とする電源供給回路。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図2】

【図3】

【図4】

【図5】

【図6】

【公開番号】特開2007−233807(P2007−233807A)

【公開日】平成19年9月13日(2007.9.13)

【国際特許分類】

【出願番号】特願2006−56043(P2006−56043)

【出願日】平成18年3月2日(2006.3.2)

【出願人】(000100997)株式会社アキタ電子システムズ (41)

【Fターム(参考)】

【公開日】平成19年9月13日(2007.9.13)

【国際特許分類】

【出願日】平成18年3月2日(2006.3.2)

【出願人】(000100997)株式会社アキタ電子システムズ (41)

【Fターム(参考)】

[ Back to top ]