電源回路

【課題】 広帯域無線通信を行う送信機に用いられ、電源変換効率を向上させると共に、電圧レベル切替の遷移時間の影響を低減し、出力信号の歪特性を改善することができる電源回路を提供する。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

【解決手段】 入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力するスイッチ制御部83′と、入力信号を特定の時間遅延させるタイミング制御部121を備え、スイッチ制御部83′が、制御信号の立ち上げの場合に、タイミング制御部121での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、立ち下げの場合には遅延時間のタイミングで立ち下げる電源回路としている。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、広帯域の高周波信号で無線通信を行う送信機の電力増幅器で用いられる電源回路に係り、特に、電力変換効率を向上させることができる電源回路に関する。

【背景技術】

【0002】

[先行技術の説明]

送信機の電力増幅器への要求として、設置場所の制約や据付コストの低減のために、小型・軽量化が強く求められている。装置の体積・重量は、電力損失によって発生する熱を放熱するための放熱フィンが多くを占めるが、電力効率を改善することで放熱フィンを小さくすることが可能になり、小型・軽量化に寄与する。

【0003】

[電力効率を改善する電力増幅器:図12]

電力効率を改善する方法として、電力増幅器に入力される信号の電圧振幅に応じて、電力増幅器に印加する電源電圧を制御するET(Envelop Tracking)方式や、飽和型の電力増幅器の電源電圧を変動させるEER(Envelop Elimination and Restoration)方式がある。

【0004】

ET方式及びEER方式の電力増幅器について図12を用いて説明する。図12(a)はET方式の電力増幅器を示す概略構成図であり、(b)はEER方式の電力増幅器を示す概略構成図である。

[ET方式の電力増幅器:図12(a)]

図12(a)に示すように、ET方式の電力増幅器は、入力端子1と、分配器2と、包絡線検波器3と、電源回路4と、主増幅器6と、出力端子7とを備えている。

具体的には、入力端子1と、分配器2と、主増幅器6と、出力端子7が直列に接続されており、分配器2には包絡線検波器3が接続され、包絡線検波器3には電源回路4が接続され、電源回路4は主増幅器6に接続されて電源を供給する構成となっている。

【0005】

ET方式では、入力端子1から入力されたRF信号を分配器2で分配し、一方を包絡線検波器3に入力して包絡線を抽出し、電源回路4に入力する。電源回路4は主増幅器6に印加する電源電圧を主増幅器6の出力における包絡線と同等または僅かに大きい電圧で変動させる。

したがって、主増幅器6に印加される電源電圧と、出力信号振幅の差が小さく抑えられることになり、主増幅器6は電力ロスが小さい領域で動作することが可能となるものである。

【0006】

[EER方式の電力増幅器:図12(b)]

図12(b)に示すように、EER方式の電力増幅器は、入力端子1と、分配器2と、包絡線検波器3と、電源回路4と、RFリミット増幅器5と、主増幅器6と、出力端子7とを備えている。

つまり、分配器2と主増幅器6との間にRFリミット増幅器5が設けられて主増幅器6への入力電圧を制限している点が(a)に示したET方式の電力増幅器とは異なっている。

【0007】

そして、上記構成のEER方式の電力増幅器では、入力端子1から入力されたRF信号は、分配器2で分配され、一方は包絡線検波器3で検波されて包絡線信号が電源回路4に入力される。そして、電源回路4は、主増幅器6の電源電圧を包絡線信号に従って変動させる。

分配器2で分配された他方のRF信号は、RFリミット増幅器5で振幅変動分が除去され、位相情報のみを保ちながら主増幅器6で増幅される。

主増幅器6の電源電圧は、包絡線検波器3からの振幅情報に従って変動するので、振幅情報は復元され、主増幅器6は常に飽和状態で動作するため高効率となる。

【0008】

[高速動作可能な電源回路:図13]

ところで、ET方式やEER方式の電力増幅器全体における効率を考えた場合、主増幅器6だけでなく、電源回路4の効率も重要になってくる。

W−CDMA(Wideband-Code Division Multiple Access)信号やOFDM(Orthogonal Frequency Division Multiplexing)信号のような広帯域信号の包絡線信号の帯域は広く、電源回路4は高速に動作する必要がある。

【0009】

高速に動作する電源回路としては、例えば、非特許文献1や非特許文献2に記載されている(非特許文献1,2参照)。

高速に動作する電源回路には、線形増幅回路としてプッシュプル増幅器を使用し、DC/DCコンバータとしてD級回路を使用したものがある。

このような電源回路の構成例について図13を用いて説明する。図13は、高速に動作する電源回路の例を示す構成図である。

【0010】

図13に示すように、高速に動作する電源回路(高速動作用電源回路)は、主として、入力端子8と、広帯域の電圧源であるプッシュプル増幅器12と、制御回路である電流検出器25及びヒステリシスコンパレータ26と、高効率なDC/DCコンバータ11と、出力端子9とから構成されている。

尚、プッシュプル増幅器12は、請求項に記載したプッシュプル増幅部に相当する。

【0011】

そして、入力端子8は、図12に示した包絡線検波器3の出力段に接続され、出力端子9は、図12に示した主増幅器6の電源端子に接続される。

電流検出器25は、例えば抵抗から構成される。

また、DC/DCコンバータ11は、電圧電源と、スイッチ素子13と、ダイオード14と、インダクタンス15とを備えている。

プッシュプル増幅器12については後述する。

【0012】

[DC/DCコンバータ11の動作]

DC/DCコンバータ11の動作について簡単に説明する。

包絡線検波器3の出力がDC成分の場合、DC/DCコンバータ11は、追従モードで動作して、スイッチ素子13を自励周波数で周期的にオン/オフする。

また、包絡線検波器3の出力がDC成分と高い周波数のAC成分になると、DC/DCコンバータ11は、非追従モードで動作し、AC高周波成分を基本とする周波数でスイッチ素子13をオン/オフする。このとき、DC/DCコンバータ11は、DC成分のみを出力し、高い周波数のAC成分はプッシュプル増幅器12から出力される。

【0013】

[電源回路の効率]

図13に示した高速動作用電源回路では、自励周波数を高くして追従できるAC成分を増やすことで、つまり、高効率なDC/DCコンバータ11から出力するエネルギーの割合を増やすことで、電源回路の高効率化を試みることが考えられる。

しかし、WiMAX(Worldwide Interoperability for Microwave Access)やLTE(Long Term Evolution)などの広帯域な通信システムでは、包絡線も広帯域になるため、DC/DCコンバータ11のスイッチング周波数を上げると、スイッチング損失が大きくなり、電源回路の効率は低下する。

【0014】

そこで、適切な回路定数を設定することにより、WiMAXやLTE等の広帯域な通信システムでは、周波数の低いAC成分は、効率の高いDC/DCコンバータ11から供給し、周波数の高いAC成分は、プッシュプル増幅器12から供給するようにしている。

【0015】

[電源回路の大電流への対応]

ところで、主増幅器6の出力電力が大きい場合には、電源回路4からも多くの電流を供給する必要がある。

図13の高速動作用電源回路において、DC/DCコンバータ11では、スイッチ素子13、ダイオード14、インダクタンス15として、必要な電流を流せる部品を選択すればよい。

しかしながら、プッシュプル増幅器12に用いられるオペアンプについては、一般的に大電流を流せる部品はない。そこで、オペアンプの出力にNPNトランジスタとPNPトランジスタを接続して、出力できる電流の容量を増やしている。

【0016】

[プッシュプル増幅器の構成:図13]

次に、従来の高速動作用電源回路におけるプッシュプル増幅器(従来のプッシュプル増幅器)の構成について図13を用いて説明する。

図13に示すように、従来のプッシュプル増幅器12は、オペアンプ16と、バイアス回路を構成する抵抗器19、ダイオード20、ダイオード21、抵抗器22と、プッシュプル回路のNPNトランジスタ17、PNPトランジスタ18と、直流電圧源23と、直流電圧源24とで構成されている。

【0017】

そして、上記構成のプッシュプル増幅器12において、入力信号は入力端子8を通ってオペアンプ16の+端子に入力され、オペアンプの−端子へは出力信号がフィードバックされる。

ダイオード20は、NPNトランジスタ17のベース−間の電圧降下を、ダイオード21はPNPトランジスタ18のベース−エミッタ間の電圧降下を補償するためのものであり、抵抗器19、抵抗器22と共にバイアス回路を構成する。

【0018】

直流電圧源24よりも高い電圧値に設定される直流電圧源23に接続されたNPNトランジスタ17と、直流電圧源23よりも低い電圧値に設定される直流電圧源24に接続されたPNPトランジスタ18はプッシュプル動作により増幅を行う。

そして、NPNトランジスタ17は基準電圧よりも高い電圧を出力し、PNPトランジスタ18は基準電圧よりも低い電圧を出力する。

【0019】

NPNトランジスタ17及びPNPトランジスタ18の出力波形は、正弦波を半波整流した波形となり、これはB級にバイアスされた増幅器に相当する。プッシュプル増幅器12の出力波形は、NPNトランジスタ17の出力波形とPNPトランジスタ18の出力波形とを合成したものとなる。

【0020】

[B級増幅器の電力変換効率:図14]

ここで、B級増幅器の電力変換効率について説明する。

B級増幅器が正弦波を出力するときの電力変換効率ηは、式1で表されることが知られている。

η=π/4×Vomax/Vdd (式1)

式1をNPNトランジスタ17について説明すると、Vddは直流電圧源23の電源電圧であり、Vomaxは、NPNトランジスタ17の出力電圧の最大値である。

【0021】

式1において、VomaxがVddと同じ電圧の場合、つまり飽和出力時の電圧変換効率ηは78.5%となるが、最大出力電圧Vomaxが下がると電力変換効率ηも低下する。

【0022】

図14は、B級増幅器の電力変換効率特性を示す説明図である。

図14では、出力電圧に対する電力変換効率ηを表しており、横軸のバックオフは、Vomax/Vddを対数で表したものである。

バックオフが0dBの点が飽和出力を示しており、このときの電力変換効率ηは、上述したように78.5%となり、バックオフが大きくなると(最大出力電圧Vomaxが低下すると)電力変換効率ηは低下し、バックオフが−8dBの時の電力変換効率ηは、30%となる。

【0023】

[プッシュプル増幅器の電力変換効率:図14]

式1及び図14では、NPNトランジスタ17について説明したが、PNPトランジスタ18についても同様のことが言えるため、プッシュプル増幅器12全体の特性も式1及び図14で表すことができるものである。

尚、プッシュプル増幅器12では、オペアンプ16やバイアス回路も電力を消費するが、NPNトランジスタ17及びPNPトランジスタ18の電流増幅率hfeが大きく、オペアンプ16の消費電力はプッシュプル増幅器12のそれと比較すると僅かであるため、プッシュプル増幅器12の電力変換効率は、図14に示した特性とほぼ一致する。

【0024】

[OFDM信号における包絡線信号のスペクトラムの累積確率密度分布例:図15]

ここで、OFDM信号における包絡線信号の累積確率密度分布について図15を用いて説明する。図15は、OFDM信号における包絡線信号の累積確率密度分布の例を示す説明図である。

図15では、帯域幅10MHz、PAPR(Peak to Average Power Ratio):8dBのOFDM変調信号の包絡線を求め、電力の累積確率密度分布をDCから10MHzまでプロットしている。

【0025】

上述したように、電源回路4は、DC成分と低い周波数成分はDC/DCコンバータ11から供給し、高い周波数成分はプッシュプル増幅器12から供給するが、仮に、3MHz未満をDC/DCコンバータ11から供給し、3MHz以上をプッシュプル増幅器12が供給するとした場合、図15から、電源回路4が供給する電力の内、DC/DCコンバータ11から90%の電力を、プッシュプル増幅器12から10%の電力を供給することになる。

【0026】

[OFDM信号での電源回路の電力変換効率:図14]

OFDM信号での電源回路4の電力変換効率について説明する。

DC成分と低い周波数成分を供給するDC/DCコンバータ11の電力変換効率は、スイッチ素子13のオン抵抗や、スイッチング損失、ダイオードの順方向電圧、インダクタンス14の損失などで決まり、ηdとする。

【0027】

一方、OFDM信号のPAPRは8dBであるから、プッシュプル増幅器12の電力変換効率は、図10からわかるように、バックオフ−8dBのときの電力変換効率となる。ここでは、このときの電力変換効率をηbとする。

【0028】

つまり、電源回路4が主増幅器6に供給する電力の内、10%を電力変換効率ηbのプッシュプル増幅器12から、90%を電力変換効率ηdのDC/DCコンバータ11から供給することになる。よって、電源回路4の電力変換効率ηsは式2で計算できる。

ηs=1/(10%/ηb+90%/ηd) (式2)

仮に、ηb=30%、ηd=90%として計算すると、ηs=75%となる。

電源回路4全体の電力変換効率を改善するためには、電力変換効率の低いプッシュプル増幅器12の効率をあげることが必要である。

【0029】

従来のプッシュプル増幅器12では、NPNトランジスタ17のコレクタ端子及びPNPトランジスタ18のコレクタ端子に接続される直流電圧源23及び直流電圧源24の電圧は、出力レベルに関係なく一定であるため、出力レベルが下がるに従って電力変換効率も低下する。

【先行技術文献】

【非特許文献】

【0030】

【非特許文献1】"An Improved Power-Added Efficiency 19-dBm Hybrid Envelope Elimination and Restoration Power Amplifier for 802.11g WLAN Applications" , Feipeng Wang et al., IEEE TRANSACTIOINS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 54, NO. 12, DECEMBER 2006, P. 4086-4099

【非特許文献2】"A Class B Switch- Mode Assisted Linear Amplifier" , Geoffrey R. Walker, IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 18. No. 6, NOVEMBER 2003, p.1278-1285

【発明の概要】

【発明が解決しようとする課題】

【0031】

しかしながら、従来のプッシュプル増幅器では、NPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧が、出力レベルにかかわらず一定レベルであるため、出力レベルが下がると電力変換効率が低下してしまうという問題点があった。

【0032】

尚、非特許文献1、2には、プッシュプル増幅器のNPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧を、出力レベルに応じて調整することは記載されていない。

【0033】

本発明は、上記実状に鑑みて為されたもので、プッシュプル増幅器のNPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧を、出力レベルに応じて調整して、出力レベルが下がっても電力変換効率が低下しない電源回路を提供することを目的とする。

【課題を解決するための手段】

【0034】

上記従来例の問題点を解決するための本発明は、電力増幅に用いられる電源回路であって、入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、プッシュプル増幅部に入力される入力信号を遅延させるタイミング調整部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力する制御部とを備え、制御部が、制御信号の立ち上げの場合に、タイミング調整部での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げることを特徴としている。

【0035】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち上げ及び立ち下げの電圧レベル切り替えに対応して、タイミング調整部での遅延時間から遷移時間を差し引いた時間をタイミング遅延時間として記憶しており、制御信号の立ち上げの場合に、入力信号のタイミングから前記タイミング遅延時間だけ遅延させたタイミングで前記制御信号を立ち上げることを特徴としている。

【0036】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち上げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち上げの場合に、検出された入力信号と傾きとに基づいて、制御信号を立ち上げるタイミングを算出して、当該算出されたタイミングで制御信号を立ち上げることを特徴としている。

【0037】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち下げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる代わりに、検出された入力信号と傾きとに基づいて、制御信号を立ち下げるタイミングを算出して、算出されたタイミングで制御信号を立ち下げることを特徴としている。

【0038】

また、本発明は、ET方式の電力増幅器であって、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を前記主増幅器に供給することを特徴としている。

【0039】

また、本発明は、EER方式の電力増幅器であって、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器と、入力信号の電圧を制限して主増幅器に出力するリミット増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を主増幅器に供給することを特徴としている。

【発明の効果】

【0040】

本発明によれば、電力増幅に用いられる電源回路であって、入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、プッシュプル増幅部に入力される入力信号を遅延させるタイミング調整部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力する制御部とを備え、制御部が、制御信号の立ち上げの場合に、タイミング調整部での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる電源回路としているので、出力レベルが下がっても電力変換効率を低下させず、電圧レベルの立ち上がりに要する遷移時間の影響を低減し、出力信号の立ち上がり波形に追随した電源電圧を供給でき、効率を向上させると共に増幅部での飽和を防ぎ、出力信号の歪特性を改善することができる効果がある。

【0041】

また、本発明によれば、制御部が、制御信号の立ち上げ及び立ち下げの電圧レベル切り替えに対応して、タイミング調整部での遅延時間から遷移時間を差し引いた時間をタイミング遅延時間として記憶しており、制御信号の立ち上げの場合に、入力信号のタイミングから前記タイミング遅延時間だけ遅延させたタイミングで前記制御信号を立ち上げる上記電源回路としているので、制御信号を、出力信号より遷移時間分早いタイミングで立ち上げる処理を容易に行うことができる効果がある。

【0042】

また、本発明によれば、制御部が、制御信号の立ち上げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち上げの場合に、検出された入力信号と傾きとに基づいて、制御信号を立ち上げるタイミングを算出して、当該算出されたタイミングで制御信号を立ち上げる上記電源回路としているので、実際の信号波形に基づく適切なタイミングで制御信号を立ち上げ、急峻な立ち上がりを含む広帯域信号に対しても電源電圧を追随させ、出力信号の歪特性を改善することができる効果がある。

【0043】

また、本発明によれば、制御部が、制御信号の立ち下げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる代わりに、検出された入力信号と傾きとに基づいて、制御信号を立ち下げるタイミングを算出して、算出されたタイミングで制御信号を立ち下げる上記電源回路としているので、実際の信号波形に基づく適切なタイミングで制御信号を立ち下げ、急峻な立ち下がりを含む広帯域信号に対しても電源電圧を追随させ、出力信号の歪特性を改善することができる効果がある。

【0044】

また、本発明によれば、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を前記主増幅器に供給するET方式の電力増幅器としているので、出力信号の立ち上がり/立ち下がりの波形によく追随した電源電圧を供給でき、電力増幅器全体の効率を向上させると共に出力信号の歪特性を改善することができる効果がある。

【0045】

また、本発明によれば、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器と、入力信号の電圧を制限して主増幅器に出力するリミット増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を主増幅器に供給するEER方式の電力増幅器としているので、出力信号の立ち上がり/立ち下がりの波形によく追随した電源電圧を供給でき、電力増幅器全体の効率を向上させると共に出力信号の歪特性を改善することができる効果がある。

【図面の簡単な説明】

【0046】

【図1】本発明の第1の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

【図2】第1のプッシュプル増幅器におけるスイッチ制御信号の一例と、それに伴うトランジスタのコレクタ電圧及び出力波形を示す説明図である。

【図3】第1のプッシュプル増幅器の電力変換効率特性を示す説明図である。

【図4】NPNトランジスタ17のコレクタ端子に直流電圧を供給する直流電圧源回路の構成例を示すブロック図である。

【図5】遷移時間がない場合の出力信号波形とコレクタ端子の電位との関係を示す説明図である。

【図6】NPNトランジスタ17のコレクタ電圧の遷移時間を示す説明図である。

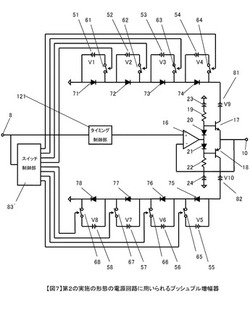

【図7】本発明の第2の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

【図8】第2のプッシュプル増幅器におけるスイッチ制御信号の制御タイミングを示す説明図である。

【図9】第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係を示す説明図である。

【図10】コレクタ電圧の遷移状態における傾きを直線近似する場合の説明図である。

【図11】第2の電源回路に用いられる別のプッシュプル増幅器の構成を示す説明図である。

【図12】(a)はET方式の電力増幅器を示す概略構成図であり、(b)はEER方式の電力増幅器を示す概略構成図である。

【図13】高速に動作する電源回路の例を示す構成図である。

【図14】B級増幅器の電力変換効率特性を示す説明図である。

【図15】OFDM信号における包絡線信号の累積確率密度分布の例を示す説明図である。

【図16】スイッチ制御信号C1の立ち上げタイミングの算出方法を示す説明図である。

【図17】スイッチ制御信号C1の立ち下げタイミングの算出方法を示す説明図である。

【発明を実施するための形態】

【0047】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る電源回路は、プッシュプル増幅器に、スイッチと直流電圧源が直列に接続され、更にそれらに並列にダイオードが接続された回路部を1つの回路ブロックとして、複数の回路ブロックが直列に接続された第1と第2の電源電圧生成回路を備え、当該第1と第2の電源電圧生成回路が、それぞれNPNトランジスタのコレクタ端子及びPNPトランジスタのコレクタ端子に接続され、スイッチ制御部が、入力信号レベルに応じて、複数のブロックの直流電圧源をNPNトランジスタ又はPNPトランジスタのコレクタ端子に接続するスイッチのオン/オフを制御する制御信号を出力して、NPNトランジスタ及びPNPトランジスタのコレクタ電圧を入力信号レベルに応じて制御して、出力レベルに追従したコレクタ電圧とすることができ、出力レベルが低い場合でも飽和に近い動作を可能とし、電源回路全体の電力変換効率を改善することができるものである。

【0048】

また、本発明の実施の形態に係る電源回路は、上記電源回路において、更に、タイミング調整部を設け、タイミング調整部が入力信号を一定時間遅延すると共に、スイッチ制御部が、各スイッチのオン/オフを制御する制御信号の切り替え時には、当該遅延時間よりもコレクタ電圧の電圧レベルに応じたレベル切り替えの遷移時間分早く制御信号の立ち上げを行うようにしているので、コレクタ電圧のレベル切り替わりに要する遷移時間の影響を低減し、電源回路の出力波形の歪を改善することができるものである。

【0049】

また、本発明の実施の形態に係る電源回路は、上記電源回路において、スイッチ制御部が、予め記憶しているコレクタ電圧の電圧レベルに応じたレベル切替の傾きと、検出された入力信号レベルとに基づいて、制御信号の立ち上げ又は立ち下げのタイミングを算出し、当該タイミングで制御信号を立ち上げ又は立ち下げるようにしているので、実際の信号波形に基づいて制御信号の出力タイミングを決定することができ、電源回路の出力波形の歪を改善することができるものである。

【0050】

[第1の実施の形態:図1]

本発明の第1の実施の形態に係る電源回路は、図13に示した従来の電源回路と同様に、プッシュプル増幅器とDC/DCコンバータとを備えている。

本発明の第1の実施の形態に係る電源回路について図1を用いて説明する。図1は、本発明の第1の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

図1に示すように、本発明の第1の実施の形態に係る電源回路(第1の電源回路)に用いられるプッシュプル増幅器(第1のプッシュプル増幅器)は、図13に示した従来のプッシュプル増幅器と同様の部分として、入力端子8と、出力端子10と、オペアンプ16と、バイアス回路を構成する抵抗器19と、ダイオード20と、ダイオード21と、抵抗器22と、プッシュプル回路を構成するNPNトランジスタ17と、PNPトランジスタ18と、直流電圧源23と、直流電圧源24とを備えている。従来のプッシュプル増幅器と同様の構成部分は、請求項に記載したプッシュプル増幅部に相当する。

【0051】

そして、第1のプッシュプル増幅器の特徴部分として、スイッチ制御部83と、NPNトランジスタ17のコレクタに接続する直流電圧源81及び複数の回路ブロックB1〜B4と、PNPトランジスタ18のコレクタに接続する直流電圧源82及び複数の回路ブロックB5〜B8とを備えている。

直流電圧源81,82の電圧をそれぞれV9,V10とする。

直流電圧源81及び複数の回路ブロックB1〜B4と、直流電圧源82及び複数の回路ブロックB5〜B8は請求項に記載した可変電源部に相当する。

【0052】

[回路ブロックB1〜B4]

NPNトランジスタ17側の回路ブロックB1〜B4の構成について説明する。

回路ブロックB1〜B4は、それぞれ、直流電圧源(51〜54)と、スイッチ(61〜64)と、ダイオード(71〜74)とを備え、各ブロックにおいて、ダイオードのアノードには直流電圧源の−側(負側)が接続され、カソードにはスイッチを介して直流電圧源の+側(正側)が接続されている。

【0053】

更に、回路ブロックB1のダイオード71のアノードは接地され、カソードは回路ブロックB2のダイオード72のアノードに接続されている。以下同様にして、回路ブロックB3,B4のダイオード73,74が直列に接続されて、回路ブロックB4のカソードは、直列電圧源81の−側(負側)に接続されている。

直列に接続された回路ブロックB1〜B4から成る回路を第1の電源電圧生成回路とする。

【0054】

そして、スイッチ61〜64は、後述するスイッチ制御部83からのスイッチ制御信号C1〜C4によってオン/オフが制御され、スイッチがオンとなった回路ブロックの直流電圧源の電圧と直流電圧源81の電圧が加算されて、基準電圧に対して正の電圧がNPNトランジスタ17のコレクタ端子に印加されるようになっている。

つまり、スイッチで選択された直流電圧源と直流電圧源81とが直列接続となる。

尚、回路ブロックB1〜B4の直流電圧源51,52,53,54の電圧を、V1,V2,V3,V4とする。

【0055】

[回路ブロックB5〜B8]

同様に、PNPトランジスタ18側の回路ブロックB5〜B8は、それぞれ、直流電圧源(55〜58)と、スイッチ(65〜68)と、ダイオード(75〜78)とを備え、各ブロックにおいて、ダイオードのアノードには直流電圧源の−側が接続され、カソードにはスイッチを介して直流電圧源のプラス側が接続されている。

【0056】

また、回路ブロックB8のダイオード78のカソードは接地され、アノードは回路ブロックB7のダイオード77のカソードに接続されている。以下同様にして、回路ブロックB6,B5のダイオード76,75が直列に接続されて、回路ブロックB5のアノードは、直列電圧源82の+側に接続されている。

直列に接続された回路ブロックB5〜B8から成る回路を第2の電源電圧生成回路とする。

第1の電源電圧生成回路及び第2の電源電圧生成回路は、請求項に記載した可変電源部に相当する。

【0057】

そして、スイッチ65〜68は、後述するスイッチ制御部83からのスイッチ制御信号C5〜C8によってオン/オフが制御され、スイッチがオンとなった回路ブロックの直流電圧源の電圧と直流電圧源82の電圧が加算されて、基準電圧に対して負の電圧がPNPトランジスタ18のコレクタ端子に印加されるようになっている。

つまり、スイッチで選択された直流電圧源と直流電圧源82が直列接続となる。

尚、回路ブロックB5〜B8の直流電圧源55,56,57,58の電圧を、V5,V6,V7,V8とする。

スイッチ制御信号C1〜C4、C5〜C8は、請求項に記載した選択信号に相当する。

【0058】

[スイッチ制御部83]

次に、第1のプッシュプル増幅器の特徴部分であるスイッチ制御部83について説明する。

スイッチ制御部83は、入力端子8から入力される信号(包絡線信号)に基づいて、NPNトランジスタ17のコレクタ端子に印加される電圧を適切な値とするよう、回路ブロックB1〜B4のスイッチ61,62,63,64のオン/オフを制御するスイッチ制御信号C1,C2,C3,C4を出力する。

【0059】

同様に、スイッチ制御部83は、包絡線信号に基づいて、PNPトランジスタ18のコレクタ端子に印加される電圧を適切な値とするよう、回路ブロックB5〜B8のスイッチ65,66,67,68のオン/オフを制御するスイッチ制御信号C5,C6,C7,C8を出力する。

【0060】

具体的には、スイッチ制御部83は、8種類のスイッチ制御信号のそれぞれを、ハイレベル(Hレベル、オン)又はローレベル(Lレベル、オフ)として出力する制御信号生成回路を備えており、入力された包絡線信号に基づいて、Hレベル又はLレベルの各スイッチ制御信号を出力する。

スイッチ制御部83の各制御信号生成回路は、例えばコンパレータ回路によって構成される。

【0061】

これにより、第1のプッシュプル増幅器では、入力信号の電力レベルに応じて、出力電圧に追随したコレクタ電圧をNPNトランジスタ17及びPNPトランジスタ18に印加することができ、プッシュプル増幅器の電力変換効率を向上させ、電源回路全体の効率を向上させることができるものである。

【0062】

[第1のプッシュプル増幅器の動作:図1]

まず、回路ブロックB1〜B4,B5〜B8の動作について簡単に説明する。

各回路ブロックB1〜B4、B5〜B8では、ダイオードのアノード端子は直流電圧源の負側に、カソード端子は直流電圧源の正側に接続されている。このような回路ブロックB1〜B4、B5〜B8を直列に接続し、各スイッチのオン/オフを制御することにより、電圧を加算してNPNトランジスタ17、PNPトランジスタ18のコレクタ端子に印加することが可能となる。

【0063】

スイッチがONの場合には、当該回路ブロックの直流電圧源の電圧が加算され、電流は直流電圧源を流れ、回路が動作する。このとき、ダイオードには順方向の逆電圧があるため電流は流れない。

また、スイッチがオフの場合には、当該回路ブロックの直流電圧源の回路が開放になっているため、電圧は加算されないが、電流はダイオードを流れ、回路は動作する。

【0064】

そして、第1のプッシュプル増幅器では、スイッチ制御部83が、入力端子8から入力される包絡線信号に応じて、スイッチ制御信号C1〜C8をHレベル又はLレベルに切り替えて出力し、対応する回路ブロックのスイッチのオン/オフを制御する。

これにより、入力電力レベルに応じて、基準電圧に対して正のコレクタ電圧をNPNトランジスタ17に印加し、基準電圧に対して負のコレクタ電圧をPNPトランジスタ18に印加するものである。

【0065】

[スイッチ制御信号とトランジスタのコレクタ電圧:図2]

次に、第1のプッシュプル増幅器におけるスイッチ制御信号とトランジスタのコレクタ電圧の関係について図2を用いて説明する。図2は、第1のプッシュプル増幅器におけるスイッチ制御信号の一例と、それに伴うトランジスタのコレクタ電圧及び出力波形を示す説明図である。

図2の(a)には、スイッチ制御信号C1〜C8の例を示しており、スイッチ制御信号C1〜C8のそれぞれについて、各制御信号がスイッチをオンにする状態(Hレベル)であるか、或いはスイッチをオフにする状態(Lレベル)であるかを表している。

【0066】

図2(a)の例では、スイッチ制御信号C1は、時間T1まではLレベルであり、時間T1〜T8の期間はHレベルであり、時間T8以降は再びLレベルとなっている。

また、スイッチ制御信号C8は、時間T12まではLレベルであり、時間T12〜T13の期間はHレベルであり、時間T13以降はLレベルとなっている。

【0067】

図2(b)では、(a)のスイッチ制御信号C1〜C8が与えられた場合のNPNトランジスタ17のコレクタ電圧(ノードA電圧)と、PNPトランジスタ18のコレクタ電圧(ノードB電圧)と、出力電圧波形とを示している。尚、基準電圧としては、例えばゼロ(0)が用いられる。

【0068】

上述したように、第1のプッシュプル増幅器では、スイッチ制御信号C1〜C8がHレベルである場合に、対応するスイッチ61〜68がオンとなる。

図2において、まず、ノードA電圧に着目して説明する。

時間が0からT1までの間は、スイッチ制御信号C1〜C4が全てLレベルであるため、スイッチ61〜64は全てオフである。

従って、電流は、直流電圧源51〜54には流れずダイオード71〜74を流れ、ノードAには直流電圧源81の電圧V9が印加される。

尚、本実施の形態では、ダイオード71〜78の順方向電圧はゼロとして説明する。

【0069】

続いて、時間T1からT2までの間は、スイッチ制御信号C1のみがHレベルで、その他のスイッチ制御信号C2〜C4はLレベルであるので、スイッチ61のみがオンとなる。

スイッチ61に対応する直流電圧源51と直流電圧源81は直列に接続されているので、ノードAの電圧は、V9+V1となる。

つまり、つまりスイッチがオンになる回路ブロックの直流電圧源の電圧が、直流電圧源81の電圧V9に加算され、当該加算された電圧がノードAに印加されることになる。

【0070】

以下同様にして、時間T2,T3,T4で、スイッチ制御信号C2,C3,C4がそれぞれHレベルとなれば、それに応じてスイッチ62,63,64がオンとなり、ノードAの電圧には、更に電圧V2,V3,V4が加算される。

【0071】

更に、時間T5,T6,T7,T8で、スイッチ制御信号C4,C3,C2,C1がLレベルとなり、スイッチ64,63,62,61がオフになると、ノードAの電圧は、図2に示すように電圧V4,V3,V2,V1が減算される。

【0072】

ノードBの電圧についても、ノードAと同様に、スイッチ制御信号C5〜C8で制御されるスイッチ65〜68がオン又はオフに切り替えられることで図2に示すように変化する。時間T9〜T16の期間に変化するノードBの電圧は、時間T1〜T8におけるノードAの電圧に対して正負が逆になっている。

【0073】

[スイッチ制御部83の動作:図1,図2]

次に、スイッチ制御部83の動作について図1及び図2を用いて説明する。

上述したように、スイッチ制御部83は、入力信号から検出された包絡線信号に基づいて、スイッチ制御信号C1〜C8をHレベル又はLレベルとして出力する。

その結果、ノードAの電圧を制御するためのスイッチ61〜64を制御するスイッチ制御信号C1〜C4は、出力波形が正のときに変化する。

【0074】

スイッチ制御部83は、入力される包絡線信号に基づいて、スイッチ制御信号C1を、出力波形の電圧がV9よりも大きいときにHレベルとする。

また、スイッチ制御部83は、スイッチ制御信号C2を出力波形の電圧がV9+V1よりも大きいときにHレベルとし、スイッチ制御信号C3を出力波形の電圧がV9+V1+V2よりも大きいときにHレベルとし、スイッチ制御信号C4を出力波形の電圧がV9+V1+V2+V3よりも大きいときにHレベルとする。

その他の条件では、スイッチ制御部83は、スイッチ制御信号C1〜C4をLレベルとする。

【0075】

同様に、ノードBの電圧を制御するためのスイッチ65〜68を制御するスイッチ制御信号C5〜C8は、出力波形が負のときに変化する。

スイッチ制御部83は、入力される包絡線信号に基づいて、スイッチ制御信号C5を、出力波形の電圧が−V10よりも小さいときにHレベルとし、スイッチ制御信号C6を出力波形の電圧が−V10−V5よりも小さいときにHレベルとし、スイッチ制御信号C7を出力波形の電圧が−V10−V5−V6よりも小さいときにHレベルとし、スイッチ制御信号C8を出力波形の電圧が−V10−V5−V6−V7よりも小さいときにHレベルとする。

その他の条件では、スイッチ制御部83は、スイッチ制御信号C5〜C8をLレベルとする。

【0076】

スイッチ制御部83は、このような条件でスイッチ制御信号C1〜C8が動作するよう構成され、コンパレータ回路を用いて容易に実現できる。このコンパレータ回路にはヒステリシス特性を持たせてもよい。

【0077】

図1に示したように、第1のプッシュプル増幅器では、スイッチ制御部83は、入力端子8から入力される包絡線信号からスイッチ制御信号C1〜C8を生成するため、入力レベルに対する出力レベルの利得を考慮して設計されている。

【0078】

また、各直流電圧源の電圧V1〜V10は同じ電圧値でもよいし、それぞれ異なる電圧値であってもよい。

更に、ここではノードAの電圧及びノードBの電圧はそれぞれ5段階に変化するように構成されているが、何段であっても構わない。

【0079】

更にまた、第1のプッシュプル増幅器では、出力波形と、V9,V1,V2,V3,V4又はV10,V5,V6,V7,V8を組み合わせて加算または減算したしきい値とを比較して各スイッチ制御信号のレベル(H又はL)を決めているが、必ずしもそのようにする必要はない。

【0080】

[第1のプッシュプル増幅器の効率:図3]

次に、第1のプッシュプル増幅器の効率について図3を用いて説明する。図3は、第1のプッシュプル増幅器の電力変換効率特性を示す説明図である。

上述したように、第1のプッシュプル増幅器では、NPNトランジスタ17のコレクタ端子(ノードA電圧)及びPNPトランジスタ18のコレクタ端子(ノードB)電圧は、出力波形に応じて変化する。

【0081】

つまり、出力波形が小さいときはコレクタ端子電圧の絶対値も小さくなるようにノードA及びノードBの電圧を制御することにより、第1のプッシュプル増幅器は、常に飽和出力に近い状態で動作する。

【0082】

そのため、図3に示すように、第1のプッシュプル増幅器の電力変換効率は、図14に示した従来方式と比較して向上する。特に、飽和出力よりも低い出力において、効率向上が顕著である。

例えば、OFDM信号に相当するバックオフ−8dBのときの電力変換効率は、図14の従来のプッシュプル増幅器では30%であったのが、第1のプッシュプル増幅器では55%に向上している。

【0083】

[直流電圧源回路の構成:図4]

次に、NPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に直流電圧を供給する直流電圧源回路の構成について図4を用いて説明する。図4は、NPNトランジスタ17のコレクタ端子に直流電圧を供給する直流電圧源回路の構成例を示すブロック図である。尚、図1に示した直流電圧源51〜54に相当する部分は同一の符号を付してある。

また、ここでは、NPNトランジスタ17側の直流電圧源回路についてのみ説明するが、PNPトランジスタ18側の直流電圧源回路も同様の構成である。

【0084】

図1に示したように、直流電圧源51〜54と直流電圧源81、直流電圧源55〜58と直流電圧源82は、スイッチ61〜64、スイッチ65〜68がオンになった場合に直列接続になるため、絶縁型電源にする必要がある。

【0085】

図4に示すように、第1のプッシュプル増幅器の直流電圧源回路は、電源を供給する入力端子201と、入力端子201から供給された電源電圧を平滑化する平滑回路202と、スイッチ回路203と、入力と複数の出力を絶縁するためのトランス204と、出力電圧の整流と平滑を行う整流平滑回路205〜208と、目標とする出力電圧との誤差を検出する誤差増幅器209と、誤差情報を制御回路に渡す際に絶縁するためのフォトカプラ210と、誤差情報を最小にすることで目標の出力電圧に制御するための制御回路211と、スイッチ回路203を駆動するためのドライバ回路212とを備えている。

【0086】

上記構成の直流電圧源回路の動作について説明する。

入力端子201から電圧Vinが入力されると、平滑回路202により平滑化され、スイッチ回路203を介してトランス204の入力側に入力される。

トランス204の出力側には、各直流電圧源51〜54の電圧値に応じた巻き数のコイルが設けられ、巻き数に応じて変換された電圧が整流平滑回路205〜208を介して、それぞれ直流電圧源51〜54の出力電圧となる。

【0087】

直流電圧源51〜54の電圧は、V1〜V4であり、直流電圧源54が目標電圧V4になるように制御する。

具体的には、直流電圧源54を監視し、誤差増幅器209で検出した直流電圧源54の電圧と目標電圧との差分である誤差信号をフォトカプラ210を介して制御回路211に入力し、制御回路211が、誤差信号が小さくなるようスイッチ回路203をオン/オフする信号のデューティー比を変えることにより、目標電圧V4とするよう制御する。

【0088】

直流電圧源51,52,53については監視を行わないが、直流電圧源54の電圧がV4になった場合に直流電圧源51,52,53の電圧がV1,V2,V3となるようにトランス204の巻き数を設計しておけばよい。

【0089】

[第1の実施の形態の効果]

本発明の第1の実施の形態に係る電源回路によれば、プッシュプル増幅器に、スイッチと直流電圧源が直列に接続され、更にそれらに並列にダイオードが接続された回路部を1つの回路ブロックとして、複数の回路ブロックB1〜B4が直列に接続された第1の電源電圧生成回路と、複数の回路ブロックB5〜B8が直列に接続された第2の電源電圧生成回路とを備え、第1の電源電圧生成回路が、NPNトランジスタ17のコレクタ端子に接続され、第2の電源電圧生成回路が、PNPトランジスタ18のコレクタ端子に接続され、スイッチ制御部83が、包絡線検波器3からの入力信号の包絡線信号に応じて、複数の回路ブロックB1〜B8のスイッチ61〜68のオン/オフを制御するスイッチ制御信号C1〜C8を出力するようにしているので、NPNトランジスタ17及びPNPトランジスタ18のコレクタ電圧を入力信号レベルに応じて、出力信号レベルに追従するよう制御して、常に飽和に近い動作を可能とし、プッシュプル増幅器の出力レベルが低い場合の電力変換効率を改善し、電源回路全体の電力変換効率を向上させることができる効果がある。

【0090】

更に、第1の電源回路を、例えばEER方式の増幅器に用いることにより、増幅器全体の効率を向上させ、消費電力を低減でき、放熱フィンを小さくして、小型化・軽量化を図ることができる効果がある。

【0091】

尚、上述した例では、直流電圧源81,82は、常時ノードA,ノードBに印加されるよう構成されているが、スイッチ及びダイオードを追加して回路ブロックとし、他の直流電圧源と同様にオン/オフを切り替えられるようにしてもよい。

【0092】

また、NPNトランジスタ17,PNPトランジスタ18のコレクタ電圧を生成する電源電圧生成回路の構成は、図1に示したものに限らず、スイッチ制御部からの制御信号によって異なる電圧を出力する回路であればどのような構成であってもよい。

【0093】

[第2の実施の形態]

次に、本発明の第2の実施の形態に係る電源回路について説明する。

[遷移時間を無視した場合のコレクタ電圧の例:図1、図5]

第2の実施の形態について具体的に説明する前に、図1に示した第1のプッシュプル増幅器において、コレクタ電圧の電位が、あるレベルから次のレベルに遷移する際の遷移時間がない場合の、出力信号波形とコレクタ電圧との関係について図1及び図5を用いて説明する。図5は、遷移時間がない場合の出力信号波形とコレクタ端子の電位との関係を示す説明図である。

尚、図5においては、各ブロックのダイオードの順方向電圧を考慮したコレクタ電圧を示している。

【0094】

図5に示すように、スイッチ制御部83は、NPNトランジスタ17及びPNPトランジスタ18のエミッタ端子に出力されるプッシュプル増幅器の出力電圧波形103と、しきい値Vth1〜Vth8の大小関係に基づいて、上述した電源電圧生成回路の各スイッチ61〜68をオン状態又はオフ状態にするスイッチ制御信号を出力する。

尚、図1の構成では、スイッチ制御部83は、入力信号の包絡線信号に基づいて、出力電圧としきい値との関係に応じた各スイッチ制御信号を生成している。

【0095】

その結果、コレクタ電圧が切り替わる際の遷移時間がないものとすると、NPNトランジスタ17のコレクタ電圧は、101に示すような波形となり、PNPトランジスタ18のコレクタ電圧は、102に示す波形となる。

【0096】

ここで、ダイオード71〜78の順方向電圧をそれぞれ、VF1,VF2,VF3,VF4,VF5,VF6,VF7,VF8とすると、例えば、図1に示したスイッチ61とスイッチ62のみがオン状態で、その他のスイッチがオフ状態の場合、電流は、直流電圧源51,52、ダイオード73,74、直流電圧源81を経由して、NPNトランジスタ17に流れ込むことになる。

この場合のNPNトランジスタ17のコレクタ単位おける電圧Vcは、

Vc=V1+V2+V9−VF3−VF4

となる。

【0097】

また、NPNトランジスタ17及びPNPトランジスタ18は、プッシュプル回路として動作しているため、NPNトランジスタ17が動作している期間では、NPNトランジスタ17のコレクタ端子とエミッタ端子の電位差は、NPNトランジスタ17が飽和しない程度に大きい必要がある。同様にPNPトランジスタ18が動作している期間においては、PNPトランジスタ18のコレクタ端子とエミッタ端子の電位差が十分に大きい必要がある。

コレクタ端子とエミッタ端子の電位差が、トランジスタの飽和電圧よりも小さくなった場合、トランジスタが飽和して、プッシュプル増幅器から出力される信号に歪が生じる。

【0098】

そこで、図5に示すように、プッシュプル増幅器の出力波形のレベルを判定するしきい値(Vth1〜Vth8)を以下のように設定する。

Vth1<V9−VF1−VF2−VF3−VF4−Vce(npn:sat)

Vth2<V9+V1−VF2−VF3−VF4−Vce(npn:sat)

Vth3<V9+V1+V2−VF3−VF4−Vce(npn:sat)

Vth4<V9+V1+V2+V3−VF4−Vce(npn:sat)

Vth5>−V10+VF5+VF6+VF7+VF8+Vce(pnp:sat)

Vth6>−V10−V5+VF6+VF7+VF8+Vce(pnp:sat)

Vth7>−V10−V5−V6+VF7+VF8+Vce(pnp:sat)

Vth8>−V10−V5−V6−V7+VF8+Vce(pnp:sat)

【0099】

ここで、Vce(npn:sat)は、NPNトランジスタ17が飽和するコレクタ−エミッタ間電圧であり、Vce(pnp:sat)は、PNPトランジスタ18が飽和するコレクタ−エミッタ間電圧である。

これにより、スイッチ制御部83からの制御信号によってどのコレクタ電圧値が選択された場合でも、NPNトランジスタ17及びPNPトランジスタ18のコレクタ端子とエミッタ端子の電位差を、トランジスタが飽和しない程度に確保できるものである。

【0100】

[コレクタ電圧の遷移時間:図6]

次に、NPNトランジスタ17及びPNPトランジスタ18のコレクタに印加されるコレクタ電圧の遷移時間について図6を用いて説明する。図6は、NPNトランジスタ17のコレクタ電圧の遷移時間を示す説明図である。

図6では、プッシュプル増幅器12の出力波形例113に対するNPNトランジスタ17のコレクタ電圧の理想的な波形111と、実際の波形112の例を示している。

【0101】

EER方式の電源回路では、プッシュプル増幅器12の出力波形113の変化に追随して、コレクタ電圧を変化させる。

図6の例では、コレクタ電圧の電圧レベルを、プッシュプル増幅器の出力波形113のレベル増加に伴って、時刻tにおいてVc(i)から次の電圧レベルVc(i+1)に切り替え、出力波形113のレベル低下に伴って、再び電圧レベルVc(i)に切り替えている。

【0102】

時刻tにおいて、スイッチ制御部83からの指示により、スイッチ61〜65のいずれかがオフ状態からオン状態となって、NPNトランジスタ17のコレクタ端に印加されている電圧が、Vc(i)からVc(i+1)に切り替わった場合、電圧レベルを遷移させる遷移時間が不要であれば、理想的な信号波形111のように階段状の波形となる。

【0103】

しかし、実際の信号波形112は、図6に示すように有限の切り替え時間(遷移時間)Δtを伴う応答となる。また、PNPトランジスタ18におけるコレクタ電圧の切り替え時の波形は、波形112の上下を反転させた波形となる。

【0104】

[広帯域信号の場合]

ここで、プッシュプル増幅器12に入力される信号が、広帯域なW−CDMA信号やOFDM信号の場合、出力波形113に示されるように急峻な立ち上がりや立下りを有する場合がある。

このような場合、コレクタ電圧の切り替えが間に合わずに、プッシュプル増幅器のコレクタ端の電位とエミッタ端の電位との差が飽和電圧を下回ると、トランジスタは飽和してプッシュプル増幅器12の出力信号波形に歪が発生してしまう。

【0105】

[遷移時間の短縮]

そのため、コレクタ電圧の電圧レベルの遷移時間を短くする必要がある。

遷移時間は、スイッチ61〜68やスイッチ制御部83の応答速度や、回路の各部に内在する寄生容量や寄生インダクタンスなどにより決まり、応答速度の速い素子や、寄生容量・寄生インダクタンスの少ない素子を使用して、回路レイアウトを最適化することである程度の改善は可能である。

しかし、広帯域信号の包絡線の急峻な立ち上がり/立下りに反応できるよう、遷移時間を十分短くすることは依然として困難であった。

【0106】

また、遷移時間の短縮を図るため、電圧レベルを急峻に切り替えようとすると、コレクタ電圧に、振幅が波打つように変化するリンギングを発生することがあり、リンギングが大きいとコレクタ端子の電位とエミッタ端子の電位との差が小さくなって出力信号に歪が発生しやすい。

つまり、リンギングを許容範囲内としつつ、コレクタ電圧の遷移時間を十分短縮することは困難であった。

【0107】

そこで、本発明の第2の実施の形態では、コレクタ電圧の切り替え時の遷移時間が、リンギングを許容範囲内とする程度の時間であっても広帯域信号のレベル変化に十分追随でき、出力信号の歪特性を劣化させない電源回路を提供する。

【0108】

[第2の実施の形態の構成:図7]

本発明の第2の実施の形態に係る電源回路は、第1の電源回路と同様に、プッシュプル増幅器とDC/DCコンバータとを備えている。

本発明の第2の実施の形態に係る電源回路で用いられるプッシュプル増幅器の構成について図7を用いて説明する。図7は、本発明の第2の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

図7に示すように、本発明の第2の実施の形態に係る電源回路(第2の電源回路)に用いられるプッシュプル増幅器(第2のプッシュプル増幅器)は、基本的な構成は、図1に示した第1のプッシュプル増幅器と同じであり、図1と同一の符号を付して説明する。

【0109】

第2のプッシュプル増幅器は、新たにタイミング制御部121を備えている点が特徴であり、また、スイッチ制御部83′の構成及び動作が第1のプッシュプル増幅器のスイッチ制御部83とは一部異なっている。

【0110】

[第2のプッシュプル増幅器の動作概略]

ここで、第2のプッシュプル増幅器の動作について簡単に説明する。

第2のプッシュプル増幅器は、コレクタ電圧の遷移時間を考慮して、入力信号を十分遅延させ、広帯域信号が入力された場合であってもコレクタ電圧が十分追随できるようにしているものである。

【0111】

具体的には、第2のプッシュプル増幅器では、入力された信号を、コレクタ電圧の遷移時間よりも大きい一定の遅延時間(td)だけ遅延させてオペアンプ16に入力すると共に、遅延させない入力信号に基づいて生成した制御信号C1〜C8を、当該遅延時間(td)からコレクタ電圧の遷移時間(Δt)を差し引いた時間(td−Δt)だけ遅延させて立ち上げる。

【0112】

これにより、スイッチ制御信号C1〜C8は、トランジスタのエミッタ端における出力信号に対して、遷移時間(Δt)分だけ早いタイミングで出力されることになり、入力信号に急峻な変化があっても、コレクタ電圧がそれに追随して変化して、出力信号における歪特性が劣化するのを防ぐことができるものである。

尚、実際には、コレクタ電圧の遷移時間は、電圧レベル毎に異なる時間となっている。

【0113】

[第2のプッシュプル増幅器の各部]

第2のプッシュプル増幅器の特徴部分について具体的に説明する。

[タイミング制御部121]

タイミング制御部121は、入力端子8から入力された信号を、予め設定された特定の遅延時間tdだけ遅延させて、オペアンプ16に出力する。

遅延時間tdは、コレクタ電圧の、どの電圧レベルにおける遷移時間よりも長い時間としている。

タイミング制御部121は、請求項に記載したタイミング調整部に相当する。

【0114】

[スイッチ制御部83′]

スイッチ制御部83′は、第1のプッシュプル増幅器におけるスイッチ制御部83と同様に、入力端子8から入力される包絡線信号に基づいて、スイッチ制御信号C1〜C8を生成するものであるが、スイッチ制御信号の出力(レベルの切り替え)のタイミングを第1のプッシュプル増幅器に比べて遅くしているものである。

【0115】

スイッチ制御部83′は、スイッチ制御信号C1〜C8を生成するコンパレータ回路に加えて、生成されたスイッチ制御信号C1〜C8を出力するタイミングを制御する制御回路を備えている。制御回路は、処理部及び記憶部を備えたマイコン等で構成される。

尚、スイッチ制御部83′は、請求項に記載した制御部に相当する。

【0116】

スイッチ制御部83′からのスイッチ制御信号C1〜C8のレベル(ハイレベル又はローレベル)の組み合わせによって決定されるNPNトランジスタ17及びPNPトランジスタ18のコレクタ電圧について説明する。

ここでは、各回路ブロックB1〜B8のダイオード71〜78の順方向電圧(VF1〜VF8)を考慮している。

【0117】

第2のプッシュプル増幅器におけるNPNトランジスタ17のコレクタ端子に印加される電圧をVc1〜Vc5、PNPトランジスタ18のコレクタ端子に印加される電圧をVc6〜Vc10とすると、図7の構成ではコレクタ電圧のレベルは10段階であり、

Vc1=V9−VF1−VF2−VF3−VF4

Vc2=V9+V1−VF2−VF3−VF4

Vc3=V9+V1+V2−VF3−VF4

Vc4=V9+V1+V2+V3−VF4

Vc5=V9+V1+V2+V3+V5

Vc6=−V10+VF5+VF6+VF7+VF8

Vc7=−V10−V5+VF6+VF7+VF8

Vc8=−V10−V5−V6+VF7+VF8

Vc9=−V10−V5−V6−V7+VF8

Vc10=−V10−V5−V6−V7−V8

となる。

【0118】

上述したように、コレクタ電圧を切り替える際の遷移時間は、電圧レベル毎に異なっており、電圧レベルVc1からVc2に切り替わるために必要な遷移時間をΔt1とする。

同様に、電圧レベルVc2からVc3への遷移時間をΔt2、電圧レベルVc3からVc4への遷移時間をΔt3、電圧レベルVc4からVc5への遷移時間をΔt4、電圧レベルVc6からVc7への遷移時間をΔt5、電圧レベルVc7からVc8への遷移時間をΔt6、電圧レベルVc8からVc9への遷移時間をΔt7、電圧レベルVc9からVc10への遷移時間をΔt8とする。

遷移時間Δt1〜Δt8の値は、プッシュプル増幅器の特性や回路を構成する各素子の特性や回路定数、更には電力増幅器の主増幅器6の特性などによって決まる値であり、設計段階で把握することが可能な値である。

【0119】

第2のプッシュプル増幅器のスイッチ制御部83′では、予め、各コレクタ電圧の切り替えレベル(Vc1→Vc2,Vc2→Vc3,...Vc9→Vc10)と、その電位の変化に要する遷移時間(Δt1〜Δt8)とを対応付けて記憶している。

尚、ここでは、遷移時間は、制御信号の立ち上がり時(スイッチをオンにする場合)のみについて考慮しており、立下り時の遷移時間は考慮していない。

つまり、スイッチ制御部83′では、各スイッチ制御信号C1〜C8の立ち上げ時の遷移時間をΔt1〜Δt8として記憶しているものである。

【0120】

そして、第2のプッシュプル増幅器の特徴として、スイッチ制御部83′では、コレクタ電圧の切り替えレベル毎に、スイッチ制御信号C1〜C8のレベルを切り替えるタイミングを遅延させる時間(タイミング遅延時間)を記憶したテーブルを備えている。

【0121】

尚、実際には、スイッチ制御部83′は、プッシュプル増幅器12への入力信号に基づいて制御を行うので、入力信号と予め設定された複数のしきい値との大小関係及び入力信号の変化の向き、つまり各スイッチ制御信号C1〜C8の立ち上がり又は立ち下げに対応して、タイミング遅延時間を記憶している。

つまり、スイッチ制御部83′は、各スイッチ制御信号C1〜C8のそれぞれについて、立ち上げ時及び立ち下げ時のタイミングを遅延するタイミング遅延時間をメモリに記憶しているものである。

【0122】

第2のプッシュプル増幅器では、スイッチ制御信号の立ち上がりの場合(スイッチをオンにする場合)には、タイミング遅延時間として、タイミング制御部121における遅延時間tdから各切り替えレベルに対応した遷移時間を減算した時間(td−Δt)を記憶している。

また、スイッチ制御信号の立下りの場合には、タイミング遅延時間として、タイミング制御部121における遅延時間tdを記憶している。

各スイッチ制御信号のタイミング遅延時間については後述する。

【0123】

[第2のプッシュプル増幅器におけるスイッチ制御信号のタイミング:図8]

次に、第2のプッシュプル増幅器におけるスイッチ制御信号のタイミングについて図8を用いて説明する。図8は、第2のプッシュプル増幅器におけるスイッチ制御信号の制御タイミングを示す説明図である。

図8では、プッシュプル増幅器の入力端子8から入力信号131が入力された場合の、スイッチ制御信号C1〜C8を示している。スイッチ制御信号C1〜C8がLレベルの時には、対応するスイッチ61〜68がオフ状態となり、スイッチ制御信号C1〜C8がHレベルの時には、対応するスイッチ61〜68がオン状態となる。

【0124】

スイッチ制御部83′は、入力信号131を、予め記憶しているしきい値Vth1〜Vth8と比較して、スイッチ制御信号C1〜C8のレベル(Hレベル又はLレベル)を決定して、入力信号131としきい値との大小関係及び変化の向きに対応して予め記憶しているタイミング遅延時間だけ遅延したタイミングで出力する。

【0125】

図8に示すように、信号波形131が、しきい値Vth1よりも大きくなる時刻をt1とし、Vth2,Vth3,Vth4よりも大きくなる時刻をそれぞれt2,t3,t4とする。

また、信号波形131が、しきい値Vth5より小さくなる時刻をt9とし、Vth6,Vth7,Vth8よりも小さくなる時刻をそれぞれt10,t11,t12とする。

【0126】

スイッチ制御部83′は、時刻t1において信号波形131がしきい値Vth1より大きくなったことを検出すると、スイッチ制御信号C1をHレベルとするが、その際、スイッチ制御部83′は、テーブルからスイッチ制御信号C1の立ち上げ時に対応するタイミング遅延時間を読み取り、時刻t1よりも当該タイミング遅延時間だけ遅らせたタイミングでHレベルに切り替えた信号を出力する。

【0127】

上述したように、スイッチ制御信号C1の立ち上げ時のタイミング遅延時間をtd1とすると、td1は、タイミング制御部121における遅延時間tdから、スイッチ制御信号C1の立ち上げ時の遷移時間Δt1を差し引いた時間である(td1=td−Δt1)。

【0128】

同様に、スイッチ制御部83′は、NPNトランジスタ17のコレクタ電圧を切り替えるスイッチ制御信号C2〜C4を、時刻t2〜t4よりタイミング遅延時間td2〜td4だけ遅らせてLレベルからHレベルに切り替えて出力する。

また、スイッチ制御部83′は、PNPトランジスタ18のコレクタ電圧を切り替えるスイッチ制御信号C5〜C6を、時刻t9〜t12よりタイミング遅延時間td9〜td12だけ遅らせてLレベルからHレベルに切り替える。

【0129】

各スイッチ制御信号の立ち上げ時(Lレベル→Hレベル)/立ち下げ時(Hレベル→Lレベル)のタイミング遅延時間は以下のようになる。

C1立ち上げ時:td1=td−Δt1

C2立ち上げ時:td2=td−Δt2

C3立ち上げ時:td3=td−Δt3

C4立ち上げ時:td4=td−Δt4

C4立ち下げ時:td5=td

C3立ち下げ時:td6=td

C2立ち下げ時:td7=td

C1立ち下げ時:td8=td

C5立ち上げ時:td9=td−Δt5

C6立ち上げ時:td10=td−Δt6

C7立ち上げ時:td11=td−Δt7

C8立ち上げ時:td12=td−Δt8

C8立ち下げ時:td13=td

C7立ち下げ時:td14=td

C6立ち下げ時:td15=td

C5立ち下げ時:td16=td

スイッチ制御部83′には、メモリに上述したタイミング遅延時間が記憶されており、スイッチ制御信号の切り替え時は、対応するタイミング遅延時間だけ遅らせてHレベル又はLレベルに切り替えた信号を出力する。

【0130】

プッシュプル増幅器12への入力信号131は、タイミング制御部121によって遅延時間tdだけ遅延されて出力されるので、スイッチ制御信号を上述したタイミング遅延時間(td1〜td16)だけ遅らせて出力することにより、スイッチ制御信号の立ち上げ時には、プッシュプル増幅器の出力端子における信号波形に対して、コレクタ端子に印加する電圧を切り替えるタイミングを、各遷移時間分早めることが可能となる。

これにより、入力信号の立ち上がりに伴うスイッチ制御信号の立ち上げ時において、コレクタ電圧の切り替え時の遷移時間の影響を少なくすることができ、出力信号の歪特性の劣化を抑制することができるものである。

【0131】

[第2のプッシュプル増幅器の入出力信号とコレクタ電圧の例:図9]

次に、第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係について図9を用いて説明する。図9は、第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係を示す説明図である。

図9(a)に示すように、プッシュプル増幅器の入力信号131に対して、(b)に示すように、出力信号141は、タイミング制御部121によって所定の遅延時間tdだけ遅延されて出力される。

【0132】

また、出力信号141が基準電圧より大きい場合にNPNトランジスタ17のコレクタ端子に印加されるコレクタ電圧142は、上述したようなタイミング遅延時間で切り替わるスイッチ制御信号によって、出力信号141がしきい値に達するよりも早いタイミングで切り替わるため、出力信号141の変化に追従して段階的に変化している。

同様に、出力信号141が基準電圧より小さい場合にPNPトランジスタ18に印加されるコレクタ電圧143も、出力信号141の変化に追従して段階的に変化している。

【0133】

[第2の実施の形態の効果]

本発明の第2の実施の形態に係る電源回路によれば、第1の電源回路のスイッチ制御部83の代わりにスイッチ制御部83′を設け、入力信号を特定の遅延時間tdだけ遅延させるタイミング制御部121を設け、スイッチ制御部83′が、各スイッチ制御信号C1〜C8に対応して、当該スイッチ制御信号が立ち上げ/立ち下げによるNPNトランジスタ17又はPNPトランジスタ18のコレクタ電圧のレベル遷移に要する遷移時間Δtを記憶すると共に、各スイッチ制御信号C1〜C8に対応して、立ち上げ時と立ち下げ時のタイミング遅延時間を記憶しており、各スイッチ制御信号C1〜C8の立ち上げ時には、入力信号のタイミングから、当該スイッチ制御信号に対応して記憶されたタイミング遅延時間(td−Δt)だけ遅延させてHレベルに切り替え、スイッチ制御信号の立ち下げ時には、入力信号のタイミングから遅延時間tdだけ遅延させてLレベルに切り替えるようにしているので、タイミング制御部121で遅延された信号に対して、スイッチ制御信号の立ち上げ時のコレクタ電圧の遷移時間分、早くスイッチ制御信号を立ち上げることができ、コレクタ電圧の遷移時間の影響をなくして、広帯域信号の急な立ち上がりにも追随させることができ、出力信号における歪特性を改善することができる効果がある。

【0134】

また、第2の電源回路を、図12に示したET方式やEER方式の電力増幅器の電源回路として用いれば、主増幅器6の出力信号レベルに良く追随した電源電圧を主増幅器6に供給することができ、ET方式やEER方式の電力増幅器全体の効率を一層向上させることができる効果がある。

【0135】

[第3の実施の形態]

本発明の第3の実施の形態に係る電源回路(第3の電源回路)について説明する。

第3の電源回路は、プッシュプル増幅器とDC/DCコンバータとを備えており、第2の電源回路と同様の構成であるが、プッシュプル増幅器(第3のプッシュプル増幅器)12のスイッチ制御部83′におけるスイッチ制御信号の立ち上げ時の切り替えタイミングを、演算によって決定するようにしている。

【0136】

[コレクタ電圧の遷移状態における傾き:図10]

まず、コレクタ電圧の遷移状態における傾きについて図10を用いて説明する。図10は、コレクタ電圧の遷移状態における傾きを直線近似する場合の説明図である。

図10に示すように、コレクタ電圧が、ある電圧レベルVciから次の電圧レベルVc(i+1)に切り替わる場合には、矩形波形とはならずに、遷移時間Δtjで緩やかな立ち上がりとなる。

【0137】

図10の例では、コレクタ電圧の遷移状態における傾きを直線近似した場合、傾きsは、

s=(Vc(i+1)−Vci)/Δtj と表される。

コレクタ電圧の切り替えレベルに対応する遷移時間(Δt)は、上述したように、プッシュプル増幅器の特性や各素子の特性及び回路定数等により決定され、定数として予めスイッチ制御部83′に記憶されている。

従って、コレクタ電圧の切り替えレベルに対応する傾きs1〜s16も定数であり、予め記憶されている。

【0138】

[第3のプッシュプル増幅器における動作:図5,図10,図16]

第3のプッシュプル増幅器の特徴部分について図5,図10,図16を用いて説明する。

第2のプッシュプル増幅器の説明と同様に、プッシュプル増幅器12におけるNPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に印加される電圧をVc1〜Vc10とする。

また、入力信号波形131がVth1〜Vth4より大きくなる時刻を、それぞれt1〜t4とし、Vth5〜Vth8より小さくなる時刻を、それぞれt9〜t12とする。

【0139】

以下、簡単のためにNPNトランジスタ17のコレクタ端に印加される電圧レベルがVc1からVc2に切り替わる場合を例にとって説明する。

まず、入力信号がしきい値Vth1より大きくなった時刻t1から遅延時間tdまでの間に含まれる任意の時刻及びその時の電圧レベルを、それぞれ時刻tn及び電圧レベルVnとする。

更に、NPNトランジスタ17が飽和しないためのマージンとなる電圧をVmとする。Vmとしては、NPNトランジスタ17の飽和電圧よりも大きい電圧値が設定される。

【0140】

そして、スイッチ制御部83′は、(式3)によって求められる時刻ta(n)を算出する。

ta(n)=(Vc1−(Vn+Vm))/s1+tn (式3)

ここで、s1は、コレクタ端子に印加される電圧がVc1からVc2に変化する際の傾きを直線近似したものである。

また、Vmは、時刻tn時の信号の電圧値Vnに対して、トランジスタを飽和させないためのマージン電圧である。

【0141】

つまり、ta(n)は、コレクタ電圧の変化を傾きs1の直線で近似した場合に、任意の時刻tnにおける信号Vnに対してトランジスタが飽和しないコレクタ電圧を供給するためのスイッチ制御信号の立ち上げタイミング(時刻)に相当する。

【0142】

[ta(n)の算出方法:図16]

ここで、第3のプッシュプル増幅器におけるスイッチ制御信号の立ち上げタイミングの算出方法について具体的に説明する。

時刻t1からt1+tdまでの間の任意の時刻tnにおけるta(n)の算出方法について、図16を用いて説明する。図16は、コレクタ電圧をVc1からVc2に切り替える場合の、スイッチ制御信号C1の立ち上げタイミングの求め方を示す説明図である。

説明を簡単にするために、図16では、この区間の任意の時刻T1、T2、T3の信号に基づいて、ta(n)を求める場合について示している。

【0143】

上述したようにta(n)は(式3)によって求められるが、図16に示すように、時刻T1,T2,T3におけるta(n)は、各時刻における信号の電圧値V1,V2,V3に、マージン電圧Vmを加算した点(Vn+Vm)を通る傾きs1の直線がコレクタ電圧Vc1と交わる点として求められる。

【0144】

図16の例では、時刻T1については(V1+Vm)を通る傾きs1の直線とVc1との交点としてta(1)が求められる。

同様にして、時刻T2についてta(2)が求められ、時刻T3についてta(3)が求められる。

そして、第3のプッシュプル増幅器のスイッチ制御部83′では、ta(1)〜ta(3)の中で最も早いタイミングであるta(2)をVc1からVc2への切り替えタイミングta1とするものである。

【0145】

このように算出されたta(n)の中で最も早いタイミングを選択することにより、傾きS1で近似されるコレクタに印加される電圧が、信号の電圧Vnよりも下回ることは無く、トランジスタの飽和を防ぐことができるものである。

【0146】

同様にして、各コレクタ電圧レベルの切り替えについても、傾きに応じてスイッチ制御信号の立ち上げ時の切り替えタイミング(ta2〜ta4、ta9〜ta12)を求める。ta2〜ta4は、スイッチ制御信号C2〜C4の立ち上げ時の切り替えタイミングであり、ta9〜ta12は、スイッチ制御信号C5〜C8の立ち上げ時の切り替えタイミングである。

【0147】

尚、第3のプッシュプル増幅器のスイッチ制御部83′には、予め、各スイッチ制御信号の立ち上げ時におけるコレクタ電圧の変化を直線近似した場合の傾きs1〜s4、s9〜s12が記憶されている。ここで、s1〜s4は、スイッチ制御信号C1〜C4の立ち上げ時の傾き、s9〜s12は、スイッチ制御信号C5〜C8の立ち上げ時の傾きを示す。

傾きs1〜s4は正の符号を持ち、傾きs9〜s12は負の符号を持つ。

【0148】

そして、第3のプッシュプル増幅器では、スイッチ制御部83′は、入力信号の電圧としきい値とを比較し、入力信号のレベルと変化の方向に基づいて切り替えを行うスイッチ制御信号を決定し、スイッチ制御信号の立ち上げ時には上述した演算処理を行って、特定の遅延時間tdより、しきい値を越えたタイミングと切り替えタイミングta1〜ta4、ta9〜ta12との差分だけ早いタイミングでスイッチ制御信号の立ち上げを行う。

【0149】

つまり、第3のプッシュプル増幅器では、スイッチ制御信号の立ち上がりの場合には、入力信号と各レベルにおけるコレクタ電圧の遷移の傾きに応じて算出された切り替えタイミング(ta(n))と、入力信号がしきい値を超えた時刻(t(n))との時間差を、タイミング制御部121における遅延時間tdから減算して、算出された時間を各スイッチ制御信号のタイミング遅延時間とする。

また、スイッチ制御信号の立ち下げ時には、特定の遅延時間tdに合わせたタイミング遅延時間とする。

【0150】

つまり、第3のプッシュプル増幅器においては、スイッチ制御信号の立ち上げ時には、遅延された信号よりも早いタイミングで立ち上げ、スイッチ制御信号の立ち下げ時には、遅延された信号に合わせたタイミングで立ち下げる。

すなわち、第3のプッシュプル増幅器における各スイッチ制御信号の立ち上げ時(Lレベル→Hレベル)/立ち下げ時(Hレベル→Lレベル)のタイミング遅延時間は以下のようになる。

C1立ち上げ時:td1=td−(t1−ta1)

C2立ち上げ時:td2=td−(t2−ta2)

C3立ち上げ時:td3=td−(t3−ta3)

C4立ち上げ時:td4=td−(t4−ta4)

C4立ち下げ時:td5=td

C3立ち下げ時:td6=td

C2立ち下げ時:td7=td

C1立ち下げ時:td8=td

C5立ち上げ時:td9=td−(t9−ta9)

C6立ち上げ時:td10=td−(t10−ta10)

C7立ち上げ時:td11=td−(t11−ta11)

C8立ち上げ時:td12=td−(t12−ta12)

C8立ち下げ時:td13=td

C7立ち下げ時:td14=td

C6立ち下げ時:td15=td

C5立ち下げ時:td16=td

【0151】

これにより、tdだけ遅延されたプッシュプル増幅器の出力信号よりも早いタイミングでスイッチ制御信号を立ち上げ、コレクタ電圧の遷移時間があってもトランジスタの飽和を防ぎ、急激な出力信号の立ち上がりに対してもコレクタ電圧を追随させて、出力信号における歪特性を改善できるものである。

また、コレクタ電圧の立ち下がりが遷移時間によって遅くなっても、理想的なコレクタ電圧の波形を上回る電圧となるため、トランジスタが飽和することはない。

【0152】

[第3の実施の形態の効果]

本発明の第3の実施の形態に係る電源回路によれば、スイッチ制御部83′が、コレクタ電圧の各レベルにおける遷移を直線近似した場合の傾きを予め記憶しておき、入力信号としきい値とを比較して、その大小と変化の向きに基づいて各スイッチ制御信号のHレベル/Lレベルを決定し、スイッチ制御信号を立ち上げる際に、コレクタ電圧が記憶された傾きで遷移した場合に信号電圧によりトランジスタが飽和しない最も早いタイミングである切り替えタイミングta(n)を演算により算出し、信号がしきい値を超えた時刻t(n)と当該切り替えタイミングとの差分(t(n)−ta(n))を、特定の遅延時間(td)から差し引いた時間を、スイッチ制御信号の遅延時間(タイミング遅延時間)としているので、タイミング制御部121でtdだけ遅延された信号に対して、コレクタ電圧の遷移時間を考慮してトランジスタが飽和しないよう、早めにスイッチ制御信号を立ち上げることができ、出力信号における歪特性を改善することができる効果がある。

【0153】

また、第3の電源回路によれば、入力された信号に基づいてta(n)を算出してタイミング遅延時間を決定するので、広帯域信号の急激な立ち上がりに対しても迅速に対応してコレクタ電圧を追随させることができ、歪特性を改善することができる効果がある。

また、第3の電源回路によれば、実際の入力波形信号に応じてスイッチをオンする最適なタイミングを決めることが可能であり、効率を一層向上させる効果がある。

また、予めメモリに遷移時間やタイミング遅延時間を記憶する必要がないので、メモリの容量を小さくできる効果がある。

【0154】

また、第3の電源回路では、スイッチ制御信号の立ち下げ時には、遷移時間を算出せずに、入力信号のタイミングから遅延時間tdだけ遅延させたタイミングでスイッチ制御信号を立ち下げるようにしており、処理を簡易にすることができる効果がある。

更に、第3の電源回路を、図12に示したET方式やEER方式の電力増幅器の電源回路として用いることにより、電力増幅器全体の効率を一層向上させることができる効果がある。

【0155】

[第4の実施の形態]

次に、本発明の第4の実施の形態に係る電源回路(第4の電源回路)について説明する。

第4の電源回路は、プッシュプル増幅器(第4のプッシュプル増幅器)12のスイッチ制御部83′におけるスイッチ制御信号の切り替えタイミングを、立ち上げ時だけでなく立ち下げ時にも演算で決定するものである。

【0156】

上述した第3の電源回路では、スイッチ制御信号の立ち下げ時には遅延時間tdだけ遅延させたタイミングで立ち下げるようにして、十分な遅延時間を確保してトランジスタの飽和を防ぐようにしているが、第4の電源回路では、遅延時間をより短くして、電源電圧をプッシュプル増幅器12の出力波形にできるだけ追随させるようにしている。

【0157】

第4の電源回路の構成は、第2、第3の電源回路と同様の構成であり、スイッチ制御部83′の処理が第3の電源回路とは一部異なっている。

スイッチ制御部83′におけるスイッチ制御信号の立ち上げ時の切り替えタイミング(ta(n))とタイミング遅延時間(td(n))を算出する処理は、第3のプッシュプル増幅器と同様である。

【0158】

[第4のプッシュプル増幅器における動作:図17]

第4のプッシュプル増幅器の特徴部分である、スイッチ制御信号の立ち下げ時のタイミングの算出方法について具体的に説明する。図17は、コレクタ電圧をVc2からVc1に切り替える場合の、スイッチ制御信号C1の立ち下げタイミングの求め方を示す説明図である。

第2、第3のプッシュプル増幅器の説明と同様に、プッシュプル増幅器12におけるNPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に印加される電圧をVc1〜Vc10とし、入力信号波形がVth1〜Vth4より大きくなる時刻を、それぞれt1〜t4とし、Vth4〜Vth1より小さくなる時刻を、t5〜t8とし、Vth5〜Vth8より小さくなる時刻を、t9〜t12とし、Vth8〜Vth5より大きくなる時刻を、t13〜t16とする。

【0159】

また、第4のプッシュプル増幅器のスイッチ制御部83′は、コレクタ電圧の切り替えレベルに対応する傾きとして、立ち上げ時の傾きに加えて、立ち下げ時の傾き(s5〜s8、s13〜s16)を記憶している。

NPNトランジスタ17の立ち下げ時の傾きは、負の符号を持ち、コレクタ電圧が1段階下に遷移する場合の傾きと等しいか、又はそれより大きい傾きとしている。

PNPトランジスタ18立ち下げ時の傾きは、正の符号を持つ。

【0160】

以下、簡単のためにNPNトランジスタ17のコレクタ端に印加される電圧レベルがVc2からVc1に切り替わる場合を例にとって説明する。

この間のコレクタ電圧の遷移を直線近似した場合の傾きはs5としている。

図17に示すように、まず、入力信号がしきい値Vth1より小さくなった(しきい値Vth1を下回った)時刻をt8とする。

【0161】

そして、時刻t8と、時刻t8より遅延時間tdだけ早い時刻(t8−td)との間に含まれる任意の時刻及びその時の電圧レベルを、それぞれ時刻tn及び電圧レベルVnとする。

更に、NPNトランジスタ17が飽和しないためのマージンとなる電圧をVmとする。

そして、スイッチ制御部83′は、当該区間の任意の時刻tnにおいて、

ta(n)=(Vc2−(Vn+Vm))/s5+tn

を算出する。

【0162】

説明を簡単にするために、図17では、この区間の任意の時刻T1、T2、T3、T4の信号に基づいて、スイッチ制御信号C1の立ち下げタイミングta(n)を求める場合について示している。

【0163】

図17に示すように、時刻T1,T2,T3,T4のそれぞれにおけるta(n)は、各時刻における信号の電圧値V1,V2,V3,V4にマージン電圧Vmを加算した点(Vn+Vm)を通る傾きs5の直線が、コレクタ電圧Vc2と交わる点として求められる。

【0164】

図17の例では、時刻T1については(V1+Vm)を通る傾きs5の直線とVc2との交点としてta(1)が求められ、同様にして、時刻T2についてta(2)が、時刻T3についてta(3)が、時刻T4についてta(4)が求められる。

そして、第4のプッシュプル増幅器のスイッチ制御部83′は、ta(1)〜ta(4)の中で最も遅いタイミングであるta(4)をVc2からVc1への切り替えタイミングta8とするものである。

【0165】

つまり、このように求めた切り替えタイミングでスイッチ制御信号を立ち下げれば、コレクタ電圧が遷移時間を持って立ち下がった場合に、当該区間の信号でトランジスタが飽和することはなく、更にコレクタ電圧を出力信号波形により追随させることができるものである。

【0166】

そして、第4のプッシュプル増幅器では、スイッチ制御部83′は、入力信号の電圧としきい値とを比較し、入力信号のレベルと変化の方向に基づいて切り替えを行うスイッチ制御信号を決定し、スイッチ制御信号の立ち上げ時及び立ち下げ時に演算処理を行って、特定の遅延時間tdより、しきい値を越えたタイミングと切り替えタイミングta1〜ta12との差分だけ早いタイミングでスイッチ制御信号の立ち上げを行う。

【0167】

つまり、第4のプッシュプル増幅器では、スイッチ制御信号の立ち上がり/立ち下がりの場合には、入力信号と各レベルにおけるコレクタ電圧の遷移の傾きに応じて算出された切り替えタイミング(ta(n))と、入力信号がしきい値を超えた又は下回った時刻(t(n))との時間差を、タイミング制御部121における遅延時間tdから減算して、算出された時間を各スイッチ制御信号のタイミング遅延時間とする。

【0168】

上述したように、スイッチ制御信号の立ち上げ時には、トランジスタが飽和しない最も早いタイミングをta(n)とし、立ち下げ時には、トランジスタが飽和しない最も遅いタイミングをta(n)としているので、時間差(t(n)−ta(n))は、立ち上げ時の方が立ち下げ時の時間差よりも大きくなる。

【0169】

すなわち、第4のプッシュプル増幅器における各スイッチ制御信号の立ち上げ時(Lレベル→Hレベル)/立ち下げ時(Hレベル→Lレベル)のタイミング遅延時間は以下のようになる。

C1立ち上げ時:td1=td−(t1−ta1)

C2立ち上げ時:td2=td−(t2−ta2)

C3立ち上げ時:td3=td−(t3−ta3)

C4立ち上げ時:td4=td−(t4−ta4)

C4立ち下げ時:td5=td−(t5−ta5)

C3立ち下げ時:td6=td−(t6−ta6)

C2立ち下げ時:td7=td−(t7−ta7)

C1立ち下げ時:td8=td−(t8−ta8)

C5立ち上げ時:td9=td−(t9−ta9)

C6立ち上げ時:td10=td−(t10−ta10)

C7立ち上げ時:td11=td−(t11−ta11)

C8立ち上げ時:td12=td−(t12−ta12)

C8立ち下げ時:td13=td−(t13−ta13)

C7立ち下げ時:td14=td−(t14−ta14)

C6立ち下げ時:td15=td−(t15−ta15)

C5立ち下げ時:td16=td−(t16−ta16)

【0170】

これにより、第4のプッシュプル増幅器では、立ち上げ時だけでなく立ち下げ時にも実際の入力信号に基づいて演算を行って、tdだけ遅延されたプッシュプル増幅器の出力信号よりも早く、且つトランジスタが飽和しないタイミングで制御信号を立ち下げ、出力信号の立ち上がりだけでなく立ち下がりに対してもコレクタ電圧を追随させて、出力信号における歪特性を改善できるものである。

【0171】

[第4の実施の形態の効果]

本発明の第4の実施の形態に係る電源回路によれば、スイッチ制御部83′が、コレクタ電圧の各レベルにおける立ち上がり/立ち下がりの遷移を直線近似した場合の傾きを予め記憶しておき、入力信号としきい値とを比較して、その大小と変化の向きに基づいて各スイッチ制御信号のHレベル/Lレベルを決定し、スイッチ制御信号を立ち上げる際には、信号電圧によりトランジスタが飽和しない最も早いタイミングを算出し、スイッチ制御信号を立ち下げる際には、信号電圧によりトランジスタが飽和しない最も遅いタイミングを算出して、そのタイミングを切り替えタイミングta(n)とし、信号がしきい値を超えた/下回った時刻t(n)と当該切り替えタイミングとの差分(t(n)−ta(n))を、特定の遅延時間(td)から差し引いた時間を、スイッチ制御信号の遅延時間(タイミング遅延時間)としているので、タイミング制御部121でtdだけ遅延された信号に対して、コレクタ電圧の遷移時間を考慮して最適な遅延時間でスイッチ制御信号の立ち上げ/立ち下げを行って、トランジスタを飽和させることなく、コレクタ電圧を出力信号に追随させることができ、出力信号における歪特性を改善することができる効果がある。

【0172】

特に、第4の電源回路では、実際の入力信号に基づいてスイッチ制御信号の立ち上げ/立ち下げの最適なタイミングを演算で算出しているので、広帯域信号の急峻な立ち上がりや立ち下がりに対しても迅速に追随するコレクタ電圧を供給でき、電力変換効率を向上させると共に出力信号の歪を改善することができる効果がある。

つまり、第4の電源回路では、実際の入力信号波形に応じてスイッチをオン/オフする最適なタイミングを決めることが可能であり、効率を一層向上させる効果がある。

また、第4の電源回路を、図12に示したET方式やEER方式の電力増幅器の電源回路として用いることにより、電力増幅器全体の効率を一層向上させることができる効果がある。

【0173】

[別のプッシュプル増幅器に適用した場合:図11]

次に、上述した第1〜第4の電源回路に別の構成のプッシュプル増幅器を適用した例について図11を用いて説明する。図11は、第2の電源回路に用いられる別のプッシュプル増幅器の構成を示す説明図である。

図11に示すように、別のプッシュプル増幅器の構成は、図7に示した第2のプッシュプル増幅器の構成とほぼ同様であるが、NPNトランジスタ17にコレクタ電圧を供給する第1の電源電圧供給回路と、PNPトランジスタ18にコレクタ電圧を供給する第2の電源電圧供給回路において、図7のプッシュプル増幅器とはダイオードの接続が異なっている。

【0174】

他の構成部分は第2のプッシュプル増幅器と同様であり、タイミング制御部121及びスイッチ制御部83′の動作も同じである。

【0175】

別のプッシュプル増幅器の第1の電源電圧供給回路は、直列に接続された直流電圧源とスイッチ、及びそれらに並列に接続されたダイオードから成るブロックB1〜B4を備えており、ブロックB1〜B4が全て直列に接続されているのではなく、各ダイオード71〜74のカソードが、それぞれノード90に接続されて、NPNトランジスタ17側の直流電圧源81の−側(負側)に接続されている。

【0176】

同様に、別のプッシュプル増幅器の第2の電源電圧供給回路は、ブロックB5〜B8のダイオード75〜78が、それぞれノード91に接続されて、PNPトランジスタ18側の直流電圧源82の+側(正側)に接続されている。

【0177】

このように、各ブロックのダイオードが独立してNPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に接続することにより、直流電圧源51〜54の内のいくつが選択された場合でも、ダイオードは1つしか接続されないため、常にダイオード1つ分の順方向電圧のみが差し引かれることになり、NPNトランジスタ17及びPNPトランジスタ18に供給する電源を安定させることができるものである。

【0178】

つまり、別のプッシュプル増幅器の構成によれば、電流が通過するダイオードの数を減らすことが可能であり、上述した実施の形態1〜4の構成例のように複数のダイオードを通過する場合と比較して、ダイオードの順方向電圧による電圧降下を抑制することができ、効率を一層向上させる効果がある。

【0179】

また、別のプッシュプル増幅器は、第2の電源回路だけでなく、第3、第4の電源回路に適用することも可能である。

また、タイミング制御部121を備えない構成とすれば、第1のプッシュプル増幅器と同様に動作し、第1のプッシュプル増幅器の効果に加えて、どの状態でもダイオードの順方向電圧を一定にして電源を安定させることができる効果が得られるものである。

【産業上の利用可能性】

【0180】

本発明は、広帯域の高周波信号で無線通信を行う送信機の電力増幅器で用いられ、電力変換効率を向上させることができる電源回路に適している。

【符号の説明】

【0181】

1,8...入力端子、 2...分配器、 3...包絡線検波器、 4...電源回路、 5...RFリミット増幅器、 6...主増幅器、 7,9,10...出力端子、 11...DC/DCコンバータ、 12...プッシュプル増幅器、 13...スイッチ素子、 14,20,21...ダイオード、 15...インダクタンス、 16...オペアンプ、 17...NPNトランジスタ、 18...PNPトランジスタ、 19,22...抵抗器、 23,24,51,52,53,54,55,56,57,58,81,82...直流電圧源、 25...電流検出器、 26...ヒステリシスコンパレータ、 61,62,63,64,65,66,67,68...スイッチ、 71,72,73,74,75,76,77,78...ダイオード、 83,83′...スイッチ制御部、 101,142...NPNトランジスタコレクタ電圧、 102,143...PNPトランジスタコレクタ電圧、 103,113,141...出力信号、111...理想的な波形、 112...実際の波形、 121...タイミング制御部、 131...入力信号、 201...電圧電源、 202...平滑回路、 203...スイッチ回路、 204...トランス、 205,206,207,208...整流平滑回路、 209...誤差増幅器、 210...フォトカプラ、 211...制御回路、 212...ドライバ回路

【技術分野】

【0001】

本発明は、広帯域の高周波信号で無線通信を行う送信機の電力増幅器で用いられる電源回路に係り、特に、電力変換効率を向上させることができる電源回路に関する。

【背景技術】

【0002】

[先行技術の説明]

送信機の電力増幅器への要求として、設置場所の制約や据付コストの低減のために、小型・軽量化が強く求められている。装置の体積・重量は、電力損失によって発生する熱を放熱するための放熱フィンが多くを占めるが、電力効率を改善することで放熱フィンを小さくすることが可能になり、小型・軽量化に寄与する。

【0003】

[電力効率を改善する電力増幅器:図12]

電力効率を改善する方法として、電力増幅器に入力される信号の電圧振幅に応じて、電力増幅器に印加する電源電圧を制御するET(Envelop Tracking)方式や、飽和型の電力増幅器の電源電圧を変動させるEER(Envelop Elimination and Restoration)方式がある。

【0004】

ET方式及びEER方式の電力増幅器について図12を用いて説明する。図12(a)はET方式の電力増幅器を示す概略構成図であり、(b)はEER方式の電力増幅器を示す概略構成図である。

[ET方式の電力増幅器:図12(a)]

図12(a)に示すように、ET方式の電力増幅器は、入力端子1と、分配器2と、包絡線検波器3と、電源回路4と、主増幅器6と、出力端子7とを備えている。

具体的には、入力端子1と、分配器2と、主増幅器6と、出力端子7が直列に接続されており、分配器2には包絡線検波器3が接続され、包絡線検波器3には電源回路4が接続され、電源回路4は主増幅器6に接続されて電源を供給する構成となっている。

【0005】

ET方式では、入力端子1から入力されたRF信号を分配器2で分配し、一方を包絡線検波器3に入力して包絡線を抽出し、電源回路4に入力する。電源回路4は主増幅器6に印加する電源電圧を主増幅器6の出力における包絡線と同等または僅かに大きい電圧で変動させる。

したがって、主増幅器6に印加される電源電圧と、出力信号振幅の差が小さく抑えられることになり、主増幅器6は電力ロスが小さい領域で動作することが可能となるものである。

【0006】

[EER方式の電力増幅器:図12(b)]

図12(b)に示すように、EER方式の電力増幅器は、入力端子1と、分配器2と、包絡線検波器3と、電源回路4と、RFリミット増幅器5と、主増幅器6と、出力端子7とを備えている。

つまり、分配器2と主増幅器6との間にRFリミット増幅器5が設けられて主増幅器6への入力電圧を制限している点が(a)に示したET方式の電力増幅器とは異なっている。

【0007】

そして、上記構成のEER方式の電力増幅器では、入力端子1から入力されたRF信号は、分配器2で分配され、一方は包絡線検波器3で検波されて包絡線信号が電源回路4に入力される。そして、電源回路4は、主増幅器6の電源電圧を包絡線信号に従って変動させる。

分配器2で分配された他方のRF信号は、RFリミット増幅器5で振幅変動分が除去され、位相情報のみを保ちながら主増幅器6で増幅される。

主増幅器6の電源電圧は、包絡線検波器3からの振幅情報に従って変動するので、振幅情報は復元され、主増幅器6は常に飽和状態で動作するため高効率となる。

【0008】

[高速動作可能な電源回路:図13]

ところで、ET方式やEER方式の電力増幅器全体における効率を考えた場合、主増幅器6だけでなく、電源回路4の効率も重要になってくる。

W−CDMA(Wideband-Code Division Multiple Access)信号やOFDM(Orthogonal Frequency Division Multiplexing)信号のような広帯域信号の包絡線信号の帯域は広く、電源回路4は高速に動作する必要がある。

【0009】

高速に動作する電源回路としては、例えば、非特許文献1や非特許文献2に記載されている(非特許文献1,2参照)。

高速に動作する電源回路には、線形増幅回路としてプッシュプル増幅器を使用し、DC/DCコンバータとしてD級回路を使用したものがある。

このような電源回路の構成例について図13を用いて説明する。図13は、高速に動作する電源回路の例を示す構成図である。

【0010】

図13に示すように、高速に動作する電源回路(高速動作用電源回路)は、主として、入力端子8と、広帯域の電圧源であるプッシュプル増幅器12と、制御回路である電流検出器25及びヒステリシスコンパレータ26と、高効率なDC/DCコンバータ11と、出力端子9とから構成されている。

尚、プッシュプル増幅器12は、請求項に記載したプッシュプル増幅部に相当する。

【0011】

そして、入力端子8は、図12に示した包絡線検波器3の出力段に接続され、出力端子9は、図12に示した主増幅器6の電源端子に接続される。

電流検出器25は、例えば抵抗から構成される。

また、DC/DCコンバータ11は、電圧電源と、スイッチ素子13と、ダイオード14と、インダクタンス15とを備えている。

プッシュプル増幅器12については後述する。

【0012】

[DC/DCコンバータ11の動作]

DC/DCコンバータ11の動作について簡単に説明する。

包絡線検波器3の出力がDC成分の場合、DC/DCコンバータ11は、追従モードで動作して、スイッチ素子13を自励周波数で周期的にオン/オフする。

また、包絡線検波器3の出力がDC成分と高い周波数のAC成分になると、DC/DCコンバータ11は、非追従モードで動作し、AC高周波成分を基本とする周波数でスイッチ素子13をオン/オフする。このとき、DC/DCコンバータ11は、DC成分のみを出力し、高い周波数のAC成分はプッシュプル増幅器12から出力される。

【0013】

[電源回路の効率]

図13に示した高速動作用電源回路では、自励周波数を高くして追従できるAC成分を増やすことで、つまり、高効率なDC/DCコンバータ11から出力するエネルギーの割合を増やすことで、電源回路の高効率化を試みることが考えられる。

しかし、WiMAX(Worldwide Interoperability for Microwave Access)やLTE(Long Term Evolution)などの広帯域な通信システムでは、包絡線も広帯域になるため、DC/DCコンバータ11のスイッチング周波数を上げると、スイッチング損失が大きくなり、電源回路の効率は低下する。

【0014】

そこで、適切な回路定数を設定することにより、WiMAXやLTE等の広帯域な通信システムでは、周波数の低いAC成分は、効率の高いDC/DCコンバータ11から供給し、周波数の高いAC成分は、プッシュプル増幅器12から供給するようにしている。

【0015】

[電源回路の大電流への対応]

ところで、主増幅器6の出力電力が大きい場合には、電源回路4からも多くの電流を供給する必要がある。

図13の高速動作用電源回路において、DC/DCコンバータ11では、スイッチ素子13、ダイオード14、インダクタンス15として、必要な電流を流せる部品を選択すればよい。

しかしながら、プッシュプル増幅器12に用いられるオペアンプについては、一般的に大電流を流せる部品はない。そこで、オペアンプの出力にNPNトランジスタとPNPトランジスタを接続して、出力できる電流の容量を増やしている。

【0016】

[プッシュプル増幅器の構成:図13]

次に、従来の高速動作用電源回路におけるプッシュプル増幅器(従来のプッシュプル増幅器)の構成について図13を用いて説明する。

図13に示すように、従来のプッシュプル増幅器12は、オペアンプ16と、バイアス回路を構成する抵抗器19、ダイオード20、ダイオード21、抵抗器22と、プッシュプル回路のNPNトランジスタ17、PNPトランジスタ18と、直流電圧源23と、直流電圧源24とで構成されている。

【0017】

そして、上記構成のプッシュプル増幅器12において、入力信号は入力端子8を通ってオペアンプ16の+端子に入力され、オペアンプの−端子へは出力信号がフィードバックされる。

ダイオード20は、NPNトランジスタ17のベース−間の電圧降下を、ダイオード21はPNPトランジスタ18のベース−エミッタ間の電圧降下を補償するためのものであり、抵抗器19、抵抗器22と共にバイアス回路を構成する。

【0018】

直流電圧源24よりも高い電圧値に設定される直流電圧源23に接続されたNPNトランジスタ17と、直流電圧源23よりも低い電圧値に設定される直流電圧源24に接続されたPNPトランジスタ18はプッシュプル動作により増幅を行う。

そして、NPNトランジスタ17は基準電圧よりも高い電圧を出力し、PNPトランジスタ18は基準電圧よりも低い電圧を出力する。

【0019】

NPNトランジスタ17及びPNPトランジスタ18の出力波形は、正弦波を半波整流した波形となり、これはB級にバイアスされた増幅器に相当する。プッシュプル増幅器12の出力波形は、NPNトランジスタ17の出力波形とPNPトランジスタ18の出力波形とを合成したものとなる。

【0020】

[B級増幅器の電力変換効率:図14]

ここで、B級増幅器の電力変換効率について説明する。

B級増幅器が正弦波を出力するときの電力変換効率ηは、式1で表されることが知られている。

η=π/4×Vomax/Vdd (式1)

式1をNPNトランジスタ17について説明すると、Vddは直流電圧源23の電源電圧であり、Vomaxは、NPNトランジスタ17の出力電圧の最大値である。

【0021】

式1において、VomaxがVddと同じ電圧の場合、つまり飽和出力時の電圧変換効率ηは78.5%となるが、最大出力電圧Vomaxが下がると電力変換効率ηも低下する。

【0022】

図14は、B級増幅器の電力変換効率特性を示す説明図である。

図14では、出力電圧に対する電力変換効率ηを表しており、横軸のバックオフは、Vomax/Vddを対数で表したものである。

バックオフが0dBの点が飽和出力を示しており、このときの電力変換効率ηは、上述したように78.5%となり、バックオフが大きくなると(最大出力電圧Vomaxが低下すると)電力変換効率ηは低下し、バックオフが−8dBの時の電力変換効率ηは、30%となる。

【0023】

[プッシュプル増幅器の電力変換効率:図14]

式1及び図14では、NPNトランジスタ17について説明したが、PNPトランジスタ18についても同様のことが言えるため、プッシュプル増幅器12全体の特性も式1及び図14で表すことができるものである。

尚、プッシュプル増幅器12では、オペアンプ16やバイアス回路も電力を消費するが、NPNトランジスタ17及びPNPトランジスタ18の電流増幅率hfeが大きく、オペアンプ16の消費電力はプッシュプル増幅器12のそれと比較すると僅かであるため、プッシュプル増幅器12の電力変換効率は、図14に示した特性とほぼ一致する。

【0024】

[OFDM信号における包絡線信号のスペクトラムの累積確率密度分布例:図15]

ここで、OFDM信号における包絡線信号の累積確率密度分布について図15を用いて説明する。図15は、OFDM信号における包絡線信号の累積確率密度分布の例を示す説明図である。

図15では、帯域幅10MHz、PAPR(Peak to Average Power Ratio):8dBのOFDM変調信号の包絡線を求め、電力の累積確率密度分布をDCから10MHzまでプロットしている。

【0025】

上述したように、電源回路4は、DC成分と低い周波数成分はDC/DCコンバータ11から供給し、高い周波数成分はプッシュプル増幅器12から供給するが、仮に、3MHz未満をDC/DCコンバータ11から供給し、3MHz以上をプッシュプル増幅器12が供給するとした場合、図15から、電源回路4が供給する電力の内、DC/DCコンバータ11から90%の電力を、プッシュプル増幅器12から10%の電力を供給することになる。

【0026】

[OFDM信号での電源回路の電力変換効率:図14]

OFDM信号での電源回路4の電力変換効率について説明する。

DC成分と低い周波数成分を供給するDC/DCコンバータ11の電力変換効率は、スイッチ素子13のオン抵抗や、スイッチング損失、ダイオードの順方向電圧、インダクタンス14の損失などで決まり、ηdとする。

【0027】

一方、OFDM信号のPAPRは8dBであるから、プッシュプル増幅器12の電力変換効率は、図10からわかるように、バックオフ−8dBのときの電力変換効率となる。ここでは、このときの電力変換効率をηbとする。

【0028】

つまり、電源回路4が主増幅器6に供給する電力の内、10%を電力変換効率ηbのプッシュプル増幅器12から、90%を電力変換効率ηdのDC/DCコンバータ11から供給することになる。よって、電源回路4の電力変換効率ηsは式2で計算できる。

ηs=1/(10%/ηb+90%/ηd) (式2)

仮に、ηb=30%、ηd=90%として計算すると、ηs=75%となる。

電源回路4全体の電力変換効率を改善するためには、電力変換効率の低いプッシュプル増幅器12の効率をあげることが必要である。

【0029】

従来のプッシュプル増幅器12では、NPNトランジスタ17のコレクタ端子及びPNPトランジスタ18のコレクタ端子に接続される直流電圧源23及び直流電圧源24の電圧は、出力レベルに関係なく一定であるため、出力レベルが下がるに従って電力変換効率も低下する。

【先行技術文献】

【非特許文献】

【0030】

【非特許文献1】"An Improved Power-Added Efficiency 19-dBm Hybrid Envelope Elimination and Restoration Power Amplifier for 802.11g WLAN Applications" , Feipeng Wang et al., IEEE TRANSACTIOINS ON MICROWAVE THEORY AND TECHNIQUES, VOL. 54, NO. 12, DECEMBER 2006, P. 4086-4099

【非特許文献2】"A Class B Switch- Mode Assisted Linear Amplifier" , Geoffrey R. Walker, IEEE TRANSACTIONS ON POWER ELECTRONICS, VOL. 18. No. 6, NOVEMBER 2003, p.1278-1285

【発明の概要】

【発明が解決しようとする課題】

【0031】

しかしながら、従来のプッシュプル増幅器では、NPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧が、出力レベルにかかわらず一定レベルであるため、出力レベルが下がると電力変換効率が低下してしまうという問題点があった。

【0032】

尚、非特許文献1、2には、プッシュプル増幅器のNPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧を、出力レベルに応じて調整することは記載されていない。

【0033】

本発明は、上記実状に鑑みて為されたもので、プッシュプル増幅器のNPNトランジスタ及びPNPトランジスタのコレクタ端子に接続される直流電圧源の電圧を、出力レベルに応じて調整して、出力レベルが下がっても電力変換効率が低下しない電源回路を提供することを目的とする。

【課題を解決するための手段】

【0034】

上記従来例の問題点を解決するための本発明は、電力増幅に用いられる電源回路であって、入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、プッシュプル増幅部に入力される入力信号を遅延させるタイミング調整部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力する制御部とを備え、制御部が、制御信号の立ち上げの場合に、タイミング調整部での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げることを特徴としている。

【0035】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち上げ及び立ち下げの電圧レベル切り替えに対応して、タイミング調整部での遅延時間から遷移時間を差し引いた時間をタイミング遅延時間として記憶しており、制御信号の立ち上げの場合に、入力信号のタイミングから前記タイミング遅延時間だけ遅延させたタイミングで前記制御信号を立ち上げることを特徴としている。

【0036】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち上げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち上げの場合に、検出された入力信号と傾きとに基づいて、制御信号を立ち上げるタイミングを算出して、当該算出されたタイミングで制御信号を立ち上げることを特徴としている。

【0037】

また、本発明は、上記電源回路において、制御部が、制御信号の立ち下げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる代わりに、検出された入力信号と傾きとに基づいて、制御信号を立ち下げるタイミングを算出して、算出されたタイミングで制御信号を立ち下げることを特徴としている。

【0038】

また、本発明は、ET方式の電力増幅器であって、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を前記主増幅器に供給することを特徴としている。

【0039】

また、本発明は、EER方式の電力増幅器であって、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器と、入力信号の電圧を制限して主増幅器に出力するリミット増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を主増幅器に供給することを特徴としている。

【発明の効果】

【0040】

本発明によれば、電力増幅に用いられる電源回路であって、入力信号をプッシュプル増幅方式で増幅するプッシュプル増幅部と、制御信号によりプッシュプル増幅部に提供する電源電圧の電圧レベルを可変とする可変電源部と、プッシュプル増幅部に入力される入力信号を遅延させるタイミング調整部と、入力信号に基づいて電源電圧の電圧レベルを制御する制御信号を出力する制御部とを備え、制御部が、制御信号の立ち上げの場合に、タイミング調整部での遅延時間に対して電圧レベル切り替えの遷移時間に応じた早いタイミングで制御信号を立ち上げ、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる電源回路としているので、出力レベルが下がっても電力変換効率を低下させず、電圧レベルの立ち上がりに要する遷移時間の影響を低減し、出力信号の立ち上がり波形に追随した電源電圧を供給でき、効率を向上させると共に増幅部での飽和を防ぎ、出力信号の歪特性を改善することができる効果がある。

【0041】

また、本発明によれば、制御部が、制御信号の立ち上げ及び立ち下げの電圧レベル切り替えに対応して、タイミング調整部での遅延時間から遷移時間を差し引いた時間をタイミング遅延時間として記憶しており、制御信号の立ち上げの場合に、入力信号のタイミングから前記タイミング遅延時間だけ遅延させたタイミングで前記制御信号を立ち上げる上記電源回路としているので、制御信号を、出力信号より遷移時間分早いタイミングで立ち上げる処理を容易に行うことができる効果がある。

【0042】

また、本発明によれば、制御部が、制御信号の立ち上げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち上げの場合に、検出された入力信号と傾きとに基づいて、制御信号を立ち上げるタイミングを算出して、当該算出されたタイミングで制御信号を立ち上げる上記電源回路としているので、実際の信号波形に基づく適切なタイミングで制御信号を立ち上げ、急峻な立ち上がりを含む広帯域信号に対しても電源電圧を追随させ、出力信号の歪特性を改善することができる効果がある。

【0043】

また、本発明によれば、制御部が、制御信号の立ち下げの切り替えに対応する電圧レベルの遷移の傾きを記憶しており、制御信号の立ち下げの場合に、遅延時間のタイミングで制御信号を立ち下げる代わりに、検出された入力信号と傾きとに基づいて、制御信号を立ち下げるタイミングを算出して、算出されたタイミングで制御信号を立ち下げる上記電源回路としているので、実際の信号波形に基づく適切なタイミングで制御信号を立ち下げ、急峻な立ち下がりを含む広帯域信号に対しても電源電圧を追随させ、出力信号の歪特性を改善することができる効果がある。

【0044】

また、本発明によれば、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を前記主増幅器に供給するET方式の電力増幅器としているので、出力信号の立ち上がり/立ち下がりの波形によく追随した電源電圧を供給でき、電力増幅器全体の効率を向上させると共に出力信号の歪特性を改善することができる効果がある。

【0045】

また、本発明によれば、入力信号を検波する包絡線検波器と、プッシュプル増幅部の出力段にD級回路を設けた上記電源回路と、入力された信号を増幅する主増幅器と、入力信号の電圧を制限して主増幅器に出力するリミット増幅器とを備え、電源回路が、包絡線検波器で検出された包絡線に応じた電源電圧を主増幅器に供給するEER方式の電力増幅器としているので、出力信号の立ち上がり/立ち下がりの波形によく追随した電源電圧を供給でき、電力増幅器全体の効率を向上させると共に出力信号の歪特性を改善することができる効果がある。

【図面の簡単な説明】

【0046】

【図1】本発明の第1の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

【図2】第1のプッシュプル増幅器におけるスイッチ制御信号の一例と、それに伴うトランジスタのコレクタ電圧及び出力波形を示す説明図である。

【図3】第1のプッシュプル増幅器の電力変換効率特性を示す説明図である。

【図4】NPNトランジスタ17のコレクタ端子に直流電圧を供給する直流電圧源回路の構成例を示すブロック図である。

【図5】遷移時間がない場合の出力信号波形とコレクタ端子の電位との関係を示す説明図である。

【図6】NPNトランジスタ17のコレクタ電圧の遷移時間を示す説明図である。

【図7】本発明の第2の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

【図8】第2のプッシュプル増幅器におけるスイッチ制御信号の制御タイミングを示す説明図である。

【図9】第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係を示す説明図である。

【図10】コレクタ電圧の遷移状態における傾きを直線近似する場合の説明図である。

【図11】第2の電源回路に用いられる別のプッシュプル増幅器の構成を示す説明図である。

【図12】(a)はET方式の電力増幅器を示す概略構成図であり、(b)はEER方式の電力増幅器を示す概略構成図である。

【図13】高速に動作する電源回路の例を示す構成図である。

【図14】B級増幅器の電力変換効率特性を示す説明図である。

【図15】OFDM信号における包絡線信号の累積確率密度分布の例を示す説明図である。

【図16】スイッチ制御信号C1の立ち上げタイミングの算出方法を示す説明図である。

【図17】スイッチ制御信号C1の立ち下げタイミングの算出方法を示す説明図である。

【発明を実施するための形態】

【0047】

本発明の実施の形態について図面を参照しながら説明する。

[実施の形態の概要]

本発明の実施の形態に係る電源回路は、プッシュプル増幅器に、スイッチと直流電圧源が直列に接続され、更にそれらに並列にダイオードが接続された回路部を1つの回路ブロックとして、複数の回路ブロックが直列に接続された第1と第2の電源電圧生成回路を備え、当該第1と第2の電源電圧生成回路が、それぞれNPNトランジスタのコレクタ端子及びPNPトランジスタのコレクタ端子に接続され、スイッチ制御部が、入力信号レベルに応じて、複数のブロックの直流電圧源をNPNトランジスタ又はPNPトランジスタのコレクタ端子に接続するスイッチのオン/オフを制御する制御信号を出力して、NPNトランジスタ及びPNPトランジスタのコレクタ電圧を入力信号レベルに応じて制御して、出力レベルに追従したコレクタ電圧とすることができ、出力レベルが低い場合でも飽和に近い動作を可能とし、電源回路全体の電力変換効率を改善することができるものである。

【0048】

また、本発明の実施の形態に係る電源回路は、上記電源回路において、更に、タイミング調整部を設け、タイミング調整部が入力信号を一定時間遅延すると共に、スイッチ制御部が、各スイッチのオン/オフを制御する制御信号の切り替え時には、当該遅延時間よりもコレクタ電圧の電圧レベルに応じたレベル切り替えの遷移時間分早く制御信号の立ち上げを行うようにしているので、コレクタ電圧のレベル切り替わりに要する遷移時間の影響を低減し、電源回路の出力波形の歪を改善することができるものである。

【0049】

また、本発明の実施の形態に係る電源回路は、上記電源回路において、スイッチ制御部が、予め記憶しているコレクタ電圧の電圧レベルに応じたレベル切替の傾きと、検出された入力信号レベルとに基づいて、制御信号の立ち上げ又は立ち下げのタイミングを算出し、当該タイミングで制御信号を立ち上げ又は立ち下げるようにしているので、実際の信号波形に基づいて制御信号の出力タイミングを決定することができ、電源回路の出力波形の歪を改善することができるものである。

【0050】

[第1の実施の形態:図1]

本発明の第1の実施の形態に係る電源回路は、図13に示した従来の電源回路と同様に、プッシュプル増幅器とDC/DCコンバータとを備えている。

本発明の第1の実施の形態に係る電源回路について図1を用いて説明する。図1は、本発明の第1の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

図1に示すように、本発明の第1の実施の形態に係る電源回路(第1の電源回路)に用いられるプッシュプル増幅器(第1のプッシュプル増幅器)は、図13に示した従来のプッシュプル増幅器と同様の部分として、入力端子8と、出力端子10と、オペアンプ16と、バイアス回路を構成する抵抗器19と、ダイオード20と、ダイオード21と、抵抗器22と、プッシュプル回路を構成するNPNトランジスタ17と、PNPトランジスタ18と、直流電圧源23と、直流電圧源24とを備えている。従来のプッシュプル増幅器と同様の構成部分は、請求項に記載したプッシュプル増幅部に相当する。

【0051】

そして、第1のプッシュプル増幅器の特徴部分として、スイッチ制御部83と、NPNトランジスタ17のコレクタに接続する直流電圧源81及び複数の回路ブロックB1〜B4と、PNPトランジスタ18のコレクタに接続する直流電圧源82及び複数の回路ブロックB5〜B8とを備えている。

直流電圧源81,82の電圧をそれぞれV9,V10とする。

直流電圧源81及び複数の回路ブロックB1〜B4と、直流電圧源82及び複数の回路ブロックB5〜B8は請求項に記載した可変電源部に相当する。

【0052】

[回路ブロックB1〜B4]

NPNトランジスタ17側の回路ブロックB1〜B4の構成について説明する。

回路ブロックB1〜B4は、それぞれ、直流電圧源(51〜54)と、スイッチ(61〜64)と、ダイオード(71〜74)とを備え、各ブロックにおいて、ダイオードのアノードには直流電圧源の−側(負側)が接続され、カソードにはスイッチを介して直流電圧源の+側(正側)が接続されている。

【0053】

更に、回路ブロックB1のダイオード71のアノードは接地され、カソードは回路ブロックB2のダイオード72のアノードに接続されている。以下同様にして、回路ブロックB3,B4のダイオード73,74が直列に接続されて、回路ブロックB4のカソードは、直列電圧源81の−側(負側)に接続されている。

直列に接続された回路ブロックB1〜B4から成る回路を第1の電源電圧生成回路とする。

【0054】

そして、スイッチ61〜64は、後述するスイッチ制御部83からのスイッチ制御信号C1〜C4によってオン/オフが制御され、スイッチがオンとなった回路ブロックの直流電圧源の電圧と直流電圧源81の電圧が加算されて、基準電圧に対して正の電圧がNPNトランジスタ17のコレクタ端子に印加されるようになっている。

つまり、スイッチで選択された直流電圧源と直流電圧源81とが直列接続となる。

尚、回路ブロックB1〜B4の直流電圧源51,52,53,54の電圧を、V1,V2,V3,V4とする。

【0055】

[回路ブロックB5〜B8]

同様に、PNPトランジスタ18側の回路ブロックB5〜B8は、それぞれ、直流電圧源(55〜58)と、スイッチ(65〜68)と、ダイオード(75〜78)とを備え、各ブロックにおいて、ダイオードのアノードには直流電圧源の−側が接続され、カソードにはスイッチを介して直流電圧源のプラス側が接続されている。

【0056】

また、回路ブロックB8のダイオード78のカソードは接地され、アノードは回路ブロックB7のダイオード77のカソードに接続されている。以下同様にして、回路ブロックB6,B5のダイオード76,75が直列に接続されて、回路ブロックB5のアノードは、直列電圧源82の+側に接続されている。

直列に接続された回路ブロックB5〜B8から成る回路を第2の電源電圧生成回路とする。

第1の電源電圧生成回路及び第2の電源電圧生成回路は、請求項に記載した可変電源部に相当する。

【0057】

そして、スイッチ65〜68は、後述するスイッチ制御部83からのスイッチ制御信号C5〜C8によってオン/オフが制御され、スイッチがオンとなった回路ブロックの直流電圧源の電圧と直流電圧源82の電圧が加算されて、基準電圧に対して負の電圧がPNPトランジスタ18のコレクタ端子に印加されるようになっている。

つまり、スイッチで選択された直流電圧源と直流電圧源82が直列接続となる。

尚、回路ブロックB5〜B8の直流電圧源55,56,57,58の電圧を、V5,V6,V7,V8とする。

スイッチ制御信号C1〜C4、C5〜C8は、請求項に記載した選択信号に相当する。

【0058】

[スイッチ制御部83]

次に、第1のプッシュプル増幅器の特徴部分であるスイッチ制御部83について説明する。

スイッチ制御部83は、入力端子8から入力される信号(包絡線信号)に基づいて、NPNトランジスタ17のコレクタ端子に印加される電圧を適切な値とするよう、回路ブロックB1〜B4のスイッチ61,62,63,64のオン/オフを制御するスイッチ制御信号C1,C2,C3,C4を出力する。

【0059】

同様に、スイッチ制御部83は、包絡線信号に基づいて、PNPトランジスタ18のコレクタ端子に印加される電圧を適切な値とするよう、回路ブロックB5〜B8のスイッチ65,66,67,68のオン/オフを制御するスイッチ制御信号C5,C6,C7,C8を出力する。

【0060】

具体的には、スイッチ制御部83は、8種類のスイッチ制御信号のそれぞれを、ハイレベル(Hレベル、オン)又はローレベル(Lレベル、オフ)として出力する制御信号生成回路を備えており、入力された包絡線信号に基づいて、Hレベル又はLレベルの各スイッチ制御信号を出力する。

スイッチ制御部83の各制御信号生成回路は、例えばコンパレータ回路によって構成される。

【0061】

これにより、第1のプッシュプル増幅器では、入力信号の電力レベルに応じて、出力電圧に追随したコレクタ電圧をNPNトランジスタ17及びPNPトランジスタ18に印加することができ、プッシュプル増幅器の電力変換効率を向上させ、電源回路全体の効率を向上させることができるものである。

【0062】

[第1のプッシュプル増幅器の動作:図1]

まず、回路ブロックB1〜B4,B5〜B8の動作について簡単に説明する。

各回路ブロックB1〜B4、B5〜B8では、ダイオードのアノード端子は直流電圧源の負側に、カソード端子は直流電圧源の正側に接続されている。このような回路ブロックB1〜B4、B5〜B8を直列に接続し、各スイッチのオン/オフを制御することにより、電圧を加算してNPNトランジスタ17、PNPトランジスタ18のコレクタ端子に印加することが可能となる。

【0063】

スイッチがONの場合には、当該回路ブロックの直流電圧源の電圧が加算され、電流は直流電圧源を流れ、回路が動作する。このとき、ダイオードには順方向の逆電圧があるため電流は流れない。

また、スイッチがオフの場合には、当該回路ブロックの直流電圧源の回路が開放になっているため、電圧は加算されないが、電流はダイオードを流れ、回路は動作する。

【0064】

そして、第1のプッシュプル増幅器では、スイッチ制御部83が、入力端子8から入力される包絡線信号に応じて、スイッチ制御信号C1〜C8をHレベル又はLレベルに切り替えて出力し、対応する回路ブロックのスイッチのオン/オフを制御する。

これにより、入力電力レベルに応じて、基準電圧に対して正のコレクタ電圧をNPNトランジスタ17に印加し、基準電圧に対して負のコレクタ電圧をPNPトランジスタ18に印加するものである。

【0065】

[スイッチ制御信号とトランジスタのコレクタ電圧:図2]

次に、第1のプッシュプル増幅器におけるスイッチ制御信号とトランジスタのコレクタ電圧の関係について図2を用いて説明する。図2は、第1のプッシュプル増幅器におけるスイッチ制御信号の一例と、それに伴うトランジスタのコレクタ電圧及び出力波形を示す説明図である。

図2の(a)には、スイッチ制御信号C1〜C8の例を示しており、スイッチ制御信号C1〜C8のそれぞれについて、各制御信号がスイッチをオンにする状態(Hレベル)であるか、或いはスイッチをオフにする状態(Lレベル)であるかを表している。

【0066】

図2(a)の例では、スイッチ制御信号C1は、時間T1まではLレベルであり、時間T1〜T8の期間はHレベルであり、時間T8以降は再びLレベルとなっている。

また、スイッチ制御信号C8は、時間T12まではLレベルであり、時間T12〜T13の期間はHレベルであり、時間T13以降はLレベルとなっている。

【0067】

図2(b)では、(a)のスイッチ制御信号C1〜C8が与えられた場合のNPNトランジスタ17のコレクタ電圧(ノードA電圧)と、PNPトランジスタ18のコレクタ電圧(ノードB電圧)と、出力電圧波形とを示している。尚、基準電圧としては、例えばゼロ(0)が用いられる。

【0068】

上述したように、第1のプッシュプル増幅器では、スイッチ制御信号C1〜C8がHレベルである場合に、対応するスイッチ61〜68がオンとなる。

図2において、まず、ノードA電圧に着目して説明する。

時間が0からT1までの間は、スイッチ制御信号C1〜C4が全てLレベルであるため、スイッチ61〜64は全てオフである。

従って、電流は、直流電圧源51〜54には流れずダイオード71〜74を流れ、ノードAには直流電圧源81の電圧V9が印加される。

尚、本実施の形態では、ダイオード71〜78の順方向電圧はゼロとして説明する。

【0069】

続いて、時間T1からT2までの間は、スイッチ制御信号C1のみがHレベルで、その他のスイッチ制御信号C2〜C4はLレベルであるので、スイッチ61のみがオンとなる。

スイッチ61に対応する直流電圧源51と直流電圧源81は直列に接続されているので、ノードAの電圧は、V9+V1となる。

つまり、つまりスイッチがオンになる回路ブロックの直流電圧源の電圧が、直流電圧源81の電圧V9に加算され、当該加算された電圧がノードAに印加されることになる。

【0070】

以下同様にして、時間T2,T3,T4で、スイッチ制御信号C2,C3,C4がそれぞれHレベルとなれば、それに応じてスイッチ62,63,64がオンとなり、ノードAの電圧には、更に電圧V2,V3,V4が加算される。

【0071】

更に、時間T5,T6,T7,T8で、スイッチ制御信号C4,C3,C2,C1がLレベルとなり、スイッチ64,63,62,61がオフになると、ノードAの電圧は、図2に示すように電圧V4,V3,V2,V1が減算される。

【0072】

ノードBの電圧についても、ノードAと同様に、スイッチ制御信号C5〜C8で制御されるスイッチ65〜68がオン又はオフに切り替えられることで図2に示すように変化する。時間T9〜T16の期間に変化するノードBの電圧は、時間T1〜T8におけるノードAの電圧に対して正負が逆になっている。

【0073】

[スイッチ制御部83の動作:図1,図2]

次に、スイッチ制御部83の動作について図1及び図2を用いて説明する。

上述したように、スイッチ制御部83は、入力信号から検出された包絡線信号に基づいて、スイッチ制御信号C1〜C8をHレベル又はLレベルとして出力する。

その結果、ノードAの電圧を制御するためのスイッチ61〜64を制御するスイッチ制御信号C1〜C4は、出力波形が正のときに変化する。

【0074】

スイッチ制御部83は、入力される包絡線信号に基づいて、スイッチ制御信号C1を、出力波形の電圧がV9よりも大きいときにHレベルとする。

また、スイッチ制御部83は、スイッチ制御信号C2を出力波形の電圧がV9+V1よりも大きいときにHレベルとし、スイッチ制御信号C3を出力波形の電圧がV9+V1+V2よりも大きいときにHレベルとし、スイッチ制御信号C4を出力波形の電圧がV9+V1+V2+V3よりも大きいときにHレベルとする。

その他の条件では、スイッチ制御部83は、スイッチ制御信号C1〜C4をLレベルとする。

【0075】

同様に、ノードBの電圧を制御するためのスイッチ65〜68を制御するスイッチ制御信号C5〜C8は、出力波形が負のときに変化する。

スイッチ制御部83は、入力される包絡線信号に基づいて、スイッチ制御信号C5を、出力波形の電圧が−V10よりも小さいときにHレベルとし、スイッチ制御信号C6を出力波形の電圧が−V10−V5よりも小さいときにHレベルとし、スイッチ制御信号C7を出力波形の電圧が−V10−V5−V6よりも小さいときにHレベルとし、スイッチ制御信号C8を出力波形の電圧が−V10−V5−V6−V7よりも小さいときにHレベルとする。

その他の条件では、スイッチ制御部83は、スイッチ制御信号C5〜C8をLレベルとする。

【0076】

スイッチ制御部83は、このような条件でスイッチ制御信号C1〜C8が動作するよう構成され、コンパレータ回路を用いて容易に実現できる。このコンパレータ回路にはヒステリシス特性を持たせてもよい。

【0077】

図1に示したように、第1のプッシュプル増幅器では、スイッチ制御部83は、入力端子8から入力される包絡線信号からスイッチ制御信号C1〜C8を生成するため、入力レベルに対する出力レベルの利得を考慮して設計されている。

【0078】

また、各直流電圧源の電圧V1〜V10は同じ電圧値でもよいし、それぞれ異なる電圧値であってもよい。

更に、ここではノードAの電圧及びノードBの電圧はそれぞれ5段階に変化するように構成されているが、何段であっても構わない。

【0079】

更にまた、第1のプッシュプル増幅器では、出力波形と、V9,V1,V2,V3,V4又はV10,V5,V6,V7,V8を組み合わせて加算または減算したしきい値とを比較して各スイッチ制御信号のレベル(H又はL)を決めているが、必ずしもそのようにする必要はない。

【0080】

[第1のプッシュプル増幅器の効率:図3]

次に、第1のプッシュプル増幅器の効率について図3を用いて説明する。図3は、第1のプッシュプル増幅器の電力変換効率特性を示す説明図である。

上述したように、第1のプッシュプル増幅器では、NPNトランジスタ17のコレクタ端子(ノードA電圧)及びPNPトランジスタ18のコレクタ端子(ノードB)電圧は、出力波形に応じて変化する。

【0081】

つまり、出力波形が小さいときはコレクタ端子電圧の絶対値も小さくなるようにノードA及びノードBの電圧を制御することにより、第1のプッシュプル増幅器は、常に飽和出力に近い状態で動作する。

【0082】

そのため、図3に示すように、第1のプッシュプル増幅器の電力変換効率は、図14に示した従来方式と比較して向上する。特に、飽和出力よりも低い出力において、効率向上が顕著である。

例えば、OFDM信号に相当するバックオフ−8dBのときの電力変換効率は、図14の従来のプッシュプル増幅器では30%であったのが、第1のプッシュプル増幅器では55%に向上している。

【0083】

[直流電圧源回路の構成:図4]

次に、NPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に直流電圧を供給する直流電圧源回路の構成について図4を用いて説明する。図4は、NPNトランジスタ17のコレクタ端子に直流電圧を供給する直流電圧源回路の構成例を示すブロック図である。尚、図1に示した直流電圧源51〜54に相当する部分は同一の符号を付してある。

また、ここでは、NPNトランジスタ17側の直流電圧源回路についてのみ説明するが、PNPトランジスタ18側の直流電圧源回路も同様の構成である。

【0084】

図1に示したように、直流電圧源51〜54と直流電圧源81、直流電圧源55〜58と直流電圧源82は、スイッチ61〜64、スイッチ65〜68がオンになった場合に直列接続になるため、絶縁型電源にする必要がある。

【0085】

図4に示すように、第1のプッシュプル増幅器の直流電圧源回路は、電源を供給する入力端子201と、入力端子201から供給された電源電圧を平滑化する平滑回路202と、スイッチ回路203と、入力と複数の出力を絶縁するためのトランス204と、出力電圧の整流と平滑を行う整流平滑回路205〜208と、目標とする出力電圧との誤差を検出する誤差増幅器209と、誤差情報を制御回路に渡す際に絶縁するためのフォトカプラ210と、誤差情報を最小にすることで目標の出力電圧に制御するための制御回路211と、スイッチ回路203を駆動するためのドライバ回路212とを備えている。

【0086】

上記構成の直流電圧源回路の動作について説明する。

入力端子201から電圧Vinが入力されると、平滑回路202により平滑化され、スイッチ回路203を介してトランス204の入力側に入力される。

トランス204の出力側には、各直流電圧源51〜54の電圧値に応じた巻き数のコイルが設けられ、巻き数に応じて変換された電圧が整流平滑回路205〜208を介して、それぞれ直流電圧源51〜54の出力電圧となる。

【0087】

直流電圧源51〜54の電圧は、V1〜V4であり、直流電圧源54が目標電圧V4になるように制御する。

具体的には、直流電圧源54を監視し、誤差増幅器209で検出した直流電圧源54の電圧と目標電圧との差分である誤差信号をフォトカプラ210を介して制御回路211に入力し、制御回路211が、誤差信号が小さくなるようスイッチ回路203をオン/オフする信号のデューティー比を変えることにより、目標電圧V4とするよう制御する。

【0088】

直流電圧源51,52,53については監視を行わないが、直流電圧源54の電圧がV4になった場合に直流電圧源51,52,53の電圧がV1,V2,V3となるようにトランス204の巻き数を設計しておけばよい。

【0089】

[第1の実施の形態の効果]

本発明の第1の実施の形態に係る電源回路によれば、プッシュプル増幅器に、スイッチと直流電圧源が直列に接続され、更にそれらに並列にダイオードが接続された回路部を1つの回路ブロックとして、複数の回路ブロックB1〜B4が直列に接続された第1の電源電圧生成回路と、複数の回路ブロックB5〜B8が直列に接続された第2の電源電圧生成回路とを備え、第1の電源電圧生成回路が、NPNトランジスタ17のコレクタ端子に接続され、第2の電源電圧生成回路が、PNPトランジスタ18のコレクタ端子に接続され、スイッチ制御部83が、包絡線検波器3からの入力信号の包絡線信号に応じて、複数の回路ブロックB1〜B8のスイッチ61〜68のオン/オフを制御するスイッチ制御信号C1〜C8を出力するようにしているので、NPNトランジスタ17及びPNPトランジスタ18のコレクタ電圧を入力信号レベルに応じて、出力信号レベルに追従するよう制御して、常に飽和に近い動作を可能とし、プッシュプル増幅器の出力レベルが低い場合の電力変換効率を改善し、電源回路全体の電力変換効率を向上させることができる効果がある。

【0090】

更に、第1の電源回路を、例えばEER方式の増幅器に用いることにより、増幅器全体の効率を向上させ、消費電力を低減でき、放熱フィンを小さくして、小型化・軽量化を図ることができる効果がある。

【0091】

尚、上述した例では、直流電圧源81,82は、常時ノードA,ノードBに印加されるよう構成されているが、スイッチ及びダイオードを追加して回路ブロックとし、他の直流電圧源と同様にオン/オフを切り替えられるようにしてもよい。

【0092】

また、NPNトランジスタ17,PNPトランジスタ18のコレクタ電圧を生成する電源電圧生成回路の構成は、図1に示したものに限らず、スイッチ制御部からの制御信号によって異なる電圧を出力する回路であればどのような構成であってもよい。

【0093】

[第2の実施の形態]

次に、本発明の第2の実施の形態に係る電源回路について説明する。

[遷移時間を無視した場合のコレクタ電圧の例:図1、図5]

第2の実施の形態について具体的に説明する前に、図1に示した第1のプッシュプル増幅器において、コレクタ電圧の電位が、あるレベルから次のレベルに遷移する際の遷移時間がない場合の、出力信号波形とコレクタ電圧との関係について図1及び図5を用いて説明する。図5は、遷移時間がない場合の出力信号波形とコレクタ端子の電位との関係を示す説明図である。

尚、図5においては、各ブロックのダイオードの順方向電圧を考慮したコレクタ電圧を示している。

【0094】

図5に示すように、スイッチ制御部83は、NPNトランジスタ17及びPNPトランジスタ18のエミッタ端子に出力されるプッシュプル増幅器の出力電圧波形103と、しきい値Vth1〜Vth8の大小関係に基づいて、上述した電源電圧生成回路の各スイッチ61〜68をオン状態又はオフ状態にするスイッチ制御信号を出力する。

尚、図1の構成では、スイッチ制御部83は、入力信号の包絡線信号に基づいて、出力電圧としきい値との関係に応じた各スイッチ制御信号を生成している。

【0095】

その結果、コレクタ電圧が切り替わる際の遷移時間がないものとすると、NPNトランジスタ17のコレクタ電圧は、101に示すような波形となり、PNPトランジスタ18のコレクタ電圧は、102に示す波形となる。

【0096】

ここで、ダイオード71〜78の順方向電圧をそれぞれ、VF1,VF2,VF3,VF4,VF5,VF6,VF7,VF8とすると、例えば、図1に示したスイッチ61とスイッチ62のみがオン状態で、その他のスイッチがオフ状態の場合、電流は、直流電圧源51,52、ダイオード73,74、直流電圧源81を経由して、NPNトランジスタ17に流れ込むことになる。

この場合のNPNトランジスタ17のコレクタ単位おける電圧Vcは、

Vc=V1+V2+V9−VF3−VF4

となる。

【0097】

また、NPNトランジスタ17及びPNPトランジスタ18は、プッシュプル回路として動作しているため、NPNトランジスタ17が動作している期間では、NPNトランジスタ17のコレクタ端子とエミッタ端子の電位差は、NPNトランジスタ17が飽和しない程度に大きい必要がある。同様にPNPトランジスタ18が動作している期間においては、PNPトランジスタ18のコレクタ端子とエミッタ端子の電位差が十分に大きい必要がある。

コレクタ端子とエミッタ端子の電位差が、トランジスタの飽和電圧よりも小さくなった場合、トランジスタが飽和して、プッシュプル増幅器から出力される信号に歪が生じる。

【0098】

そこで、図5に示すように、プッシュプル増幅器の出力波形のレベルを判定するしきい値(Vth1〜Vth8)を以下のように設定する。

Vth1<V9−VF1−VF2−VF3−VF4−Vce(npn:sat)

Vth2<V9+V1−VF2−VF3−VF4−Vce(npn:sat)

Vth3<V9+V1+V2−VF3−VF4−Vce(npn:sat)

Vth4<V9+V1+V2+V3−VF4−Vce(npn:sat)

Vth5>−V10+VF5+VF6+VF7+VF8+Vce(pnp:sat)

Vth6>−V10−V5+VF6+VF7+VF8+Vce(pnp:sat)

Vth7>−V10−V5−V6+VF7+VF8+Vce(pnp:sat)

Vth8>−V10−V5−V6−V7+VF8+Vce(pnp:sat)

【0099】

ここで、Vce(npn:sat)は、NPNトランジスタ17が飽和するコレクタ−エミッタ間電圧であり、Vce(pnp:sat)は、PNPトランジスタ18が飽和するコレクタ−エミッタ間電圧である。

これにより、スイッチ制御部83からの制御信号によってどのコレクタ電圧値が選択された場合でも、NPNトランジスタ17及びPNPトランジスタ18のコレクタ端子とエミッタ端子の電位差を、トランジスタが飽和しない程度に確保できるものである。

【0100】

[コレクタ電圧の遷移時間:図6]

次に、NPNトランジスタ17及びPNPトランジスタ18のコレクタに印加されるコレクタ電圧の遷移時間について図6を用いて説明する。図6は、NPNトランジスタ17のコレクタ電圧の遷移時間を示す説明図である。

図6では、プッシュプル増幅器12の出力波形例113に対するNPNトランジスタ17のコレクタ電圧の理想的な波形111と、実際の波形112の例を示している。

【0101】

EER方式の電源回路では、プッシュプル増幅器12の出力波形113の変化に追随して、コレクタ電圧を変化させる。

図6の例では、コレクタ電圧の電圧レベルを、プッシュプル増幅器の出力波形113のレベル増加に伴って、時刻tにおいてVc(i)から次の電圧レベルVc(i+1)に切り替え、出力波形113のレベル低下に伴って、再び電圧レベルVc(i)に切り替えている。

【0102】

時刻tにおいて、スイッチ制御部83からの指示により、スイッチ61〜65のいずれかがオフ状態からオン状態となって、NPNトランジスタ17のコレクタ端に印加されている電圧が、Vc(i)からVc(i+1)に切り替わった場合、電圧レベルを遷移させる遷移時間が不要であれば、理想的な信号波形111のように階段状の波形となる。

【0103】

しかし、実際の信号波形112は、図6に示すように有限の切り替え時間(遷移時間)Δtを伴う応答となる。また、PNPトランジスタ18におけるコレクタ電圧の切り替え時の波形は、波形112の上下を反転させた波形となる。

【0104】

[広帯域信号の場合]

ここで、プッシュプル増幅器12に入力される信号が、広帯域なW−CDMA信号やOFDM信号の場合、出力波形113に示されるように急峻な立ち上がりや立下りを有する場合がある。

このような場合、コレクタ電圧の切り替えが間に合わずに、プッシュプル増幅器のコレクタ端の電位とエミッタ端の電位との差が飽和電圧を下回ると、トランジスタは飽和してプッシュプル増幅器12の出力信号波形に歪が発生してしまう。

【0105】

[遷移時間の短縮]

そのため、コレクタ電圧の電圧レベルの遷移時間を短くする必要がある。

遷移時間は、スイッチ61〜68やスイッチ制御部83の応答速度や、回路の各部に内在する寄生容量や寄生インダクタンスなどにより決まり、応答速度の速い素子や、寄生容量・寄生インダクタンスの少ない素子を使用して、回路レイアウトを最適化することである程度の改善は可能である。

しかし、広帯域信号の包絡線の急峻な立ち上がり/立下りに反応できるよう、遷移時間を十分短くすることは依然として困難であった。

【0106】

また、遷移時間の短縮を図るため、電圧レベルを急峻に切り替えようとすると、コレクタ電圧に、振幅が波打つように変化するリンギングを発生することがあり、リンギングが大きいとコレクタ端子の電位とエミッタ端子の電位との差が小さくなって出力信号に歪が発生しやすい。

つまり、リンギングを許容範囲内としつつ、コレクタ電圧の遷移時間を十分短縮することは困難であった。

【0107】

そこで、本発明の第2の実施の形態では、コレクタ電圧の切り替え時の遷移時間が、リンギングを許容範囲内とする程度の時間であっても広帯域信号のレベル変化に十分追随でき、出力信号の歪特性を劣化させない電源回路を提供する。

【0108】

[第2の実施の形態の構成:図7]

本発明の第2の実施の形態に係る電源回路は、第1の電源回路と同様に、プッシュプル増幅器とDC/DCコンバータとを備えている。

本発明の第2の実施の形態に係る電源回路で用いられるプッシュプル増幅器の構成について図7を用いて説明する。図7は、本発明の第2の実施の形態に係る電源回路に用いられるプッシュプル増幅器の構成図である。

図7に示すように、本発明の第2の実施の形態に係る電源回路(第2の電源回路)に用いられるプッシュプル増幅器(第2のプッシュプル増幅器)は、基本的な構成は、図1に示した第1のプッシュプル増幅器と同じであり、図1と同一の符号を付して説明する。

【0109】

第2のプッシュプル増幅器は、新たにタイミング制御部121を備えている点が特徴であり、また、スイッチ制御部83′の構成及び動作が第1のプッシュプル増幅器のスイッチ制御部83とは一部異なっている。

【0110】

[第2のプッシュプル増幅器の動作概略]

ここで、第2のプッシュプル増幅器の動作について簡単に説明する。

第2のプッシュプル増幅器は、コレクタ電圧の遷移時間を考慮して、入力信号を十分遅延させ、広帯域信号が入力された場合であってもコレクタ電圧が十分追随できるようにしているものである。

【0111】

具体的には、第2のプッシュプル増幅器では、入力された信号を、コレクタ電圧の遷移時間よりも大きい一定の遅延時間(td)だけ遅延させてオペアンプ16に入力すると共に、遅延させない入力信号に基づいて生成した制御信号C1〜C8を、当該遅延時間(td)からコレクタ電圧の遷移時間(Δt)を差し引いた時間(td−Δt)だけ遅延させて立ち上げる。

【0112】

これにより、スイッチ制御信号C1〜C8は、トランジスタのエミッタ端における出力信号に対して、遷移時間(Δt)分だけ早いタイミングで出力されることになり、入力信号に急峻な変化があっても、コレクタ電圧がそれに追随して変化して、出力信号における歪特性が劣化するのを防ぐことができるものである。

尚、実際には、コレクタ電圧の遷移時間は、電圧レベル毎に異なる時間となっている。

【0113】

[第2のプッシュプル増幅器の各部]

第2のプッシュプル増幅器の特徴部分について具体的に説明する。

[タイミング制御部121]

タイミング制御部121は、入力端子8から入力された信号を、予め設定された特定の遅延時間tdだけ遅延させて、オペアンプ16に出力する。

遅延時間tdは、コレクタ電圧の、どの電圧レベルにおける遷移時間よりも長い時間としている。

タイミング制御部121は、請求項に記載したタイミング調整部に相当する。

【0114】

[スイッチ制御部83′]

スイッチ制御部83′は、第1のプッシュプル増幅器におけるスイッチ制御部83と同様に、入力端子8から入力される包絡線信号に基づいて、スイッチ制御信号C1〜C8を生成するものであるが、スイッチ制御信号の出力(レベルの切り替え)のタイミングを第1のプッシュプル増幅器に比べて遅くしているものである。

【0115】

スイッチ制御部83′は、スイッチ制御信号C1〜C8を生成するコンパレータ回路に加えて、生成されたスイッチ制御信号C1〜C8を出力するタイミングを制御する制御回路を備えている。制御回路は、処理部及び記憶部を備えたマイコン等で構成される。

尚、スイッチ制御部83′は、請求項に記載した制御部に相当する。

【0116】

スイッチ制御部83′からのスイッチ制御信号C1〜C8のレベル(ハイレベル又はローレベル)の組み合わせによって決定されるNPNトランジスタ17及びPNPトランジスタ18のコレクタ電圧について説明する。

ここでは、各回路ブロックB1〜B8のダイオード71〜78の順方向電圧(VF1〜VF8)を考慮している。

【0117】

第2のプッシュプル増幅器におけるNPNトランジスタ17のコレクタ端子に印加される電圧をVc1〜Vc5、PNPトランジスタ18のコレクタ端子に印加される電圧をVc6〜Vc10とすると、図7の構成ではコレクタ電圧のレベルは10段階であり、

Vc1=V9−VF1−VF2−VF3−VF4

Vc2=V9+V1−VF2−VF3−VF4

Vc3=V9+V1+V2−VF3−VF4

Vc4=V9+V1+V2+V3−VF4

Vc5=V9+V1+V2+V3+V5

Vc6=−V10+VF5+VF6+VF7+VF8

Vc7=−V10−V5+VF6+VF7+VF8

Vc8=−V10−V5−V6+VF7+VF8

Vc9=−V10−V5−V6−V7+VF8

Vc10=−V10−V5−V6−V7−V8

となる。

【0118】

上述したように、コレクタ電圧を切り替える際の遷移時間は、電圧レベル毎に異なっており、電圧レベルVc1からVc2に切り替わるために必要な遷移時間をΔt1とする。

同様に、電圧レベルVc2からVc3への遷移時間をΔt2、電圧レベルVc3からVc4への遷移時間をΔt3、電圧レベルVc4からVc5への遷移時間をΔt4、電圧レベルVc6からVc7への遷移時間をΔt5、電圧レベルVc7からVc8への遷移時間をΔt6、電圧レベルVc8からVc9への遷移時間をΔt7、電圧レベルVc9からVc10への遷移時間をΔt8とする。

遷移時間Δt1〜Δt8の値は、プッシュプル増幅器の特性や回路を構成する各素子の特性や回路定数、更には電力増幅器の主増幅器6の特性などによって決まる値であり、設計段階で把握することが可能な値である。

【0119】

第2のプッシュプル増幅器のスイッチ制御部83′では、予め、各コレクタ電圧の切り替えレベル(Vc1→Vc2,Vc2→Vc3,...Vc9→Vc10)と、その電位の変化に要する遷移時間(Δt1〜Δt8)とを対応付けて記憶している。

尚、ここでは、遷移時間は、制御信号の立ち上がり時(スイッチをオンにする場合)のみについて考慮しており、立下り時の遷移時間は考慮していない。

つまり、スイッチ制御部83′では、各スイッチ制御信号C1〜C8の立ち上げ時の遷移時間をΔt1〜Δt8として記憶しているものである。

【0120】

そして、第2のプッシュプル増幅器の特徴として、スイッチ制御部83′では、コレクタ電圧の切り替えレベル毎に、スイッチ制御信号C1〜C8のレベルを切り替えるタイミングを遅延させる時間(タイミング遅延時間)を記憶したテーブルを備えている。

【0121】

尚、実際には、スイッチ制御部83′は、プッシュプル増幅器12への入力信号に基づいて制御を行うので、入力信号と予め設定された複数のしきい値との大小関係及び入力信号の変化の向き、つまり各スイッチ制御信号C1〜C8の立ち上がり又は立ち下げに対応して、タイミング遅延時間を記憶している。

つまり、スイッチ制御部83′は、各スイッチ制御信号C1〜C8のそれぞれについて、立ち上げ時及び立ち下げ時のタイミングを遅延するタイミング遅延時間をメモリに記憶しているものである。

【0122】

第2のプッシュプル増幅器では、スイッチ制御信号の立ち上がりの場合(スイッチをオンにする場合)には、タイミング遅延時間として、タイミング制御部121における遅延時間tdから各切り替えレベルに対応した遷移時間を減算した時間(td−Δt)を記憶している。

また、スイッチ制御信号の立下りの場合には、タイミング遅延時間として、タイミング制御部121における遅延時間tdを記憶している。

各スイッチ制御信号のタイミング遅延時間については後述する。

【0123】

[第2のプッシュプル増幅器におけるスイッチ制御信号のタイミング:図8]

次に、第2のプッシュプル増幅器におけるスイッチ制御信号のタイミングについて図8を用いて説明する。図8は、第2のプッシュプル増幅器におけるスイッチ制御信号の制御タイミングを示す説明図である。

図8では、プッシュプル増幅器の入力端子8から入力信号131が入力された場合の、スイッチ制御信号C1〜C8を示している。スイッチ制御信号C1〜C8がLレベルの時には、対応するスイッチ61〜68がオフ状態となり、スイッチ制御信号C1〜C8がHレベルの時には、対応するスイッチ61〜68がオン状態となる。

【0124】

スイッチ制御部83′は、入力信号131を、予め記憶しているしきい値Vth1〜Vth8と比較して、スイッチ制御信号C1〜C8のレベル(Hレベル又はLレベル)を決定して、入力信号131としきい値との大小関係及び変化の向きに対応して予め記憶しているタイミング遅延時間だけ遅延したタイミングで出力する。

【0125】

図8に示すように、信号波形131が、しきい値Vth1よりも大きくなる時刻をt1とし、Vth2,Vth3,Vth4よりも大きくなる時刻をそれぞれt2,t3,t4とする。

また、信号波形131が、しきい値Vth5より小さくなる時刻をt9とし、Vth6,Vth7,Vth8よりも小さくなる時刻をそれぞれt10,t11,t12とする。

【0126】

スイッチ制御部83′は、時刻t1において信号波形131がしきい値Vth1より大きくなったことを検出すると、スイッチ制御信号C1をHレベルとするが、その際、スイッチ制御部83′は、テーブルからスイッチ制御信号C1の立ち上げ時に対応するタイミング遅延時間を読み取り、時刻t1よりも当該タイミング遅延時間だけ遅らせたタイミングでHレベルに切り替えた信号を出力する。

【0127】

上述したように、スイッチ制御信号C1の立ち上げ時のタイミング遅延時間をtd1とすると、td1は、タイミング制御部121における遅延時間tdから、スイッチ制御信号C1の立ち上げ時の遷移時間Δt1を差し引いた時間である(td1=td−Δt1)。

【0128】

同様に、スイッチ制御部83′は、NPNトランジスタ17のコレクタ電圧を切り替えるスイッチ制御信号C2〜C4を、時刻t2〜t4よりタイミング遅延時間td2〜td4だけ遅らせてLレベルからHレベルに切り替えて出力する。

また、スイッチ制御部83′は、PNPトランジスタ18のコレクタ電圧を切り替えるスイッチ制御信号C5〜C6を、時刻t9〜t12よりタイミング遅延時間td9〜td12だけ遅らせてLレベルからHレベルに切り替える。

【0129】

各スイッチ制御信号の立ち上げ時(Lレベル→Hレベル)/立ち下げ時(Hレベル→Lレベル)のタイミング遅延時間は以下のようになる。

C1立ち上げ時:td1=td−Δt1

C2立ち上げ時:td2=td−Δt2

C3立ち上げ時:td3=td−Δt3

C4立ち上げ時:td4=td−Δt4

C4立ち下げ時:td5=td

C3立ち下げ時:td6=td

C2立ち下げ時:td7=td

C1立ち下げ時:td8=td

C5立ち上げ時:td9=td−Δt5

C6立ち上げ時:td10=td−Δt6

C7立ち上げ時:td11=td−Δt7

C8立ち上げ時:td12=td−Δt8

C8立ち下げ時:td13=td

C7立ち下げ時:td14=td

C6立ち下げ時:td15=td

C5立ち下げ時:td16=td

スイッチ制御部83′には、メモリに上述したタイミング遅延時間が記憶されており、スイッチ制御信号の切り替え時は、対応するタイミング遅延時間だけ遅らせてHレベル又はLレベルに切り替えた信号を出力する。

【0130】

プッシュプル増幅器12への入力信号131は、タイミング制御部121によって遅延時間tdだけ遅延されて出力されるので、スイッチ制御信号を上述したタイミング遅延時間(td1〜td16)だけ遅らせて出力することにより、スイッチ制御信号の立ち上げ時には、プッシュプル増幅器の出力端子における信号波形に対して、コレクタ端子に印加する電圧を切り替えるタイミングを、各遷移時間分早めることが可能となる。

これにより、入力信号の立ち上がりに伴うスイッチ制御信号の立ち上げ時において、コレクタ電圧の切り替え時の遷移時間の影響を少なくすることができ、出力信号の歪特性の劣化を抑制することができるものである。

【0131】

[第2のプッシュプル増幅器の入出力信号とコレクタ電圧の例:図9]

次に、第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係について図9を用いて説明する。図9は、第2のプッシュプル増幅器の入出力信号とコレクタ電圧との関係を示す説明図である。

図9(a)に示すように、プッシュプル増幅器の入力信号131に対して、(b)に示すように、出力信号141は、タイミング制御部121によって所定の遅延時間tdだけ遅延されて出力される。

【0132】

また、出力信号141が基準電圧より大きい場合にNPNトランジスタ17のコレクタ端子に印加されるコレクタ電圧142は、上述したようなタイミング遅延時間で切り替わるスイッチ制御信号によって、出力信号141がしきい値に達するよりも早いタイミングで切り替わるため、出力信号141の変化に追従して段階的に変化している。

同様に、出力信号141が基準電圧より小さい場合にPNPトランジスタ18に印加されるコレクタ電圧143も、出力信号141の変化に追従して段階的に変化している。

【0133】

[第2の実施の形態の効果]

本発明の第2の実施の形態に係る電源回路によれば、第1の電源回路のスイッチ制御部83の代わりにスイッチ制御部83′を設け、入力信号を特定の遅延時間tdだけ遅延させるタイミング制御部121を設け、スイッチ制御部83′が、各スイッチ制御信号C1〜C8に対応して、当該スイッチ制御信号が立ち上げ/立ち下げによるNPNトランジスタ17又はPNPトランジスタ18のコレクタ電圧のレベル遷移に要する遷移時間Δtを記憶すると共に、各スイッチ制御信号C1〜C8に対応して、立ち上げ時と立ち下げ時のタイミング遅延時間を記憶しており、各スイッチ制御信号C1〜C8の立ち上げ時には、入力信号のタイミングから、当該スイッチ制御信号に対応して記憶されたタイミング遅延時間(td−Δt)だけ遅延させてHレベルに切り替え、スイッチ制御信号の立ち下げ時には、入力信号のタイミングから遅延時間tdだけ遅延させてLレベルに切り替えるようにしているので、タイミング制御部121で遅延された信号に対して、スイッチ制御信号の立ち上げ時のコレクタ電圧の遷移時間分、早くスイッチ制御信号を立ち上げることができ、コレクタ電圧の遷移時間の影響をなくして、広帯域信号の急な立ち上がりにも追随させることができ、出力信号における歪特性を改善することができる効果がある。

【0134】

また、第2の電源回路を、図12に示したET方式やEER方式の電力増幅器の電源回路として用いれば、主増幅器6の出力信号レベルに良く追随した電源電圧を主増幅器6に供給することができ、ET方式やEER方式の電力増幅器全体の効率を一層向上させることができる効果がある。

【0135】

[第3の実施の形態]

本発明の第3の実施の形態に係る電源回路(第3の電源回路)について説明する。

第3の電源回路は、プッシュプル増幅器とDC/DCコンバータとを備えており、第2の電源回路と同様の構成であるが、プッシュプル増幅器(第3のプッシュプル増幅器)12のスイッチ制御部83′におけるスイッチ制御信号の立ち上げ時の切り替えタイミングを、演算によって決定するようにしている。

【0136】

[コレクタ電圧の遷移状態における傾き:図10]

まず、コレクタ電圧の遷移状態における傾きについて図10を用いて説明する。図10は、コレクタ電圧の遷移状態における傾きを直線近似する場合の説明図である。

図10に示すように、コレクタ電圧が、ある電圧レベルVciから次の電圧レベルVc(i+1)に切り替わる場合には、矩形波形とはならずに、遷移時間Δtjで緩やかな立ち上がりとなる。

【0137】

図10の例では、コレクタ電圧の遷移状態における傾きを直線近似した場合、傾きsは、

s=(Vc(i+1)−Vci)/Δtj と表される。

コレクタ電圧の切り替えレベルに対応する遷移時間(Δt)は、上述したように、プッシュプル増幅器の特性や各素子の特性及び回路定数等により決定され、定数として予めスイッチ制御部83′に記憶されている。

従って、コレクタ電圧の切り替えレベルに対応する傾きs1〜s16も定数であり、予め記憶されている。

【0138】

[第3のプッシュプル増幅器における動作:図5,図10,図16]

第3のプッシュプル増幅器の特徴部分について図5,図10,図16を用いて説明する。

第2のプッシュプル増幅器の説明と同様に、プッシュプル増幅器12におけるNPNトランジスタ17又はPNPトランジスタ18のコレクタ端子に印加される電圧をVc1〜Vc10とする。

また、入力信号波形131がVth1〜Vth4より大きくなる時刻を、それぞれt1〜t4とし、Vth5〜Vth8より小さくなる時刻を、それぞれt9〜t12とする。

【0139】

以下、簡単のためにNPNトランジスタ17のコレクタ端に印加される電圧レベルがVc1からVc2に切り替わる場合を例にとって説明する。

まず、入力信号がしきい値Vth1より大きくなった時刻t1から遅延時間tdまでの間に含まれる任意の時刻及びその時の電圧レベルを、それぞれ時刻tn及び電圧レベルVnとする。

更に、NPNトランジスタ17が飽和しないためのマージンとなる電圧をVmとする。Vmとしては、NPNトランジスタ17の飽和電圧よりも大きい電圧値が設定される。

【0140】

そして、スイッチ制御部83′は、(式3)によって求められる時刻ta(n)を算出する。

ta(n)=(Vc1−(Vn+Vm))/s1+tn (式3)

ここで、s1は、コレクタ端子に印加される電圧がVc1からVc2に変化する際の傾きを直線近似したものである。

また、Vmは、時刻tn時の信号の電圧値Vnに対して、トランジスタを飽和させないためのマージン電圧である。

【0141】

つまり、ta(n)は、コレクタ電圧の変化を傾きs1の直線で近似した場合に、任意の時刻tnにおける信号Vnに対してトランジスタが飽和しないコレクタ電圧を供給するためのスイッチ制御信号の立ち上げタイミング(時刻)に相当する。

【0142】

[ta(n)の算出方法:図16]

ここで、第3のプッシュプル増幅器におけるスイッチ制御信号の立ち上げタイミングの算出方法について具体的に説明する。

時刻t1からt1+tdまでの間の任意の時刻tnにおけるta(n)の算出方法について、図16を用いて説明する。図16は、コレクタ電圧をVc1からVc2に切り替える場合の、スイッチ制御信号C1の立ち上げタイミングの求め方を示す説明図である。

説明を簡単にするために、図16では、この区間の任意の時刻T1、T2、T3の信号に基づいて、ta(n)を求める場合について示している。

【0143】

上述したようにta(n)は(式3)によって求められるが、図16に示すように、時刻T1,T2,T3におけるta(n)は、各時刻における信号の電圧値V1,V2,V3に、マージン電圧Vmを加算した点(Vn+Vm)を通る傾きs1の直線がコレクタ電圧Vc1と交わる点として求められる。

【0144】

図16の例では、時刻T1については(V1+Vm)を通る傾きs1の直線とVc1との交点としてta(1)が求められる。

同様にして、時刻T2についてta(2)が求められ、時刻T3についてta(3)が求められる。

そして、第3のプッシュプル増幅器のスイッチ制御部83′では、ta(1)〜ta(3)の中で最も早いタイミングであるta(2)をVc1からVc2への切り替えタイミングta1とするものである。

【0145】

このように算出されたta(n)の中で最も早いタイミングを選択することにより、傾きS1で近似されるコレクタに印加される電圧が、信号の電圧Vnよりも下回ることは無く、トランジスタの飽和を防ぐことができるものである。

【0146】

同様にして、各コレクタ電圧レベルの切り替えについても、傾きに応じてスイッチ制御信号の立ち上げ時の切り替えタイミング(ta2〜ta4、ta9〜ta12)を求める。ta2〜ta4は、スイッチ制御信号C2〜C4の立ち上げ時の切り替えタイミングであり、ta9〜ta12は、スイッチ制御信号C5〜C8の立ち上げ時の切り替えタイミングである。

【0147】

尚、第3のプッシュプル増幅器のスイッチ制御部83′には、予め、各スイッチ制御信号の立ち上げ時におけるコレクタ電圧の変化を直線近似した場合の傾きs1〜s4、s9〜s12が記憶されている。ここで、s1〜s4は、スイッチ制御信号C1〜C4の立ち上げ時の傾き、s9〜s12は、スイッチ制御信号C5〜C8の立ち上げ時の傾きを示す。

傾きs1〜s4は正の符号を持ち、傾きs9〜s12は負の符号を持つ。

【0148】

そして、第3のプッシュプル増幅器では、スイッチ制御部83′は、入力信号の電圧としきい値とを比較し、入力信号のレベルと変化の方向に基づいて切り替えを行うスイッチ制御信号を決定し、スイッチ制御信号の立ち上げ時には上述した演算処理を行って、特定の遅延時間tdより、しきい値を越えたタイミングと切り替えタイミングta1〜ta4、ta9〜ta12との差分だけ早いタイミングでスイッチ制御信号の立ち上げを行う。

【0149】

つまり、第3のプッシュプル増幅器では、スイッチ制御信号の立ち上がりの場合には、入力信号と各レベルにおけるコレクタ電圧の遷移の傾きに応じて算出された切り替えタイミング(ta(n))と、入力信号がしきい値を超えた時刻(t(n))との時間差を、タイミング制御部121における遅延時間tdから減算して、算出された時間を各スイッチ制御信号のタイミング遅延時間とする。

また、スイッチ制御信号の立ち下げ時には、特定の遅延時間tdに合わせたタイミング遅延時間とする。

【0150】

つまり、第3のプッシュプル増幅器においては、スイッチ制御信号の立ち上げ時には、遅延された信号よりも早いタイミングで立ち上げ、スイッチ制御信号の立ち下げ時には、遅延された信号に合わせたタイミングで立ち下げる。

すなわち、第3のプッシュプル増幅器における各スイッチ制御信号の立ち上げ時(Lレベル→Hレベル)/立ち下げ時(Hレベル→Lレベル)のタイミング遅延時間は以下のようになる。

C1立ち上げ時:td1=td−(t1−ta1)

C2立ち上げ時:td2=td−(t2−ta2)

C3立ち上げ時:td3=td−(t3−ta3)

C4立ち上げ時:td4=td−(t4−ta4)

C4立ち下げ時:td5=td

C3立ち下げ時:td6=td

C2立ち下げ時:td7=td

C1立ち下げ時:td8=td