高周波発生装置

【課題】 溶接電源等に内蔵されている従来の高周波発生装置では、高速サイリスタ素子を用いているため母材―電極間から放電される高周波高電圧の発生回数が少ない。

【解決手段】 商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、シャントレギュレータ等で形成されるマルチバイブレータ駆動回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、シャントレギュレータが通電するとマルチバイブレータが安定から所定時間の非安定になる単安定マルチバイブレータ回路と、共振コンデンサとトランスのインダクタンスとで形成される共振回路と、単安定マルチバイブレータ回路が非安定状態になると共振回路を駆動させるMOSFET素子と、放電ギャップと、トランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置である。

【解決手段】 商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、シャントレギュレータ等で形成されるマルチバイブレータ駆動回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、シャントレギュレータが通電するとマルチバイブレータが安定から所定時間の非安定になる単安定マルチバイブレータ回路と、共振コンデンサとトランスのインダクタンスとで形成される共振回路と、単安定マルチバイブレータ回路が非安定状態になると共振回路を駆動させるMOSFET素子と、放電ギャップと、トランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置である。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、非消耗電極の溶接トーチと被加工物との間に高周波高電圧を重畳してアークを発生させる高周波発生装置の技術に関するものである。

【背景技術】

【0002】

溶接電源、切断電源に内蔵されている従来の高周波発生装置では、高速サイリスタ素子を用いて高周波高電圧を発生させていた。

【0003】

図5は、従来技術の高周波発生装置を使用した溶接電源の電気接続図である。図5において、直流電源回路は、1次整流回路DR1と1次整流回路DR1の出力側に並列に設けた1次平滑コンデンサC1とで形成され、商用交流電源を整流及び平滑して直流電圧を生成する。

【0004】

インバータ回路INVは、図示省略の相対向する4つのスイッチング素子からフルブリッジを形成し、直流電圧を高周波交流電圧に変換して出力する。

【0005】

変圧器INTは、インバータ回路INVによって変換された高周波交流電圧をアーク加工に適した高周波交流電圧に変換し、2次整流回路DR2は、主変圧器INTの出力を整流し直流リアクトルDCLを介して非消耗電極1と被加工物Mとの間に電力を供給する。

【0006】

図5に示す、出力電流検出回路IDは、主変圧器INTの2次側の出力電流を検出して出力電流検出信号Idとして出力する。誤差増幅回路ERは、出力電流検出信号Idの値と出力電流検出信号Idの値とを誤差増幅して誤差増幅信号Erとして出力する。出力制御回路SCは、パルス周波数が一定でパルス幅を変調するPWM制御を行い、誤差増幅信号Erに応じてインバータ回路INVを制御する。

【0007】

図6は、高速サイリスタ素子を用いた従来の高周波発生回路の詳細図であり、全波整流回路DR3と第1の平滑コンデンサC2とで形成し商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路DCと、直流電源回路DCに並列に設けたフリーホィールダイオードD2及び保護抵抗R9と、脈流を有する直流電圧が所定のブレークオーバ電圧を超えると通電するサイダック素子SSSと、共振コンデンサC4とフライバックトランスTとで形成され直流電源回路DCのプラス側出力に共振コンデンサC4の一方を接続し、共振コンデンサC4の他方をフライバックトランスTの1次側の一方に接続し、フライバックトランスTの1次側の他方を直流電源回路DCのマイナス側出力に接続し成る共振回路と、共振コンデンサC4の一方にアノードを接続し、フライバックトランスTの1次側の他方にカソードを接続し、サイダック素子SSSの通電に応じてオンするサイリスタ素子SCRと、ゲート電流を供給するコンデンサC11と、フライバックトランスTの2次側に並列に設けた放電ギャップSGと、フライバックトランスTの2次側の一方に接続した複数の直列コンデンサと、フライバックトランスTの2次側の他方と直列コンデンサと間に、外部にカップリングコイルCCを設けることで高周波発生装置が形成される。

【0008】

図7は、従来技術の動作を説明する波形タイミング図である。図7において、同図(A)の波形はサイダック電流Isssを示し、同図(B)の波形はサイダック電圧Vsssを示し、同図(C)の波形はサイリスタ素子SCRのゲート電流igを示し、同図(D)の波形はサイリスタ素子SCRの通電電流Iscrを示し、同図(E)の波形はサイリスタ素子SCRの通電電圧Vscrを示し、同図(F)の波形はフリーホィールダイオードD2の通電電流Idr2、同図(J)の波形はフライバックトランスの1次側のトランス電圧Vpをし、同図(H)の波形はフライバックトランスの1次側のトランス電流Ipを示す。

【0009】

図8は、高速サイリスタ素子SCRを用いた従来の高周波発生装置の動作モードであり、4つのモードを繰り返している。そして、図7は4つの動作モードを説明する波形タイミング図であり、図7及び図8を参照して従来の技術の高周波発生装置の動作について説明する。

【0010】

図6に示す図示省略の高周波制御信号Rs、図7に示す時刻t=t0以前にスイッチSWに入力されるとスイッチSWは閉路され、直流電源回路DCは脈流を有する直流電圧を出力し、図7(B)に示すサイダック電圧Vsssが上昇し、ブレークオーバ電圧に達するとサイダック素子SSSが通電する。

【0011】

「モード1」

サイダック素子SSSが時刻t=t0のとき、ブレークオーバ電圧に達して通電しているので、図7(C)に示すサイリスタ素子SCRのゲート電流igが上昇し、高速サイリスタ素子SCRがオンする。SCRがオンするとSSSの電圧はブレークオーバ電圧以下となるのでSSSは遮断するが、SCRはオンしているのでSSSの電圧は上昇しない。このときゲート電流はC11より供給される。このとき図7及び図8に示すMODE1に移行し、フライバックトランスTの1次側に流れていた電流の方向が逆転し、高速サイリスタ素子SCRに図7(D)に示す通電電流Iscrが流れ込む。このとき共振コンデンサC4とフライバックトランスTの1次側の漏れインダクタンスにより共振が起こり、高速サイリスタ素子SCRの電流はゼロから傾きを持ちながら上昇するためソフトスイッチング動作、すなわちゼロ電流スイッチング(ZCS)でターンオンする。

【0012】

「モード2」

図7(D)に示す、高速サイリスタ素子SCRの通電電流Iscrが減少し共振電流がゼロになると、高速サイリスタ素子SCRがターンオフし、図7及び図8に示すMODE2に移行し、フリーホィールダイオードD2へ図7(F)示す通電電流Idr2が流れ始める。この時、フライバックトランスTの1次側のトランス電流Ipは正方向へと変わる。

【0013】

「モード3」

図7(D)に示すフリーホィールダイオードD2へ流れる通電電流Idr2が減少し、時刻t=t2において、通電電流Idr2がゼロになると図7及び図8に示すMODE3に移行し、サイダック素子SSS、高速サイリスタ素子SCR、共振コンデンサC4の電圧が上昇を始める。

【0014】

「モード4」

共振コンデンサC4の電圧の上昇に応じて図7(B)に示すサイダック電圧Vsssが上昇し、ブレークオーバ電圧に達すると、図7及び図8に示すMODE4に移行し、サイダック素子SSSが再度通電する。このときコンデンサC11が充電される。そして、以後、MODE1に戻り上述と同一動作を繰り返す。

上述より、TIG溶接等のアークスタート時に、溶接トーチと被加工物との間に高周波高電圧を重畳してアークを発生させるとき、図6に示す高周波発生装置が一般的に使用されている。

(例えば、特許文献1)

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開昭61−7070号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

TIG溶接、プラズマ切断等に使用する高周波発生装置では、母材―電極間で放電する高電圧の発生回数が多くなるとアークのスタート性が良いことが知られている。一般に駆動素子のスイッチング周波数が高くなると母材―電極間で放電する高電圧の発生回数も多くなるという関係がある。従来の高周波発生装置を形成する共振回路では、スイッチング周波数の高速化を図るために駆動素子として応答速度の速いサイリスタ素子を使用していた。しかし、高速のサイリスタ素子を用いても応答速度に限界があり、スイッチング周波数の最大値は、例えば、30KHz近傍にあり、放電ギャップで放電する高電圧の周波数が不充分でアークのスタート性に問題があった。

【0017】

そこで、本発明では、母材―電極間で放電する高電圧の発生回数を充分多くできる高周波発生装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

上述した課題を解決するために、第1の発明は、全波整流回路と平滑コンデンサとでなり商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、前記直流電源回路の出力側に並列に設けた第1の抵抗器と第2の抵抗器とを直列接続し、この接続した中接点とシャントレギュレータのリファレンス、前記シャントレギュレータのアノードと前記直流電源回路のマイナス側出力とを接続して形成されるマルチバイブレータ駆動回路と、前記直流電源回路のプラス側出力に第3の抵抗器の一方を接続し、前記第3の抵抗器の他方と第2の平滑コンデンサの一方及び第1のツェナダイオードのカソードとを接続し、前記第2の平滑コンデンサの他方及び前記第1のツェナダイオードのアノードと前記直流電源回路のマイナス側出力とを接続し形成し、前記第1のツェナダイオードのカソードからマルチバイブレータ電圧を出力するマルチバイブレータ電源回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、マルチバイブレータ駆動回路の前記シャントレギュレータが通電すると前記マルチバイブレータが安定状態から所定時間の非安定状態になる単安定マルチバイブレータ回路と、前記直流電源回路のプラス側出力に共振コンデンサの一方を接続し、前記共振コンデンサの他方にフライバックトランスの1次側の一方に接続し、前記フライバックトランスの1次側の他方を前記直流電源回路のマイナス側出力に接続して形勢される共振回路と、前記共振コンデンサの一方にドレイン側を接続し、前記フライバックトランスの1次側の他方にソース側を接続し前記単安定マルチバイブレータ回路が非安定状態になると前記共振回路を駆動させるMOSFET素子と、前記フライバックトランスの2次側に並列に設けた放電ギャップと、前記フライバックトランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置である。

【発明の効果】

【0019】

上述した課題を解決するために、本発明では、高周波発生装置を形成する共振回路の駆動素子として、高速のサイリスタ素子に代えてMOSFET素子を使用する。このとき、MOSFET素子のスイッチング速度はスイッチング損失値によって抑制がかかる。そこで、MOSFET素子のターンオン及びターンオフのとき、ソフトスイッチング動作、即ちゼロ電流スイッチング(ZCS)を行なうことでスイッチング損失を大きく減少させ、このスイッチング損失の減少値に応じてMOSFET素子の高速スイッチングが可能になる。そして、共振回路の共振周波数の最大値、例えば、30KHz近傍に対して70KHz近傍まで高速化され、この高速化により放電ギャップで放電する高電圧の周波数も高くなるのでアークのスタート性が向上する。

【図面の簡単な説明】

【0020】

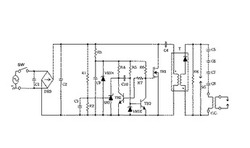

【図1】本発明の実施の形態1に係る高周波発生装置の詳細図である

【図2】本発明の高周波発生装置の1次側のブロック図である。

【図3】本発明の動作を説明する波形タイミング図である。

【図4】本発明の動作を説明する動作モード図である。

【図5】従来技術の高周波発生装置を使用した溶接電源の電気接続図である。

【図6】従来技術の高周波発生装置の詳細図である

【図7】従来技術の動作を説明する波形タイミング図である。

【図8】従来技術の動作を説明する動作モード図である。

【発明を実施するための形態】

【0021】

図1は、本発明の実施の形態1に係る高周波発生装置の詳細図である。同図において、図6に示す、従来技術の高周波発生装置の詳細図と同一符号の構成物は、同一動作を行なうので説明は省略し符号の相違する構成物についてのみ説明する。

【0022】

次に、図1及び図2を用いて構成について説明する。

図2に示す直流電源回路DCは、図1に示す全波整流回路DR3と平滑コンデンサC2とで形成し商用交流電源を整流し脈流を有する直流電圧として出力する。単安定マルチバイブレータ駆動回路MDは、図1に示す直流電源回路DCの出力側に並列に設けた第1の抵抗器R1と第2の抵抗器R2とを直列接続し、この直列接続の中接点とシャントレギュレータSR1のリファレンスRefを接続し、且つ、シャントレギュレータSR1のアノードAを直流電源回路DCのマイナス側出力に接続して形成する。

【0023】

図2に示すマルチバイブレータ電源回路CDは、直流電源回路DCのプラス側出力に第3の抵抗器R3の一方を接続し第3の抵抗器R3の他方に第2の平滑コンデンサC9の一方及び第1のツェナダイオードVRD1のカソードKとを接続し、第2の平滑コンデンサC9の他方及び第1のツェナダイオードVRD1のアノードAと直流電源回路のマイナス側出力とを接続して形成し、直流電源回路DCからの直流電圧を下記に示すMOSFET素子のゲートに適応した電圧レベルに変換して出力する。

【0024】

図2に示す単安定マルチバイブレータ回路MBは、マルチバイブレータ電源回路CDの出力(第3の抵抗器R3の他方と第2の平滑コンデンサC9の一方の接続点)と第4の抵抗器R4、第5の抵抗器R5及び第6の抵抗器R6の一方を接続し、第4の抵抗器R4の他方とシャントレギュレータSR1のカソードK、第1のスイッチング素子TR2のコレクタ及び周波数設定用コンデンサC10の一方とを接続し、第5の抵抗器R5の他方と周波数設定用コンデンサの他方、第2のスイッチング素子TR3のベース及び第2のツェナダイオードVR2のカソードとを接続し、第6の抵抗器R6の他方と第1のスイッチング素子TR2のベース及び第2のスイッチング素子TR3のコレクタとを接続し、直流電源回路DCのマイナス側出力と第1のスイッチング素子TR2のエミッタ、第2のツェナダイオードVRD2のアノード及び第2のスイッチング素子TRのエミッタとを接続して形成し、シャントレギュレータSR1のカソードK、アノードA間が通電すると安定状態から非安定状態に移行する。

【0025】

図2に示す共振駆動回路RDは、図1に示す共振コンデンサC4の一方にMOSFET素子TR1のドレイン側を接続し、前記フライバックトランスTの1次側の他方にMOSFET素子TR1のソース側を接続したMOSFET素子TR1から形成される。

【0026】

共振回路は、図1に示す直流電源回路DCのプラス側出力に共振コンデンサC4の一方を接続し共振コンデンサC4の他方にフライバックトランスTの1次側の一方に接続し、フライバックトランスの1次側の他方を直流電源回路DCのマイナス側出力に接続して成る。

【0027】

図3は、本発明の動作を説明する波形タイミング図である。図3において、同図(A)の波形は、シャントレギュレータSR1の通電電流Isr1を示し、同図(B)の波形は、シャントレギュレータSR1のリファレンス電圧Vrefを示し、同図(C)の波形は、MOSFET素子TR1のゲート電圧Vgを示し、同図(D)の波形は、MOSFET素子TR1のドレイン電流Itr1を示し、同図(E)の波形は、MOSFET素子TR1のドレイン・ソース間電圧Vtr1を示し、同図(F)の波形は、フライバックトランスの1次側のトランス電圧Vpを示し、同図(G)の波形は、フライバックトランスの1次側のトランス電流Ipを示し、同図(H)の波形は、第1のスイッチング素子TR2のコレクタ・エミッタ間電圧VceTR2を示し、同図(I)の波形は、第1のスイッチング素子TR2のベース・エミッタ間電圧VbeTR2を示し、同図(J)の波形は、第1のスイッチング素子TR2のコレクタ電流IcTR2を示し、同図(K)の波形は、第1のスイッチング素子TR2のベース電流IbTR2を示し、同図(L)の波形は、第2のスイッチング素子TR2のベース、エミッタ間電圧VbeTR3を示し、同図(M)の波形は、第2のスイッチング素子TR3のコレクタ電流IcTR3を示し、同図(N)の波形は、第2のスイッチング素子TR3のベース電流IbTR3を示し、同図(O)の波形は、周波数設定用コンデンサC10の放電電流Ic10を示す。

【0028】

図4は、本発明の高周波発生装置の動作モードであり、6つのモードを繰り返している。そして、図3は6つの動作モードを説明する波形タイミング図であり、図3及び図4を参照して本発明の動作について説明する。

【0029】

図1に示す図示省略の高周波制御信号Rsが、時刻t=t0以前に図2に示すスイッチSWに入力されるとスイッチSWは閉路され、直流電源回路DCは脈流を有する直流電圧を出力し、第1の抵抗器R1及び第2の抵抗器R2で分圧された電圧がシャントレギュレータSR1のリファレンスRefに適応した電圧になり、シャントレギュレータSR1は、図3(B)に示すリファレンスRefの値が予め定めた基準電圧値を超えるとシャントレギュレータSR1のカソードK・アノードA、間に同図(A)に示す通電電流Isr1が流れ、且つ、周波数設定用コンデンサは同図(O)に示す放電電流Ic10として放電する。

【0030】

図1に示す周波数設定用コンデンサの放電により第2のスイッチング素子TR3のベースに図3(L)に示す逆電圧が印加されてオフし、且つ、第1のスイッチング素子TR2のベースに図3(I)に示す正電圧が印加されてオンすると、単安定マルチバイブレータ回路は安定状態から非安定状態に移行する。

【0031】

MODE1(時刻t=t0〜t1)

単安定マルチバイブレータ回路が非安定状態になると、MOSFET素子TR1の図3(C)に示すゲート電圧Vgが上昇し、時刻t=t0のときMOSFET素子TR1はオンする。このとき、図3及び図4に示すMODE1に移行し、フライバックトランスTの1次側に流れていた電流方向が逆転し、MOSFET素子TR1に図3(D)に示すドレイン電流Itr1が流れ込む。この時、共振コンデンサC4とフライバックトランスTの漏れインダクタンスによる共振が起こり、MOSFET素子TR1のドレイン電流はゼロから傾きを持ちながら上昇するためソフトスイッチング動作、即ち、ゼロ電流スイッチング(ZCS)でターンオンする。これに伴い、第2の平滑コンデンサC9は第3の抵抗器R3を介して放電を開始し、同時にMOSFET素子TR1のゲートへ電流を供給する。つまり抵抗器R7はMOSFET素子TR1のゲート抵抗としての役割を持ち、この値によりMOSFET素子TR1の立ち上がり特性が決定される。このとき第1のスイッチング素子TR2はこの時オン状態である。

【0032】

MODE2(時刻t=t1〜t2)

図3(D)に示すMOSFET素子TR1のドレイン電流(共振電流)Itr1が負、すなわちMOSFET素子TR1の図示省略の内蔵ダイオードへ自然転流すると回路動作は図3及び図4のMODE2へと移行する。このとき、図3(G)に示すフライバックトランスTの1次側のトランス電流Ipは正方向へと変化する。しかし、MOSFET素子TR1のゲートは引続きオン状態にあるので、このモード中にTR1のゲートがオフ状態になることでZCSターンオフとなる。第1のスイッチング素子TR2は図4のMODE1に引続きオン状態であり、単安定マルチバイブレータ回路が安定状態に戻る過渡状態として第2のスイッチング素子TR3がオンし始める。第2の平滑コンデンサC9は図4のMODE1と同様に放電動作をしている。

【0033】

MODE3(時刻t=t2〜t3)

単安定マルチバイブレータ回路が安定状態に戻り、第1のスイッチング素子TR2がオフする。そして、周波数設定用コンデンサは充電し、第2のスイッチング素子TR3のベースへ電流を供給している。

【0034】

MODE4(時刻t=t3〜t4)

図3(D)に示すMOSFET素子TR1のドレイン電流Itr1がゼロになると、MOSFET素子TR1のゲート電圧は既にオフしているのでMOSFET素子TR1は自然にオフする。第2のスイッチング素子TR3は引続きオンしているので第2の平滑コンデンサC9は、図3及び図4のMODE4から充電を開始する。そして、第1の抵抗器R1へ電流が流れ始め、シャントレギュレータSR1のリファレンス電圧Vrefは入力電圧の(R2/(R1+R2))で決められた分だけゼロから上昇していく。

【0035】

MODE5(時刻t=t4〜t5)

図3(B)に示すシャントレギュレータSR1のリファレンス電圧Vrefが時刻t=4において基準値電圧値を超えると通電し、シャントレギュレータSR1のカソード・アノード間に図3(A)に示す通電電流Isr1が流れ込む。この時、第2のスイッチング素子TR3のベースには周波数設定用コンデンサC10の電圧が逆にかかるが、ベース・エミッタ間にVRD2を挿入することによりVRD2から周波数設定用コンデンサC10へ電流が流れ込み、ベース・エミッタ間電圧が定格を越えないように動作している。このとき周波数設定用コンデンサC10は放電し、第2の平滑コンデンサC9は第3の抵抗器R3を介して充電している。

【0036】

MODE6(時刻t=t5〜t6)

第1のスイッチング素子TR2がオンしてマルチバイブレータは完全に非安定モードへと移行する。そして以後は、MODE1〜MODE5の動作を繰り返す。

【0037】

上述より、MOSFET素子のターンオン及びターンオフのとき、ソフトスイッチング動作、即ち、ゼロ電流スイッチング(ZCS)可能となりスイッチング損失が大幅に減少する。この減少によりMOSFET素子の高速スイッチングが可能となり、従来の共振周波数の30KHz近傍の限界に対し、70KHz近傍まで高速化が実現できる。

コンデンサC10・抵抗R6はMOSFETのスイッチングに関係しており、これらを調整することで、MOSFETは容易にZCS動作を実現する。(図1に示すC10とR6はマルチバイブレータの周波数設定用で、ゲート信号のデュティサイクルに関係する。)

【符号の説明】

【0038】

1 非消耗電極

AC 商用交流電源

CC カップリングコイル

C1 1次平滑コンデンサ

C2 平滑コンデンサ

C3 コンデンサ

C4 共振コンデンサ

C5 2次側コンデンサ

C6 2次側コンデンサ

C7 2次側コンデンサ

C8 2次側コンデンサ

C9 第2の平滑コンデンサ

C10 周波数設定用コンデンサ

C11 コンデンサ

DCL 直流リアクトル

D2 フリーホィールダイオード

DR1 1次整流回路

DR2 2次整流回路

DR3 全波整流回路

ER 誤差増幅回路

Er 誤差増幅信号

HFG 高周波発生装置

ID 出力電流検出回路

Id 出力電流検出信号

IR 出力電流設定回路

Ir 出力電流設定信号

INV インバータ回路

INT 主変圧器

M 被加工物

R1 第1の抵抗器

R2 第2の抵抗器

R3 第3の抵抗器

R4 第4の抵抗器

R5 第5の抵抗器

R6 第6の抵抗器

R7 第7の抵抗器

R8 保護抵抗

R9 第9の抵抗器

R10 第10の抵抗器

R11 第11の抵抗器

SC 出力制御信号

SR1 シャントレギュレータ

SCR 高速サイリスタ素子

SSS サイダック素子

T フライバックトランス

TH 溶接トーチ

TR1 MOSFET素子

TR2 第1のスイッチング素子

TR3 第2のスイッチング素子

TS 起動スイッチ

Ts 起動信号

VRD1 第1のツェナダイオード

VRD2 第2のツェナダイオード

【技術分野】

【0001】

本発明は、非消耗電極の溶接トーチと被加工物との間に高周波高電圧を重畳してアークを発生させる高周波発生装置の技術に関するものである。

【背景技術】

【0002】

溶接電源、切断電源に内蔵されている従来の高周波発生装置では、高速サイリスタ素子を用いて高周波高電圧を発生させていた。

【0003】

図5は、従来技術の高周波発生装置を使用した溶接電源の電気接続図である。図5において、直流電源回路は、1次整流回路DR1と1次整流回路DR1の出力側に並列に設けた1次平滑コンデンサC1とで形成され、商用交流電源を整流及び平滑して直流電圧を生成する。

【0004】

インバータ回路INVは、図示省略の相対向する4つのスイッチング素子からフルブリッジを形成し、直流電圧を高周波交流電圧に変換して出力する。

【0005】

変圧器INTは、インバータ回路INVによって変換された高周波交流電圧をアーク加工に適した高周波交流電圧に変換し、2次整流回路DR2は、主変圧器INTの出力を整流し直流リアクトルDCLを介して非消耗電極1と被加工物Mとの間に電力を供給する。

【0006】

図5に示す、出力電流検出回路IDは、主変圧器INTの2次側の出力電流を検出して出力電流検出信号Idとして出力する。誤差増幅回路ERは、出力電流検出信号Idの値と出力電流検出信号Idの値とを誤差増幅して誤差増幅信号Erとして出力する。出力制御回路SCは、パルス周波数が一定でパルス幅を変調するPWM制御を行い、誤差増幅信号Erに応じてインバータ回路INVを制御する。

【0007】

図6は、高速サイリスタ素子を用いた従来の高周波発生回路の詳細図であり、全波整流回路DR3と第1の平滑コンデンサC2とで形成し商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路DCと、直流電源回路DCに並列に設けたフリーホィールダイオードD2及び保護抵抗R9と、脈流を有する直流電圧が所定のブレークオーバ電圧を超えると通電するサイダック素子SSSと、共振コンデンサC4とフライバックトランスTとで形成され直流電源回路DCのプラス側出力に共振コンデンサC4の一方を接続し、共振コンデンサC4の他方をフライバックトランスTの1次側の一方に接続し、フライバックトランスTの1次側の他方を直流電源回路DCのマイナス側出力に接続し成る共振回路と、共振コンデンサC4の一方にアノードを接続し、フライバックトランスTの1次側の他方にカソードを接続し、サイダック素子SSSの通電に応じてオンするサイリスタ素子SCRと、ゲート電流を供給するコンデンサC11と、フライバックトランスTの2次側に並列に設けた放電ギャップSGと、フライバックトランスTの2次側の一方に接続した複数の直列コンデンサと、フライバックトランスTの2次側の他方と直列コンデンサと間に、外部にカップリングコイルCCを設けることで高周波発生装置が形成される。

【0008】

図7は、従来技術の動作を説明する波形タイミング図である。図7において、同図(A)の波形はサイダック電流Isssを示し、同図(B)の波形はサイダック電圧Vsssを示し、同図(C)の波形はサイリスタ素子SCRのゲート電流igを示し、同図(D)の波形はサイリスタ素子SCRの通電電流Iscrを示し、同図(E)の波形はサイリスタ素子SCRの通電電圧Vscrを示し、同図(F)の波形はフリーホィールダイオードD2の通電電流Idr2、同図(J)の波形はフライバックトランスの1次側のトランス電圧Vpをし、同図(H)の波形はフライバックトランスの1次側のトランス電流Ipを示す。

【0009】

図8は、高速サイリスタ素子SCRを用いた従来の高周波発生装置の動作モードであり、4つのモードを繰り返している。そして、図7は4つの動作モードを説明する波形タイミング図であり、図7及び図8を参照して従来の技術の高周波発生装置の動作について説明する。

【0010】

図6に示す図示省略の高周波制御信号Rs、図7に示す時刻t=t0以前にスイッチSWに入力されるとスイッチSWは閉路され、直流電源回路DCは脈流を有する直流電圧を出力し、図7(B)に示すサイダック電圧Vsssが上昇し、ブレークオーバ電圧に達するとサイダック素子SSSが通電する。

【0011】

「モード1」

サイダック素子SSSが時刻t=t0のとき、ブレークオーバ電圧に達して通電しているので、図7(C)に示すサイリスタ素子SCRのゲート電流igが上昇し、高速サイリスタ素子SCRがオンする。SCRがオンするとSSSの電圧はブレークオーバ電圧以下となるのでSSSは遮断するが、SCRはオンしているのでSSSの電圧は上昇しない。このときゲート電流はC11より供給される。このとき図7及び図8に示すMODE1に移行し、フライバックトランスTの1次側に流れていた電流の方向が逆転し、高速サイリスタ素子SCRに図7(D)に示す通電電流Iscrが流れ込む。このとき共振コンデンサC4とフライバックトランスTの1次側の漏れインダクタンスにより共振が起こり、高速サイリスタ素子SCRの電流はゼロから傾きを持ちながら上昇するためソフトスイッチング動作、すなわちゼロ電流スイッチング(ZCS)でターンオンする。

【0012】

「モード2」

図7(D)に示す、高速サイリスタ素子SCRの通電電流Iscrが減少し共振電流がゼロになると、高速サイリスタ素子SCRがターンオフし、図7及び図8に示すMODE2に移行し、フリーホィールダイオードD2へ図7(F)示す通電電流Idr2が流れ始める。この時、フライバックトランスTの1次側のトランス電流Ipは正方向へと変わる。

【0013】

「モード3」

図7(D)に示すフリーホィールダイオードD2へ流れる通電電流Idr2が減少し、時刻t=t2において、通電電流Idr2がゼロになると図7及び図8に示すMODE3に移行し、サイダック素子SSS、高速サイリスタ素子SCR、共振コンデンサC4の電圧が上昇を始める。

【0014】

「モード4」

共振コンデンサC4の電圧の上昇に応じて図7(B)に示すサイダック電圧Vsssが上昇し、ブレークオーバ電圧に達すると、図7及び図8に示すMODE4に移行し、サイダック素子SSSが再度通電する。このときコンデンサC11が充電される。そして、以後、MODE1に戻り上述と同一動作を繰り返す。

上述より、TIG溶接等のアークスタート時に、溶接トーチと被加工物との間に高周波高電圧を重畳してアークを発生させるとき、図6に示す高周波発生装置が一般的に使用されている。

(例えば、特許文献1)

【先行技術文献】

【特許文献】

【0015】

【特許文献1】特開昭61−7070号公報

【発明の概要】

【発明が解決しようとする課題】

【0016】

TIG溶接、プラズマ切断等に使用する高周波発生装置では、母材―電極間で放電する高電圧の発生回数が多くなるとアークのスタート性が良いことが知られている。一般に駆動素子のスイッチング周波数が高くなると母材―電極間で放電する高電圧の発生回数も多くなるという関係がある。従来の高周波発生装置を形成する共振回路では、スイッチング周波数の高速化を図るために駆動素子として応答速度の速いサイリスタ素子を使用していた。しかし、高速のサイリスタ素子を用いても応答速度に限界があり、スイッチング周波数の最大値は、例えば、30KHz近傍にあり、放電ギャップで放電する高電圧の周波数が不充分でアークのスタート性に問題があった。

【0017】

そこで、本発明では、母材―電極間で放電する高電圧の発生回数を充分多くできる高周波発生装置を提供することを目的とする。

【課題を解決するための手段】

【0018】

上述した課題を解決するために、第1の発明は、全波整流回路と平滑コンデンサとでなり商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、前記直流電源回路の出力側に並列に設けた第1の抵抗器と第2の抵抗器とを直列接続し、この接続した中接点とシャントレギュレータのリファレンス、前記シャントレギュレータのアノードと前記直流電源回路のマイナス側出力とを接続して形成されるマルチバイブレータ駆動回路と、前記直流電源回路のプラス側出力に第3の抵抗器の一方を接続し、前記第3の抵抗器の他方と第2の平滑コンデンサの一方及び第1のツェナダイオードのカソードとを接続し、前記第2の平滑コンデンサの他方及び前記第1のツェナダイオードのアノードと前記直流電源回路のマイナス側出力とを接続し形成し、前記第1のツェナダイオードのカソードからマルチバイブレータ電圧を出力するマルチバイブレータ電源回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、マルチバイブレータ駆動回路の前記シャントレギュレータが通電すると前記マルチバイブレータが安定状態から所定時間の非安定状態になる単安定マルチバイブレータ回路と、前記直流電源回路のプラス側出力に共振コンデンサの一方を接続し、前記共振コンデンサの他方にフライバックトランスの1次側の一方に接続し、前記フライバックトランスの1次側の他方を前記直流電源回路のマイナス側出力に接続して形勢される共振回路と、前記共振コンデンサの一方にドレイン側を接続し、前記フライバックトランスの1次側の他方にソース側を接続し前記単安定マルチバイブレータ回路が非安定状態になると前記共振回路を駆動させるMOSFET素子と、前記フライバックトランスの2次側に並列に設けた放電ギャップと、前記フライバックトランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置である。

【発明の効果】

【0019】

上述した課題を解決するために、本発明では、高周波発生装置を形成する共振回路の駆動素子として、高速のサイリスタ素子に代えてMOSFET素子を使用する。このとき、MOSFET素子のスイッチング速度はスイッチング損失値によって抑制がかかる。そこで、MOSFET素子のターンオン及びターンオフのとき、ソフトスイッチング動作、即ちゼロ電流スイッチング(ZCS)を行なうことでスイッチング損失を大きく減少させ、このスイッチング損失の減少値に応じてMOSFET素子の高速スイッチングが可能になる。そして、共振回路の共振周波数の最大値、例えば、30KHz近傍に対して70KHz近傍まで高速化され、この高速化により放電ギャップで放電する高電圧の周波数も高くなるのでアークのスタート性が向上する。

【図面の簡単な説明】

【0020】

【図1】本発明の実施の形態1に係る高周波発生装置の詳細図である

【図2】本発明の高周波発生装置の1次側のブロック図である。

【図3】本発明の動作を説明する波形タイミング図である。

【図4】本発明の動作を説明する動作モード図である。

【図5】従来技術の高周波発生装置を使用した溶接電源の電気接続図である。

【図6】従来技術の高周波発生装置の詳細図である

【図7】従来技術の動作を説明する波形タイミング図である。

【図8】従来技術の動作を説明する動作モード図である。

【発明を実施するための形態】

【0021】

図1は、本発明の実施の形態1に係る高周波発生装置の詳細図である。同図において、図6に示す、従来技術の高周波発生装置の詳細図と同一符号の構成物は、同一動作を行なうので説明は省略し符号の相違する構成物についてのみ説明する。

【0022】

次に、図1及び図2を用いて構成について説明する。

図2に示す直流電源回路DCは、図1に示す全波整流回路DR3と平滑コンデンサC2とで形成し商用交流電源を整流し脈流を有する直流電圧として出力する。単安定マルチバイブレータ駆動回路MDは、図1に示す直流電源回路DCの出力側に並列に設けた第1の抵抗器R1と第2の抵抗器R2とを直列接続し、この直列接続の中接点とシャントレギュレータSR1のリファレンスRefを接続し、且つ、シャントレギュレータSR1のアノードAを直流電源回路DCのマイナス側出力に接続して形成する。

【0023】

図2に示すマルチバイブレータ電源回路CDは、直流電源回路DCのプラス側出力に第3の抵抗器R3の一方を接続し第3の抵抗器R3の他方に第2の平滑コンデンサC9の一方及び第1のツェナダイオードVRD1のカソードKとを接続し、第2の平滑コンデンサC9の他方及び第1のツェナダイオードVRD1のアノードAと直流電源回路のマイナス側出力とを接続して形成し、直流電源回路DCからの直流電圧を下記に示すMOSFET素子のゲートに適応した電圧レベルに変換して出力する。

【0024】

図2に示す単安定マルチバイブレータ回路MBは、マルチバイブレータ電源回路CDの出力(第3の抵抗器R3の他方と第2の平滑コンデンサC9の一方の接続点)と第4の抵抗器R4、第5の抵抗器R5及び第6の抵抗器R6の一方を接続し、第4の抵抗器R4の他方とシャントレギュレータSR1のカソードK、第1のスイッチング素子TR2のコレクタ及び周波数設定用コンデンサC10の一方とを接続し、第5の抵抗器R5の他方と周波数設定用コンデンサの他方、第2のスイッチング素子TR3のベース及び第2のツェナダイオードVR2のカソードとを接続し、第6の抵抗器R6の他方と第1のスイッチング素子TR2のベース及び第2のスイッチング素子TR3のコレクタとを接続し、直流電源回路DCのマイナス側出力と第1のスイッチング素子TR2のエミッタ、第2のツェナダイオードVRD2のアノード及び第2のスイッチング素子TRのエミッタとを接続して形成し、シャントレギュレータSR1のカソードK、アノードA間が通電すると安定状態から非安定状態に移行する。

【0025】

図2に示す共振駆動回路RDは、図1に示す共振コンデンサC4の一方にMOSFET素子TR1のドレイン側を接続し、前記フライバックトランスTの1次側の他方にMOSFET素子TR1のソース側を接続したMOSFET素子TR1から形成される。

【0026】

共振回路は、図1に示す直流電源回路DCのプラス側出力に共振コンデンサC4の一方を接続し共振コンデンサC4の他方にフライバックトランスTの1次側の一方に接続し、フライバックトランスの1次側の他方を直流電源回路DCのマイナス側出力に接続して成る。

【0027】

図3は、本発明の動作を説明する波形タイミング図である。図3において、同図(A)の波形は、シャントレギュレータSR1の通電電流Isr1を示し、同図(B)の波形は、シャントレギュレータSR1のリファレンス電圧Vrefを示し、同図(C)の波形は、MOSFET素子TR1のゲート電圧Vgを示し、同図(D)の波形は、MOSFET素子TR1のドレイン電流Itr1を示し、同図(E)の波形は、MOSFET素子TR1のドレイン・ソース間電圧Vtr1を示し、同図(F)の波形は、フライバックトランスの1次側のトランス電圧Vpを示し、同図(G)の波形は、フライバックトランスの1次側のトランス電流Ipを示し、同図(H)の波形は、第1のスイッチング素子TR2のコレクタ・エミッタ間電圧VceTR2を示し、同図(I)の波形は、第1のスイッチング素子TR2のベース・エミッタ間電圧VbeTR2を示し、同図(J)の波形は、第1のスイッチング素子TR2のコレクタ電流IcTR2を示し、同図(K)の波形は、第1のスイッチング素子TR2のベース電流IbTR2を示し、同図(L)の波形は、第2のスイッチング素子TR2のベース、エミッタ間電圧VbeTR3を示し、同図(M)の波形は、第2のスイッチング素子TR3のコレクタ電流IcTR3を示し、同図(N)の波形は、第2のスイッチング素子TR3のベース電流IbTR3を示し、同図(O)の波形は、周波数設定用コンデンサC10の放電電流Ic10を示す。

【0028】

図4は、本発明の高周波発生装置の動作モードであり、6つのモードを繰り返している。そして、図3は6つの動作モードを説明する波形タイミング図であり、図3及び図4を参照して本発明の動作について説明する。

【0029】

図1に示す図示省略の高周波制御信号Rsが、時刻t=t0以前に図2に示すスイッチSWに入力されるとスイッチSWは閉路され、直流電源回路DCは脈流を有する直流電圧を出力し、第1の抵抗器R1及び第2の抵抗器R2で分圧された電圧がシャントレギュレータSR1のリファレンスRefに適応した電圧になり、シャントレギュレータSR1は、図3(B)に示すリファレンスRefの値が予め定めた基準電圧値を超えるとシャントレギュレータSR1のカソードK・アノードA、間に同図(A)に示す通電電流Isr1が流れ、且つ、周波数設定用コンデンサは同図(O)に示す放電電流Ic10として放電する。

【0030】

図1に示す周波数設定用コンデンサの放電により第2のスイッチング素子TR3のベースに図3(L)に示す逆電圧が印加されてオフし、且つ、第1のスイッチング素子TR2のベースに図3(I)に示す正電圧が印加されてオンすると、単安定マルチバイブレータ回路は安定状態から非安定状態に移行する。

【0031】

MODE1(時刻t=t0〜t1)

単安定マルチバイブレータ回路が非安定状態になると、MOSFET素子TR1の図3(C)に示すゲート電圧Vgが上昇し、時刻t=t0のときMOSFET素子TR1はオンする。このとき、図3及び図4に示すMODE1に移行し、フライバックトランスTの1次側に流れていた電流方向が逆転し、MOSFET素子TR1に図3(D)に示すドレイン電流Itr1が流れ込む。この時、共振コンデンサC4とフライバックトランスTの漏れインダクタンスによる共振が起こり、MOSFET素子TR1のドレイン電流はゼロから傾きを持ちながら上昇するためソフトスイッチング動作、即ち、ゼロ電流スイッチング(ZCS)でターンオンする。これに伴い、第2の平滑コンデンサC9は第3の抵抗器R3を介して放電を開始し、同時にMOSFET素子TR1のゲートへ電流を供給する。つまり抵抗器R7はMOSFET素子TR1のゲート抵抗としての役割を持ち、この値によりMOSFET素子TR1の立ち上がり特性が決定される。このとき第1のスイッチング素子TR2はこの時オン状態である。

【0032】

MODE2(時刻t=t1〜t2)

図3(D)に示すMOSFET素子TR1のドレイン電流(共振電流)Itr1が負、すなわちMOSFET素子TR1の図示省略の内蔵ダイオードへ自然転流すると回路動作は図3及び図4のMODE2へと移行する。このとき、図3(G)に示すフライバックトランスTの1次側のトランス電流Ipは正方向へと変化する。しかし、MOSFET素子TR1のゲートは引続きオン状態にあるので、このモード中にTR1のゲートがオフ状態になることでZCSターンオフとなる。第1のスイッチング素子TR2は図4のMODE1に引続きオン状態であり、単安定マルチバイブレータ回路が安定状態に戻る過渡状態として第2のスイッチング素子TR3がオンし始める。第2の平滑コンデンサC9は図4のMODE1と同様に放電動作をしている。

【0033】

MODE3(時刻t=t2〜t3)

単安定マルチバイブレータ回路が安定状態に戻り、第1のスイッチング素子TR2がオフする。そして、周波数設定用コンデンサは充電し、第2のスイッチング素子TR3のベースへ電流を供給している。

【0034】

MODE4(時刻t=t3〜t4)

図3(D)に示すMOSFET素子TR1のドレイン電流Itr1がゼロになると、MOSFET素子TR1のゲート電圧は既にオフしているのでMOSFET素子TR1は自然にオフする。第2のスイッチング素子TR3は引続きオンしているので第2の平滑コンデンサC9は、図3及び図4のMODE4から充電を開始する。そして、第1の抵抗器R1へ電流が流れ始め、シャントレギュレータSR1のリファレンス電圧Vrefは入力電圧の(R2/(R1+R2))で決められた分だけゼロから上昇していく。

【0035】

MODE5(時刻t=t4〜t5)

図3(B)に示すシャントレギュレータSR1のリファレンス電圧Vrefが時刻t=4において基準値電圧値を超えると通電し、シャントレギュレータSR1のカソード・アノード間に図3(A)に示す通電電流Isr1が流れ込む。この時、第2のスイッチング素子TR3のベースには周波数設定用コンデンサC10の電圧が逆にかかるが、ベース・エミッタ間にVRD2を挿入することによりVRD2から周波数設定用コンデンサC10へ電流が流れ込み、ベース・エミッタ間電圧が定格を越えないように動作している。このとき周波数設定用コンデンサC10は放電し、第2の平滑コンデンサC9は第3の抵抗器R3を介して充電している。

【0036】

MODE6(時刻t=t5〜t6)

第1のスイッチング素子TR2がオンしてマルチバイブレータは完全に非安定モードへと移行する。そして以後は、MODE1〜MODE5の動作を繰り返す。

【0037】

上述より、MOSFET素子のターンオン及びターンオフのとき、ソフトスイッチング動作、即ち、ゼロ電流スイッチング(ZCS)可能となりスイッチング損失が大幅に減少する。この減少によりMOSFET素子の高速スイッチングが可能となり、従来の共振周波数の30KHz近傍の限界に対し、70KHz近傍まで高速化が実現できる。

コンデンサC10・抵抗R6はMOSFETのスイッチングに関係しており、これらを調整することで、MOSFETは容易にZCS動作を実現する。(図1に示すC10とR6はマルチバイブレータの周波数設定用で、ゲート信号のデュティサイクルに関係する。)

【符号の説明】

【0038】

1 非消耗電極

AC 商用交流電源

CC カップリングコイル

C1 1次平滑コンデンサ

C2 平滑コンデンサ

C3 コンデンサ

C4 共振コンデンサ

C5 2次側コンデンサ

C6 2次側コンデンサ

C7 2次側コンデンサ

C8 2次側コンデンサ

C9 第2の平滑コンデンサ

C10 周波数設定用コンデンサ

C11 コンデンサ

DCL 直流リアクトル

D2 フリーホィールダイオード

DR1 1次整流回路

DR2 2次整流回路

DR3 全波整流回路

ER 誤差増幅回路

Er 誤差増幅信号

HFG 高周波発生装置

ID 出力電流検出回路

Id 出力電流検出信号

IR 出力電流設定回路

Ir 出力電流設定信号

INV インバータ回路

INT 主変圧器

M 被加工物

R1 第1の抵抗器

R2 第2の抵抗器

R3 第3の抵抗器

R4 第4の抵抗器

R5 第5の抵抗器

R6 第6の抵抗器

R7 第7の抵抗器

R8 保護抵抗

R9 第9の抵抗器

R10 第10の抵抗器

R11 第11の抵抗器

SC 出力制御信号

SR1 シャントレギュレータ

SCR 高速サイリスタ素子

SSS サイダック素子

T フライバックトランス

TH 溶接トーチ

TR1 MOSFET素子

TR2 第1のスイッチング素子

TR3 第2のスイッチング素子

TS 起動スイッチ

Ts 起動信号

VRD1 第1のツェナダイオード

VRD2 第2のツェナダイオード

【特許請求の範囲】

【請求項1】

全波整流回路と平滑コンデンサとでなり商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、前記直流電源回路の出力側に並列に設けた第1の抵抗器と第2の抵抗器とを直列接続し、この接続した中接点とシャントレギュレータのリファレンス、前記シャントレギュレータのアノードと前記直流電源回路のマイナス側出力とを接続して形成されるマルチバイブレータ駆動回路と、前記直流電源回路のプラス側出力に第3の抵抗器の一方を接続し、前記第3の抵抗器の他方と第2の平滑コンデンサの一方及び第1のツェナダイオードのカソードとを接続し、前記第2の平滑コンデンサの他方及び前記第1のツェナダイオードのアノードと前記直流電源回路のマイナス側出力とを接続し形成し、前記第1のツェナダイオードのカソードからマルチバイブレータ電圧を出力するマルチバイブレータ電源回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、マルチバイブレータ駆動回路の前記シャントレギュレータが通電すると前記マルチバイブレータが安定状態から所定時間の非安定状態になる単安定マルチバイブレータ回路と、前記直流電源回路のプラス側出力に共振コンデンサの一方を接続し、前記共振コンデンサの他方にフライバックトランスの1次側の一方に接続し、前記フライバックトランスの1次側の他方を前記直流電源回路のマイナス側出力に接続して形勢される共振回路と、前記共振コンデンサの一方にドレイン側を接続し、前記フライバックトランスの1次側の他方にソース側を接続し前記単安定マルチバイブレータ回路が非安定状態になると前記共振回路を駆動させるMOSFET素子と、前記フライバックトランスの2次側に並列に設けた放電ギャップと、前記フライバックトランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置。

【請求項1】

全波整流回路と平滑コンデンサとでなり商用交流電源を整流し脈流を有する直流電圧を出力する直流電源回路と、前記直流電源回路の出力側に並列に設けた第1の抵抗器と第2の抵抗器とを直列接続し、この接続した中接点とシャントレギュレータのリファレンス、前記シャントレギュレータのアノードと前記直流電源回路のマイナス側出力とを接続して形成されるマルチバイブレータ駆動回路と、前記直流電源回路のプラス側出力に第3の抵抗器の一方を接続し、前記第3の抵抗器の他方と第2の平滑コンデンサの一方及び第1のツェナダイオードのカソードとを接続し、前記第2の平滑コンデンサの他方及び前記第1のツェナダイオードのアノードと前記直流電源回路のマイナス側出力とを接続し形成し、前記第1のツェナダイオードのカソードからマルチバイブレータ電圧を出力するマルチバイブレータ電源回路と、第1のスイッチング素子、第2のスイッチング素子、周波数設定用コンデンサ及び第5の抵抗器でマルチバイブレータを形成し、マルチバイブレータ駆動回路の前記シャントレギュレータが通電すると前記マルチバイブレータが安定状態から所定時間の非安定状態になる単安定マルチバイブレータ回路と、前記直流電源回路のプラス側出力に共振コンデンサの一方を接続し、前記共振コンデンサの他方にフライバックトランスの1次側の一方に接続し、前記フライバックトランスの1次側の他方を前記直流電源回路のマイナス側出力に接続して形勢される共振回路と、前記共振コンデンサの一方にドレイン側を接続し、前記フライバックトランスの1次側の他方にソース側を接続し前記単安定マルチバイブレータ回路が非安定状態になると前記共振回路を駆動させるMOSFET素子と、前記フライバックトランスの2次側に並列に設けた放電ギャップと、前記フライバックトランスの2次側の一方に直列接続した複数の2次側コンデンサと、を備えた高周波発生装置。

【図1】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【図2】

【図3】

【図4】

【図5】

【図6】

【図7】

【図8】

【公開番号】特開2013−27151(P2013−27151A)

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願番号】特願2011−159691(P2011−159691)

【出願日】平成23年7月21日(2011.7.21)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

【公開日】平成25年2月4日(2013.2.4)

【国際特許分類】

【出願日】平成23年7月21日(2011.7.21)

【出願人】(000000262)株式会社ダイヘン (990)

【Fターム(参考)】

[ Back to top ]