A/D変換装置および固体撮像装置

【課題】電圧分解能を低下させることなく、高速化することができるA/D変換装置および固体撮像装置を提供する。

【解決手段】所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い第1のサンプリング期間と、(1/n)Tsの第2のサンプリング期間とを設定し、アナログ信号を出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、デジタルオフセット信号で選択されたアナログオフセット信号を加えた増幅アナログ信号を出力して第2のサンプリングを行わせるA/D制御回路と、第1のサンプリング結果から第1のデジタル信号とデジタルオフセット信号とを生成し、第2のサンプリング結果から第2のデジタル信号を生成し、デジタルオフセット信号と第2のデジタル信号とに基づいて、期間Tsに対応した第3のデジタル信号を生成して出力するデジタル生成回路と、を備える。

【解決手段】所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い第1のサンプリング期間と、(1/n)Tsの第2のサンプリング期間とを設定し、アナログ信号を出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、デジタルオフセット信号で選択されたアナログオフセット信号を加えた増幅アナログ信号を出力して第2のサンプリングを行わせるA/D制御回路と、第1のサンプリング結果から第1のデジタル信号とデジタルオフセット信号とを生成し、第2のサンプリング結果から第2のデジタル信号を生成し、デジタルオフセット信号と第2のデジタル信号とに基づいて、期間Tsに対応した第3のデジタル信号を生成して出力するデジタル生成回路と、を備える。

【発明の詳細な説明】

【技術分野】

【0001】

本発明は、A/D変換装置および固体撮像装置に関する。

【背景技術】

【0002】

近年、固体撮像装置としてCMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)イメージセンサが注目され、実用化されている。このCMOSイメージセンサは、CCD(Charge Copled Device:電荷結合素子)イメージセンサが専用の製造プロセスによって製造されるのに対し、一般的な半導体の製造プロセスを用いて製造することが可能である。このことから、CMOSイメージセンサは、例えば、SOC(System On Chip)のように、センサ内に種々の機能回路を組み込みことによって、多機能化を実現することが可能となっている。

【0003】

そして、近年では、デジタルカメラ、デジタルビデオカメラや内視鏡などに搭載する固体撮像装置として、アナログ・デジタル変換器(以下、「A/D変換回路」という)を内蔵した固体撮像装置を使用する例が増えている。このような固体撮像装置に内蔵されるA/D変換回路においては、その回路の全てをデジタル回路で実現したパルス遅延型A/D変換回路(特許文献1参照)を用いる場合がある。なお、以下の説明においてA/D変換回路といった場合には、パルス遅延型A/D変換回路のことを示すものとする。

【0004】

図8は、従来のA/D変換回路の概略構成を示したブロック図である。図8に示した従来のA/D変換回路400は、遅延回路401と、クロック生成回路402と、パルス位置数値化回路403と、を備えている。

【0005】

遅延回路401は、複数の遅延素子が円環状に接続されている。図8においては、遅延回路401が、初段の遅延素子1aが、否定論理積ゲート(NAND回路)などのような、2つの入力端子を有する論理ゲート、その他の段の遅延素子1bが、論理否定ゲート(NOT回路)などのような、1つの入力端子を有する論理ゲートで構成されている場合を示している。なお、以下の説明において、遅延素子1aと遅延素子1bとを区別しない場合には、単に「遅延素子1」という。

【0006】

初段の遅延素子1aには、パルス信号Pinと、最終段の遅延素子1bの出力信号とが入力される。また、次段以降の各遅延素子1bには、前段の遅延素子1の出力信号が入力される。パルス信号Pinが、初段の遅延素子1aに入力されると、遅延回路401内の走行を開始する。このとき、各遅延素子1は、印加された駆動電圧の大きさに応じた伝播遅延時間で、入力されたパルス信号Pinを伝播(走行)させる。なお、各遅延素子1は、印加された駆動電圧(アナログ信号Vin)が低いほど入力信号(パルス信号Pin)を長く遅延させる特性を備えている。各遅延素子1から出力された出力信号は、遅延回路401内を走行したパルス信号Pinの走行位置として、パルス位置数値化回路403に出力される。

【0007】

クロック生成回路402は、パルス信号Pinと、サンプリング期間がTsのサンプリングクロックCkを生成する。また、クロック生成回路402は、生成したパルス信号Pinを遅延回路401に、サンプリングクロックCkをパルス位置数値化回路403に、それぞれ出力する。

【0008】

パルス位置数値化回路403は、ラッチ&エンコーダ回路4031と、カウンタ4032と、ラッチ回路4033と、減算回路4034と、を備えている。

ラッチ&エンコーダ回路4031は、クロック生成回路402から入力されたサンプリングクロックCkのエッジに同期して、遅延回路401内を走行したパルス信号Pinの走行位置を検出する。また、ラッチ&エンコーダ回路4031は、検出したパルス信号Pinの走行位置を、bビット(bは正の整数)の数値に変換(エンコード)して減算回路4034に出力する。

【0009】

カウンタ4032は、サンプリング期間Ts内にパルス信号Pinが円環状の遅延回路401内を周回した周回数を取得する。また、カウンタ4032は、取得した周回数を、aビット(aは正の整数)の計数値としてラッチ回路4033に出力する。

ラッチ回路4033は、クロック生成回路402から入力されたサンプリングクロックCkのエッジに同期して、カウンタ4032から出力された計数値をラッチし、減算回路4034に出力する。

【0010】

減算回路4034は、ラッチ回路4033から出力された出力信号を上位ビット値a、ラッチ&エンコーダ回路4031から出力された出力信号を下位ビット値bとする合成デジタル値abを取り込む。そして、減算回路4034は、最新(今回)のサンプリングによる合成デジタル値abから、前回のサンプリングによる合成デジタル値abを差し引く減算処理を行い、サンプリング期間Ts内にパルス信号Pinが伝播した遅延素子1の個数を表すデジタル信号Doutを算出する。

このようにして、図8に示した従来のA/D変換回路400では、アナログ信号Vinをデジタル信号Doutに変換、すなわち、A/D変換することができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特許第3064644号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

このようなA/D変換回路400において、高速な処理を実行する(以下、「高速化」という)ことが求められている。そこで、A/D変換回路400の高速化を実現するための方法として、サンプリング期間Tsを短くすることが考えられる。

【0013】

しかしながら、従来のA/D変換回路400の電圧分解能は、サンプリング期間Tsに関係している。そして、従来のA/D変換回路400では、サンプリング期間Tsを長くした方が、電圧分解能が高くなる、という性質を備えている。これは、サンプリング期間Tsが長い方が、パルス信号Pinが遅延素子1を伝播する個数が多くなり、パルス信号Pinが伝搬した遅延素子1の個数を表すデジタル信号Doutの値が大きくなるからである。そして、例えば、同じアナログ信号VinをA/D変換した場合には、デジタル信号Doutの値が大きい方が、デジタル信号Doutの最小単位(例えば、最下位ビット)が表すアナログ信号Vinの電圧幅である量子化ステップ幅が小さくなり、結果として、電圧分解能が高くなるというものである。ここで、量子化ステップ幅の単位は、[V/LSB]である。

【0014】

このため、A/D変換回路400の高速化を実現する方法として、サンプリング期間Tsを短くしてしまうと、A/D変換回路400の高速化を実現することができる一方、量子化ステップ幅が大きくなり、電圧分解能が低下してしまう、という問題がある。

【0015】

本発明は、上記の課題認識に基づいてなされたものであり、電圧分解能を低下させることなく、高速化することができるA/D変換装置および固体撮像装置を提供することを目的としている。

【課題を解決するための手段】

【0016】

上記の課題を解決するため、本発明のA/D変換装置は、入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い期間の第1のサンプリング期間と、(1/n)Tsの期間の第2のサンプリング期間とを設定し、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第1のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第1のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第2のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第2のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第2のサンプリングを行わせる、A/D制御回路と、前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、前記所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、を備えることを特徴とする。

【0017】

また、本発明のA/D変換装置は、前記A/D入力信号の電圧範囲が、前記遅延回路に入力することができる電圧の範囲である入力電圧範囲よりも小さい所定の電圧範囲となるように、前記A/D制御回路に入力する前記アナログ信号の電圧範囲を調整する入力調整回路、をさらに備え、前記A/D制御回路は、前記所定の電圧範囲に基づいて、それぞれの前記アナログオフセット信号を設定する、ことを特徴とする。

【0018】

また、本発明の前記入力調整回路は、前記入力電圧範囲の最大の電圧値から前記第1のデジタル信号の1ビットに対応する電圧値を減算した電圧値を、前記所定の電圧範囲における最大の電圧値として設定する、ことを特徴とする。

【0019】

また、本発明の前記入力調整回路は、前記入力電圧範囲の最小の電圧値に前記第1のデジタル信号の1ビットに対応する電圧値を加算した電圧値を、前記所定の電圧範囲における最小の電圧値として設定する、ことを特徴とする。

【0020】

また、本発明の前記A/D制御回路は、前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいて、前記デジタルオフセット信号に対応したn個の前記アナログオフセット信号を設定し、前記デジタルオフセット信号に応じて、n個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、ことを特徴とする。

【0021】

また、本発明の前記A/D制御回路は、前記デジタルオフセット信号に対応したm(m:正の整数、m≧2n−1)個の前記アナログオフセット信号を設定し、該設定される1個目およびm個目の前記アナログオフセット信号は、前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいた電圧値に設定され、前記デジタルオフセット信号に応じて、m個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、ことを特徴とする。

【0022】

また、本発明の固体撮像装置は、入射された光量に応じた光電変換信号を出力する複数の画素が2次元の行列状に配置された画素部と、入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、第1のサンプリングのときに、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力し、第2のサンプリングのときに、該アナログ信号をn(n:正の整数、n≧2)倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力するアナログ変換回路と、前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、を具備したA/D変換装置を、前記画素部の各列に対応したA/D変換回路として複数配置したカラムA/D変換回路と、前記所定のアナログ・デジタル変換期間Tsに対して、(1−1/n)Tsより短い期間の第1のサンプリング期間と、(1/n)Tsの期間の第2のサンプリング期間とを設定し、前記第1のサンプリング期間を開始するときに、前記パルス信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記遅延回路に出力し、該第1のサンプリング期間が終了するときに、前記サンプリングタイミング信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記サンプリング回路に出力して前記第1のサンプリングを行わせ、前記第2のサンプリング期間を開始するときに、前記パルス信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記遅延回路に出力し、該第2のサンプリング期間が終了するときに、前記サンプリングタイミング信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記サンプリング回路に出力して前記第2のサンプリングを行わせる、タイミング生成回路と、を備え、前記カラムA/D変換回路は、前記画素部の各列の前記画素から出力された前記光電変換信号のそれぞれを、対応する前記A/D変換回路に入力するそれぞれのアナログ信号とし、前記第2のサンプリングが終了した後に、それぞれの前記A/D変換回路が出力した前記デジタル信号を、該カラムA/D変換回路からの出力信号としてそれぞれ出力する、ことを特徴とする。

【発明の効果】

【0023】

本発明によれば、A/D変換装置の電圧分解能を低下させることなく、高速化することができるという効果が得られる。

【図面の簡単な説明】

【0024】

【図1】本発明の第1の実施形態におけるA/D変換回路の概略構成を示したブロック図である。

【図2】本第1の実施形態のA/D変換回路における、サンプリング時刻とデジタル信号との関係、および本第1の実施形態のA/D変換回路によるアナログ・デジタル変換動作における各信号のタイミングを示したタイミングチャートである。

【図3】本第1の実施形態のA/D変換回路に備えたアナログ変換回路の概略構成を示したブロック図である。

【図4】本第1の実施形態のA/D変換回路におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【図5】本第2の実施形態のA/D変換回路に備えたアナログ変換回路の概略構成を示したブロック図である。

【図6】本第2の実施形態のA/D変換回路におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【図7】本発明のA/D変換回路を列毎に複数搭載したカラムA/D変換回路方式の固体撮像装置の概略構成を示したブロック図である。

【図8】従来のA/D変換回路の概略構成を示したブロック図である。

【発明を実施するための形態】

【0025】

<第1の実施形態>

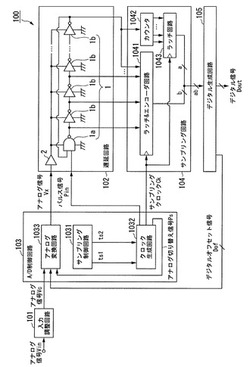

以下、本発明の第1の実施形態について、図面を参照して説明する。図1は、本第1の実施形態におけるA/D変換回路の概略構成を示したブロック図である。図1に示したA/D変換回路100は、入力調整回路101と、遅延回路102と、A/D制御回路103と、サンプリング回路104と、デジタル生成回路105と、を備えている。なお、以下の説明においては、図8に示したような従来のA/D変換回路400が、入力されたアナログ信号Vinをデジタル信号DoutにA/D変換するためのサンプリング期間を、「Ts」とする。

【0026】

本第1の実施形態のA/D変換回路100では、1回のA/D変換期間内に、入力されたアナログ信号Vinをデジタル信号DoutにA/D変換するためのサンプリングを、2回行う。ただし、本第1の実施形態のA/D変換回路100における合計のサンプリング期間は、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間である。より具体的には、A/D変換回路100は、(1−1/n)Tsより短いサンプリング期間の1回目のサンプリング(以下、「第1サンプリング」という)と、(1/n)Tsのサンプリング期間の2回目のサンプリング(以下、「第2サンプリング」という)との、2回のサンプリングを行う。なお、本第1の実施形態では、上記のn(n:正の整数、n≧2)の数値が、n=2である場合について説明する。

【0027】

入力調整回路101は、入力されたアナログ信号Vinの電圧の範囲を調整した、アナログ信号Vcを出力する。より具体的には、入力調整回路101は、アナログ信号Vinのダイナミックレンジが、最小値Vminから最大値Vmaxまでの電圧範囲(以下、「アナログ信号範囲」という)となるように、アナログ信号Vinを調整し、調整したアナログ信号Vinを、アナログ信号Vcとして出力する。ここで、アナログ信号範囲は、最小値Vluから最大値Vloまでの遅延回路102の入力電圧範囲(以下、「A/D入力範囲」という)よりも小さい(狭い)範囲である。アナログ信号範囲の最大値Vmaxおよび最小値Vminと、A/D入力範囲の最大値Vloおよび最小値Vluとは、下式(1)の関係にある。

【0028】

【数1】

【0029】

上式(1)において、ΔVは第1サンプリングのときの量子化ステップ幅である。

【0030】

遅延回路102は、k個(k:正の整数、k≧2)の円環状に接続されている遅延素子と、バッファ2と、で構成されている。図1においては、初段の遅延素子1aが、否定論理積ゲート(NAND回路)などのような、2つの入力端子を有する論理ゲート、その他の段の遅延素子1bが、論理否定ゲート(NOT回路)などのような、1つの入力端子を有する論理ゲートで構成されている場合を示している。なお、以下の説明において、遅延素子1aと遅延素子1bとを区別しない場合には、単に「遅延素子1」という。

【0031】

初段の遅延素子1aには、パルス信号Pinと、最終段の遅延素子1bの出力信号とが入力される。また、次段以降の各遅延素子1bには、前段の遅延素子1の出力信号が入力される。パルス信号Pinは、初段の遅延素子1aに入力されると、遅延回路102内の走行を開始する。このとき、各遅延素子1は、バッファ2を介して印加された駆動電圧の大きさに応じた伝播遅延時間で、入力されたパルス信号Pinを伝播(走行)させる。なお、各遅延素子1は、バッファ2を介して印加された駆動電圧(アナログ信号Vx)が低いほど入力信号(パルス信号Pin)を長く遅延させる特性を備えている。各遅延素子1から出力された出力信号は、遅延回路102内を走行したパルス信号Pinの走行位置として、サンプリング回路104出力される。

【0032】

A/D制御回路103は、サンプリング制御回路1031と、クロック生成回路1032と、アナログ変換回路1033と、を備えている。

【0033】

サンプリング制御回路1031は、従来のA/D変換回路400のサンプリング期間Tsに対して、第1サンプリングのサンプリング期間Ts1(以下、「第1サンプリング期間Ts1」という)が、Ts1<(1−1/n)Tsとなるように、第1サンプリングにおけるサンプリング時刻ts1(以下、「第1サンプリング時刻ts1」という)を設定する。また、サンプリング制御回路1031は、従来のA/D変換回路400のサンプリング期間Tsに対して、第2サンプリングのサンプリング期間Ts2(以下、「第2サンプリング期間Ts2」という)が、Ts2=(1/n)Tsとなるように、第2サンプリングにおけるサンプリング時刻ts2(以下、「第2サンプリング時刻ts2」という)を設定する。そして、サンプリング制御回路1031は、設定した第1サンプリング時刻ts1の数値と、第2サンプリング時刻ts2の数値とを、クロック生成回路1032に出力する。

【0034】

クロック生成回路1032は、第1サンプリングと第2サンプリングとにおけるパルス信号Pinを生成し、遅延回路102に出力する。また、クロック生成回路1032は、サンプリング制御回路1031から入力された第1サンプリング時刻ts1の数値と第2サンプリング時刻ts2の数値とに基づいて、A/D変換回路100の1回のA/D変換期間内に、2回の立ち上がりエッジを備えたサンプリングクロックCkを生成する。より具体的には、パルス信号Pinを遅延回路102に出力した後、第1サンプリング時刻ts1のときに1回目の立ち上がりエッジがあり、再度、パルス信号Pinを遅延回路102に出力した後、第2サンプリング時刻ts2のときに2回目の立ち上がりエッジがあるサンプリングクロックCkを生成する。そして、クロック生成回路1032は、生成したサンプリングクロックCkを、サンプリング回路104に出力する。

【0035】

これより、A/D変換回路100は、サンプリングクロックCkの2回の立ち上がりエッジを用いて、1回のA/D変換期間内に、第1サンプリングと第2サンプリングとの計2回のサンプリングを行う。より具体的には、サンプリングクロックCkの1回目の立ち上がりエッジで第1サンプリングを行い、サンプリングクロックCkの2回目の立ち上がりエッジで第2サンプリングを行う。

【0036】

また、クロック生成回路1032は、サンプリング制御回路1031から入力された第1サンプリング時刻ts1の数値と第2サンプリング時刻ts2の数値とに基づいて、第1サンプリングと第2サンプリングとで、遅延回路102に入力されるアナログ信号Vxを切り替えるためのアナログ切り替え信号Psを生成する。そして、クロック生成回路1032は、生成したアナログ切り替え信号Psを、アナログ変換回路1033に出力する。

【0037】

これにより、遅延回路102に入力されるアナログ信号Vxが、アナログ変換回路1033によって、第1サンプリングと第2サンプリングとで、異なるアナログ信号に切り替えられる。より具体的には、アナログ切り替え信号Psによって、遅延回路102に入力されるアナログ信号Vxが、第1サンプリングではアナログ信号Vcに、第2サンプリングではアナログ変換回路1033で生成されるアナログ信号(後述する、アナログ信号Vg)に、それぞれ切り替えられる。

【0038】

アナログ変換回路1033は、入力調整回路101から入力されたアナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。アナログ変換回路1033がアナログ信号Vcをオフセットするためのアナログオフセット信号は、デジタル生成回路105から入力された制御信号(後述する、デジタルオフセット信号Dof)に応じて切り替える。そして、アナログ変換回路1033は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または生成したアナログ信号Vgのいずれか一方のアナログ信号を、アナログ信号Vxとして遅延回路102に出力する。なお、アナログ変換回路1033におけるアナログ信号Vgの生成方法に関する詳細な説明は、後述する。

【0039】

サンプリング回路104は、ラッチ&エンコーダ回路1041と、カウンタ1042と、ラッチ回路1043と、を備えている。

【0040】

ラッチ&エンコーダ回路1041は、A/D制御回路103内のクロック生成回路1032から入力されたサンプリングクロックCkの立ち上がりエッジに同期して、遅延回路102内を走行したパルス信号Pinの走行位置を検出する。すなわち、ラッチ&エンコーダ回路1041は、第1サンプリング時刻ts1および第2サンプリング時刻ts2のときに、それぞれ、パルス信号Pinの走行位置を検出する。また、ラッチ&エンコーダ回路1041は、検出したそれぞれのパルス信号Pinの走行位置を、それぞれbビット(bは正の整数)の数値に変換(エンコード)して、デジタル生成回路105に出力する。

【0041】

カウンタ1042は、サンプリング期間内に遅延回路102を周回したパルス信号Pinの周回数を取得する。より具体的には、カウンタ1042は、第1サンプリング期間Ts1および第2サンプリング期間Ts2のそれぞれのサンプリング期間内に、遅延回路102を周回したパルス信号Pinの周回数を、それぞれ取得する。そして、カウンタ1042は、取得したそれぞれの周回数を、それぞれaビット(aは正の整数)の計数値としてラッチ回路1043に出力する。

【0042】

ラッチ回路1043は、A/D制御回路103内のクロック生成回路1032から入力されたサンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042から出力された計数値をラッチし、デジタル生成回路105に出力する。すなわち、ラッチ回路1043は、第1サンプリング時刻ts1および第2サンプリング時刻ts2のときにカウンタ1042から出力されたaビットの計数値をそれぞれラッチし、ラッチしたそれぞれのaビットの計数値を、デジタル生成回路105に出力する。

【0043】

デジタル生成回路105は、サンプリング回路104内のラッチ&エンコーダ回路1041が取得したパルス信号Pinの走行位置の値、およびサンプリング回路104内のラッチ回路1043が取得したパルス信号Pinの周回数の値を取り込む。そして、デジタル生成回路105は、取り込んだ2つの値に基づいて、サンプリング期間内にパルス信号Pinが伝播した遅延素子1の個数を算出し、算出した遅延素子1の個数を表すデジタル信号に数値化、すなわち、A/D変換する。より具体的には、デジタル生成回路105は、第1サンプリング時刻ts1のときのaビットの計数値とbビットの数値とに基づいて、第1サンプリング期間Ts1のデジタル信号Dout1に数値化し、第2サンプリング時刻ts2のときのaビットの計数値とbビットの数値とに基づいて、第2サンプリング期間Ts2のデジタル信号Dout2に数値化する。

【0044】

また、デジタル生成回路105は、デジタル信号Dout1の数値に基づいて、アナログ信号Vcを、アナログオフセット信号で調整するための制御信号であるデジタルオフセット信号Dofを生成し、生成したデジタルオフセット信号Dofを、アナログ変換回路1033に出力する。デジタルオフセット信号Dofは、デジタル信号Dout1の数値に応じて、アナログオフセット信号を選択するための制御信号である。なお、本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号Vmax/nまたはアナログオフセット信号Vmin/nのいずれか一方を選択するための制御信号が、デジタルオフセット信号Dofとして出力される。

【0045】

また、デジタル生成回路105は、デジタルオフセット信号Dofおよびデジタル信号Dout2に基づいて、従来のA/D変換回路400と同様のサンプリング期間Ts(>Ts1+Ts2)内にパルス信号Pinが伝播した遅延素子1の個数を算出し、算出した遅延素子1の個数を表すデジタル信号Doutに数値化する。

このようにして、A/D変換回路100では、入力調整回路101に入力したアナログ信号Vinを、最終的なデジタル信号Doutに変換、すなわち、A/D変換する。

【0046】

次に、本第1の実施形態のA/D変換回路100におけるA/D変換の動作手順について説明する。図2は、本第1の実施形態のA/D変換回路100における、サンプリング時刻とデジタル信号との関係、および本第1の実施形態のA/D変換回路100によるアナログ・デジタル変換動作における各信号のタイミングを示したタイミングチャートである。なお、上述した第1サンプリング期間Ts1は、サンプリング時刻t1sからt1までの期間のことを指し、第2サンプリング期間Ts2は、サンプリング時刻t2sからt2までの期間のことを指す。以下の説明においては、A/D変換回路100内の構成要素の動作を、A/D変換回路100における1回のA/D変換期間であるサンプリング期間Tsum内の各サンプリング時刻の経過に沿って説明する。

【0047】

サンプリング時刻t1s以前の期間では、クロック生成回路1032が、アナログ切り替え信号PsをHighにし、アナログ変換回路1033が、アナログ信号Vxとしてアナログ信号Vcを出力する。これにより、遅延回路102に入力されるアナログ信号Vxは、アナログ信号Vcとなる。

【0048】

サンプリング時刻t1sでは、クロック生成回路1032が、パルス信号Pinを、Highにする。これにより、パルス信号Pinが、遅延回路102内の走行を開始する。このようにして、A/D変換回路100は、1回のA/D変換における第1サンプリングを開始する。

【0049】

サンプリング時刻t1では、ラッチ&エンコーダ回路1041が、サンプリングクロックCkの立ち上がりエッジに同期して、第1サンプリングにおけるパルス信号Pinの走行位置を検出し、検出したパルス信号Pinの走行位置を、デジタル生成回路105に出力する。また、サンプリング時刻t1では、ラッチ回路1043が、サンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042が取得した第1サンプリングにおけるパルス信号Pinの周回数をラッチし、デジタル生成回路105に出力する。このようにして、A/D変換回路100は、1回のA/D変換における第1サンプリングを終了する。

【0050】

サンプリング時刻t1からt2sまでの期間(以下、「アナログ変換期間Ta」という)では、デジタル生成回路105が、ラッチ&エンコーダ回路1041から入力されたパルス信号Pinの走行位置の値、およびラッチ回路1043から入力されたパルス信号Pinの周回数の値に基づいて、デジタル信号Dout1を算出し、デジタルオフセット信号Dofを生成する。本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号のいずれか一方を選択するための、HighまたはLowの1bitのデジタルオフセット信号Dofが、デジタル信号Dout1の数値に応じて、すなわち、アナログ信号Vcの大きさに応じて生成され、アナログ変換回路1033に出力される。

【0051】

そして、アナログ変換回路1033は、デジタル生成回路105から入力された1bitのデジタルオフセット信号Dofの値(HighまたはLow)に応じて、アナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。

【0052】

また、アナログ変換期間Taでは、クロック生成回路1032が、パルス信号Pinを、Lowにする。これにより、パルス信号Pinは、遅延回路102内の走行を停止する。

【0053】

また、アナログ変換期間Taでは、クロック生成回路1032が、アナログ切り替え信号PsをLowにし、アナログ変換回路1033が、アナログ信号Vxとしてアナログ信号Vgを出力する。これにより、遅延回路102に入力されるアナログ信号Vxは、アナログ信号Vgとなる。

【0054】

サンプリング時刻t2sでは、クロック生成回路1032が、パルス信号Pinを、Highにする。これにより、パルス信号Pinが、遅延回路102内の走行を開始する。このようにして、A/D変換回路100は、1回のA/D変換における第2サンプリングを開始する。

【0055】

サンプリング時刻t2では、ラッチ&エンコーダ回路1041が、サンプリングクロックCkの立ち上がりエッジに同期して、第2サンプリングにおけるパルス信号Pinの走行位置を検出し、検出したパルス信号Pinの走行位置を、デジタル生成回路105に出力する。また、サンプリング時刻t2では、ラッチ回路1043が、サンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042が取得した第2サンプリングにおけるパルス信号Pinの周回数をラッチし、デジタル生成回路105に出力する。このようにして、A/D変換回路100は、1回のA/D変換における第2サンプリングを終了する。

【0056】

サンプリング時刻t2以降の期間では、デジタル生成回路105が、ラッチ&エンコーダ回路1041から入力されたパルス信号Pinの走行位置の値、およびラッチ回路1043から入力されたパルス信号Pinの周回数の値に基づいて、デジタル信号Dout2を算出する。また、デジタル生成回路105は、アナログ変換期間Taで生成したデジタルオフセット信号Dof、および算出したデジタル信号Dout2に基づいて、デジタル信号Doutを算出する。そして、算出したデジタル信号Doutを、従来のA/D変換回路400と同様のサンプリング期間TsでA/D変換した最終的なデジタル信号Doutとして出力する。

【0057】

また、サンプリング時刻t2以降の期間では、クロック生成回路1032が、パルス信号Pinを、Lowにする。これにより、パルス信号Pinは、遅延回路102内の走行を停止する。

【0058】

次に、アナログ信号Vgの算出方法について説明する。図3は、本第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033の概略構成を示したブロック図である。図3に示したアナログ変換回路1033は、減算回路1034と、増幅回路1035と、2つ(n個、n=2)のアナログオフセット信号Vmax/nおよびVmin/nと、スイッチ3と、スイッチ4と、を備えている。

【0059】

アナログオフセット信号Vmax/nおよびVmin/nは、アナログ信号Vcをオフセットするために、予め定められたアナログ信号である。本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号Vmax/2とアナログオフセット信号Vmin/2とが、予め定められている。

【0060】

スイッチ4は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、2つのアナログオフセット信号Vmax/nまたはアナログオフセット信号Vmin/nのいずれか一方を、減算回路1034に出力する。スイッチ4の出力端子は、デジタルオフセット信号Dof=Highのとき、アナログオフセット信号Vmax/nの入力端子に接続され、デジタルオフセット信号Dof=Lowのとき、アナログオフセット信号Vmin/nの入力端子に接続される。

【0061】

減算回路1034は、入力調整回路101から入力されたアナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmax/nまたはVmin/nのいずれかを減算する。そして、アナログオフセット信号を減算したアナログ信号Vcを、増幅回路1035に出力する。より具体的には、デジタルオフセット信号Dof=Highの場合、減算回路1034は、アナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmax/nを減算し、増幅回路1035に出力する。また、デジタルオフセット信号Dof=Lowの場合、減算回路1034は、アナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmin/nを減算し、増幅回路1035に出力する。

【0062】

増幅回路1035は、減算回路1034から入力された、アナログオフセット信号Vmax/nまたはVmin/nのいずれかが減算されたアナログ信号Vcを増幅したアナログ信号Vcを生成し、アナログ信号Vgとして出力する。本第1の実施形態のA/D変換回路100では、n=2であるため、増幅回路1035は、アナログオフセット信号が減算されたアナログ信号Vcを2倍に増幅したアナログ信号Vgを生成する。このときのアナログ信号Vgは、下式(2)で表される。

【0063】

【数2】

【0064】

スイッチ3は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または増幅回路1035が増幅したアナログ信号Vgいずれか一方を、アナログ変換回路1033が出力するアナログ信号Vxとして、遅延回路102に出力する。スイッチ3の出力端子は、アナログ切り替え信号Ps=Highのとき、アナログ信号Vcの入力端子に接続され、アナログ切り替え信号Ps=Lowのとき、アナログ信号Vgの入力端子に接続される。

【0065】

第1サンプリングのとき、アナログ切り替え信号Ps=Highにより、スイッチ3の出力端子は、アナログ変換回路1033のアナログ信号Vcの入力端子に接続される。これより、アナログ信号Vxはアナログ信号Vcに等しくなり、遅延回路102に出力される。

【0066】

第2サンプリングのとき、アナログ切り替え信号Ps=Lowにより、スイッチ3の出力端子は、増幅回路1035の出力端子に接続される。これより、アナログ信号Vxはアナログ信号Vgに等しくなり、遅延回路102に出力される。

【0067】

次に、A/D変換回路100におけるアナログ信号(アナログ信号Vc,アナログ信号Vg)およびデジタル信号(デジタル信号Dout1,デジタル信号Dout2,デジタル信号Dout)の関係について説明する。図4は、本第1の実施形態のA/D変換回路100におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【0068】

図4(a)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換期間Taのときにデジタル生成回路105が算出するデジタル信号Dout1との関係を示している。また、図4(b)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換回路1033が生成するアナログ信号Vgとの関係を示している。また、図4(c)には、入力調整回路101によって調整されたアナログ信号Vcと、第2サンプリングのあとにデジタル生成回路105が算出するデジタル信号Dout2との関係を示している。また、図4(d)は、入力調整回路101によって調整されたアナログ信号Vcと、デジタル生成回路105が最終的に算出するデジタル信号Doutとの関係を示している。

【0069】

なお、図4において、アナログ信号Vcの電圧値Vmは、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/n)である。また、ΔVは、第1サンプリングのときの量子化ステップ幅である。以下の説明においては、図4(a)に示したように、第1サンプリングのときのアナログ信号Vcの電圧値Vmに対応するデジタル信号Dout1の値をDthとし、デジタル信号Dout1の値が(Dth−1)からDthに切り替わるときのアナログ信号Vcの電圧値をVm’とする。

【0070】

図4(a)に示したように、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1≧Dthとなった場合、アナログ信号Vcの電圧値は、Vc≧Vm’であると判定し、アナログ変換期間Taにおいて、Highのデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1<Dthとなった場合、アナログ信号Vcの電圧値は、Vc<Vm’であると判定し、アナログ変換期間Taにおいて、Lowのデジタルオフセット信号Dofを出力する。すなわち、デジタル生成回路105は、予め定められたデジタル信号Dout1の値Dthを閾値として、HighまたはLowの1bitのデジタルオフセット信号Dofを生成している。

【0071】

このようにしてアナログ変換期間Taでは、デジタル生成回路105が生成したデジタルオフセット信号Dofの値(HighまたはLow)によって、第1サンプリングのときに入力されたアナログ信号Vcの電圧値と、アナログ信号Vcの電圧値Vmとの大小を判定する。そして、第2サンプリングのときに遅延回路102に入力される、上式(2)で表されるアナログ信号Vgは、下式(3)で表される。

【0072】

【数3】

【0073】

図4(b)は、上式(3)におけるアナログ信号Vcとアナログ信号Vgとの関係を表している。

【0074】

ところで、電圧値がVm’≦Vc≦Vmのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(3)より、Vg=2Vc−Vmaxとなり、図4(b)に示したように、アナログ信号Vgの電圧値はVg≦Vminとなる。ここで、仮に、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合を考える。この場合に、電圧値がVm’≦Vc≦Vmのアナログ信号Vcがアナログ変換回路1033に入力されると、アナログ信号Vgの電圧値は、A/D入力範囲の最小値Vluよりも小さくなり、遅延回路102のA/D入力範囲を超えてしまうことも考えられる。以下の説明においては、アナログ信号Vgの電圧値が遅延回路102のA/D入力範囲を超えてしまう現象を、「オーバーレンジ」という。アナログ信号Vgの電圧値は、第1サンプリングのときの量子化ステップ幅であるΔVの幅が大きい、すなわち、第1サンプリング期間Ts1が短いと、よりオーバーレンジとなりやすい。このため、入力調整回路101は、アナログ変換回路1033が生成するアナログ信号Vgがオーバーレンジとならないように、上式(1)を満たすような、アナログ信号Vcの最小値Vminおよび最大値Vmaxを設定している。本第1の実施形態のA/D変換回路100では、n=2であるため、図4(b)に示したように、アナログ信号Vgの最小値Vminが、Vmin≧Vlu+2ΔVとなるような、アナログ信号Vcの最小値Vminを設定している。

【0075】

図4(c)は、アナログ信号Vcを横軸として、第2サンプリングのときのアナログ信号Vgに対応するデジタル信号Dout2を縦軸に表している。図4(c)に示したように、アナログ信号Vcの最小値Vminから電圧値Vm’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw1を、アナログ信号Vcの電圧値Vm’から最大値Vmaxまでの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw2を、それぞれ取得することができる。ここで、アナログ信号Vcの電圧値Vm’から電圧値Vmまでの電圧範囲におけるデジタル信号Dout2のデジタル信号幅をΔDwとする。このとき、アナログ信号範囲の約1/2(=1/n、n=2)となるアナログ信号Vcの最小値Vminから電圧値Vmまでの電圧範囲、またはアナログ信号Vcの電圧値Vmから最大値Vmaxまでの電圧範囲におけるデジタル信号幅Dwは、Dw=Dw1+ΔDw=Dw2−ΔDwを取得することができる。

【0076】

n=2の場合において、このデジタル信号幅Dwは、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号Vcの最小値Vminから最大値Vmaxまでの電圧範囲に対応するデジタル信号幅Dwsの1/2(=1/n、n=2)に等しくなる。すなわち、デジタル信号幅Dwは、Dw=Dws/n=Dws/2となる。

【0077】

これは、A/D変換回路100が、サンプリング期間と電圧分解能が比例する関係にあることから、n=2の場合において、第2サンプリング期間Ts2をサンプリング期間Tsの1/2(=1/n)、すなわち、Ts2=(1/n)Ts=Ts/2とする代わりに、アナログ信号範囲を2倍(n倍、n=2)に拡大する処理を行っているためである。

【0078】

図4(d)は、アナログ信号Vcを横軸として、デジタルオフセット信号Dof、およびデジタル信号Dout2に基づいて算出したデジタル信号Doutを縦軸に表している。デジタル生成回路105は、デジタルオフセット信号Dofに応じて、図4(c)に示したデジタル信号Dout2のデジタル信号幅Dw2を、デジタル信号幅Dw1の上にオフセットし、図4(d)に示したような、デジタル信号幅Dwoのデジタル信号Doutを算出する。より具体的には、デジタルオフセット信号Dofの値がHighであるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vmax/nにおけるデジタル信号幅Dw2の値を加算することによって、デジタル信号Doutを算出する。これにより、図4(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2=2Dwとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。

【0079】

このように、A/D変換回路100では、図2に示したように、第1サンプリング期間Ts1をTs1<(1−1/n)Tsと設定し、第2サンプリング期間Ts2をTs2=(1/n)Tsと設定する。また、アナログ変換期間Taは、第1サンプリング期間Ts1や第2サンプリング期間Ts2に比べて非常に短い期間とする。これにより、A/D変換回路100では、上述した3つの期間を合計した、A/D変換回路100における1回のA/D変換期間であるサンプリング期間Tsum(≒Ts1+Ts2)を、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間とすることができる。

【0080】

また、A/D変換回路100では、第1サンプリングの結果に基づいて算出したデジタル信号Dout1から、アナログ信号Vcをオフセットするためのアナログオフセット信号を選択するデジタルオフセット信号Dofを生成する。そして、生成したデジタルオフセット信号Dofと、第2サンプリングの結果に基づいて算出したデジタル信号Dout2とに基づいて、最終的なデジタル信号Doutを算出する。これにより、A/D変換回路100では、サンプリング期間Tsよりも短いサンプリング期間Tsumにおいても、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル電圧幅Dwoのデジタル信号Doutを取得することができる。

【0081】

上記に述べたとおり、本第1の実施形態のA/D変換回路100は、サンプリング期間Tsよりも短い第1サンプリング期間Ts1で第1サンプリングを行い、第1サンプリングの結果に基づいて、予め定められたn個(本第1の実施形態では、n=2)のアナログオフセット信号の中から、実際にアナログ信号Vcをオフセットするアナログオフセット信号を選択する。そして、選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、サンプリング期間Tsの1/nのサンプリング期間の第2サンプリングを行い、最終的なデジタル信号Doutを算出する。すなわち、本第1の実施形態のA/D変換回路100では、第2サンプリング期間Ts2を1/n(本第1の実施形態では、n=2)とする代わりに、アナログ信号範囲をn倍(2倍)に拡大することによって、同様の電圧分解能のデジタル信号Doutを得る。これにより、従来のA/D変換回路400におけるサンプリング期間Tsのときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短く、すなわち、A/D変換を高速化することができる。

【0082】

なお、本第1の実施形態のA/D変換回路100では、n=2とし、2つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに2倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2で第2サンプリングを行う場合について説明した。しかし、アナログオフセット信号の数、増幅する倍数、サンプリング期間Tsを短くするための除数であるnは、2以上の正の整数であればよく、本第1の実施形態で説明した値に限定されるものではない。例えば、n=3とし、3つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに3倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/3とした第2サンプリング期間Ts2の第2サンプリングを行い、最終的なデジタル信号Doutを算出する構成にすることもできる。

【0083】

なお、本第1の実施形態のA/D変換回路100では、図4(b)で説明したように、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合に、電圧値がVm’≦Vc≦Vmのアナログ信号Vcがアナログ変換回路1033に入力されると、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしてしまうということが考えられていた。そこで、A/D変換回路100では、入力調整回路101が、アナログ変換回路1033が生成するアナログ信号Vgがオーバーレンジとならないように、アナログ信号Vcの最小値Vminおよび最大値Vmaxを設定していた。しかし、アナログ信号Vgの電圧値がオーバーレンジとならないようにする方法は、本第1の実施形態で説明した方法に限定されるものではない。

【0084】

<第2の実施形態>

次に、本発明の第2の実施形態について説明する。本第2の実施形態では、第1の実施形態とは異なる方法で、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしないようにする。なお、本第2の実施形態におけるA/D変換回路の構成は、第1の実施形態のA/D変換回路100に備えたA/D制御回路103内のアナログ変換回路1033が異なる構成となっているのみであり、その他の構成要素は、第1の実施形態のA/D変換回路100と同様の構成である。より具体的には、図1に示した第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033に代わって、後述するアナログ変換回路2033を備えているのみである。従って、本第2の実施形態のA/D変換回路の説明においては、第1の実施形態のA/D変換回路100とは異なる構成、および動作のみを説明して、詳細な説明は省略する。なお、以下の説明においては、本第2の実施形態のA/D変換回路の構成要素において、図1に示した第1の実施形態のA/D変換回路100と同様の構成要素は、同一の符号を用いて説明する。例えば、本第2の実施形態のA/D変換回路も、A/D変換回路100として説明する。

【0085】

本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、1回のA/D変換期間内に、2回のサンプリングを行う。ただし、本第2の実施形態のA/D変換回路100では、アナログオフセット信号の数が、第1の実施形態のA/D変換回路100と異なる。なお、本第2の実施形態では、増幅する倍数およびサンプリング期間Tsを短くするための除数であるn(n:正の整数、n≧2)の数値がn=2、アナログオフセット信号の数であるm(m:正の整数、m≧2n−1)の数値がm=3、である場合について説明する。

【0086】

本第2の実施形態のA/D変換回路100に備えた入力調整回路101は、第1の実施形態のA/D変換回路100に備えた入力調整回路101と同様に、入力されたアナログ信号Vinの電圧の範囲を、アナログ信号Vinのダイナミックレンジが、最小値Vminから最大値Vmaxまでのアナログ信号範囲となるように調整した、アナログ信号Vcを出力する。ここで、アナログ信号範囲は、第1の実施形態のA/D変換回路100に備えた入力調整回路101と同様に、最小値Vluから最大値Vloまでの遅延回路102のA/D入力範囲よりも小さい(狭い)範囲である。ただし、本第2の実施形態のA/D変換回路100に備えた入力調整回路101では、アナログ信号範囲の最大値Vmaxおよび最小値Vminと、A/D入力範囲の最大値Vloおよび最小値Vluとは、下式(4)の関係にある。

【0087】

【数4】

【0088】

A/D制御回路103は、サンプリング制御回路1031と、クロック生成回路1032と、アナログ変換回路2033と、を備えている。上述したように、本第2の実施形態のA/D変換回路100では、第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033が、アナログ変換回路2033に代わっている。サンプリング制御回路1031およびクロック生成回路1032は、第1の実施形態のA/D変換回路100に備えたサンプリング制御回路1031およびクロック生成回路1032と同様であるため、詳細な説明は省略する。

【0089】

アナログ変換回路2033は、第1の実施形態のアナログ変換回路1033と同様に、入力調整回路101から入力されたアナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。アナログ変換回路2033は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、アナログオフセット信号を切り替える。そして、アナログ変換回路2033は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または生成したアナログ信号Vgのいずれか一方のアナログ信号を、アナログ信号Vxとして遅延回路102に出力する。

【0090】

デジタル生成回路105は、デジタル信号Dout1の数値に基づいて、アナログ信号Vcを、アナログオフセット信号で調整するための制御信号であるデジタルオフセット信号Dofを生成し、生成したデジタルオフセット信号Dofを、アナログ変換回路2033に出力する。なお、本第2の実施形態のA/D変換回路100では、m=3であるため、3つのアナログオフセット信号から1つのアナログオフセット信号を選択するためのデジタルオフセット信号Dofを、アナログ変換回路2033に出力する。

【0091】

本第2の実施形態のA/D変換回路100におけるA/D変換の動作手順は、図2に示した第1の実施形態のA/D変換回路100における動作手順(タイミングチャート)と同様であるため、詳細な説明は省略する。

【0092】

次に、アナログ信号Vgの算出方法について説明する。図5は、本第2の実施形態のA/D変換回路100に備えたアナログ変換回路2033の概略構成を示したブロック図である。図5に示したアナログ変換回路2033は、減算回路2034と、増幅回路2035と、3値(m=3)のアナログオフセット信号Vmax/n、Vm/n、およびVmin/nと、スイッチ5と、スイッチ6と、を備えている。

【0093】

アナログオフセット信号Vmax/n、Vm/n、およびVmin/nは、アナログ信号Vcをオフセットするために、予め定められたアナログ信号である。本第2の実施形態のA/D変換回路100では、m=3であるため、3つのアナログオフセット信号Vmax/nと、アナログオフセット信号Vm/nと、アナログオフセット信号Vmin/nとが、予め定められている。ここで、アナログオフセット信号VmaxおよびVminの電圧値は、それぞれアナログ信号範囲の最大値Vmaxおよび最小値Vminである。また、アナログオフセット信号Vmの電圧値は、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/2)である。

【0094】

スイッチ6は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、3つのアナログオフセット信号Vmax/n、Vm/n、およびVmin/nの中から、1つのアナログオフセット信号を、減算回路2034に出力する。ここで、デジタル生成回路105から入力されるデジタルオフセット信号Dofは、“0”、“1”、“2”のいずれかの数値を示すことによって、3つのアナログオフセット信号Vmax/n、Vm/n、またはVmin/nの中から、いずれか1つを選択するための制御信号である。スイッチ6の出力端子は、デジタルオフセット信号Dof=2のとき、アナログオフセット信号Vmax/nの入力端子に接続され、デジタルオフセット信号Dof=1のとき、アナログオフセット信号Vm/nの入力端子に接続され、デジタルオフセット信号Dof=0のとき、アナログオフセット信号Vmin/nの入力端子に接続される。

【0095】

減算回路2034は、入力調整回路101から入力されたアナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmax/n、Vm/n、またはVmin/nの中のいずれかを減算する。そして、アナログオフセット信号を減算したアナログ信号Vcを、増幅回路2035に出力する。より具体的には、デジタルオフセット信号Dof=2の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmax/nを減算し、増幅回路2035に出力する。また、デジタルオフセット信号Dof=1の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vm/nを減算し、増幅回路2035に出力する。また、デジタルオフセット信号Dof=0の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmin/nを減算し、増幅回路2035に出力する。

【0096】

増幅回路2035は、減算回路2034から入力された、アナログオフセット信号Vmax/n、Vm/n、またはVmin/nのいずれかが減算されたアナログ信号Vcを増幅したアナログ信号Vcを生成し、アナログ信号Vgとして出力する。本第2の実施形態のA/D変換回路100では、n=2であるため、増幅回路2035は、アナログオフセット信号が減算されたアナログ信号Vcを2倍に増幅したアナログ信号Vgを生成する。このときのアナログ信号Vgは、下式(5)で表される。

【0097】

【数5】

【0098】

スイッチ5は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または増幅回路2035が増幅したアナログ信号Vgいずれか一方を、アナログ変換回路2033が出力するアナログ信号Vxとして、遅延回路102に出力する。スイッチ5の出力端子は、アナログ切り替え信号Ps=Highのとき、アナログ信号Vcの入力端子に接続され、アナログ切り替え信号Ps=Lowのとき、アナログ信号Vgの入力端子に接続される。

【0099】

第1サンプリングのとき、アナログ切り替え信号Ps=Highにより、スイッチ5の出力端子は、アナログ変換回路2033のアナログ信号Vcの入力端子に接続される。これより、アナログ信号Vxはアナログ信号Vcに等しくなり、遅延回路102に出力される。

【0100】

第2サンプリングのとき、アナログ切り替え信号Ps=Lowにより、スイッチ5の出力端子は、増幅回路2035の出力端子に接続される。これより、アナログ信号Vxはアナログ信号Vgに等しくなり、遅延回路102に出力される。

【0101】

次に、本第2の実施形態のA/D変換回路100におけるアナログ信号(アナログ信号Vc,アナログ信号Vg)およびデジタル信号(デジタル信号Dout1,デジタル信号Dout2,デジタル信号Dout)の関係について説明する。図6は、本第2の実施形態のA/D変換回路100におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【0102】

図6(a)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換期間Taのときにデジタル生成回路105が算出するデジタル信号Dout1との関係を示している。また、図6(b)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換回路2033が生成するアナログ信号Vgとの関係を示している。また、図6(c)には、入力調整回路101によって調整されたアナログ信号Vcと、第2サンプリングのあとにデジタル生成回路105が算出するデジタル信号Dout2との関係を示している。また、図6(d)は、入力調整回路101によって調整されたアナログ信号Vcと、デジタル生成回路105が最終的に算出するデジタル信号Doutとの関係を示している。

【0103】

なお、図6において、アナログ信号Vcの電圧値Vmは、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/n)である。また、ΔVは、第1サンプリングのときの量子化ステップ幅である。以下の説明においては、図6(a)に示したように、第1サンプリングのときのアナログ信号Vcの電圧値Vmよりも少し大きいアナログ信号Vcの電圧値Vmoに対応するデジタル信号Dout1の値をDthoとし、デジタル信号Dout1の値が(Dtho−1)からDthoに切り替わるときのアナログ信号Vcの電圧値をVmo’とする。また、アナログ信号Vcの電圧値Vmよりも少し小さいアナログ信号Vcの電圧値Vmuに対応するデジタル信号Dout1の値をDthuとし、デジタル信号Dout1の値が(Dthu−1)からDthuに切り替わるときのアナログ信号Vcの電圧値をVmu’とする。

【0104】

図6(a)に示したように、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1≧Dthoとなった場合、アナログ信号Vcの電圧値は、Vc≧Vmo’であると判定し、アナログ変換期間Taにおいて、“2”のデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDthu≦Dout1<Dthoとなった場合、アナログ信号Vcの電圧値は、Vmu’≦Vc<Vmo’であると判定し、アナログ変換期間Taにおいて、“1”のデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1<Dthuとなった場合、アナログ信号Vcの電圧値は、Vc<Vmu’であると判定し、アナログ変換期間Taにおいて、“0”のデジタルオフセット信号Dofを出力する。すなわち、デジタル生成回路105は、予め定められたデジタル信号Dout1の値DthoおよびDthuを閾値として、“0”、“1”、“2”のいずれかの数値を示す2bitのデジタルオフセット信号Dofを生成している。

【0105】

このようにしてアナログ変換期間Taでは、デジタル生成回路105が生成したデジタルオフセット信号Dofの値(“0”、“1”、“2”のいずれかの数値)によって、第1サンプリングのときに入力されたアナログ信号Vcの電圧値と、アナログ信号Vcの電圧値とを比較する。そして、第2サンプリングのときに遅延回路102に入力される、上式(5)で表されるアナログ信号Vgは、下式(6)で表される。

【0106】

【数6】

【0107】

図6(b)は、上式(6)におけるアナログ信号Vcとアナログ信号Vgとの関係を表している。

【0108】

ところで、電圧値がVmo’≦Vc≦Vmoのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(6)より、Vg=2Vc−Vmaxとなり、図6(b)に示したように、アナログ信号Vgの電圧値はVg>Vminである。また、電圧値がVmu’≦Vc≦Vmuのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(6)より、Vg=2Vc−Vmとなり、また、図6(b)に示したように、アナログ信号Vgの電圧値はVg>Vminである。従って、本第2の実施形態のA/D変換回路100では、仮に、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合でも、アナログ信号Vgの電圧値は、A/D入力範囲をオーバーレンジしない。

【0109】

すなわち、本第2の実施形態のA/D変換回路100では、アナログ信号Vcの2つ((m−1)個、m=3)の電圧値VmoおよびVmuに対応するデジタル信号Dout1の値DthoおよびDthuを設け、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値に応じて、デジタルオフセット信号Dofの出力値を決定する。これにより、第1の実施形態のA/D変換回路100では、上式(1)に示したように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要があったが、本第2の実施形態のA/D変換回路100では、上式(4)に示したように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要がなく、アナログ信号Vgのオーバーレンジを回避することができる。

【0110】

このため、本第2の実施形態のA/D変換回路100では、入力調整回路101によるアナログ信号Vinの電圧の範囲の調整は、アナログ信号Vcがアナログ信号範囲となるように調整するのみとなる。このとき、例えば、アナログ信号Vinのダイナミックレンジが、遅延回路102のA/D入力範囲を必ず超えることがないのであれば、本第2の実施形態のA/D変換回路100に入力調整回路101を備えない構成とすることも可能となる。

【0111】

図6(c)は、アナログ信号Vcを横軸として、第2サンプリングのときのアナログ信号Vgに対応するデジタル信号Dout2を縦軸に表している。図6(c)に示したように、アナログ信号Vcの最小値Vminから電圧値Vmu’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw1を、アナログ信号Vcの電圧値Vmu’から電圧値Vmo’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw2を、アナログ信号Vcの電圧値Vmo’から最大値Vmaxまでの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw3を、それぞれ取得することができる。

【0112】

ここで、n=2の場合において、デジタル信号幅Dw1とDw2とDw3との合計値(Dw1+Dw2+Dw3)を、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル信号幅Dwsに等しくする、すなわち、Dws=Dw1+Dw2+Dw3=Dwoとするためには、アナログ信号Vcの電圧値VmoとVmuとを、例えば、下式(7)のように設定する。

【0113】

【数7】

【0114】

図6(d)は、アナログ信号Vcを横軸として、デジタルオフセット信号Dof、およびデジタル信号Dout2に基づいて算出したデジタル信号Doutを縦軸に表している。デジタル生成回路105は、デジタルオフセット信号Dofに応じて、図6(c)に示したデジタル信号Dout2のデジタル信号幅Dw1の上にデジタル信号幅Dw2をオフセットし、さらに上に、デジタル信号幅Dw3をオフセットし、図6(d)に示したような、デジタル信号幅Dwoのデジタル信号Doutを算出する。より具体的には、デジタルオフセット信号Dofの値が“1”であるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vm/nにおけるデジタル信号幅Dw2の値を加算することによって、デジタル信号Doutを算出する。また、デジタルオフセット信号Dofの値が“2”であるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vmax/nにおけるデジタル信号幅Dw2とデジタル信号幅Dw3との合計値(Dw2+Dw3)を加算することによって、デジタル信号Doutを算出する。これにより、図6(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2+Dw3=Dwoとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。これにより、図6(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2=2Dwとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。

【0115】

このように、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、1回のA/D変換期間であるサンプリング期間Tsum(≒Ts1+Ts2)を、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間とすることができる。また、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、サンプリング期間Tsよりも短いサンプリング期間Tsumにおいても、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル電圧幅Dwoのデジタル信号Doutを取得することができる。

【0116】

また、本第2の実施形態のA/D変換回路100では、アナログ信号Vcの2つ((m−1)個、m=3)の電圧値VmoおよびVmuに対応するデジタル信号Dout1の値DthoおよびDthuを設け、第1サンプリングの結果に基づいて算出したデジタル信号Dout1から、アナログ信号Vcをオフセットするためのアナログオフセット信号を選択するデジタルオフセット信号Dofを生成する。これにより、第1の実施形態のA/D変換回路100のように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要がなく、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしてしまうことを、回避することができる。

【0117】

上記に述べたとおり、本第2の実施形態のA/D変換回路100は、サンプリング期間Tsよりも短い第1サンプリング期間Ts1で第1サンプリングを行い、第1サンプリングの結果に基づいて、予め定められたm個(本第2の実施形態では、m=3)のアナログオフセット信号の中から、実際にアナログ信号Vcをオフセットするアナログオフセット信号を選択する。これにより、アナログ信号範囲をA/D入力範囲よりも狭める必要なく、アナログ信号Vgの電圧値がA/D入力範囲からオーバーレンジしてしまうことを、回避する。そして、選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、サンプリング期間Tsの1/nのサンプリング期間の第2サンプリングを行い、最終的なデジタル信号Doutを算出する。すなわち、本第2の実施形態のA/D変換回路100でも、第2サンプリング期間Ts2を1/n(本第2の実施形態では、n=2)とする代わりに、アナログ信号範囲をn倍(2倍)に拡大することによって、同様の電圧分解能のデジタル信号Doutを得る。これにより、アナログ信号範囲を狭めることなく、従来のA/D変換回路400におけるサンプリング期間Tsのときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短く、すなわち、A/D変換を高速化することができる。

【0118】

なお、本第2の実施形態のA/D変換回路100では、m=3とし、3つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに、n=2とし、2倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2で第2サンプリングを行う場合について説明した。しかし、アナログオフセット信号の数であるmは、3以上の正の整数であればよく、本第2の実施形態で説明した値に限定されるものではない。例えば、n=2,m=4とし、4つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに2倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2の第2サンプリングを行い、最終的なデジタル信号Doutを算出する構成にすることもできる。また、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、増幅する倍数およびサンプリング期間Tsを短くするための除数であるnは、2以上の正の整数であればよく、本第2の実施形態で説明した値に限定されるものではない。

【0119】

<第3の実施形態>

以下、本発明の第3の実施形態について説明する。図7は、本発明のA/D変換回路を列毎に複数搭載したカラムA/D変換回路方式の固体撮像装置の概略構成を示したブロック図である。図7に示した固体撮像装置300は、画素部301と、垂直走査回路302と、水平走査回路303と、信号処理回路304と、カラムA/D変換回路305と、制御回路306と、を備えている。なお、図7においては、図1に示した本発明の第1、または第2の実施形態のA/D変換回路100を、固体撮像装置300に備えた場合の一例を示している。

【0120】

固体撮像装置300は、画素部301の各画素7が発生した光電変換信号に対して信号処理回路304によって各種の信号処理を行い、その後、カラムA/D変換回路305によってA/D変換してデジタル信号Doutとして出力する。

【0121】

制御回路306は、垂直走査回路302と、水平走査回路303と、信号処理回路304と、カラムA/D変換回路305と、を駆動させるための制御信号を出力する。

【0122】

垂直走査回路302は、制御回路306から出力された制御信号に応じて、画素部301内の画素7を画素部301の行単位で選択し、選択した行の各画素7から生成された光電変換信号を信号処理回路304に出力させる。

【0123】

画素部301は、複数の画素7を行方向および列方向の二次元的に配置した画素アレイである。各画素7は、フォトダイオードを備え、一定の蓄積時間内に入射した光量に応じた光電変換信号を発生し、垂直走査回路302からの選択に応じて、生成した光電変換信号を信号処理回路304に出力する。

【0124】

信号処理回路304は、制御回路306から入力された制御信号に応じて、画素部301から入力された光電変換信号からリセット雑音と1/f雑音とを除去した後、信号を増幅する。信号処理回路304は、増幅した信号をアナログ信号VinとしてカラムA/D変換回路305に出力する。

【0125】

カラムA/D変換回路305は、同じ構成のA/D変換回路100を、画素部301の列の数だけ複数備えている。ただし、カラムA/D変換回路305内に備えたA/D変換回路100は、A/D制御回路103内のクロック生成回路1032、およびサンプリング制御回路1031をそれぞれ備える構成ではなく、全てのA/D変換回路100に共通のクロック生成回路1032、およびサンプリング制御回路1031を1つのみ備えている。図7では、カラムA/D変換回路305内に備えた全てのA/D変換回路100に共通のクロック生成回路1032とサンプリング制御回路1031とをまとめて、タイミング生成回路110として表している。各列に備えたA/D変換回路100のそれぞれは、制御回路306から入力された制御信号に応じて、信号処理回路304から入力されたアナログ信号Vinを、A/D変換したデジタル信号Doutを出力する。

【0126】

水平走査回路303は、制御回路306から入力された制御信号に応じて、カラムA/D変換回路305の各A/D変換回路100によってA/D変換されたデジタル信号Doutを、画素部301の列単位で選択する。水平走査回路303が選択された列のデジタル信号Doutが、固体撮像装置300の出力として順次出力される。

【0127】

上記に述べたように、本第3の実施形態の固体撮像装置300では、画素部301の各画素7が生成した光電変換信号に対して信号処理回路304によって各種の信号処理を行って、アナログ信号Vinを取得する。その後、カラムA/D変換回路305によってアナログ信号VinをA/D変換したデジタル信号Doutを出力する。このとき、カラムA/D変換回路305内の各A/D変換回路100は、従来のA/D変換回路400におけるサンプリング期間Tsよりも短いサンプリング期間Tsumで、従来のA/D変換回路400がサンプリング期間TsでA/D変換したときと同等の電圧分解能のデジタル信号Doutを出力することができる。

【0128】

このことにより、本第3の実施形態の固体撮像装置300内のカラムA/D変換回路305は、図8に示した従来のA/D変換回路400を画素部の各列に備えた、図示しない従来のカラムA/D変換回路がサンプリング期間TsでA/D変換したときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短くし、高速化することができる。

【0129】

また、本第3の実施形態の固体撮像装置300では、カラムA/D変換回路305内の各A/D変換回路として、図1に示した本発明の第1、または第2の実施形態のA/D変換回路100を備えている。しかし、固体撮像装置300に備えたカラムA/D変換回路305内には、上記に述べたように、全てのA/D変換回路100に共通のタイミング生成回路110(クロック生成回路1032およびサンプリング制御回路1031)を1つのみ備えている。このため、本第3の実施形態の固体撮像装置300では、クロック生成回路1032およびサンプリング制御回路1031を備えたA/D変換回路100を、画素部301の列毎に備える場合よりも、固体撮像装置300に備えるカラムA/D変換回路305の回路規模を削減することができる。この回路規模の削減は、固体撮像装置300のように、狭小な領域内にA/D変換回路を搭載するような場合において有効であり、固体撮像装置300は、回路規模が削減された状態で、従来の固体撮像装置と同等の電圧分解能のデジタル信号Doutを、高速に出力することができる。

【0130】

なお、本第3の実施形態の固体撮像装置300においては、カラムA/D変換回路305内に、同じ構成のA/D変換回路100を、画素部301の列の数だけ複数備える場合について説明したが、画素部301の複数の列毎に1つのA/D変換回路100を複数備える構成とすることもできる。すなわち、A/D変換回路100を画素部301の複数の列で共有する構成とすることもできる。このような構成であっても、同様に、A/D変換回路100の高速化の効果を得ることができる。

【0131】

また、本第3の実施形態の固体撮像装置300においては、カラムA/D変換回路305内に、全てのA/D変換回路100に共通のタイミング生成回路110(クロック生成回路1032およびサンプリング制御回路1031)を1つのみ備える場合について説明したが、共通のタイミング生成回路110を、例えば、制御回路306や、水平走査回路303の中に備える構成とすることもできる。また、共通のタイミング生成回路110を、固体撮像装置300の外部の制御装置に備える構成とすることもできる。これにより、固体撮像装置300の回路規模を削減することができる。

【0132】

上記に述べたとおり、本発明を実施するための形態によれば、従来のA/D変換回路におけるサンプリング期間Tsに対して、Ts1<(1−1/n)Tsである第1サンプリング期間Ts1と、Ts2=(1/n)Tsである第2サンプリング期間Ts2とを設定する。また、第1サンプリング期間Ts1や第2サンプリング期間Ts2に比べて非常に短いアナログ変換期間Taを設ける。そして、第1サンプリング期間Ts1で第1サンプリングを行い、アナログ変換期間Taの期間で、第1サンプリングの結果に基づいて、予め定められたn個のアナログオフセット信号の中から、入力されたアナログ信号を実際にオフセットするアナログオフセット信号を選択する。その後、入力されたアナログ信号を選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号で、第2サンプリング期間Ts2の第2サンプリングを行う。そして、アナログオフセット信号を選択するための制御信号の値と第1サンプリングの結果とに基づいて、最終的なデジタル信号を算出する。従来のA/D変換回路が出力するデジタル信号の電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短くすることによるA/D変換の高速化を実現することができる。

【0133】

また、本発明を実施するための形態によれば、A/D変換回路を固体撮像装置内に搭載した場合に、従来の固体撮像装置が出力するデジタル信号の電圧分解能と同等の電圧分解能を確保した上で、A/D変換回路のサンプリング期間を短くすることによる固体撮像装置の高速化を実現することができる。これにより、従来の固体撮像装置に対して、デジタル信号の電圧分解能を犠牲にすることなく、高速な固体撮像装置を提供することができる。

【0134】

なお、本実施形態においては、例えば、アナログ変換回路1033およびアナログ変換回路2033において、入力されたアナログ信号Vcからアナログ信号Vgを生成する際に、アナログ信号Vcからアナログオフセット信号を減算した後に増幅する場合について説明した。しかし、アナログ信号Vgを生成する際の処理は、本発明を実施するための形態に限定されるものではない。例えば、入力されたアナログ信号Vcを最初に増幅し、増幅されたアナログ信号Vcからアナログオフセット信号を減算してアナログ信号Vgを生成する構成、つまり、アナログ変換回路1033においては、減算回路1034と増幅回路1035とが逆の配置になっている構成とすることもできる。

【0135】

また、本実施形態においては、例えば、アナログ変換回路1033およびアナログ変換回路2033において、デジタルオフセット信号Dofの値毎に1つアナログオフセット信号を備えている場合の例について説明した。しかし、アナログオフセット信号の電圧値は、図示した実際にアナログ信号Vcをオフセットするアナログオフセット信号の電圧値を実現することができればよく、アナログオフセット信号の構成は、本発明を実施するための形態に限定されるものではない。例えば、複数の電圧値のオフセット信号をアナログ変換回路1033内に備え、デジタルオフセット信号Dofの値に応じて選択されるアナログオフセット信号の電圧値を、複数のオフセット信号の電圧値の組み合わせで実現する構成とすることもできる。より具体的には、例えば、電圧値が1Vのアナログオフセット信号を選択する場合、電圧値が0.3Vのオフセット信号と、電圧値が0.7Vのオフセット信号とを組み合わせて、電圧値が1Vのアナログオフセット信号を実現することもできる。

【0136】

また、本実施形態においては、遅延素子1としてNAND回路およびNOT回路を使用した場合の例について説明したが、遅延素子1として使用する回路は、本発明を実施するための形態に限定されるものではない。例えば、遅延素子1として、NOR回路(否定論理和ゲート)、差動回路など、様々な構成の遅延素子であってもよい。

【0137】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲においての種々の変更も含まれる。

【符号の説明】

【0138】

100・・・A/D変換回路(A/D変換装置)

101・・・入力調整回路

102・・・遅延回路

1,1a,1b・・・遅延素子

2・・・バッファ

103・・・A/D制御回路

1031・・・サンプリング制御回路(A/D制御回路,タイミング生成回路)

1032・・・クロック生成回路(A/D制御回路,タイミング生成回路)

110・・・タイミング生成回路

1033,2033・・・アナログ変換回路(A/D制御回路,アナログ変換回路)

1034,2034・・・減算回路(A/D制御回路)

1035,2035・・・増幅回路(A/D制御回路)

Vmax/n,Vm/n,Vmin/n・・・アナログオフセット信号

3,5・・・スイッチ(A/D制御回路)

4,6・・・スイッチ(A/D制御回路)

104・・・サンプリング回路

1041・・・ラッチ&エンコーダ回路

1042・・・カウンタ

1043・・・ラッチ回路

105・・・デジタル生成回路

300・・・固体撮像装置

301・・・画素部

7・・・画素

302・・・垂直走査回路

303・・・水平走査回路

304・・・信号処理回路

305・・・カラムA/D変換回路(A/D変換装置)

306・・・制御回路

400・・・A/D変換回路(A/D変換装置)

401・・・遅延回路

402・・・クロック生成回路

403・・・パルス位置数値化回路

4031・・・ラッチ&エンコーダ回路

4032・・・カウンタ

4033・・・ラッチ回路

4034・・・減算回路

【技術分野】

【0001】

本発明は、A/D変換装置および固体撮像装置に関する。

【背景技術】

【0002】

近年、固体撮像装置としてCMOS(Complementary Metal Oxide Semiconductor:相補型金属酸化膜半導体)イメージセンサが注目され、実用化されている。このCMOSイメージセンサは、CCD(Charge Copled Device:電荷結合素子)イメージセンサが専用の製造プロセスによって製造されるのに対し、一般的な半導体の製造プロセスを用いて製造することが可能である。このことから、CMOSイメージセンサは、例えば、SOC(System On Chip)のように、センサ内に種々の機能回路を組み込みことによって、多機能化を実現することが可能となっている。

【0003】

そして、近年では、デジタルカメラ、デジタルビデオカメラや内視鏡などに搭載する固体撮像装置として、アナログ・デジタル変換器(以下、「A/D変換回路」という)を内蔵した固体撮像装置を使用する例が増えている。このような固体撮像装置に内蔵されるA/D変換回路においては、その回路の全てをデジタル回路で実現したパルス遅延型A/D変換回路(特許文献1参照)を用いる場合がある。なお、以下の説明においてA/D変換回路といった場合には、パルス遅延型A/D変換回路のことを示すものとする。

【0004】

図8は、従来のA/D変換回路の概略構成を示したブロック図である。図8に示した従来のA/D変換回路400は、遅延回路401と、クロック生成回路402と、パルス位置数値化回路403と、を備えている。

【0005】

遅延回路401は、複数の遅延素子が円環状に接続されている。図8においては、遅延回路401が、初段の遅延素子1aが、否定論理積ゲート(NAND回路)などのような、2つの入力端子を有する論理ゲート、その他の段の遅延素子1bが、論理否定ゲート(NOT回路)などのような、1つの入力端子を有する論理ゲートで構成されている場合を示している。なお、以下の説明において、遅延素子1aと遅延素子1bとを区別しない場合には、単に「遅延素子1」という。

【0006】

初段の遅延素子1aには、パルス信号Pinと、最終段の遅延素子1bの出力信号とが入力される。また、次段以降の各遅延素子1bには、前段の遅延素子1の出力信号が入力される。パルス信号Pinが、初段の遅延素子1aに入力されると、遅延回路401内の走行を開始する。このとき、各遅延素子1は、印加された駆動電圧の大きさに応じた伝播遅延時間で、入力されたパルス信号Pinを伝播(走行)させる。なお、各遅延素子1は、印加された駆動電圧(アナログ信号Vin)が低いほど入力信号(パルス信号Pin)を長く遅延させる特性を備えている。各遅延素子1から出力された出力信号は、遅延回路401内を走行したパルス信号Pinの走行位置として、パルス位置数値化回路403に出力される。

【0007】

クロック生成回路402は、パルス信号Pinと、サンプリング期間がTsのサンプリングクロックCkを生成する。また、クロック生成回路402は、生成したパルス信号Pinを遅延回路401に、サンプリングクロックCkをパルス位置数値化回路403に、それぞれ出力する。

【0008】

パルス位置数値化回路403は、ラッチ&エンコーダ回路4031と、カウンタ4032と、ラッチ回路4033と、減算回路4034と、を備えている。

ラッチ&エンコーダ回路4031は、クロック生成回路402から入力されたサンプリングクロックCkのエッジに同期して、遅延回路401内を走行したパルス信号Pinの走行位置を検出する。また、ラッチ&エンコーダ回路4031は、検出したパルス信号Pinの走行位置を、bビット(bは正の整数)の数値に変換(エンコード)して減算回路4034に出力する。

【0009】

カウンタ4032は、サンプリング期間Ts内にパルス信号Pinが円環状の遅延回路401内を周回した周回数を取得する。また、カウンタ4032は、取得した周回数を、aビット(aは正の整数)の計数値としてラッチ回路4033に出力する。

ラッチ回路4033は、クロック生成回路402から入力されたサンプリングクロックCkのエッジに同期して、カウンタ4032から出力された計数値をラッチし、減算回路4034に出力する。

【0010】

減算回路4034は、ラッチ回路4033から出力された出力信号を上位ビット値a、ラッチ&エンコーダ回路4031から出力された出力信号を下位ビット値bとする合成デジタル値abを取り込む。そして、減算回路4034は、最新(今回)のサンプリングによる合成デジタル値abから、前回のサンプリングによる合成デジタル値abを差し引く減算処理を行い、サンプリング期間Ts内にパルス信号Pinが伝播した遅延素子1の個数を表すデジタル信号Doutを算出する。

このようにして、図8に示した従来のA/D変換回路400では、アナログ信号Vinをデジタル信号Doutに変換、すなわち、A/D変換することができる。

【先行技術文献】

【特許文献】

【0011】

【特許文献1】特許第3064644号公報

【発明の概要】

【発明が解決しようとする課題】

【0012】

このようなA/D変換回路400において、高速な処理を実行する(以下、「高速化」という)ことが求められている。そこで、A/D変換回路400の高速化を実現するための方法として、サンプリング期間Tsを短くすることが考えられる。

【0013】

しかしながら、従来のA/D変換回路400の電圧分解能は、サンプリング期間Tsに関係している。そして、従来のA/D変換回路400では、サンプリング期間Tsを長くした方が、電圧分解能が高くなる、という性質を備えている。これは、サンプリング期間Tsが長い方が、パルス信号Pinが遅延素子1を伝播する個数が多くなり、パルス信号Pinが伝搬した遅延素子1の個数を表すデジタル信号Doutの値が大きくなるからである。そして、例えば、同じアナログ信号VinをA/D変換した場合には、デジタル信号Doutの値が大きい方が、デジタル信号Doutの最小単位(例えば、最下位ビット)が表すアナログ信号Vinの電圧幅である量子化ステップ幅が小さくなり、結果として、電圧分解能が高くなるというものである。ここで、量子化ステップ幅の単位は、[V/LSB]である。

【0014】

このため、A/D変換回路400の高速化を実現する方法として、サンプリング期間Tsを短くしてしまうと、A/D変換回路400の高速化を実現することができる一方、量子化ステップ幅が大きくなり、電圧分解能が低下してしまう、という問題がある。

【0015】

本発明は、上記の課題認識に基づいてなされたものであり、電圧分解能を低下させることなく、高速化することができるA/D変換装置および固体撮像装置を提供することを目的としている。

【課題を解決するための手段】

【0016】

上記の課題を解決するため、本発明のA/D変換装置は、入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い期間の第1のサンプリング期間と、(1/n)Tsの期間の第2のサンプリング期間とを設定し、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第1のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第1のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第2のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第2のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第2のサンプリングを行わせる、A/D制御回路と、前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、前記所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、を備えることを特徴とする。

【0017】

また、本発明のA/D変換装置は、前記A/D入力信号の電圧範囲が、前記遅延回路に入力することができる電圧の範囲である入力電圧範囲よりも小さい所定の電圧範囲となるように、前記A/D制御回路に入力する前記アナログ信号の電圧範囲を調整する入力調整回路、をさらに備え、前記A/D制御回路は、前記所定の電圧範囲に基づいて、それぞれの前記アナログオフセット信号を設定する、ことを特徴とする。

【0018】

また、本発明の前記入力調整回路は、前記入力電圧範囲の最大の電圧値から前記第1のデジタル信号の1ビットに対応する電圧値を減算した電圧値を、前記所定の電圧範囲における最大の電圧値として設定する、ことを特徴とする。

【0019】

また、本発明の前記入力調整回路は、前記入力電圧範囲の最小の電圧値に前記第1のデジタル信号の1ビットに対応する電圧値を加算した電圧値を、前記所定の電圧範囲における最小の電圧値として設定する、ことを特徴とする。

【0020】

また、本発明の前記A/D制御回路は、前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいて、前記デジタルオフセット信号に対応したn個の前記アナログオフセット信号を設定し、前記デジタルオフセット信号に応じて、n個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、ことを特徴とする。

【0021】

また、本発明の前記A/D制御回路は、前記デジタルオフセット信号に対応したm(m:正の整数、m≧2n−1)個の前記アナログオフセット信号を設定し、該設定される1個目およびm個目の前記アナログオフセット信号は、前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいた電圧値に設定され、前記デジタルオフセット信号に応じて、m個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、ことを特徴とする。

【0022】

また、本発明の固体撮像装置は、入射された光量に応じた光電変換信号を出力する複数の画素が2次元の行列状に配置された画素部と、入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、第1のサンプリングのときに、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力し、第2のサンプリングのときに、該アナログ信号をn(n:正の整数、n≧2)倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力するアナログ変換回路と、前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、を具備したA/D変換装置を、前記画素部の各列に対応したA/D変換回路として複数配置したカラムA/D変換回路と、前記所定のアナログ・デジタル変換期間Tsに対して、(1−1/n)Tsより短い期間の第1のサンプリング期間と、(1/n)Tsの期間の第2のサンプリング期間とを設定し、前記第1のサンプリング期間を開始するときに、前記パルス信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記遅延回路に出力し、該第1のサンプリング期間が終了するときに、前記サンプリングタイミング信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記サンプリング回路に出力して前記第1のサンプリングを行わせ、前記第2のサンプリング期間を開始するときに、前記パルス信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記遅延回路に出力し、該第2のサンプリング期間が終了するときに、前記サンプリングタイミング信号を前記カラムA/D変換回路に備える全ての前記A/D変換回路の前記サンプリング回路に出力して前記第2のサンプリングを行わせる、タイミング生成回路と、を備え、前記カラムA/D変換回路は、前記画素部の各列の前記画素から出力された前記光電変換信号のそれぞれを、対応する前記A/D変換回路に入力するそれぞれのアナログ信号とし、前記第2のサンプリングが終了した後に、それぞれの前記A/D変換回路が出力した前記デジタル信号を、該カラムA/D変換回路からの出力信号としてそれぞれ出力する、ことを特徴とする。

【発明の効果】

【0023】

本発明によれば、A/D変換装置の電圧分解能を低下させることなく、高速化することができるという効果が得られる。

【図面の簡単な説明】

【0024】

【図1】本発明の第1の実施形態におけるA/D変換回路の概略構成を示したブロック図である。

【図2】本第1の実施形態のA/D変換回路における、サンプリング時刻とデジタル信号との関係、および本第1の実施形態のA/D変換回路によるアナログ・デジタル変換動作における各信号のタイミングを示したタイミングチャートである。

【図3】本第1の実施形態のA/D変換回路に備えたアナログ変換回路の概略構成を示したブロック図である。

【図4】本第1の実施形態のA/D変換回路におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【図5】本第2の実施形態のA/D変換回路に備えたアナログ変換回路の概略構成を示したブロック図である。

【図6】本第2の実施形態のA/D変換回路におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【図7】本発明のA/D変換回路を列毎に複数搭載したカラムA/D変換回路方式の固体撮像装置の概略構成を示したブロック図である。

【図8】従来のA/D変換回路の概略構成を示したブロック図である。

【発明を実施するための形態】

【0025】

<第1の実施形態>

以下、本発明の第1の実施形態について、図面を参照して説明する。図1は、本第1の実施形態におけるA/D変換回路の概略構成を示したブロック図である。図1に示したA/D変換回路100は、入力調整回路101と、遅延回路102と、A/D制御回路103と、サンプリング回路104と、デジタル生成回路105と、を備えている。なお、以下の説明においては、図8に示したような従来のA/D変換回路400が、入力されたアナログ信号Vinをデジタル信号DoutにA/D変換するためのサンプリング期間を、「Ts」とする。

【0026】

本第1の実施形態のA/D変換回路100では、1回のA/D変換期間内に、入力されたアナログ信号Vinをデジタル信号DoutにA/D変換するためのサンプリングを、2回行う。ただし、本第1の実施形態のA/D変換回路100における合計のサンプリング期間は、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間である。より具体的には、A/D変換回路100は、(1−1/n)Tsより短いサンプリング期間の1回目のサンプリング(以下、「第1サンプリング」という)と、(1/n)Tsのサンプリング期間の2回目のサンプリング(以下、「第2サンプリング」という)との、2回のサンプリングを行う。なお、本第1の実施形態では、上記のn(n:正の整数、n≧2)の数値が、n=2である場合について説明する。

【0027】

入力調整回路101は、入力されたアナログ信号Vinの電圧の範囲を調整した、アナログ信号Vcを出力する。より具体的には、入力調整回路101は、アナログ信号Vinのダイナミックレンジが、最小値Vminから最大値Vmaxまでの電圧範囲(以下、「アナログ信号範囲」という)となるように、アナログ信号Vinを調整し、調整したアナログ信号Vinを、アナログ信号Vcとして出力する。ここで、アナログ信号範囲は、最小値Vluから最大値Vloまでの遅延回路102の入力電圧範囲(以下、「A/D入力範囲」という)よりも小さい(狭い)範囲である。アナログ信号範囲の最大値Vmaxおよび最小値Vminと、A/D入力範囲の最大値Vloおよび最小値Vluとは、下式(1)の関係にある。

【0028】

【数1】

【0029】

上式(1)において、ΔVは第1サンプリングのときの量子化ステップ幅である。

【0030】

遅延回路102は、k個(k:正の整数、k≧2)の円環状に接続されている遅延素子と、バッファ2と、で構成されている。図1においては、初段の遅延素子1aが、否定論理積ゲート(NAND回路)などのような、2つの入力端子を有する論理ゲート、その他の段の遅延素子1bが、論理否定ゲート(NOT回路)などのような、1つの入力端子を有する論理ゲートで構成されている場合を示している。なお、以下の説明において、遅延素子1aと遅延素子1bとを区別しない場合には、単に「遅延素子1」という。

【0031】

初段の遅延素子1aには、パルス信号Pinと、最終段の遅延素子1bの出力信号とが入力される。また、次段以降の各遅延素子1bには、前段の遅延素子1の出力信号が入力される。パルス信号Pinは、初段の遅延素子1aに入力されると、遅延回路102内の走行を開始する。このとき、各遅延素子1は、バッファ2を介して印加された駆動電圧の大きさに応じた伝播遅延時間で、入力されたパルス信号Pinを伝播(走行)させる。なお、各遅延素子1は、バッファ2を介して印加された駆動電圧(アナログ信号Vx)が低いほど入力信号(パルス信号Pin)を長く遅延させる特性を備えている。各遅延素子1から出力された出力信号は、遅延回路102内を走行したパルス信号Pinの走行位置として、サンプリング回路104出力される。

【0032】

A/D制御回路103は、サンプリング制御回路1031と、クロック生成回路1032と、アナログ変換回路1033と、を備えている。

【0033】

サンプリング制御回路1031は、従来のA/D変換回路400のサンプリング期間Tsに対して、第1サンプリングのサンプリング期間Ts1(以下、「第1サンプリング期間Ts1」という)が、Ts1<(1−1/n)Tsとなるように、第1サンプリングにおけるサンプリング時刻ts1(以下、「第1サンプリング時刻ts1」という)を設定する。また、サンプリング制御回路1031は、従来のA/D変換回路400のサンプリング期間Tsに対して、第2サンプリングのサンプリング期間Ts2(以下、「第2サンプリング期間Ts2」という)が、Ts2=(1/n)Tsとなるように、第2サンプリングにおけるサンプリング時刻ts2(以下、「第2サンプリング時刻ts2」という)を設定する。そして、サンプリング制御回路1031は、設定した第1サンプリング時刻ts1の数値と、第2サンプリング時刻ts2の数値とを、クロック生成回路1032に出力する。

【0034】

クロック生成回路1032は、第1サンプリングと第2サンプリングとにおけるパルス信号Pinを生成し、遅延回路102に出力する。また、クロック生成回路1032は、サンプリング制御回路1031から入力された第1サンプリング時刻ts1の数値と第2サンプリング時刻ts2の数値とに基づいて、A/D変換回路100の1回のA/D変換期間内に、2回の立ち上がりエッジを備えたサンプリングクロックCkを生成する。より具体的には、パルス信号Pinを遅延回路102に出力した後、第1サンプリング時刻ts1のときに1回目の立ち上がりエッジがあり、再度、パルス信号Pinを遅延回路102に出力した後、第2サンプリング時刻ts2のときに2回目の立ち上がりエッジがあるサンプリングクロックCkを生成する。そして、クロック生成回路1032は、生成したサンプリングクロックCkを、サンプリング回路104に出力する。

【0035】

これより、A/D変換回路100は、サンプリングクロックCkの2回の立ち上がりエッジを用いて、1回のA/D変換期間内に、第1サンプリングと第2サンプリングとの計2回のサンプリングを行う。より具体的には、サンプリングクロックCkの1回目の立ち上がりエッジで第1サンプリングを行い、サンプリングクロックCkの2回目の立ち上がりエッジで第2サンプリングを行う。

【0036】

また、クロック生成回路1032は、サンプリング制御回路1031から入力された第1サンプリング時刻ts1の数値と第2サンプリング時刻ts2の数値とに基づいて、第1サンプリングと第2サンプリングとで、遅延回路102に入力されるアナログ信号Vxを切り替えるためのアナログ切り替え信号Psを生成する。そして、クロック生成回路1032は、生成したアナログ切り替え信号Psを、アナログ変換回路1033に出力する。

【0037】

これにより、遅延回路102に入力されるアナログ信号Vxが、アナログ変換回路1033によって、第1サンプリングと第2サンプリングとで、異なるアナログ信号に切り替えられる。より具体的には、アナログ切り替え信号Psによって、遅延回路102に入力されるアナログ信号Vxが、第1サンプリングではアナログ信号Vcに、第2サンプリングではアナログ変換回路1033で生成されるアナログ信号(後述する、アナログ信号Vg)に、それぞれ切り替えられる。

【0038】

アナログ変換回路1033は、入力調整回路101から入力されたアナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。アナログ変換回路1033がアナログ信号Vcをオフセットするためのアナログオフセット信号は、デジタル生成回路105から入力された制御信号(後述する、デジタルオフセット信号Dof)に応じて切り替える。そして、アナログ変換回路1033は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または生成したアナログ信号Vgのいずれか一方のアナログ信号を、アナログ信号Vxとして遅延回路102に出力する。なお、アナログ変換回路1033におけるアナログ信号Vgの生成方法に関する詳細な説明は、後述する。

【0039】

サンプリング回路104は、ラッチ&エンコーダ回路1041と、カウンタ1042と、ラッチ回路1043と、を備えている。

【0040】

ラッチ&エンコーダ回路1041は、A/D制御回路103内のクロック生成回路1032から入力されたサンプリングクロックCkの立ち上がりエッジに同期して、遅延回路102内を走行したパルス信号Pinの走行位置を検出する。すなわち、ラッチ&エンコーダ回路1041は、第1サンプリング時刻ts1および第2サンプリング時刻ts2のときに、それぞれ、パルス信号Pinの走行位置を検出する。また、ラッチ&エンコーダ回路1041は、検出したそれぞれのパルス信号Pinの走行位置を、それぞれbビット(bは正の整数)の数値に変換(エンコード)して、デジタル生成回路105に出力する。

【0041】

カウンタ1042は、サンプリング期間内に遅延回路102を周回したパルス信号Pinの周回数を取得する。より具体的には、カウンタ1042は、第1サンプリング期間Ts1および第2サンプリング期間Ts2のそれぞれのサンプリング期間内に、遅延回路102を周回したパルス信号Pinの周回数を、それぞれ取得する。そして、カウンタ1042は、取得したそれぞれの周回数を、それぞれaビット(aは正の整数)の計数値としてラッチ回路1043に出力する。

【0042】

ラッチ回路1043は、A/D制御回路103内のクロック生成回路1032から入力されたサンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042から出力された計数値をラッチし、デジタル生成回路105に出力する。すなわち、ラッチ回路1043は、第1サンプリング時刻ts1および第2サンプリング時刻ts2のときにカウンタ1042から出力されたaビットの計数値をそれぞれラッチし、ラッチしたそれぞれのaビットの計数値を、デジタル生成回路105に出力する。

【0043】

デジタル生成回路105は、サンプリング回路104内のラッチ&エンコーダ回路1041が取得したパルス信号Pinの走行位置の値、およびサンプリング回路104内のラッチ回路1043が取得したパルス信号Pinの周回数の値を取り込む。そして、デジタル生成回路105は、取り込んだ2つの値に基づいて、サンプリング期間内にパルス信号Pinが伝播した遅延素子1の個数を算出し、算出した遅延素子1の個数を表すデジタル信号に数値化、すなわち、A/D変換する。より具体的には、デジタル生成回路105は、第1サンプリング時刻ts1のときのaビットの計数値とbビットの数値とに基づいて、第1サンプリング期間Ts1のデジタル信号Dout1に数値化し、第2サンプリング時刻ts2のときのaビットの計数値とbビットの数値とに基づいて、第2サンプリング期間Ts2のデジタル信号Dout2に数値化する。

【0044】

また、デジタル生成回路105は、デジタル信号Dout1の数値に基づいて、アナログ信号Vcを、アナログオフセット信号で調整するための制御信号であるデジタルオフセット信号Dofを生成し、生成したデジタルオフセット信号Dofを、アナログ変換回路1033に出力する。デジタルオフセット信号Dofは、デジタル信号Dout1の数値に応じて、アナログオフセット信号を選択するための制御信号である。なお、本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号Vmax/nまたはアナログオフセット信号Vmin/nのいずれか一方を選択するための制御信号が、デジタルオフセット信号Dofとして出力される。

【0045】

また、デジタル生成回路105は、デジタルオフセット信号Dofおよびデジタル信号Dout2に基づいて、従来のA/D変換回路400と同様のサンプリング期間Ts(>Ts1+Ts2)内にパルス信号Pinが伝播した遅延素子1の個数を算出し、算出した遅延素子1の個数を表すデジタル信号Doutに数値化する。

このようにして、A/D変換回路100では、入力調整回路101に入力したアナログ信号Vinを、最終的なデジタル信号Doutに変換、すなわち、A/D変換する。

【0046】

次に、本第1の実施形態のA/D変換回路100におけるA/D変換の動作手順について説明する。図2は、本第1の実施形態のA/D変換回路100における、サンプリング時刻とデジタル信号との関係、および本第1の実施形態のA/D変換回路100によるアナログ・デジタル変換動作における各信号のタイミングを示したタイミングチャートである。なお、上述した第1サンプリング期間Ts1は、サンプリング時刻t1sからt1までの期間のことを指し、第2サンプリング期間Ts2は、サンプリング時刻t2sからt2までの期間のことを指す。以下の説明においては、A/D変換回路100内の構成要素の動作を、A/D変換回路100における1回のA/D変換期間であるサンプリング期間Tsum内の各サンプリング時刻の経過に沿って説明する。

【0047】

サンプリング時刻t1s以前の期間では、クロック生成回路1032が、アナログ切り替え信号PsをHighにし、アナログ変換回路1033が、アナログ信号Vxとしてアナログ信号Vcを出力する。これにより、遅延回路102に入力されるアナログ信号Vxは、アナログ信号Vcとなる。

【0048】

サンプリング時刻t1sでは、クロック生成回路1032が、パルス信号Pinを、Highにする。これにより、パルス信号Pinが、遅延回路102内の走行を開始する。このようにして、A/D変換回路100は、1回のA/D変換における第1サンプリングを開始する。

【0049】

サンプリング時刻t1では、ラッチ&エンコーダ回路1041が、サンプリングクロックCkの立ち上がりエッジに同期して、第1サンプリングにおけるパルス信号Pinの走行位置を検出し、検出したパルス信号Pinの走行位置を、デジタル生成回路105に出力する。また、サンプリング時刻t1では、ラッチ回路1043が、サンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042が取得した第1サンプリングにおけるパルス信号Pinの周回数をラッチし、デジタル生成回路105に出力する。このようにして、A/D変換回路100は、1回のA/D変換における第1サンプリングを終了する。

【0050】

サンプリング時刻t1からt2sまでの期間(以下、「アナログ変換期間Ta」という)では、デジタル生成回路105が、ラッチ&エンコーダ回路1041から入力されたパルス信号Pinの走行位置の値、およびラッチ回路1043から入力されたパルス信号Pinの周回数の値に基づいて、デジタル信号Dout1を算出し、デジタルオフセット信号Dofを生成する。本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号のいずれか一方を選択するための、HighまたはLowの1bitのデジタルオフセット信号Dofが、デジタル信号Dout1の数値に応じて、すなわち、アナログ信号Vcの大きさに応じて生成され、アナログ変換回路1033に出力される。

【0051】

そして、アナログ変換回路1033は、デジタル生成回路105から入力された1bitのデジタルオフセット信号Dofの値(HighまたはLow)に応じて、アナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。

【0052】

また、アナログ変換期間Taでは、クロック生成回路1032が、パルス信号Pinを、Lowにする。これにより、パルス信号Pinは、遅延回路102内の走行を停止する。

【0053】

また、アナログ変換期間Taでは、クロック生成回路1032が、アナログ切り替え信号PsをLowにし、アナログ変換回路1033が、アナログ信号Vxとしてアナログ信号Vgを出力する。これにより、遅延回路102に入力されるアナログ信号Vxは、アナログ信号Vgとなる。

【0054】

サンプリング時刻t2sでは、クロック生成回路1032が、パルス信号Pinを、Highにする。これにより、パルス信号Pinが、遅延回路102内の走行を開始する。このようにして、A/D変換回路100は、1回のA/D変換における第2サンプリングを開始する。

【0055】

サンプリング時刻t2では、ラッチ&エンコーダ回路1041が、サンプリングクロックCkの立ち上がりエッジに同期して、第2サンプリングにおけるパルス信号Pinの走行位置を検出し、検出したパルス信号Pinの走行位置を、デジタル生成回路105に出力する。また、サンプリング時刻t2では、ラッチ回路1043が、サンプリングクロックCkの立ち上がりエッジに同期して、カウンタ1042が取得した第2サンプリングにおけるパルス信号Pinの周回数をラッチし、デジタル生成回路105に出力する。このようにして、A/D変換回路100は、1回のA/D変換における第2サンプリングを終了する。

【0056】

サンプリング時刻t2以降の期間では、デジタル生成回路105が、ラッチ&エンコーダ回路1041から入力されたパルス信号Pinの走行位置の値、およびラッチ回路1043から入力されたパルス信号Pinの周回数の値に基づいて、デジタル信号Dout2を算出する。また、デジタル生成回路105は、アナログ変換期間Taで生成したデジタルオフセット信号Dof、および算出したデジタル信号Dout2に基づいて、デジタル信号Doutを算出する。そして、算出したデジタル信号Doutを、従来のA/D変換回路400と同様のサンプリング期間TsでA/D変換した最終的なデジタル信号Doutとして出力する。

【0057】

また、サンプリング時刻t2以降の期間では、クロック生成回路1032が、パルス信号Pinを、Lowにする。これにより、パルス信号Pinは、遅延回路102内の走行を停止する。

【0058】

次に、アナログ信号Vgの算出方法について説明する。図3は、本第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033の概略構成を示したブロック図である。図3に示したアナログ変換回路1033は、減算回路1034と、増幅回路1035と、2つ(n個、n=2)のアナログオフセット信号Vmax/nおよびVmin/nと、スイッチ3と、スイッチ4と、を備えている。

【0059】

アナログオフセット信号Vmax/nおよびVmin/nは、アナログ信号Vcをオフセットするために、予め定められたアナログ信号である。本第1の実施形態のA/D変換回路100では、n=2であるため、2つのアナログオフセット信号Vmax/2とアナログオフセット信号Vmin/2とが、予め定められている。

【0060】

スイッチ4は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、2つのアナログオフセット信号Vmax/nまたはアナログオフセット信号Vmin/nのいずれか一方を、減算回路1034に出力する。スイッチ4の出力端子は、デジタルオフセット信号Dof=Highのとき、アナログオフセット信号Vmax/nの入力端子に接続され、デジタルオフセット信号Dof=Lowのとき、アナログオフセット信号Vmin/nの入力端子に接続される。

【0061】

減算回路1034は、入力調整回路101から入力されたアナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmax/nまたはVmin/nのいずれかを減算する。そして、アナログオフセット信号を減算したアナログ信号Vcを、増幅回路1035に出力する。より具体的には、デジタルオフセット信号Dof=Highの場合、減算回路1034は、アナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmax/nを減算し、増幅回路1035に出力する。また、デジタルオフセット信号Dof=Lowの場合、減算回路1034は、アナログ信号Vcから、スイッチ4を介して入力されたアナログオフセット信号Vmin/nを減算し、増幅回路1035に出力する。

【0062】

増幅回路1035は、減算回路1034から入力された、アナログオフセット信号Vmax/nまたはVmin/nのいずれかが減算されたアナログ信号Vcを増幅したアナログ信号Vcを生成し、アナログ信号Vgとして出力する。本第1の実施形態のA/D変換回路100では、n=2であるため、増幅回路1035は、アナログオフセット信号が減算されたアナログ信号Vcを2倍に増幅したアナログ信号Vgを生成する。このときのアナログ信号Vgは、下式(2)で表される。

【0063】

【数2】

【0064】

スイッチ3は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または増幅回路1035が増幅したアナログ信号Vgいずれか一方を、アナログ変換回路1033が出力するアナログ信号Vxとして、遅延回路102に出力する。スイッチ3の出力端子は、アナログ切り替え信号Ps=Highのとき、アナログ信号Vcの入力端子に接続され、アナログ切り替え信号Ps=Lowのとき、アナログ信号Vgの入力端子に接続される。

【0065】

第1サンプリングのとき、アナログ切り替え信号Ps=Highにより、スイッチ3の出力端子は、アナログ変換回路1033のアナログ信号Vcの入力端子に接続される。これより、アナログ信号Vxはアナログ信号Vcに等しくなり、遅延回路102に出力される。

【0066】

第2サンプリングのとき、アナログ切り替え信号Ps=Lowにより、スイッチ3の出力端子は、増幅回路1035の出力端子に接続される。これより、アナログ信号Vxはアナログ信号Vgに等しくなり、遅延回路102に出力される。

【0067】

次に、A/D変換回路100におけるアナログ信号(アナログ信号Vc,アナログ信号Vg)およびデジタル信号(デジタル信号Dout1,デジタル信号Dout2,デジタル信号Dout)の関係について説明する。図4は、本第1の実施形態のA/D変換回路100におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【0068】

図4(a)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換期間Taのときにデジタル生成回路105が算出するデジタル信号Dout1との関係を示している。また、図4(b)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換回路1033が生成するアナログ信号Vgとの関係を示している。また、図4(c)には、入力調整回路101によって調整されたアナログ信号Vcと、第2サンプリングのあとにデジタル生成回路105が算出するデジタル信号Dout2との関係を示している。また、図4(d)は、入力調整回路101によって調整されたアナログ信号Vcと、デジタル生成回路105が最終的に算出するデジタル信号Doutとの関係を示している。

【0069】

なお、図4において、アナログ信号Vcの電圧値Vmは、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/n)である。また、ΔVは、第1サンプリングのときの量子化ステップ幅である。以下の説明においては、図4(a)に示したように、第1サンプリングのときのアナログ信号Vcの電圧値Vmに対応するデジタル信号Dout1の値をDthとし、デジタル信号Dout1の値が(Dth−1)からDthに切り替わるときのアナログ信号Vcの電圧値をVm’とする。

【0070】

図4(a)に示したように、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1≧Dthとなった場合、アナログ信号Vcの電圧値は、Vc≧Vm’であると判定し、アナログ変換期間Taにおいて、Highのデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1<Dthとなった場合、アナログ信号Vcの電圧値は、Vc<Vm’であると判定し、アナログ変換期間Taにおいて、Lowのデジタルオフセット信号Dofを出力する。すなわち、デジタル生成回路105は、予め定められたデジタル信号Dout1の値Dthを閾値として、HighまたはLowの1bitのデジタルオフセット信号Dofを生成している。

【0071】

このようにしてアナログ変換期間Taでは、デジタル生成回路105が生成したデジタルオフセット信号Dofの値(HighまたはLow)によって、第1サンプリングのときに入力されたアナログ信号Vcの電圧値と、アナログ信号Vcの電圧値Vmとの大小を判定する。そして、第2サンプリングのときに遅延回路102に入力される、上式(2)で表されるアナログ信号Vgは、下式(3)で表される。

【0072】

【数3】

【0073】

図4(b)は、上式(3)におけるアナログ信号Vcとアナログ信号Vgとの関係を表している。

【0074】

ところで、電圧値がVm’≦Vc≦Vmのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(3)より、Vg=2Vc−Vmaxとなり、図4(b)に示したように、アナログ信号Vgの電圧値はVg≦Vminとなる。ここで、仮に、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合を考える。この場合に、電圧値がVm’≦Vc≦Vmのアナログ信号Vcがアナログ変換回路1033に入力されると、アナログ信号Vgの電圧値は、A/D入力範囲の最小値Vluよりも小さくなり、遅延回路102のA/D入力範囲を超えてしまうことも考えられる。以下の説明においては、アナログ信号Vgの電圧値が遅延回路102のA/D入力範囲を超えてしまう現象を、「オーバーレンジ」という。アナログ信号Vgの電圧値は、第1サンプリングのときの量子化ステップ幅であるΔVの幅が大きい、すなわち、第1サンプリング期間Ts1が短いと、よりオーバーレンジとなりやすい。このため、入力調整回路101は、アナログ変換回路1033が生成するアナログ信号Vgがオーバーレンジとならないように、上式(1)を満たすような、アナログ信号Vcの最小値Vminおよび最大値Vmaxを設定している。本第1の実施形態のA/D変換回路100では、n=2であるため、図4(b)に示したように、アナログ信号Vgの最小値Vminが、Vmin≧Vlu+2ΔVとなるような、アナログ信号Vcの最小値Vminを設定している。

【0075】

図4(c)は、アナログ信号Vcを横軸として、第2サンプリングのときのアナログ信号Vgに対応するデジタル信号Dout2を縦軸に表している。図4(c)に示したように、アナログ信号Vcの最小値Vminから電圧値Vm’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw1を、アナログ信号Vcの電圧値Vm’から最大値Vmaxまでの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw2を、それぞれ取得することができる。ここで、アナログ信号Vcの電圧値Vm’から電圧値Vmまでの電圧範囲におけるデジタル信号Dout2のデジタル信号幅をΔDwとする。このとき、アナログ信号範囲の約1/2(=1/n、n=2)となるアナログ信号Vcの最小値Vminから電圧値Vmまでの電圧範囲、またはアナログ信号Vcの電圧値Vmから最大値Vmaxまでの電圧範囲におけるデジタル信号幅Dwは、Dw=Dw1+ΔDw=Dw2−ΔDwを取得することができる。

【0076】

n=2の場合において、このデジタル信号幅Dwは、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号Vcの最小値Vminから最大値Vmaxまでの電圧範囲に対応するデジタル信号幅Dwsの1/2(=1/n、n=2)に等しくなる。すなわち、デジタル信号幅Dwは、Dw=Dws/n=Dws/2となる。

【0077】

これは、A/D変換回路100が、サンプリング期間と電圧分解能が比例する関係にあることから、n=2の場合において、第2サンプリング期間Ts2をサンプリング期間Tsの1/2(=1/n)、すなわち、Ts2=(1/n)Ts=Ts/2とする代わりに、アナログ信号範囲を2倍(n倍、n=2)に拡大する処理を行っているためである。

【0078】

図4(d)は、アナログ信号Vcを横軸として、デジタルオフセット信号Dof、およびデジタル信号Dout2に基づいて算出したデジタル信号Doutを縦軸に表している。デジタル生成回路105は、デジタルオフセット信号Dofに応じて、図4(c)に示したデジタル信号Dout2のデジタル信号幅Dw2を、デジタル信号幅Dw1の上にオフセットし、図4(d)に示したような、デジタル信号幅Dwoのデジタル信号Doutを算出する。より具体的には、デジタルオフセット信号Dofの値がHighであるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vmax/nにおけるデジタル信号幅Dw2の値を加算することによって、デジタル信号Doutを算出する。これにより、図4(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2=2Dwとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。

【0079】

このように、A/D変換回路100では、図2に示したように、第1サンプリング期間Ts1をTs1<(1−1/n)Tsと設定し、第2サンプリング期間Ts2をTs2=(1/n)Tsと設定する。また、アナログ変換期間Taは、第1サンプリング期間Ts1や第2サンプリング期間Ts2に比べて非常に短い期間とする。これにより、A/D変換回路100では、上述した3つの期間を合計した、A/D変換回路100における1回のA/D変換期間であるサンプリング期間Tsum(≒Ts1+Ts2)を、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間とすることができる。

【0080】

また、A/D変換回路100では、第1サンプリングの結果に基づいて算出したデジタル信号Dout1から、アナログ信号Vcをオフセットするためのアナログオフセット信号を選択するデジタルオフセット信号Dofを生成する。そして、生成したデジタルオフセット信号Dofと、第2サンプリングの結果に基づいて算出したデジタル信号Dout2とに基づいて、最終的なデジタル信号Doutを算出する。これにより、A/D変換回路100では、サンプリング期間Tsよりも短いサンプリング期間Tsumにおいても、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル電圧幅Dwoのデジタル信号Doutを取得することができる。

【0081】

上記に述べたとおり、本第1の実施形態のA/D変換回路100は、サンプリング期間Tsよりも短い第1サンプリング期間Ts1で第1サンプリングを行い、第1サンプリングの結果に基づいて、予め定められたn個(本第1の実施形態では、n=2)のアナログオフセット信号の中から、実際にアナログ信号Vcをオフセットするアナログオフセット信号を選択する。そして、選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、サンプリング期間Tsの1/nのサンプリング期間の第2サンプリングを行い、最終的なデジタル信号Doutを算出する。すなわち、本第1の実施形態のA/D変換回路100では、第2サンプリング期間Ts2を1/n(本第1の実施形態では、n=2)とする代わりに、アナログ信号範囲をn倍(2倍)に拡大することによって、同様の電圧分解能のデジタル信号Doutを得る。これにより、従来のA/D変換回路400におけるサンプリング期間Tsのときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短く、すなわち、A/D変換を高速化することができる。

【0082】

なお、本第1の実施形態のA/D変換回路100では、n=2とし、2つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに2倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2で第2サンプリングを行う場合について説明した。しかし、アナログオフセット信号の数、増幅する倍数、サンプリング期間Tsを短くするための除数であるnは、2以上の正の整数であればよく、本第1の実施形態で説明した値に限定されるものではない。例えば、n=3とし、3つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに3倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/3とした第2サンプリング期間Ts2の第2サンプリングを行い、最終的なデジタル信号Doutを算出する構成にすることもできる。

【0083】

なお、本第1の実施形態のA/D変換回路100では、図4(b)で説明したように、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合に、電圧値がVm’≦Vc≦Vmのアナログ信号Vcがアナログ変換回路1033に入力されると、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしてしまうということが考えられていた。そこで、A/D変換回路100では、入力調整回路101が、アナログ変換回路1033が生成するアナログ信号Vgがオーバーレンジとならないように、アナログ信号Vcの最小値Vminおよび最大値Vmaxを設定していた。しかし、アナログ信号Vgの電圧値がオーバーレンジとならないようにする方法は、本第1の実施形態で説明した方法に限定されるものではない。

【0084】

<第2の実施形態>

次に、本発明の第2の実施形態について説明する。本第2の実施形態では、第1の実施形態とは異なる方法で、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしないようにする。なお、本第2の実施形態におけるA/D変換回路の構成は、第1の実施形態のA/D変換回路100に備えたA/D制御回路103内のアナログ変換回路1033が異なる構成となっているのみであり、その他の構成要素は、第1の実施形態のA/D変換回路100と同様の構成である。より具体的には、図1に示した第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033に代わって、後述するアナログ変換回路2033を備えているのみである。従って、本第2の実施形態のA/D変換回路の説明においては、第1の実施形態のA/D変換回路100とは異なる構成、および動作のみを説明して、詳細な説明は省略する。なお、以下の説明においては、本第2の実施形態のA/D変換回路の構成要素において、図1に示した第1の実施形態のA/D変換回路100と同様の構成要素は、同一の符号を用いて説明する。例えば、本第2の実施形態のA/D変換回路も、A/D変換回路100として説明する。

【0085】

本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、1回のA/D変換期間内に、2回のサンプリングを行う。ただし、本第2の実施形態のA/D変換回路100では、アナログオフセット信号の数が、第1の実施形態のA/D変換回路100と異なる。なお、本第2の実施形態では、増幅する倍数およびサンプリング期間Tsを短くするための除数であるn(n:正の整数、n≧2)の数値がn=2、アナログオフセット信号の数であるm(m:正の整数、m≧2n−1)の数値がm=3、である場合について説明する。

【0086】

本第2の実施形態のA/D変換回路100に備えた入力調整回路101は、第1の実施形態のA/D変換回路100に備えた入力調整回路101と同様に、入力されたアナログ信号Vinの電圧の範囲を、アナログ信号Vinのダイナミックレンジが、最小値Vminから最大値Vmaxまでのアナログ信号範囲となるように調整した、アナログ信号Vcを出力する。ここで、アナログ信号範囲は、第1の実施形態のA/D変換回路100に備えた入力調整回路101と同様に、最小値Vluから最大値Vloまでの遅延回路102のA/D入力範囲よりも小さい(狭い)範囲である。ただし、本第2の実施形態のA/D変換回路100に備えた入力調整回路101では、アナログ信号範囲の最大値Vmaxおよび最小値Vminと、A/D入力範囲の最大値Vloおよび最小値Vluとは、下式(4)の関係にある。

【0087】

【数4】

【0088】

A/D制御回路103は、サンプリング制御回路1031と、クロック生成回路1032と、アナログ変換回路2033と、を備えている。上述したように、本第2の実施形態のA/D変換回路100では、第1の実施形態のA/D変換回路100に備えたアナログ変換回路1033が、アナログ変換回路2033に代わっている。サンプリング制御回路1031およびクロック生成回路1032は、第1の実施形態のA/D変換回路100に備えたサンプリング制御回路1031およびクロック生成回路1032と同様であるため、詳細な説明は省略する。

【0089】

アナログ変換回路2033は、第1の実施形態のアナログ変換回路1033と同様に、入力調整回路101から入力されたアナログ信号Vcを、アナログオフセット信号でオフセットしたアナログ信号Vgを生成する。アナログ変換回路2033は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、アナログオフセット信号を切り替える。そして、アナログ変換回路2033は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または生成したアナログ信号Vgのいずれか一方のアナログ信号を、アナログ信号Vxとして遅延回路102に出力する。

【0090】

デジタル生成回路105は、デジタル信号Dout1の数値に基づいて、アナログ信号Vcを、アナログオフセット信号で調整するための制御信号であるデジタルオフセット信号Dofを生成し、生成したデジタルオフセット信号Dofを、アナログ変換回路2033に出力する。なお、本第2の実施形態のA/D変換回路100では、m=3であるため、3つのアナログオフセット信号から1つのアナログオフセット信号を選択するためのデジタルオフセット信号Dofを、アナログ変換回路2033に出力する。

【0091】

本第2の実施形態のA/D変換回路100におけるA/D変換の動作手順は、図2に示した第1の実施形態のA/D変換回路100における動作手順(タイミングチャート)と同様であるため、詳細な説明は省略する。

【0092】

次に、アナログ信号Vgの算出方法について説明する。図5は、本第2の実施形態のA/D変換回路100に備えたアナログ変換回路2033の概略構成を示したブロック図である。図5に示したアナログ変換回路2033は、減算回路2034と、増幅回路2035と、3値(m=3)のアナログオフセット信号Vmax/n、Vm/n、およびVmin/nと、スイッチ5と、スイッチ6と、を備えている。

【0093】

アナログオフセット信号Vmax/n、Vm/n、およびVmin/nは、アナログ信号Vcをオフセットするために、予め定められたアナログ信号である。本第2の実施形態のA/D変換回路100では、m=3であるため、3つのアナログオフセット信号Vmax/nと、アナログオフセット信号Vm/nと、アナログオフセット信号Vmin/nとが、予め定められている。ここで、アナログオフセット信号VmaxおよびVminの電圧値は、それぞれアナログ信号範囲の最大値Vmaxおよび最小値Vminである。また、アナログオフセット信号Vmの電圧値は、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/2)である。

【0094】

スイッチ6は、デジタル生成回路105から入力されたデジタルオフセット信号Dofに応じて、3つのアナログオフセット信号Vmax/n、Vm/n、およびVmin/nの中から、1つのアナログオフセット信号を、減算回路2034に出力する。ここで、デジタル生成回路105から入力されるデジタルオフセット信号Dofは、“0”、“1”、“2”のいずれかの数値を示すことによって、3つのアナログオフセット信号Vmax/n、Vm/n、またはVmin/nの中から、いずれか1つを選択するための制御信号である。スイッチ6の出力端子は、デジタルオフセット信号Dof=2のとき、アナログオフセット信号Vmax/nの入力端子に接続され、デジタルオフセット信号Dof=1のとき、アナログオフセット信号Vm/nの入力端子に接続され、デジタルオフセット信号Dof=0のとき、アナログオフセット信号Vmin/nの入力端子に接続される。

【0095】

減算回路2034は、入力調整回路101から入力されたアナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmax/n、Vm/n、またはVmin/nの中のいずれかを減算する。そして、アナログオフセット信号を減算したアナログ信号Vcを、増幅回路2035に出力する。より具体的には、デジタルオフセット信号Dof=2の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmax/nを減算し、増幅回路2035に出力する。また、デジタルオフセット信号Dof=1の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vm/nを減算し、増幅回路2035に出力する。また、デジタルオフセット信号Dof=0の場合、減算回路2034は、アナログ信号Vcから、スイッチ6を介して入力されたアナログオフセット信号Vmin/nを減算し、増幅回路2035に出力する。

【0096】

増幅回路2035は、減算回路2034から入力された、アナログオフセット信号Vmax/n、Vm/n、またはVmin/nのいずれかが減算されたアナログ信号Vcを増幅したアナログ信号Vcを生成し、アナログ信号Vgとして出力する。本第2の実施形態のA/D変換回路100では、n=2であるため、増幅回路2035は、アナログオフセット信号が減算されたアナログ信号Vcを2倍に増幅したアナログ信号Vgを生成する。このときのアナログ信号Vgは、下式(5)で表される。

【0097】

【数5】

【0098】

スイッチ5は、クロック生成回路1032から入力されたアナログ切り替え信号Psに応じて、入力調整回路101から入力されたアナログ信号Vc、または増幅回路2035が増幅したアナログ信号Vgいずれか一方を、アナログ変換回路2033が出力するアナログ信号Vxとして、遅延回路102に出力する。スイッチ5の出力端子は、アナログ切り替え信号Ps=Highのとき、アナログ信号Vcの入力端子に接続され、アナログ切り替え信号Ps=Lowのとき、アナログ信号Vgの入力端子に接続される。

【0099】

第1サンプリングのとき、アナログ切り替え信号Ps=Highにより、スイッチ5の出力端子は、アナログ変換回路2033のアナログ信号Vcの入力端子に接続される。これより、アナログ信号Vxはアナログ信号Vcに等しくなり、遅延回路102に出力される。

【0100】

第2サンプリングのとき、アナログ切り替え信号Ps=Lowにより、スイッチ5の出力端子は、増幅回路2035の出力端子に接続される。これより、アナログ信号Vxはアナログ信号Vgに等しくなり、遅延回路102に出力される。

【0101】

次に、本第2の実施形態のA/D変換回路100におけるアナログ信号(アナログ信号Vc,アナログ信号Vg)およびデジタル信号(デジタル信号Dout1,デジタル信号Dout2,デジタル信号Dout)の関係について説明する。図6は、本第2の実施形態のA/D変換回路100におけるアナログ信号とデジタル信号とのそれぞれの関係を示した図である。

【0102】

図6(a)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換期間Taのときにデジタル生成回路105が算出するデジタル信号Dout1との関係を示している。また、図6(b)には、入力調整回路101によって調整されたアナログ信号Vcと、アナログ変換回路2033が生成するアナログ信号Vgとの関係を示している。また、図6(c)には、入力調整回路101によって調整されたアナログ信号Vcと、第2サンプリングのあとにデジタル生成回路105が算出するデジタル信号Dout2との関係を示している。また、図6(d)は、入力調整回路101によって調整されたアナログ信号Vcと、デジタル生成回路105が最終的に算出するデジタル信号Doutとの関係を示している。

【0103】

なお、図6において、アナログ信号Vcの電圧値Vmは、最小値Vminから最大値Vmaxまでのアナログ信号範囲の中間の電圧値(=(Vmax+Vmin)/n)である。また、ΔVは、第1サンプリングのときの量子化ステップ幅である。以下の説明においては、図6(a)に示したように、第1サンプリングのときのアナログ信号Vcの電圧値Vmよりも少し大きいアナログ信号Vcの電圧値Vmoに対応するデジタル信号Dout1の値をDthoとし、デジタル信号Dout1の値が(Dtho−1)からDthoに切り替わるときのアナログ信号Vcの電圧値をVmo’とする。また、アナログ信号Vcの電圧値Vmよりも少し小さいアナログ信号Vcの電圧値Vmuに対応するデジタル信号Dout1の値をDthuとし、デジタル信号Dout1の値が(Dthu−1)からDthuに切り替わるときのアナログ信号Vcの電圧値をVmu’とする。

【0104】

図6(a)に示したように、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1≧Dthoとなった場合、アナログ信号Vcの電圧値は、Vc≧Vmo’であると判定し、アナログ変換期間Taにおいて、“2”のデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDthu≦Dout1<Dthoとなった場合、アナログ信号Vcの電圧値は、Vmu’≦Vc<Vmo’であると判定し、アナログ変換期間Taにおいて、“1”のデジタルオフセット信号Dofを出力する。また、デジタル生成回路105は、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値がDout1<Dthuとなった場合、アナログ信号Vcの電圧値は、Vc<Vmu’であると判定し、アナログ変換期間Taにおいて、“0”のデジタルオフセット信号Dofを出力する。すなわち、デジタル生成回路105は、予め定められたデジタル信号Dout1の値DthoおよびDthuを閾値として、“0”、“1”、“2”のいずれかの数値を示す2bitのデジタルオフセット信号Dofを生成している。

【0105】

このようにしてアナログ変換期間Taでは、デジタル生成回路105が生成したデジタルオフセット信号Dofの値(“0”、“1”、“2”のいずれかの数値)によって、第1サンプリングのときに入力されたアナログ信号Vcの電圧値と、アナログ信号Vcの電圧値とを比較する。そして、第2サンプリングのときに遅延回路102に入力される、上式(5)で表されるアナログ信号Vgは、下式(6)で表される。

【0106】

【数6】

【0107】

図6(b)は、上式(6)におけるアナログ信号Vcとアナログ信号Vgとの関係を表している。

【0108】

ところで、電圧値がVmo’≦Vc≦Vmoのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(6)より、Vg=2Vc−Vmaxとなり、図6(b)に示したように、アナログ信号Vgの電圧値はVg>Vminである。また、電圧値がVmu’≦Vc≦Vmuのアナログ信号Vcが遅延回路102に入力されたとき、アナログ信号Vgは、上式(6)より、Vg=2Vc−Vmとなり、また、図6(b)に示したように、アナログ信号Vgの電圧値はVg>Vminである。従って、本第2の実施形態のA/D変換回路100では、仮に、アナログ信号Vcの最小値Vminを、A/D入力範囲(最小値Vluから最大値Vloまで)における最小値Vluに設定した場合でも、アナログ信号Vgの電圧値は、A/D入力範囲をオーバーレンジしない。

【0109】

すなわち、本第2の実施形態のA/D変換回路100では、アナログ信号Vcの2つ((m−1)個、m=3)の電圧値VmoおよびVmuに対応するデジタル信号Dout1の値DthoおよびDthuを設け、第1サンプリングの結果に基づいて算出したデジタル信号Dout1の値に応じて、デジタルオフセット信号Dofの出力値を決定する。これにより、第1の実施形態のA/D変換回路100では、上式(1)に示したように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要があったが、本第2の実施形態のA/D変換回路100では、上式(4)に示したように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要がなく、アナログ信号Vgのオーバーレンジを回避することができる。

【0110】

このため、本第2の実施形態のA/D変換回路100では、入力調整回路101によるアナログ信号Vinの電圧の範囲の調整は、アナログ信号Vcがアナログ信号範囲となるように調整するのみとなる。このとき、例えば、アナログ信号Vinのダイナミックレンジが、遅延回路102のA/D入力範囲を必ず超えることがないのであれば、本第2の実施形態のA/D変換回路100に入力調整回路101を備えない構成とすることも可能となる。

【0111】

図6(c)は、アナログ信号Vcを横軸として、第2サンプリングのときのアナログ信号Vgに対応するデジタル信号Dout2を縦軸に表している。図6(c)に示したように、アナログ信号Vcの最小値Vminから電圧値Vmu’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw1を、アナログ信号Vcの電圧値Vmu’から電圧値Vmo’までの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw2を、アナログ信号Vcの電圧値Vmo’から最大値Vmaxまでの電圧範囲において、デジタル信号Dout2のデジタル信号幅Dw3を、それぞれ取得することができる。

【0112】

ここで、n=2の場合において、デジタル信号幅Dw1とDw2とDw3との合計値(Dw1+Dw2+Dw3)を、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル信号幅Dwsに等しくする、すなわち、Dws=Dw1+Dw2+Dw3=Dwoとするためには、アナログ信号Vcの電圧値VmoとVmuとを、例えば、下式(7)のように設定する。

【0113】

【数7】

【0114】

図6(d)は、アナログ信号Vcを横軸として、デジタルオフセット信号Dof、およびデジタル信号Dout2に基づいて算出したデジタル信号Doutを縦軸に表している。デジタル生成回路105は、デジタルオフセット信号Dofに応じて、図6(c)に示したデジタル信号Dout2のデジタル信号幅Dw1の上にデジタル信号幅Dw2をオフセットし、さらに上に、デジタル信号幅Dw3をオフセットし、図6(d)に示したような、デジタル信号幅Dwoのデジタル信号Doutを算出する。より具体的には、デジタルオフセット信号Dofの値が“1”であるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vm/nにおけるデジタル信号幅Dw2の値を加算することによって、デジタル信号Doutを算出する。また、デジタルオフセット信号Dofの値が“2”であるときには、デジタル信号Dout2の値に、予め求めることができるアナログオフセット信号Vmax/nにおけるデジタル信号幅Dw2とデジタル信号幅Dw3との合計値(Dw2+Dw3)を加算することによって、デジタル信号Doutを算出する。これにより、図6(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2+Dw3=Dwoとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。これにより、図6(d)に示したように、アナログ信号範囲で取得できるデジタル信号Doutのデジタル電圧幅Dwoは、Dwo=Dw1+Dw2=2Dwとなり、従来のA/D変換回路400におけるデジタル信号幅Dwsに等しくなる。

【0115】

このように、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、1回のA/D変換期間であるサンプリング期間Tsum(≒Ts1+Ts2)を、従来のA/D変換回路400におけるサンプリング期間Tsよりも短い期間とすることができる。また、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、サンプリング期間Tsよりも短いサンプリング期間Tsumにおいても、従来のA/D変換回路400におけるサンプリング期間Tsのときのアナログ信号範囲に対応するデジタル電圧幅Dwoのデジタル信号Doutを取得することができる。

【0116】

また、本第2の実施形態のA/D変換回路100では、アナログ信号Vcの2つ((m−1)個、m=3)の電圧値VmoおよびVmuに対応するデジタル信号Dout1の値DthoおよびDthuを設け、第1サンプリングの結果に基づいて算出したデジタル信号Dout1から、アナログ信号Vcをオフセットするためのアナログオフセット信号を選択するデジタルオフセット信号Dofを生成する。これにより、第1の実施形態のA/D変換回路100のように、アナログ信号範囲をA/D入力範囲よりもnΔV以上の電圧範囲だけ狭める必要がなく、アナログ信号Vgの電圧値がA/D入力範囲をオーバーレンジしてしまうことを、回避することができる。

【0117】

上記に述べたとおり、本第2の実施形態のA/D変換回路100は、サンプリング期間Tsよりも短い第1サンプリング期間Ts1で第1サンプリングを行い、第1サンプリングの結果に基づいて、予め定められたm個(本第2の実施形態では、m=3)のアナログオフセット信号の中から、実際にアナログ信号Vcをオフセットするアナログオフセット信号を選択する。これにより、アナログ信号範囲をA/D入力範囲よりも狭める必要なく、アナログ信号Vgの電圧値がA/D入力範囲からオーバーレンジしてしまうことを、回避する。そして、選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、サンプリング期間Tsの1/nのサンプリング期間の第2サンプリングを行い、最終的なデジタル信号Doutを算出する。すなわち、本第2の実施形態のA/D変換回路100でも、第2サンプリング期間Ts2を1/n(本第2の実施形態では、n=2)とする代わりに、アナログ信号範囲をn倍(2倍)に拡大することによって、同様の電圧分解能のデジタル信号Doutを得る。これにより、アナログ信号範囲を狭めることなく、従来のA/D変換回路400におけるサンプリング期間Tsのときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短く、すなわち、A/D変換を高速化することができる。

【0118】

なお、本第2の実施形態のA/D変換回路100では、m=3とし、3つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに、n=2とし、2倍に増幅したアナログ信号Vc、すなわち、アナログ信号Vgで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2で第2サンプリングを行う場合について説明した。しかし、アナログオフセット信号の数であるmは、3以上の正の整数であればよく、本第2の実施形態で説明した値に限定されるものではない。例えば、n=2,m=4とし、4つのアナログオフセット信号の中から選択したアナログオフセット信号でオフセットし、さらに2倍に増幅したアナログ信号Vcで、従来のサンプリング期間Tsの1/2とした第2サンプリング期間Ts2の第2サンプリングを行い、最終的なデジタル信号Doutを算出する構成にすることもできる。また、本第2の実施形態のA/D変換回路100でも、第1の実施形態のA/D変換回路100と同様に、増幅する倍数およびサンプリング期間Tsを短くするための除数であるnは、2以上の正の整数であればよく、本第2の実施形態で説明した値に限定されるものではない。

【0119】

<第3の実施形態>

以下、本発明の第3の実施形態について説明する。図7は、本発明のA/D変換回路を列毎に複数搭載したカラムA/D変換回路方式の固体撮像装置の概略構成を示したブロック図である。図7に示した固体撮像装置300は、画素部301と、垂直走査回路302と、水平走査回路303と、信号処理回路304と、カラムA/D変換回路305と、制御回路306と、を備えている。なお、図7においては、図1に示した本発明の第1、または第2の実施形態のA/D変換回路100を、固体撮像装置300に備えた場合の一例を示している。

【0120】

固体撮像装置300は、画素部301の各画素7が発生した光電変換信号に対して信号処理回路304によって各種の信号処理を行い、その後、カラムA/D変換回路305によってA/D変換してデジタル信号Doutとして出力する。

【0121】

制御回路306は、垂直走査回路302と、水平走査回路303と、信号処理回路304と、カラムA/D変換回路305と、を駆動させるための制御信号を出力する。

【0122】

垂直走査回路302は、制御回路306から出力された制御信号に応じて、画素部301内の画素7を画素部301の行単位で選択し、選択した行の各画素7から生成された光電変換信号を信号処理回路304に出力させる。

【0123】

画素部301は、複数の画素7を行方向および列方向の二次元的に配置した画素アレイである。各画素7は、フォトダイオードを備え、一定の蓄積時間内に入射した光量に応じた光電変換信号を発生し、垂直走査回路302からの選択に応じて、生成した光電変換信号を信号処理回路304に出力する。

【0124】

信号処理回路304は、制御回路306から入力された制御信号に応じて、画素部301から入力された光電変換信号からリセット雑音と1/f雑音とを除去した後、信号を増幅する。信号処理回路304は、増幅した信号をアナログ信号VinとしてカラムA/D変換回路305に出力する。

【0125】

カラムA/D変換回路305は、同じ構成のA/D変換回路100を、画素部301の列の数だけ複数備えている。ただし、カラムA/D変換回路305内に備えたA/D変換回路100は、A/D制御回路103内のクロック生成回路1032、およびサンプリング制御回路1031をそれぞれ備える構成ではなく、全てのA/D変換回路100に共通のクロック生成回路1032、およびサンプリング制御回路1031を1つのみ備えている。図7では、カラムA/D変換回路305内に備えた全てのA/D変換回路100に共通のクロック生成回路1032とサンプリング制御回路1031とをまとめて、タイミング生成回路110として表している。各列に備えたA/D変換回路100のそれぞれは、制御回路306から入力された制御信号に応じて、信号処理回路304から入力されたアナログ信号Vinを、A/D変換したデジタル信号Doutを出力する。

【0126】

水平走査回路303は、制御回路306から入力された制御信号に応じて、カラムA/D変換回路305の各A/D変換回路100によってA/D変換されたデジタル信号Doutを、画素部301の列単位で選択する。水平走査回路303が選択された列のデジタル信号Doutが、固体撮像装置300の出力として順次出力される。

【0127】

上記に述べたように、本第3の実施形態の固体撮像装置300では、画素部301の各画素7が生成した光電変換信号に対して信号処理回路304によって各種の信号処理を行って、アナログ信号Vinを取得する。その後、カラムA/D変換回路305によってアナログ信号VinをA/D変換したデジタル信号Doutを出力する。このとき、カラムA/D変換回路305内の各A/D変換回路100は、従来のA/D変換回路400におけるサンプリング期間Tsよりも短いサンプリング期間Tsumで、従来のA/D変換回路400がサンプリング期間TsでA/D変換したときと同等の電圧分解能のデジタル信号Doutを出力することができる。

【0128】

このことにより、本第3の実施形態の固体撮像装置300内のカラムA/D変換回路305は、図8に示した従来のA/D変換回路400を画素部の各列に備えた、図示しない従来のカラムA/D変換回路がサンプリング期間TsでA/D変換したときの電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短くし、高速化することができる。

【0129】

また、本第3の実施形態の固体撮像装置300では、カラムA/D変換回路305内の各A/D変換回路として、図1に示した本発明の第1、または第2の実施形態のA/D変換回路100を備えている。しかし、固体撮像装置300に備えたカラムA/D変換回路305内には、上記に述べたように、全てのA/D変換回路100に共通のタイミング生成回路110(クロック生成回路1032およびサンプリング制御回路1031)を1つのみ備えている。このため、本第3の実施形態の固体撮像装置300では、クロック生成回路1032およびサンプリング制御回路1031を備えたA/D変換回路100を、画素部301の列毎に備える場合よりも、固体撮像装置300に備えるカラムA/D変換回路305の回路規模を削減することができる。この回路規模の削減は、固体撮像装置300のように、狭小な領域内にA/D変換回路を搭載するような場合において有効であり、固体撮像装置300は、回路規模が削減された状態で、従来の固体撮像装置と同等の電圧分解能のデジタル信号Doutを、高速に出力することができる。

【0130】

なお、本第3の実施形態の固体撮像装置300においては、カラムA/D変換回路305内に、同じ構成のA/D変換回路100を、画素部301の列の数だけ複数備える場合について説明したが、画素部301の複数の列毎に1つのA/D変換回路100を複数備える構成とすることもできる。すなわち、A/D変換回路100を画素部301の複数の列で共有する構成とすることもできる。このような構成であっても、同様に、A/D変換回路100の高速化の効果を得ることができる。

【0131】

また、本第3の実施形態の固体撮像装置300においては、カラムA/D変換回路305内に、全てのA/D変換回路100に共通のタイミング生成回路110(クロック生成回路1032およびサンプリング制御回路1031)を1つのみ備える場合について説明したが、共通のタイミング生成回路110を、例えば、制御回路306や、水平走査回路303の中に備える構成とすることもできる。また、共通のタイミング生成回路110を、固体撮像装置300の外部の制御装置に備える構成とすることもできる。これにより、固体撮像装置300の回路規模を削減することができる。

【0132】

上記に述べたとおり、本発明を実施するための形態によれば、従来のA/D変換回路におけるサンプリング期間Tsに対して、Ts1<(1−1/n)Tsである第1サンプリング期間Ts1と、Ts2=(1/n)Tsである第2サンプリング期間Ts2とを設定する。また、第1サンプリング期間Ts1や第2サンプリング期間Ts2に比べて非常に短いアナログ変換期間Taを設ける。そして、第1サンプリング期間Ts1で第1サンプリングを行い、アナログ変換期間Taの期間で、第1サンプリングの結果に基づいて、予め定められたn個のアナログオフセット信号の中から、入力されたアナログ信号を実際にオフセットするアナログオフセット信号を選択する。その後、入力されたアナログ信号を選択したアナログオフセット信号でオフセットし、n倍に増幅したアナログ信号で、第2サンプリング期間Ts2の第2サンプリングを行う。そして、アナログオフセット信号を選択するための制御信号の値と第1サンプリングの結果とに基づいて、最終的なデジタル信号を算出する。従来のA/D変換回路が出力するデジタル信号の電圧分解能と同等の電圧分解能を確保した上で、サンプリング期間を短くすることによるA/D変換の高速化を実現することができる。

【0133】

また、本発明を実施するための形態によれば、A/D変換回路を固体撮像装置内に搭載した場合に、従来の固体撮像装置が出力するデジタル信号の電圧分解能と同等の電圧分解能を確保した上で、A/D変換回路のサンプリング期間を短くすることによる固体撮像装置の高速化を実現することができる。これにより、従来の固体撮像装置に対して、デジタル信号の電圧分解能を犠牲にすることなく、高速な固体撮像装置を提供することができる。

【0134】

なお、本実施形態においては、例えば、アナログ変換回路1033およびアナログ変換回路2033において、入力されたアナログ信号Vcからアナログ信号Vgを生成する際に、アナログ信号Vcからアナログオフセット信号を減算した後に増幅する場合について説明した。しかし、アナログ信号Vgを生成する際の処理は、本発明を実施するための形態に限定されるものではない。例えば、入力されたアナログ信号Vcを最初に増幅し、増幅されたアナログ信号Vcからアナログオフセット信号を減算してアナログ信号Vgを生成する構成、つまり、アナログ変換回路1033においては、減算回路1034と増幅回路1035とが逆の配置になっている構成とすることもできる。

【0135】

また、本実施形態においては、例えば、アナログ変換回路1033およびアナログ変換回路2033において、デジタルオフセット信号Dofの値毎に1つアナログオフセット信号を備えている場合の例について説明した。しかし、アナログオフセット信号の電圧値は、図示した実際にアナログ信号Vcをオフセットするアナログオフセット信号の電圧値を実現することができればよく、アナログオフセット信号の構成は、本発明を実施するための形態に限定されるものではない。例えば、複数の電圧値のオフセット信号をアナログ変換回路1033内に備え、デジタルオフセット信号Dofの値に応じて選択されるアナログオフセット信号の電圧値を、複数のオフセット信号の電圧値の組み合わせで実現する構成とすることもできる。より具体的には、例えば、電圧値が1Vのアナログオフセット信号を選択する場合、電圧値が0.3Vのオフセット信号と、電圧値が0.7Vのオフセット信号とを組み合わせて、電圧値が1Vのアナログオフセット信号を実現することもできる。

【0136】

また、本実施形態においては、遅延素子1としてNAND回路およびNOT回路を使用した場合の例について説明したが、遅延素子1として使用する回路は、本発明を実施するための形態に限定されるものではない。例えば、遅延素子1として、NOR回路(否定論理和ゲート)、差動回路など、様々な構成の遅延素子であってもよい。

【0137】

以上、本発明の実施形態について、図面を参照して説明してきたが、具体的な構成はこの実施形態に限定されるものではなく、本発明の趣旨を逸脱しない範囲においての種々の変更も含まれる。

【符号の説明】

【0138】

100・・・A/D変換回路(A/D変換装置)

101・・・入力調整回路

102・・・遅延回路

1,1a,1b・・・遅延素子

2・・・バッファ

103・・・A/D制御回路

1031・・・サンプリング制御回路(A/D制御回路,タイミング生成回路)

1032・・・クロック生成回路(A/D制御回路,タイミング生成回路)

110・・・タイミング生成回路

1033,2033・・・アナログ変換回路(A/D制御回路,アナログ変換回路)

1034,2034・・・減算回路(A/D制御回路)

1035,2035・・・増幅回路(A/D制御回路)

Vmax/n,Vm/n,Vmin/n・・・アナログオフセット信号

3,5・・・スイッチ(A/D制御回路)

4,6・・・スイッチ(A/D制御回路)

104・・・サンプリング回路

1041・・・ラッチ&エンコーダ回路

1042・・・カウンタ

1043・・・ラッチ回路

105・・・デジタル生成回路

300・・・固体撮像装置

301・・・画素部

7・・・画素

302・・・垂直走査回路

303・・・水平走査回路

304・・・信号処理回路

305・・・カラムA/D変換回路(A/D変換装置)

306・・・制御回路

400・・・A/D変換回路(A/D変換装置)

401・・・遅延回路

402・・・クロック生成回路

403・・・パルス位置数値化回路

4031・・・ラッチ&エンコーダ回路

4032・・・カウンタ

4033・・・ラッチ回路

4034・・・減算回路

【特許請求の範囲】

【請求項1】

入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、

入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、

所定のアナログ・デジタル変換期間をTsとしたとき、(1−1/n)Ts(n:正の整数、n≧2)より短い期間の第1のサンプリング期間と、(1/n)Tsの期間の第2のサンプリング期間とを設定し、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第1のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第1のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第1のサンプリングを行わせ、該アナログ信号をn倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力すると共に、前記第2のサンプリング期間を開始するときに前記パルス信号を前記遅延回路に出力し、該第2のサンプリング期間が終了するときに前記サンプリングタイミング信号を前記サンプリング回路に出力して第2のサンプリングを行わせる、A/D制御回路と、

前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、前記所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、

を備えることを特徴とするA/D変換装置。

【請求項2】

前記A/D入力信号の電圧範囲が、前記遅延回路に入力することができる電圧の範囲である入力電圧範囲よりも小さい所定の電圧範囲となるように、前記A/D制御回路に入力する前記アナログ信号の電圧範囲を調整する入力調整回路、

をさらに備え、

前記A/D制御回路は、

前記所定の電圧範囲に基づいて、それぞれの前記アナログオフセット信号を設定する、

ことを特徴とする請求項1に記載のA/D変換装置。

【請求項3】

前記入力調整回路は、

前記入力電圧範囲の最大の電圧値から前記第1のデジタル信号の1ビットに対応する電圧値を減算した電圧値を、前記所定の電圧範囲における最大の電圧値として設定する、

ことを特徴とする請求項2に記載のA/D変換装置。

【請求項4】

前記入力調整回路は、

前記入力電圧範囲の最小の電圧値に前記第1のデジタル信号の1ビットに対応する電圧値を加算した電圧値を、前記所定の電圧範囲における最小の電圧値として設定する、

ことを特徴とする請求項3に記載のA/D変換装置。

【請求項5】

前記A/D制御回路は、

前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいて、前記デジタルオフセット信号に対応したn個の前記アナログオフセット信号を設定し、

前記デジタルオフセット信号に応じて、n個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、

ことを特徴とする請求項4に記載のA/D変換装置。

【請求項6】

前記A/D制御回路は、

前記デジタルオフセット信号に対応したm(m:正の整数、m≧2n−1)個の前記アナログオフセット信号を設定し、

該設定される1個目およびm個目の前記アナログオフセット信号は、前記所定の電圧範囲の最小の電圧値および最大の電圧値に基づいた電圧値に設定され、

前記デジタルオフセット信号に応じて、m個の前記アナログオフセット信号の中から1つのアナログオフセット信号を選択する、

ことを特徴とする請求項2に記載のA/D変換装置。

【請求項7】

入射された光量に応じた光電変換信号を出力する複数の画素が2次元の行列状に配置された画素部と、

入力されたA/D入力信号の大きさに応じて、入力されたパルス信号を遅延させて伝播するk(k:正の整数、k≧2)個の遅延素子が円環状に接続された遅延回路と、入力されたサンプリングタイミング信号に応じて、前記遅延回路内のそれぞれの前記遅延素子の出力信号をサンプリングし、該サンプリングしたそれぞれの前記遅延素子の出力信号の値を、サンプリング結果として出力するサンプリング回路と、第1のサンプリングのときに、入力されたアナログ信号を、前記A/D入力信号として前記遅延回路に出力し、第2のサンプリングのときに、該アナログ信号をn(n:正の整数、n≧2)倍に増幅し、さらに、複数設定されたアナログオフセット信号の中から、入力されたデジタルオフセット信号に応じて選択されたアナログオフセット信号を加えた増幅アナログ信号を、前記A/D入力信号として前記遅延回路に出力するアナログ変換回路と、前記第1のサンプリングにおける前記サンプリング結果に基づいて、前記アナログ信号の大きさに応じた第1のデジタル信号と、該第1のデジタル信号に基づいた前記デジタルオフセット信号とを生成し、前記第2のサンプリングにおける前記サンプリング結果に基づいて、前記増幅アナログ信号の大きさに応じた第2のデジタル信号を生成し、該デジタルオフセット信号と、該第2のデジタル信号とに基づいて、所定のアナログ・デジタル変換期間Tsに対応した第3のデジタル信号を生成し、生成した該第3のデジタル信号を、前記アナログ信号の大きさに応じたデジタル信号として出力するデジタル生成回路と、を具備したA/D変換装置を、前記画素部の各列に対応したA/D変換回路として複数配置したカラムA/D変換回路と、