日東電工株式会社により出願された特許

11 - 20 / 5,557

SPRセンサセルおよびSPRセンサ

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

粘着シート剥離方法および両面粘着シート

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

粘着テープ又はシート

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

電気・電子機器類の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

透明導電性フィルム用粘着剤層、粘着剤層付き透明導電性フィルム、透明導電性積層体、およびタッチパネル

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

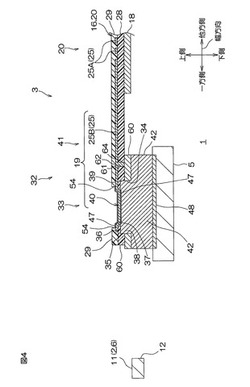

配線回路基板

【課題】電子素子と導体層との電気的な接続信頼性を向上させることのできる配線回路基板を提供すること。

【解決手段】回路付サスペンション基板3は、互いに間隔を隔てて配置され、厚み方向を貫通する第1ベース上開口部37および第2ベース開口部61が形成されるベース絶縁層28と、厚み方向に投影したときに、第1ベース上開口部37に重なる圧電側端子40、および、一端部62が第2ベース開口部61に重なり、圧電側端子40に連続する電源配線25Bを備え、ベース絶縁層28の上に形成される導体層19と、ベース絶縁層28の下に形成され、厚み方向に投影したときに、第2ベース開口部61と重なる第1ベース上開口部37の周りに配置され、圧電素子5を支持するための金属台座部60と、第2ベース開口部61内に充填され、電源配線25Bと金属台座部60とを導通させる導通部64とを備える。

(もっと読む)

タッチパネルセンサ

【課題】干渉ムラの低減することが可能なタッチパネルセンサを提供する。

【解決手段】本発明に係るタッチパネルセンサは、フィルム基材と、前記フィルム基材の第1の面に形成される第1透明電極パターンと、この第1透明電極パターンを覆うようにフィルム基材の第1の面上に積層される第1接着剤層と、フィルム基材の第2の面に形成される第2透明電極パターンと、第2透明電極パターンを覆うようにフィルム基材の第2の面上に積層される第2接着剤層と、を備え、フィルム基材は、可視光領域の波長λに対して、λ/4の面内位相差を有する。

(もっと読む)

素子接続用基板、その製造方法および発光ダイオード装置

【課題】接続される発光ダイオード素子を封止シートによって確実に封止することができながら、光反射性に優れる、素子接続用基板、その製造方法、および、発光効率に優れる発光ダイオード装置を提供すること。

【解決手段】素子接続用基板1は、発光ダイオード素子17が上に接続されるためのリードフレーム4であって、互いに隙間2を隔てて配置される複数のリード3を備えるリードフレーム4と、隙間2に充填される光反射性の第1絶縁樹脂部5とを備える。

(もっと読む)

ハードコートフィルム、偏光板、画像表示装置、ハードコート層の密着性向上方法およびハードコートフィルムの製造方法

【課題】相溶層設計のできない樹脂フィルムに対して、紫外線カット機能が付与されているにもかかわらず、高い密着性を持ったハードコート層を付与したハードコートフィルムを提供する。

【解決手段】樹脂フィルム110表面に、ハードコート層120を有するハードコートフィルム100であって、ハードコート層120が、紫外線カット機能を有しており、ハードコート層120が、紫外線反応性樹脂および溶剤を含むハードコート層形成材料を用いて形成されており、樹脂フィルム110とハードコート層120との界面に相溶層が形成されず、樹脂フィルム110のハードコート層120を有する面110aが、表面改質処理がされており、ハードコート層120の、樹脂フィルム110側の界面における前記反応性樹脂の反応率が、55%以上である。

(もっと読む)

半導体装置の製造方法

【課題】 半導体素子の実装時のボイドを抑制し、信頼性の高い半導体装置を製造可能な半導体装置の製造方法を提供すること。

【解決手段】 本発明は、被着体と、該被着体と電気的に接続された半導体素子と、該被着体と該半導体素子との間の空間を充填するアンダーフィル材を備える半導体装置の製造方法であって、基材と該基材上に積層されたアンダーフィル材とを備える封止シートを準備する工程と、半導体ウェハの接続部材が形成された面に上記封止シートを貼り合わせる工程と、上記半導体ウェハをダイシングして上記アンダーフィル材付きの半導体素子を形成する工程と、上記アンダーフィル材付きの半導体素子を100〜200℃で1秒以上保持する工程と、上記被着体と上記半導体素子の間の空間をアンダーフィル材で充填しつつ上記接続部材を介して上記半導体素子と上記被着体とを電気的に接続する工程とを含む。

(もっと読む)

11 - 20 / 5,557

[ Back to top ]