住友電工デバイス・イノベーション株式会社により出願された特許

1 - 10 / 291

光送信モジュール

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

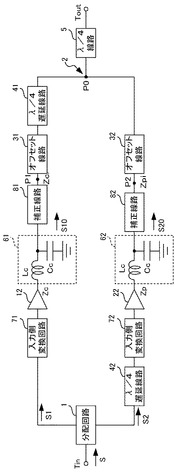

ドハティ増幅器

【課題】 単純な回路構成を有し、調整が容易なドハティ増幅器を提供する。

【解決手段】 第1の入力信号を増幅するキャリアアンプ12と、飽和出力電力がキャリアアンプと異なり、第2の入力信号を増幅するピークアンプ22とを有し、キャリアアンプは、第1のトランジスタと、第1のトランジスタと同一のパッケージ内に設けられた第1の内部変換回路とを含み、ピークアンプは、第2のトランジスタと、第2のトランジスタと同一のパッケージ内に設けられた第2の内部変換回路とを含み、第1及び第2の内部変換回路は、第1及び第2のトランジスタの出力インピーダンスを互いに異なる値に変換する。

(もっと読む)

容量素子

【課題】電極と誘電体部との密着性を良好なものとすること。

【解決手段】本発明は、上部電極18と、下部電極14と、上部電極18と下部電極14との間に配置され、窒化シリコン又は酸化アルミニウムからなる第1の膜22、第2の膜24及び第3の膜26を下部電極14側から順に有し、第1の膜22及び第3の膜26は、第2の膜24よりもシリコン組成比又はアルミニウム組成比が大きい誘電体部16と、を備える容量素子である。

(もっと読む)

半導体装置の製造方法

【課題】チャージアップに起因するリーク電流及び閾値電圧の変動を抑制することが可能な半導体装置の製造方法を提供すること。

【解決手段】本発明は、半導体層内に、活性領域30を含むFET34、活性領域30からなるスクライブライン36、FET34とスクライブライン36との間に位置する不活性領域32、及び不活性領域32を横断してFET34とスクライブライン36とを電気的に接続する接続領域38を設ける工程と、半導体層上に絶縁膜20を形成する工程と、ドライエッチング法により絶縁膜20に選択的に開口部21を形成する工程と、を有する半導体装置である。

(もっと読む)

移相器およびその設計方法

【課題】移相量のばらつきを抑制すること。

【解決手段】第1および第2インダクタと第1キャパシタとを備えるT型のLCLローパスフィルタと、第2および第3キャパシタと第3インダクタとを備えるT型のCLCハイパスフィルタと、を具備し、前記ローパスフィルタと前記ハイパスフィルタとの位相差により移相を行ない、移相を行なう高周波信号の特性インピーダンスをZ0、前記高周波信号の角周波数をω、移相量をΔΘとしたとき、各インダクタおよびキャパシタの値を製造ばらつきによるΔΘが小さくなるように設定する移相器。

(もっと読む)

半導体装置

【課題】良好な放熱性を有し、かつ反りを抑制することが可能な半導体装置を提供すること。

【解決手段】本発明は、ガリウム砒素からなる半導体基板10と、半導体基板10上に設けられた能動層15と、能動層15と対向する半導体基板10の下面に設けられた第1Ni層12と、第1Ni層の下面に設けられたCu層14と、Cu層14の下面に設けられた第2Ni層16と、を具備する半導体装置である。本発明によれば、良好な放熱性を確保し、かつ反りを抑制することが可能な半導体装置を提供することできる。

(もっと読む)

カプラ

【課題】パターンサイズが小さく、結合強度の大きいカプラを提供すること。

【解決手段】複数の第1線路12、14が上下に積層されてなり、前記複数の第1線路のそれぞれ一端と他端が上下で電気的に接続された第1結合線路10と、複数の第2線路22、24が上下に積層されてなり、前記複数の第2線路のそれぞれ一端と他端が上下で電気的に接続された第2結合線路20と、を具備し、前記第1結合線路と前記第2結合線路とは、平行して配置されてなるカプラ。

(もっと読む)

高周波回路装置

【課題】 電気的特性を向上させた高周波回路装置を提供する。

【解決手段】 高周波回路装置は、一端同士1331,1341が互いに離間して対向した2つの伝送線路133,134と、2つの伝送線路の一方の一端に実装され、該実装面となる下面電極30と、該実装時に下面電極の上方に位置する上面電極32を備えるキャパシタCと、2つの伝送線路の対向する一端同士の間の領域に配置され、一端同士を電気的に接続する抵抗素子Rと、キャパシタの上面電極と2つの伝送線路の他方との間を電気的に接続する接続導体135とを備える。

(もっと読む)

半導体装置の製造方法

【課題】エピ抵抗や抵抗チップを用いることなく、奇モードのループ発振を抑えること。

【解決手段】本発明は、金属層60を形成する工程と、複数のFETそれぞれのゲートフィンガー14を共通に接続するゲートバスライン26のパターンのうち一部分を除いたパターンを有するめっき層64と、一部分の領域を被覆する第2マスク層66と、をマスクにして金属層60をパターニングすることで、ゲートバスライン26を形成する工程と、を有する半導体装置の製造方法である。

(もっと読む)

回路基板エッジコネクタ

【課題】エッジコネクタの端子導体間にコネクタの接触子が落ち込まない構造の回路基板エッジコネクタを提供する。

【解決手段】多数の接触子が収容されたコネクタに挿抜されて電気的に接続される多数の端子導体13が配列された回路基板エッジコネクタ11であって、端子導体13の側面にコネクタの接触子17が落ち込んで接触しないように、ソルダレジスト14が形成されている。ソルダレジスト14は、端子導体13の厚さ以上に形成され、また、端子導体のエッジ側先端より先まで形成され、さらに、先端側が傾斜面で形成されている。

(もっと読む)

1 - 10 / 291

[ Back to top ]