レクサー・メディア・インコーポレイテッドにより出願された特許

1 - 10 / 13

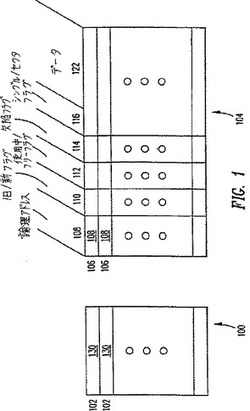

フラッシュメモリ内のブロックにおける移動セクタ

【課題】CAMセル装置の過剰なオーバーヘッドなしに格納されたデータに迅速にアクセスを提供する半導体ハードディスクアーキテクチャーを提供する。

【解決手段】不揮発性メモリ104を有し、ホストに接続された、該不揮発性メモリにブロックで構成された情報を格納するための記憶装置であって、該ブロックの各々は、それに関連した論理ブロックアドレス(LBA)および物理ブロックアドレス(PBA)を有し、該LBAは、アクセスされるブロックを識別するために該ホストによって該記憶装置に提供され、該PBAは、該アクセスされるブロックが格納される該不揮発性メモリ内でフリーロケーションを識別するために該記憶装置によって発展され、該不揮発性内の格納されたブロックの各々は、選択的に消去可能であり、且つ1つ以上のセクタをさらに有する記憶装置。

(もっと読む)

カード識別の互換性

【課題】ホストと1つ以上のデータラインを介してホストに結合される1つ以上のメディアカードとを含む高速通信の自動検出のための高速マルチメディアカードシステムを提供すること。

【解決手段】本発明のシステムは、ホストと1つ以上のデータラインを介してホストに結合される1つ以上のメディアカードとを含み、1つ以上のデータラインのうちの少なくとも1つはシリアルデータラインである。1つ以上のメディアカードはそれぞれそれに関連した固有CIDを有する。各カードの固有CIDを要求するホストからの第1のコマンドに応答し、かつ、ホストに応答して、1つ以上のメディアカードは、シリアルデータラインを介してそのメディアカードの各CIDをホストへ送信し、送信されたCIDがホストから予測されたものと一致する場合、ホストは、CIDが一致したカードに相対カードアドレス(RCA)を割り当てる、第2のコマンドを転送する。

(もっと読む)

複数のデバイスへ同時書き込み操作を行うことにより高まるフラッシュメモリデバイスにおけるメモリ性能

【課題】読み出しおよび書き込み操作を行う際にかかる時間を短縮するために、非揮発性メモリをセクタフォーマットで組織化されたデジタル情報の記憶用に採用し、それによりシステムの全体的な性能を上げ、同時にこのデジタルシステムの製造経費を削減する、デジタルシステムを提供する。

【解決手段】コントローラはセクタ単位に構成された情報を転送し、各セクタはホストと不揮発性メモリバンクとの間にユーザデータ部分およびオーバーヘッド部分を含み、2つの不揮発性メモリデバイス内の同じセクタに関連する2バイトのセクタの記憶および読み出しを同時に行う。各不揮発性メモリデバイスは、メモリロケーションの行によって規定され、ここで、少なくとも2つの半導体デバイスの対応する行が、その内部に2セクタの情報を、不揮発性メモリデバイスのメモリ行の1つに維持された2つのセクタに関連するオーバーヘッド情報と共に維持する。

(もっと読む)

セクタ書き込み操作時間を効果的に減少させるための不揮発性メモリユニット内のブロックの構成

【課題】セクタ書き込み操作時間を効果的に減少させるための不揮発性メモリユニット内の好適なブロックの構成を提供すること。

【解決手段】本発明の一実施形態は、ブロックに分けられた不揮発性メモリ(16)内の格納位置(232)内にセクタ情報を格納する不揮発性メモリシステムを備える。複数のブロックは、スーパーブロックを規定し、各ブロックは所定の複数のセクタを有する。不揮発性メモリシステムは、セクタ情報を、特定のスーパーブロック(204)の第1のブロック(210)と第2のブロック(216)にシフトさせ、セクタ情報を特定のスーパーブロックの第1のブロック(210)に書き込むコントローラ(14)を備える。第1のブロックへの書込み中に、第2のブロック(216)へのシフト全体が起こり、それにより、ブロックへの書込み動作を行うために必要な時間が減少し、全体的なシステム性能が上がる。

(もっと読む)

複数のデバイスへ同時書き込み操作を行うことにより高まるフラッシュメモリデバイスにおけるメモリ性能

【課題】読み出しおよび書き込み操作を行う際にかかる時間を短縮するために、非揮発性メモリをセクタフォーマットで組織化されたデジタル情報の記憶用に採用し、それによりシステムの全体的な性能を上げ、同時にこのデジタルシステムの製造経費を削減する、デジタルシステムを提供する

【解決手段】コントローラはセクタ単位に構成された情報を転送し、各セクタはホストと不揮発性メモリバンクとの間にユーザデータ部分およびオーバーヘッド部分を含み、2つの不揮発性メモリデバイス内の同じセクタに関連する2バイトのセクタの記憶および読み出しを同時に行う。各不揮発性メモリデバイスは、メモリロケーションの行によって規定され、ここで、少なくとも2つの半導体デバイスの対応する行が、その内部に2セクタの情報を、不揮発性メモリデバイスのメモリ行の1つに維持された2つのセクタに関連するオーバーヘッド情報と共に維持する。

(もっと読む)

フラッシュメモリ内のブロックにおける移動セクタ

【課題】CAMセル装置の過剰なオーバーヘッドなしに格納されたデータに迅速にアクセスを提供する半導体ハードディスクアーキテクチャーを提供する。

【解決手段】不揮発性メモリを有し、ホストに接続された、該不揮発性メモリにブロックで構成された情報を格納するための記憶装置であって、該ブロックの各々は、それに関連した論理ブロックアドレス(LBA)および物理ブロックアドレス(PBA)を有し、該LBAは、アクセスされるブロックを識別するために該ホストによって該記憶装置に提供され、該PBAは、該アクセスされるブロックが格納される該不揮発性メモリ内でフリーロケーションを識別するために該記憶装置によって発展され、該不揮発性内の格納されたブロックの各々は、選択的に消去可能であり、且つ1つ以上のセクタをさらに有する記憶装置。

(もっと読む)

メモリシステム

【課題】ディスク装置をエミュレートするソリッドステートメモリを提供すること。

【解決手段】ディスク装置をエミュレートするソリッドステートメモリであって、論理セクタアドレスをメインメモリアドレスに変換する変換手段と、ブロック単位で消去可能な不揮発性メモリセルから構成されるメインメモリとを備え、メインメモリ内の書き込まれていない位置を指すために第一のポインタが使用され、前記書き込まれていない位置を含む消去可能ブロックの次の消去されていない消去可能ブロックを指すために第二のポインタが使用され、第一のポインタと第二のポインタの間に少なくとも一つの消去状態の消去可能ブロックが常にあることを保証すべく制御手段が設けられていることを特徴とするソリッドステートメモリ。

(もっと読む)

メモリ管理

【課題】各論理セクタアドレス値用のデータブロックおよび複数の予備データブロックを使用して、論理セクタアドレスと対応する物理アドレスとの間のマッピングを維持する方法を提供すること。

【解決手段】各論理セクタアドレス値用のデータブロックおよび複数の予備データブロックを使用して、論理セクタアドレスと対応する物理アドレスとの間のマッピングを維持する方法。各データブロックは、直接アドレスフィールドおよび間接アドレスフィールドを含む。論理セクタアドレスにデータが最初に書き込まれたときに、直接アドレスフィールドは、対応する物理アドレスでプログラムされる。その後、同じ論理セクタアドレスにデータが書き込まれるたびに、間接アドレスフィールドが予備データブロックのアドレスでプログラムされ、予備データブロックの直接アドレスフィールドがそのデータの新しい物理アドレスでプログラムされる。

(もっと読む)

改良したコンパクトフラッシュメモリーカードとインターフェース

【課題】改良したコンパクトフラッシュメモリーカードを提供する。

【解決手段】改良したコンパクトフラッシュメモリーカードは、インターフェース装置を通じてコンピュータとの接続に50ピン接続を利用する。フラッシュメモリーカードの50ピンは、ユニバーサルシリアルバスモード、PCMCIAモード又はATAIDEモードのような広い範囲の設定を持つ違ったインターフェース装置と共に利用することができる。あるインターフェース装置に接続すると、この改良したフラッシュメモリーカードは、自動的にどの動作モードがこのインターフェース装置で使用されているかを検知し、現在の動作モードに適合するメモリーカードを設定する。メモリーカードの50ピン全てがメモリーカードからのデータの伝達か制御信号の提供に占められるから、この改良されたフラッシュメモリーカードは、単に選ばれたピンを検知するだけで、現在の動作モードを決定する。

(もっと読む)

メモリ管理

【課題】各論理セクタアドレス値用のデータブロックおよび複数の予備データブロックを使用して、論理セクタアドレスと対応する物理アドレスとの間のマッピングを維持する方法を提供すること。

【解決手段】各論理セクタアドレス値用のデータブロックおよび複数の予備データブロックを使用して、論理セクタアドレスと対応する物理アドレスとの間のマッピングを維持する方法。各データブロックは、直接アドレスフィールドおよび間接アドレスフィールドを含む。論理セクタアドレスにデータが最初に書き込まれたときに、直接アドレスフィールドは、対応する物理アドレスでプログラムされる。その後、同じ論理セクタアドレスにデータが書き込まれるたびに、間接アドレスフィールドが予備データブロックのアドレスでプログラムされ、予備データブロックの直接アドレスフィールドがそのデータの新しい物理アドレスでプログラムされる。

(もっと読む)

1 - 10 / 13

[ Back to top ]