ザ リージェンツ オブ ザ ユニバーシティ オブ ミシガンにより出願された特許

1 - 5 / 5

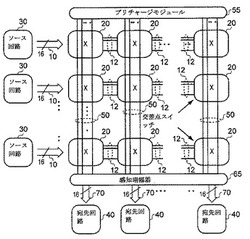

適応型優先順位スキームを適用するためのクロスバー回路、およびそのようなクロスバー回路の動作方法

【課題】クロスバー回路のコンフリクトを解決する。

【解決手段】クロスバー回路はデータ入力経路12およびデータ出力経路50のアレイを有し、各交差点にはルーティング値を記憶するようにプログラム可能な構成記憶回路と、伝送回路と、アービトレーション回路とを備えるクロスバーセル20が提供される。アービトレーション回路は、適応型優先順位スキームを適用するために、同じデータ出力経路と関連する他のクロスバーセルのアービトレーション回路と組み合わせて動作して、該複数のビット線上の電圧を選択的に修正するように動作可能である。同じデータ出力経路に複数の伝送要求がある場合、同じデータ出力経路と関連する唯一のクロスバーセルの構成記憶回路は、第1の値にプログラムされるルーティング値を有し、適応型優先順位スキームに従い複数の伝送要求間のコンフリクトを解決する。さらに、各クロスバーセルは優先順位記憶回路を備える。

(もっと読む)

予備充電ロジックにおけるエラー検出

【課題】内蔵のエラー検出回路を持ったドミノロジックのような予備充電されたロジックを含む集積回路を提供すること。

【解決手段】推論ノード22と検査ノード24とを含むドミノロジックを持つ集積回路2が提供される。予備充電回路36は、推論ノードと検査ノードの両方を予備充電する。論理回路26は、入力信号値に基づいて推論ノードと検査ノードとのため放電路を提供する。評価制御回路28,30は、先ず推論ノードを論理回路に結合し、次いで検査ノードを論理回路に結合するので、もし論理回路26への入力信号が適切な値を持つなら、これらは放電されうる。推論ノードと検査ノードとが両方とも放電されるか又は両方とも放電されないかのいずれでもない場合に、エラー検出回路32はエラーを検出する。

(もっと読む)

クロスバー回路およびそのようなクロスバー回路の動作方法

【課題】クロスバー回路およびそのようなクロスバー回路の動作方法を提供する。

【解決手段】クロスバー回路は、データ入力経路およびデータ出力経路の配列を有し、データ出力経路は、データ入力経路を横断する。データ入力経路とデータ出力経路との間の各交差点には、ルーティング値を記憶するようにプログラムできる記憶回路と、伝送回路と、を備える、クロスバーセルが提供される。伝送動作モードにおいて、伝送回路は、データ入力経路に沿ってデータ入力を検出して、関連付けた交差点において、そのデータの指示をデータ出力経路上に出力するように、データ入力経路がデータ出力経路に連結されるべきであることを示す、ルーティング値に応答する。

(もっと読む)

クロスバー回路およびそのようなクロスバー回路の動作方法

【課題】クロスバー回路およびそのようなクロスバー回路の動作方法を提供する。

【解決手段】クロスバー回路はデータ入力経路およびデータ出力経路の配列を有し、データ出力経路はデータ入力経路を横断する。データ入力経路とデータ出力経路との間の各交差点には、ルーティング値を記憶するようにプログラムできる構成記憶回路と、伝送回路と、アービトレーション回路とを備えるクロスバーセルが提供される。伝送動作モードにおいて、伝送回路は、データ入力経路に沿ってデータ入力を検出して、関連付けた交差点においてそのデータの指示をデータ出力経路上に出力するように、ルーティング値に応答する。アービトレーション動作モードにおいて、アービトレーション回路は、関連付けられたソース回路からの複数のアサートされた伝送要求が存在する場合、所定の優先順位スキームに従い複数のアサートされた伝送要求間のコンフリクトを解消する。

(もっと読む)

メモリセル構造、該メモリセル構造を用いたメモリデバイス、及び該メモリデバイスを具備した集積回路

【課題】従来のメモリセルよりも小型かつ長寿命なメモリセルのデザインを提供する。

【解決手段】メモリデバイス用メモリセル構造は、フローティングゲートノードFGを有したリードトランジスタ120と、第1プログラミング端子160を有したトンネリングコンデンサ130と、第2プログラミング端子150を有したカップリングコンデンサスタック200とを具備する。トンネリングコンデンサ130及びカップリングコンデンサスタック200は、FGに接続されている。カップリングコンデンサスタック200は、FGと第2プログラミング端子150との間に直列に接続された少なくとも2つのカップリングコンデンサから成り、トンネリングコンデンサ130よりも大きい静電容量を有する。

(もっと読む)

1 - 5 / 5

[ Back to top ]