富士通セミコンダクター株式会社により出願された特許

1 - 10 / 2,507

半導体装置の製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体メモリおよびシステム

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

通信端末および応答制御部

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置およびその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体メモリおよびシステム

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

化合物半導体装置及びその製造方法

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置

Notice: Undefined index: from_cache in /mnt/www/gzt_applicant_list.php on line 189

半導体装置の製造方法

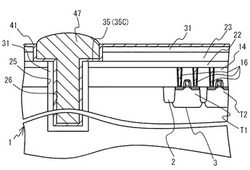

【課題】貫通電極の形成時スループットやコスト悪化を回避する。

【解決手段】シリコン基板1に、貫通電極用のホール26を形成する。さらにホール26

上を含んで絶縁膜22,23をエッチングして溝35を形成する。この後、バリアメタル

層41とシード層42を積層させてから、CMP法による研磨でホール26の内壁及び溝

35内のみにシード層42を残す。シリコン基板1をめっき槽に浸漬させ、溝35を介し

てホール26内に電流を供給すると、ホール26内と溝35のみにCu膜47が成長する

。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】半導体装置を薄型化する技術を提供する。

【解決手段】半導体装置は、基板と、前記基板の上面に設けられた半導体素子と、前記基板の上面に設けられた接着剤と、を備え、前記基板の上面に、前記半導体素子の少なくとも一部を収容する凹部が形成され、前記接着剤は、前記基板と前記半導体素子との間に設けられているとともに、前記基板の凹部を覆っている。

(もっと読む)

半導体集積回路,および,半導体集積回路の試験方法

【課題】チップ面積,製造コストが増大することなく,試験時における電源電圧降下を抑制する半導体集積回路を提供する。

【解決手段】半導体集積回路は,複数のワード線WLと,複数のワード線と交差する複数のビット線対BL,/BLと,複数のワード線と複数のビット線対との交差部に設けられた複数のメモリセル211とを有するメモリと,電源供給線VDDLからの電源電圧を電源として所定の論理演算を行うLOGIC101と,論理回論の試験制御を行う試験制御回路と,電源供給線VDDLに接続され,電源供給線VDDLからの電源電圧を複数のワード線WLに供給するドライバ部222と,試験制御回路の試験制御実行時に,電源電圧を複数のワード線WLに供給して複数のメモリセル211に電源電圧を供給するチャージ回路222aとを有する。

(もっと読む)

1 - 10 / 2,507

[ Back to top ]