アドバンスト・アナロジック・テクノロジーズ・インコーポレイテッドにより出願された特許

1 - 10 / 29

エピレス基板における分離型の相補型MOS装置

【課題】高い実装密度を得ることが可能な半導体装置の製造プロセスを提供する。

【解決手段】半導体装置を電気的に分離するための構造は、エピタキシャル層を含まない半導体基板240内にドーパントを打込むことにより形成される。この打込みに続き、極めて限られた熱収支に上記構造を晒すことでドーパントが顕著に拡散しないようにする。その結果として、上記分離構造の寸法が制限かつ規定され、こうして、エピタキシャル層を成長させる工程とドーパントを拡散させる工程とを含む従来のプロセスを用いて得られるよりも高い実装密度を得ることができる。

(もっと読む)

トレンチにより制限された分離拡散領域を備えた相補型アナログバイポーラトランジスタ

【課題】表面上に素子をより高密度に実装する。

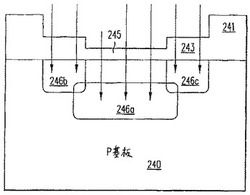

【解決手段】第1のトレンチと第2のトレンチとの間の位置において、エピタキシャル層の表面から基板へと下方に延在するドーパントのウェルは、エピタキシャル層の背景ドーピング濃度とは異なるドーピング濃度を有し、エピタキシャル層の残りの部分と第1および第2の接合を形成する。第1の接合は、第1のトレンチの底部から基板に延在し、第2の接合は、第2のトレンチの底部から前記基板に延在する。ウェルおよび第1および第2のトレンチは分離構造を構成し、分離構造は、分離構造の一方側のエピタキシャル層に形成された第1の素子と分離構造の他方側のエピタキシャル層に形成された第2の素子とを電気的に分離する。分離構造による電気的分離は第1および第2のトレンチとPN接合とによってもたらされ、ウェルは第1の導電型の材料でドープされ、基板およびエピタキシャル層は、第1の導電型とは反対の第2の導電型の材料でドープされ、第1および第2の接合はPN接合である。

(もっと読む)

半導体デバイス、半導体基板に分離されたポケットを形成する方法、半導体構成、PNPトランジスタ、横型NチャネルDMOSトランジスタ、横型トレンチDMOSトランジスタ

【課題】モジュール化された、相互作用しないやり方で、単一の半導体ウェハにともに接近して実装され、十分に分離された、最適化されたトランジスタまたは他のデバイスの任意の集合の作製を可能にする。

【解決手段】

一群の半導体デバイスが、エピタキシャル層を含まない基板に形成される。一実施例では、この一群は、5VのCMOSペア、12VのCMOSペア、5VのNPN、5VのPNP、いくつかの形状の横型トレンチMOSFET、および30V横型N−チャネルDMOSを含む。これらのデバイスの各々は、横方向かつ縦方向の双方において極めて小型であり、基板の他のすべてのデバイスから十分に分離され得る。

(もっと読む)

トレンチゲート縦型MOSFET

【課題】トレンチゲート縦型MOSFETにおいて、ゲート信号の伝播遅延をより小さくし、高速もしくはより高い周波数でのデバイス・オペレーションを可能にする

【解決手段】パワーMOSFETおよびその製造プロセスは、トレンチの内の連続的な伝導性ゲート構造を採用して、アクティブセル領域のトレンチゲートを形成し、ゲートバストレンチ中にゲートバスを形成する。ゲートとなる金属等の導電性材料を、トレンチ内においてシリコン層で包囲してゲート酸化膜領域と直接接触しない構成とすることにより、ゲート酸化膜の金属汚染を生じることなく高い導電性の金属をゲートとして取り入れることが可能となり、もって信号の伝播遅延をより小さくし、高速もしくはより高い周波数のデバイス・オペレーションが可能となる。

(もっと読む)

改善された過渡電流能力を有する昇圧DC/DC電圧コンバータ

DC/DC電圧コンバータは、コンバータの入力端子および出力端子の間に直列に接続された、誘導型スイッチング電圧調整器および容量型チャージポンプを含む。チャージポンプは、コンバータの入力端子に接続された第2の入力端子を有する。これは、チャージポンプ内のキャパシタから出力キャパシタへ電荷が伝送される電流経路における直列抵抗を低減し、それによって、コンバータの能力を改善して負荷によって要求される電流の急激な変化に応答する。  (もっと読む)

(もっと読む)

ディスクリートパワー半導体デバイスのカスコード電流センサ

カスコード電流センサは、メインMOSFETと検知MOSFETとを含む。メインMOSFETのドレイン端子は、電流が監視されるパワーデバイスに接続され、メインMOSFETのソース端子およびゲート端子は、それぞれ、検知MOSFETのソース端子およびゲート端子に接続される。ある実施例において、メインMOSFETおよび検知MOSFETのドレイン電圧は、変動電流ソースおよびネガティブフィードバックを用いて、等しくされる。メインMOSFETのゲート幅は、典型的に検知MOSFETのゲート幅よりも大きい。ゲート幅の大きさの比を用いて、検知MOSFET内の電流の大きさを検知することにより、メインMOSFET内の電流が計測される。比較的大きいMOSFETをパワー回路に導入することにより、電力損失を最小限にする。  (もっと読む)

(もっと読む)

二極性マルチ出力DC/DCコンバータ及び電圧レギュレータ

2出力二極性インダクティブ・ブースト・コンバータが、インダクタと、第1の出力ノードと、第2の出力ノードと、スイッチング・ネットワークとを含み、スイッチング・ネットワークは、以下の回路動作モード、すなわち、1)インダクタの正電極が入力電圧に接続され、インダクタの負電極が接地された第1のモードと、2)インダクタの正電極が第1の出力ノードに接続され、インダクタの負電極が第2の出力ノードに接続された第2のモードと、3)インダクタの正電極が入力電圧に接続され、インダクタの負電極が第2の出力ノードに接続された第3のモードと、を提供するように構成される。  (もっと読む)

(もっと読む)

時分割マルチ出力DC/DCコンバータ及び電圧レギュレータ

複数の出力を有するブースト・スイッチング・コンバータが、入力電源(通常はバッテリ)とノードVxとの間に接続されたインダクタを含む。ローサイド・スイッチがノードVxと接地とを接続する。2又はそれ以上の出力ステージが含まれる。個々の出力ステージは、ハイサイド・スイッチ及び出力キャパシタを含む。それぞれの負荷へ電流を送出するために個々の出力ステージが接続される。ローサイド・スイッチとハイサイド・スイッチとを反復シーケンスで駆動するために制御回路が接続される。最初にインダクタが充電され、その後個々の出力ステージに放電される。実際には、各々が異なる出力電圧を有する一連の異なるスイッチング・コンバータが設けられる。  (もっと読む)

(もっと読む)

マルチ出力を有する時分割キャパシタDC/DCコンバータ

新しい時分割キャパシタ・コンバータ・アルゴリズム及び関連する回路トポロジを使用したマルチ出力DC−DC電圧コンバータを本明細書に開示する。本発明の1つの実施形態は、フライング・キャパシタと、第1の出力ノードと、第2の出力ノードと、スイッチング・ネットワークとを含む。スイッチング・ネットワークは、以下の回路動作モード、すなわち、1)フライング・キャパシタの正極が入力電圧に接続され、フライング・キャパシタの負極が接地された第1のモードと、2)フライング・キャパシタの負極が入力電圧に接続され、フライング・キャパシタの正極が第1の出力ノードに接続された第2のモードと、3)フライング・キャパシタの正極が接地され、フライング・キャパシタの負極が第2の出力ノードに接続された第3のモードとを提供するように構成される。  (もっと読む)

(もっと読む)

同期フリーホイーリングMOSFETを有するブーストおよびアップ/ダウンスイッチングレギュレータ

フリーホイーリングMOSFETは、スイッチトDC/DCコンバータにおいてインダクタと並列に接続される。コンバータのスイッチング動作中にフリーホイーリングMOSFETがオンにされる一方、ローサイドおよびエネルギ伝達MOSFETがオフにされると、インダクタ電流はフリーホイーリングMOSFETの中を循環または「フリーホイール」する。それによって、コンバータの周波数は磁化およびエネルギ伝達段階の長さから独立し、コンバータを動作させる際の柔軟性がはるかに高くなることが可能であり、従来のDC/DCコンバータにまつわる数多くの問題を克服する。たとえば、コンバータは、昇圧モードまたは降圧モードのどちらのモードで動作してもよく、入力電圧および所望の出力電圧の値が変化すると、1つのモードから他のモードに遷移しさえしてもよい。  (もっと読む)

(もっと読む)

1 - 10 / 29

[ Back to top ]