フェアチャイルド・セミコンダクター・コーポレーションにより出願された特許

1 - 10 / 62

パワー半導体デバイスおよびその製造方法

【課題】改善されたパワーデバイスに加えてそれらの製造方法,パッケージ化の実施例を提供する。1実施例としては、シールドされたゲートトレンチMOSFETにおいて、多くの電荷調整技術と寄生容量を低減する他の技術とを組み合わせて、改善された電圧性能,速いスイッチング速度および低いオン抵抗を有するパワーデバイスを提供する。

【解決手段】シールドポリ311の上にゲートポリ310を含み、垂直方向電荷制御のために、ゲートトレンチ302より深い位置にある非ゲートトレンチを含み、電荷制御トレンチ301は、トレンチの最上部でソース金属に接続する導電材料の単層を有し得るが、独立してバイアスがかけられ、多重に積み重ねられたポリ電極313を使用する。また、デュアルゲート構造を用いることによってゲートとドレインとの間の容量Cgdを低減する。

(もっと読む)

酸化後のシリコントレンチ底部形状の構造及び形成方法

【課題】効率的に形成されかつボイドが僅かであるかまたは実質的に存在しないFCC構造を提供する。

【解決手段】基板内で上表面からある深さまで垂直に伸長し、かつ第1の側壁、第1の底部、及びトレンチの当該第1の底部近傍の当該第1の側壁に形成されているパターン215を有する第1のトレンチ210を基板内に形成するステップと、第1のトレンチの第1の側壁及び第1の底部上に酸化層235を形成するステップと、を含むLFCCデバイスの製造方法であって、酸化層は、第1のトレンチ内に配されかつ酸化層によって第1のトレンチから分離されている第2のトレンチをもたらす。第2のトレンチは、パターンを呈さず実質的に垂直な第2の側壁及び実質的に平坦な第2の底部を有する。当該パターンは、第1のトレンチの底部と第1の側壁との間の酸化レートの差を補償する。当該LFCC構造は、当該パターンを有する第1のトレンチを含む。

(もっと読む)

ドレインクリップを備えた半導体ダイパッケージ

【課題】パワートランジスタからの熱を除去して過熱を回避すべく特殊なパッケージを提供する。

【解決手段】半導体ダイパッケージは第1表面、第2表面、及び第1表面にゲート領域とソース領域とを有し第2表面にドレイン領域を有する垂直パワーMOSFETを備えた半導体ダイ108を含んでいる。ドレインクリップ101はドレイン領域に電気的に結合した主表面101(a)を有している。ゲートリード112はゲート領域に電気的に結合している。ソースリード111はソース領域に電気的に結合している。非導電性成形材料102が半導体ダイ108を封入している。ドレインクリップ101の主表面101(a)が非導電性成形材料102を介して露出している。

(もっと読む)

リードフレーム構造を含む半導体ダイパッケージ及びその製造方法

【課題】より薄い電子デバイス及びより薄い電子部品を提供する。

【解決手段】半導体ダイパッケージが開示されている。1つの実施例において、該半導体ダイパッケージは基板40を有する。この基板は、(i)ダイ取付表面を有するダイ取付領域12とリード表面を有するリードとを含むリードフレーム構造10、及び(ii)モールド材20を含む。該ダイ取付表面及び該リード表面がモールド材を介して露出せしめられる。半導体ダイが該ダイ取付領域上に配置され、該半導体ダイが該リードに電気的に結合される。

(もっと読む)

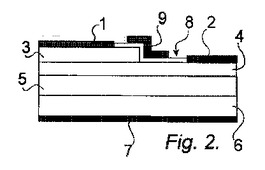

シリコンカーバイドバイポーラ接合トランジスタ

本発明は、シリコンカーバイド(SiC)バイポーラ接合トランジスタ(BJT)に関し、当該トランジスタ上のエミッタコンタクトとベースコンタクトと(1、2)の間の表面領域には、バルクSiC内の電位と比較して負の表面電位が与えられている。  (もっと読む)

(もっと読む)

基板ドレイン接続を有する横型MOSFET

1つの形式として、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているアクティブゲートを含み、当該ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、横型MOSFETは、ドレイン領域の上に配されている非アクティブゲートをさらに含む。他の形式において、横型MOSFETは、ソース領域とドレイン領域との間に横方向に配されているゲートを含み、ドレイン領域は、単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張し、ソース領域及びドレイン領域は第1の導電タイプであって、横型MOSFETは、ソース領域に接しておりかつソース領域の下方にある第2の導電タイプのヘビーボディ領域をさらに含み、ドレイン領域は、ゲートのエッジに近接しているライトドープドレイン(LDD)領域及び単結晶半導体ボディの上面から単結晶半導体ボディの底面まで伸張しているシンカーを含んでいる。  (もっと読む)

(もっと読む)

集積低漏洩ショットキーダイオード

MOSゲートの一方の側部に近接しているショットキーバリアを有し、当該ゲートの他方の側部にドリフト領域の一端を有する集積低漏洩ショットキーダイオードである。ショットキー金属及びゲート酸化膜の下は、P層とそれを覆うN層のリサーフ構造であり、当該リサーフ構造がドリフト領域を形成し、当該ドリフト領域は本発明の1つの実施例においてダイオードのカソードで終端する。当該N層及びP層は、当該ゲートの下に上向きに凸の凹形状を有する。ゲート電極及びショットキー金属は、ダイオードのアノードに接続されている。P層が当該リサーフ構造とNISO領域との間にあり、NISO領域が当該アノードとの電気的接続を有している。ショットキー金属の下のP+層は、Pウェルを通してP−層と接続されている。  (もっと読む)

(もっと読む)

効率的熱放散のための配線なし半導体パッケージ

本明細書において、複数のダイを有する配線なしの半導体パッケージが開示され、当該ダイの少なくとも2つは熱伝導性及び導電性を有するヒートシンクに取り付けられる。当該パッケージは熱を放散させるのに効率的な手段を提供する。  (もっと読む)

(もっと読む)

集積ショットキーを有する高密度FET

半導体構造は、モノリシック集積トレンチFET及びショットキーダイオードを含む。半導体構造は、第1導電型の半導体領域にまで延在する複数のトレンチをさらに含む。多数のゲート電極及びシールド電極が前記トレンチの各々内に設けられている本体領域は隣接するトレンチ間の半導体領域上に延在し、ソース領域が、各本体領域上に延在している。テイパー形状のエッジを有する凹部が、2つの隣接するトレンチの上角部から本体領域まで2つの隣接するトレンチ毎の間に延在し、本体領域の下方の半導体領域内で終端する。相互接続層は各凹部まで延在して、前記ソース領域及び前記本体領域のテイパー形状の側壁に電気的に接触し、かつ、各凹部の底部に沿って半導体領域に接触して、自身の間にショットキーコンタクトを形成する。  (もっと読む)

(もっと読む)

電力デバイスのための超接合構造及び製造方法

電力デバイスは、活性領域と、当該活性領域を囲んでいる終端領域と、当該活性領域及び当該終端領域の各々にそれぞれが交互に配置された第1及び第2導電型の複数のピラーと、を含む。当該活性領域及び当該終端領域における第1導電型のピラーは実質的に同一幅を有し、且つ当該活性領域における第2導電型のピラーは当該終端領域における第2導電型のピラーより小さい幅を有することによって、当該活性領域及び当該終端領域の各々における電荷平衡状態は、当該終端領域におけるブレークダウン電圧が当該活性領域におけるブレークダウン電圧よりも高くなることを特徴とする電力デバイス。  (もっと読む)

(もっと読む)

1 - 10 / 62

[ Back to top ]