Fターム[2G011AA00]の内容

測定用導線・探針 (17,446) | 探針形状 (4,849)

Fターム[2G011AA00]の下位に属するFターム

他に分類されない形状 (383)

針状、ひげ状、触針 (578)

球状、先端が丸い (143)

凹凸状、刃状、板状 (269)

クリップ形、わに口クリップ (23)

鉤形、引掛け形 (12)

中空環状、先端に穴 (43)

二股状 (16)

錐形、先端が円錐、先端が三角錐 (285)

平形、先端が平面、面接触 (280)

クランプ形 (7)

複合形、入力信号が2以上 (2,325)

電極状、突起状 (420)

同軸状 (54)

Fターム[2G011AA00]に分類される特許

1 - 11 / 11

半導体検査装置用プローブピン、その製造方法及び半導体検査方法

【課題】プローブピンがはんだと接触した際に、はんだの主成分であるスズがプローブピンの接触部に凝着することを防ぎ、耐スズ凝着性に優れた導電性皮膜を基材表面に形成して成る半導体検査装置用プローブピンを提供することを目的とする。

【解決手段】 導電性基材と、銅およびジルコニウムを含有する銅−ジルコニウム皮膜とを含む半導体検査装置用プローブピンであって、前記銅−ジルコニウム皮膜において、ジルコニウムと銅の総原子数に対するジルコニウム原子数の割合が、15〜85原子%であり、前記皮膜の膜厚が、0.05〜3μmであることを特徴とする半導体検査装置用プローブピン。前記銅−ジルコニウム皮膜はさらに炭素原子を含み、前記銅−ジルコニウム皮膜の総原子数に対する炭素原子数の割合が、40原子%以下であることが好適である。

(もっと読む)

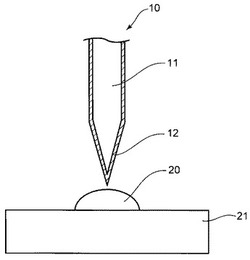

コンタクトピン

【課題】コンタクトピンの接触抵抗の増加を抑えるとともに、非磁性であるコンタクトピンを提供することを目的としている。

【解決手段】導電材からなる基材2上に、ニッケルとリンの合金からなる中間層3と、パラジウムと銀の最表層4を設けコンタクトピン1を構成する。このコンタクトピン1をバーンイン試験のための使われるICソケットのICの各端子に対応して装着し、ICの各端子とバーンイン試験にためのICソケットを搭載した基板との電気的接続を行う。

(もっと読む)

プローブカード用セラミック配線基板およびこれを用いたプローブカード

【課題】 熱負荷試験時において、プローブカード用セラミック配線基板に設けられたプローブピンとSiウエハの表面に形成された測定パッドとの位置ずれが小さく、電気特性の検査に好適に使用できるプローブカード用セラミック配線基板とこれを用いたプローブカードを提供する。

【解決手段】 X線回折のデータを用いたリートベルト解析により求めた結晶相の割合で、ムライトが48〜81質量%、アルミナ、ディオプサイトおよびジルコンから選ばれる少なくとも1種の結晶相が19〜52質量%であり、吸水率が1%以下のセラミック焼結体からなるセラミック絶縁層と、銅が40〜60体積%、タングステンが40〜60体積%となる組成を有する銅とタングステンとの複合導体とを具備する。

(もっと読む)

プローブの検査方法及び硬化性樹脂組成物

【課題】被検査体の電気的特性を検査するプローブの状態を確認するプローブ検査方法とそれに用いる硬化性樹脂組成物の提供。

【解決手段】被検査体の電気的特性を検査するプローブに硬化性樹脂組成物の硬化体を接触させ、硬化体にプローブの針跡を転写して、転写された針跡を基にプローブの状態を確認し、かつ、プローブの針跡を転写した後に、硬化体を硬化体のガラス転移温度以上に加熱してプローブの針跡を消去する工程を含み、繰り返し検査に供するプローブの検査方法であり、硬化性樹脂組成物が、特定の単官能(メタ)アクリレート、光重合開始剤、酸化防止剤を含有し、硬化性樹脂組成物の硬化体のガラス転移温度が40℃以上100℃未満であることを特徴とするプローブの検査方法。

(もっと読む)

非晶質炭素膜被覆部材の製造方法および半導体検査装置用プローブピン

【課題】導電性と耐久性を兼ね備えると共に、相手材(特にハンダに含まれるSn)の付着・凝着を極力低減して長寿命化を図ることのできる非晶質炭素膜被覆部材を製造するための有用な方法、およびこのような非晶質炭素膜被覆部材からなる半導体検査装置用プローブピンを提供する。

【解決手段】基材表面にタングステン含有非晶質炭素膜を被覆した非晶質炭素膜被覆部材を製造するに当り、固体炭素ターゲット3と固体タングステンターゲット2から別々に形成される2つの蒸発雰囲気で、前記基材表面を交互に複数回処理すると共に、1回当りの処理で蒸着されるタングステン量は理論厚さが0.40×10-10m以上、2.74×10-10m未満に相当するように設定して操業する。

(もっと読む)

プローブカード

【課題】複雑な配線の引き回しをシンプルにすることが可能なプローブカードを提供する。

【解決手段】プローブユニット2、可撓性基板18と、上記可撓性基板の表面上にそれぞれが略平行に配置された信号用可撓配線12、電源用可撓配線10およびグランド用可撓配線11の可撓配線群と、電源用ボンディングパッド13、信号用ボンディングパッド15、グランド用ボンディングパッド14を含むボンディングパッド群とを備えたフレキシブル配線板3、および、上記電源配線と上記電源用ボンディングパッド、上記グランド配線と上記グランド用ボンディングパッド、および上記信号配線と上記信号用ボンディングパッドをそれぞれ接続するボンディングワイヤを備え、上記電源用ボンディングパッドと上記グランド用ボンディングパッドの少なくとも一方が、上記可撓配線群に対して直交する方向で複数本分の上記可撓配線の先端領域におよぶ拡張領域を有している。

(もっと読む)

プローブ・カード基板上のタイル角部のソーイング

【課題】 プローバ又はプローブ・カードを支持するための他の試験デバイスの領域の範囲内に基板自体が収まるように設けると同時に、製造が簡単かつ安価である基板を設けることである。

【解決手段】 半導体デバイスを試験するための複合基板を形成する。このため、複数の実質的に同一の個々の基板を選択し、最終アレイ構成における位置に従って個々の基板の少なくともいくつかから角部を切断し、次いで個々の基板を最終アレイ構成に組み立てる。角部が切断又はソーイングされた基板の最終アレイ構成は、試験対象のウェーハの表面領域に緊密に合致し、試験環境の空間制限内に容易に収まることができる。

(もっと読む)

プローブ

【課題】高密度の配線パターンが形成されたフリップチップ面においても簡単な構造によって確実に測定対象と接触して四端子測定を行うことのできる測定用プローブ、その製造方法及び測定装置を提供する。

【解決手段】測定用プローブは、測定対象の抵抗値を測定するために測定対象と接触する接触部をそれぞれ有し、一方が電圧測定に他方が電流印加に用いられる第1及び第2のプローブ部を備える。その測定用プローブにおいては。第2のプローブ部が、第1のプローブ部を囲むように形成される本体部と、接触部を含むヘッド部と、ヘッド部が第1のプローブ部の接触部を軸方向に突出するように弾性的に付勢する付勢手段を有するとともに、ヘッド部の接触部が不使用時に第1のプローブ部の接触部よりも突出した位置にある。

(もっと読む)

半導体試験ボード

【課題】ピンアサインの異なる被試験デバイスに対して同一のFTボード(パフォーマンスボード)を使用することができるようにし、半導体デバイスの試験コストの低減化を図ることができるようにした半導体試験ボードを提供する。

【解決手段】本発明の第1実施形態28は、多層基板29を用意し、接触子45を始めとする電源用の接触子と、接触子46を始めとする接地用の接触子と、接触子47を始めとする信号用の接触子とを、DUT13のピンアサインに応じて多層基板29に装着することにより構成することができ、ICソケット17とFTボード22との間に介在させて使用する。

(もっと読む)

プローブカード

【課題】 プローブカードに関し、製品品種毎の専用のプローブカードの製作を不必要にする。

【解決手段】 プローブカード1を構成する多層配線構造中継用基板3とプローブ針4の先端部との間に交換可能な電源用プレーン5,6を少なくとも一枚設ける。

(もっと読む)

BGAパッケージ用検査用具及び検査方法

【課題】 BGAパッケージに収納された素子の電気的特性を精度よく測定する。

【解決手段】 BGAパッケージのはんだボールのピッチに合わせて孔(スルーホール)が設けられた絶縁基板を用意する。孔の縁は導電性の部材で覆われてスルーホール電極が形成されている。各々のスルーホール電極には引き出し配線が接続されている。各々のスルーホール電極がはんだボールに接触するように基板が配置される。プローブピンがスルーホールに通されて、はんだボールに接触させられる。プローブピンに電流を流してフォース端子とし、スルーホール電極からの引き出し配線をセンス端子として、4端子法(ケルビン法)による抵抗値の測定が行われる。

(もっと読む)

1 - 11 / 11

[ Back to top ]