Fターム[2G132AA00]の内容

電子回路の試験 (32,879) | 試験対象 (5,171)

Fターム[2G132AA00]の下位に属するFターム

論理回路 (2,000)

アナログデジタル混在回路(AD変換器等) (239)

アナログ回路 (164)

ASIC (97)

マルチチップモジュール (163)

機能ブロック(マクロセル)を有するもの (200)

バッファ (73)

ICカード等 (26)

実装基板 (349)

Fターム[2G132AA00]に分類される特許

1 - 20 / 1,860

半導体試験装置および半導体試験方法

故障解析装置および故障解析方法ならびにスクリーニングテスト装置およびスクリーニングテスト方法

半導体特性測定装置

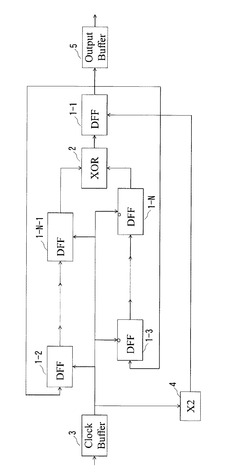

疑似ランダムビット列発生器

【課題】高速動作可能な疑似ランダムビット列発生器を提供する。

【解決手段】疑似ランダムビット列発生器は、ハーフレート・クロック信号の所定のタイミングで入力信号を識別再生する、縦続接続された(N−1)/2個(Nは奇数)のDFF1−3,・・・,1−Nと、ハーフレート・クロック信号によって決定される動作タイミングがDFF1−3,・・・,1−Nの動作タイミングと180度位相が異なるタイミングで入力信号を識別再生する、縦続接続された(N−1)/2個のDFF1−2,・・・,1−N−1と、排他的論理和回路2と、ハーフレート・クロック信号の2倍の周波数のフルレート・クロック信号により排他的論理和回路2の出力信号を識別再生するDFF1−1とを備える。

(もっと読む)

試験パターン生成装置、試験プログラム生成装置、生成方法、プログラム、および試験装置

【課題】試験装置のハードウェア仕様および試験装置用のプログラム言語に詳しくないユーザでも、試験パターンを容易に作成させる装置を提供する。

【解決手段】複数の端子を有する被試験デバイスとの間で通信する試験パターンを生成する試験パターン生成装置であって、基本サイクル中に複数の端子のそれぞれとの間で通信する信号パターンを示すサイクルプリミティブをユーザの指示に基づき生成するプリミティブ生成部と、ユーザの指示に基づき複数のサイクルプリミティブを配列して、複数の基本サイクル分の信号パターンを示すデバイスサイクルを生成するデバイスサイクル生成部と、ユーザの指示に基づき複数のデバイスサイクルを配列して、被試験デバイスに供給する試験パターンのシーケンスを生成するシーケンス生成部と、を備える試験パターン生成装置を提供する。

(もっと読む)

半導体装置及びそのテスト方法

【課題】データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置のDCテストの実施には、振幅を維持できないという問題がある。そのため、データ信号ラインにAC結合部が含まれる出力回路を備える半導体装置であって、DCテストを可能にする半導体装置が、望まれる。

【解決手段】半導体装置は、データ信号を外部に出力するメインドライバと、データ信号が伝達する配線と接続されているコンデンサと、一端がコンデンサと接続され、他の一端がバイアス電圧源に接続されている終端抵抗と、バイアス電圧源と終端抵抗との間に接続されている第1のスイッチと、を含むAC結合部と、テストモード時にAC結合部のバイアス電圧源と終端抵抗との接続を、第1のスイッチにより遮断する制御回路と、を備える。

(もっと読む)

ウェハ検査装置及び検査方法

【課題】検査時のプロービングによる不良の疑いのあるチップの流出を確実に防止することのできるウェハ検査装置及び検査方法を提供する。

【解決手段】各チップにプローブを接触させて通電テストを制御するテスト制御手段5と、テスト制御手段5の結果からチップの良否を判定するテスト判定手段6と、各チップのアドレス情報と各チップに対するテスト判定手段6のテスト判定情報及びプローブによるコンタクト情報とを対応させて記憶する記憶手段7と、プローブがチップに接触する毎にチップのアドレス情報に対応するコンタクト情報を更新するコンタクト制御手段8と、コンタクト情報が予め設定した限界条件を超えたときはチップを不良と判定するコンタクト判定手段9とを備える。

(もっと読む)

試験モジュール生成装置、試験手順生成装置、生成方法、プログラム、および試験装置

【課題】試験装置のハードウェア仕様および試験装置用のプログラム言語に詳しくないユーザでも、試験プログラムを容易に作成させる装置を提供する。

【解決手段】被試験デバイスの試験モジュールを生成する試験モジュール生成装置であって、試験条件を入力し、入力された前記試験条件を定義する条件ファイルを生成する条件ファイル生成部と、試験メソッドを記憶する試験メソッド記憶部と、生成すべき試験モジュールに応じた試験メソッドの選択指示をユーザから受け取る試験手順選択部と、選択された試験メソッドが要求するパラメータに対応する条件ファイルの選択指示をユーザから受け取る条件ファイル選択部と、選択された試験メソッドに応じた試験を選択された条件ファイルにより定義されたパラメータで実行する試験モジュールを生成する試験モジュール生成部と、を備える試験モジュール生成装置を提供する。

(もっと読む)

半導体装置の故障位置解析方法及び装置

【課題】SiC半導体装置における故障位置をOBIRCH法により解析して特定できるようにした半導体装置の故障位置解析方法及び装置を提供する。

【解決手段】半導体装置の基板の裏面側から、該基板の表面側のデバイス及び回路に、レーザー光を走査しながら照射して加熱すると共に、前記デバイス及び回路に電流を流し、電流の変化によって抵抗値変化を検出して、故障位置を解析する半導体装置の故障位置解析方法において、前記半導体装置が、NドープSiC基板を用いた半導体装置であり、前記レーザー光として、波長650〜810nmのレーザー光を用いる。

(もっと読む)

テストデータ生成装置および方法

【課題】各種テスタに共通なテストデータから、個々のテスタの制約に合致したテストデータを自動的に生成することのできるテストデータ生成装置および方法を提供する。

【解決手段】実施形態のテストデータ生成装置1は、タイミング記述検証部11が、共通テストデータ100に記述された1サイクル当たりのタイミングエッジ数が指定されたテスタの制約範囲内かを検証し、タイミングエッジ数が前記制約を超えている場合は、サイクライズ期間設定部12が、タイミングエッジ数および1サイクルの期間がテスタの制約範囲内となるサイクライズ期間を設定し、イベントデータ展開部13が、テストデータ100をイベントデータに展開し、サイクライズ処理部14が、そのイベントデータをサイクライズ期間でサイクライズし、テストデータ出力部15が、サイクライズ後のイベントデータを元の記述形式へ逆変換し、修正版共通テストデータ200を出力する。

(もっと読む)

マルチICデバイスをテストするための方法および装置

【課題】マルチICデバイスをテストするための方法および装置を提供する。

【解決手段】集積回路は、入力信号を受け取るように構成される第1の入力相互接続と、テスト・イネーブル信号を受け取るように構成される第1のテスト・イネーブル相互接続と、前記入力信号に対応する値に基づいて該集積回路のテストを実行するためのコントローラと、入力ポートと、前記第1の入力相互接続、前記コントローラ、および前記入力ポートに結合され、前記テスト・イネーブル信号がアサートされていないことに応答して前記入力信号を前記入力ポートに渡し、前記テスト・イネーブル信号がアサートされていることに応答して前記入力信号を前記コントローラに渡すように制御可能である第1のマルチプレクサとを備える。

(もっと読む)

擬似障害発生方法と装置

【課題】電子回路装置に対する擬似障害発生を容易化し、試験・評価等の作業を効率化する装置、方法の提供。

【解決手段】

電子回路装置(100)を構成する回路基板(105)上のIC(104)のON/OFF端子に接続部103を介して接続する制御部102が、ケーブルコネクタ部(101)を介してPC(110)の制御により、IC(104)のON/OFF端子に動作中の第1の値とは異なる第2の値を設定することで擬似障害を発生させる。

(もっと読む)

スイッチングマトリクスおよびその半導体素子の特性試験システム

【課題】スイッチングマトリクスのオン・オフ操作を制御するためにセンサおよびコントローラを備えたスイッチングマトリクスを提供する。

【解決手段】スイッチングマトリクスは、スイッチアレイ30を備えており、スイッチアレイ30は、一つ以上の入力ポートと、一つ以上の出力ポートと、前記入力ポートと前記出力ポートとの間の電気的な通路を開閉するように配置されている一つ以上のスイッチ素子36と、前記電気的な通路の所定の電気的特性を測定するとともに、これに基づいて信号を生成するように配置されている電気的なセンサ38または電気的なセンサアセンブリと、を備えている。電気的なセンサアセンブリが、電圧センサ、電流センサ、または電力センサであることが好ましい。

(もっと読む)

プローブ装置

【課題】パワーデバイスの静特性及び動特性の双方をウエハレベルで測定することができ、特に静特性に使用される測定ラインに影響されることなく、パワーデバイスの動特性をウエハレベルで確実に測定することができるプローブ装置を提供する。

【解決手段】本発明のプローブ装置10は、複数のパワーデバイスが形成されたウエハWを載置する移動可能な載置台12と、載置台12の上方に配置された複数のプローブ14Aを有するプローブカード14と、載置台12の載置面とその外周面に形成された導体膜電極13と、導体膜電極13とテスタ17とを電気的に接続する測定ライン16と、を備え、載置台12上のパワーデバイスの電気的特性をウエハレベルで測定するプローブ装置であって、第2の測定ライン16には、導体膜電極13とテスタ17の間で測定ライン16の電路を開閉するスイッチ機構18を設けたものである。

(もっと読む)

半導体検査装置、および半導体検査方法

【課題】本発明は、テストパターンを長く複雑なパターンにする必要がなく、スクリーニングで検出することができる回路パターンの不具合の割合を増やすことができる半導体検査装置、および半導体検査方法を提供する。

【解決手段】本発明は、半導体基板に形成した複数の半導体チップに対してスクリーニングを行なう半導体検査装置10である。半導体検査装置10は、ステージ2と、プローブ4と、テスタ部8と、光検出部5と、発光解析部6と、主制御部7と、異常判定部9とを備えている。光検出部5は、光学的なスクリーニングを行なうために、回路パターンに印加した電気信号に基づく発光を、半導体基板の他方の面側から検出する。異常判定部9は、テスタ部8で検出した出力信号に基づき、回路パターンの不具合を判断し、発光解析部6で解析した発光に基づき、回路パターンの不具合を判断して、半導体チップの異常を判定する。

(もっと読む)

信号生成装置及び信号生成方法

【課題】任意のジッタが付加された良好な信号波形を有する信号を容易に生成することができる信号生成装置を提供する。

【解決手段】基準クロックを基に制御データに応じた周波数の出力クロックを生成し出力するダイレクトデジタルシンセサイザ(DDS)と、ジッタ設定に応じてDDSの出力周波数を制御するための一連の設定データが格納されたジッタ制御テーブルを有し、基準クロックに同期させてDDSに制御データを供給する制御部とを備え、基準クロックに同期したタイミングで制御データをジッタ制御テーブルに格納されている設定データで順次書き替えることで、短時間かつ一定の時間間隔で制御データの切り替えを行い、周期的に周波数が変化する、すなわちジッタが付加された出力クロックをDDSにより生成できるようにする。

(もっと読む)

半導体装置の製造方法、測定装置、送出装置、及び、プログラム

【課題】仲介部材を介して被測定装置と測定装置を接続した状態で実行される所定の試験の精度を高める。

【解決手段】コンピュータが、仲介部材を介して測定装置に接続された被測定装置の合否を判定する工程を有する半導体装置の製造方法であって、前記仲介部材の抵抗値を算出する抵抗算出工程S10と、前記被測定装置に試験信号を入力し、その後、前記被測定装置から出力された応答信号を取得する測定工程S20と、抵抗算出工程S10で算出された抵抗値を利用して、測定工程S20で取得された応答信号を補正後、補正後の応答信号と、予め定められた規格値との比較結果に基づいて、当該被測定装置の合否を判定する判定工程S30と、を有する半導体装置の製造方法。

(もっと読む)

補償装置および試験装置

【課題】消費電力を抑制する。

【解決手段】電源装置から印加された電源電圧により動作する対象回路の消費電流を補償する補償装置であって、電源装置から対象回路へと電源電圧を供給するための電源配線に接続され、電源配線に流れる電流を消費する電流消費部と、電流消費部に印加される電源電圧に応じて電流消費部により消費される電流を変化させる電流制御部と、電流消費部の基準電流量を変更する設定部と、を備え、設定部は、対象回路がスタンバイ状態において、基準電流量を低減する補償装置を提供する。

(もっと読む)

テストパターン生成装置,テストパターン生成方法およびテストパターン生成プログラム

【課題】並列処理に起因するテストパターンの増加を抑止する。

【解決手段】第2の演算処理装置20は、複数の第1の演算処理装置10が要求値の設定対象となる同じ回路素子に対してそれぞれ異なる要求値を設定するコンフリクトが発生するか否かを要求値バッファ22aに格納された要求値に基づいて判定する。そして、第1の演算処理装置10が要求値の設定対象となる入力点に設定しようとする要求値が、他の第1の演算処理装置10が当該入力点に設定する要求値と異なるコンフリクトが発生すると、第2の演算処理装置20が判定した場合、当該第1の演算処理装置10は当該要求値の設定を抑止する。

(もっと読む)

電子デバイスにおけるパケットエラー率の決定論的試験のためのシステム及び方法

【課題】電子機器におけるパケットエラー率を試験する方法及びシステムを提供する。

【解決手段】試験器104からDUT102に一連のデータパケット201を送信し、事前定義される受信エラーフリーデータパケットの数を設定し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しいか評価し、一連のデータパケット201からDUT102でエラーなしに受信されたデータパケット201の数が事前定義される受信エラーフリーデータパケットの数と等しくないとき正常動作のDUT102でゼロの受信パケットエラーを生成することが既知の電力レベルで試験器104からDUT102に追加データパケットを送信して、電子機器におけるパケットエラー率を試験する。

(もっと読む)

1 - 20 / 1,860

[ Back to top ]