Fターム[2G132AH00]の内容

電子回路の試験 (32,879) | 信号の検出に関するもの (705)

Fターム[2G132AH00]の下位に属するFターム

Fターム[2G132AH00]に分類される特許

1 - 20 / 84

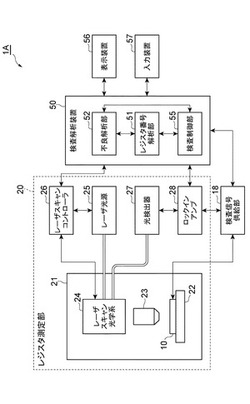

基板検査装置および基板検査方法

スキャンチェーン検査装置及び検査方法

【課題】 スキャンチェーンの検査を好適に行うことが可能なスキャンチェーン検査装置及び検査方法を提供する。

【解決手段】 半導体装置10のスキャンチェーンに検査信号を供給する検査信号供給部18と、スキャンチェーンの各レジスタでの検査信号の信号レベルの時間変化を測定するレジスタ測定部20と、測定部20による測定結果に基づいて各レジスタにレジスタ番号を付与するレジスタ番号解析部51を有する検査解析装置50とによってスキャンチェーン検査装置1Aを構成する。供給部18は、信号長nが異なるm種類の検査信号列を供給する。解析部51は、信号長nの検査信号列を用いた測定結果からスキャンチェーンの複数のレジスタをn個のグループに分けるグループ分けをm種類の検査信号列のそれぞれについて行い、その結果に基づいて各レジスタにレジスタ番号を付与する。

(もっと読む)

半導体集積回路及び半導体集積回路の設計方法

【課題】半導体集積回路の回路面積を小さくする。

【解決手段】被試験回路2の観測対象の複数の信号線TA1〜TA4上の観測点TP1〜TP4を複数の入力端子に接続し、複数の信号線TA1〜TA4を伝搬する値の、論理積、論理和、否定論理積、または否定論理和の何れかを演算し、複数の信号線TA1〜TA4の何れかを伝搬する値に応じた出力値を出力する論理回路(NOR回路3,NAND回路4)を設けることで、複数の観測点をEOR回路を用いて共用する半導体集積回路より回路面積を小さくできる。

(もっと読む)

スキャンパタン作成手法、プログラム、スキャンパタン作成装置、テスタ、及びテスト方法

【課題】スキャンテストに要する時間を削減するテストパタン作成方法を提供する。

【解決手段】テストパタン作成方法は、組み合わせ論理回路と少なくとも一つのスキャンチェーンとに関する情報を、記録媒体から読み出し、少なくとも一つのスキャンチェーンの入力側に近いフリップフロップから順番に抽出し(ステップS21)、抽出したフリップフロップがスキャンキャプチャ動作によって組み合わせ論理回路から取り込むキャプチャデータと照合する期待値の必要性を判定し(ステップS22〜S25)、期待値が不要と判定されたフリップフロップが入力側から連続して存在するフリップフロップの数を取得し(ステップS27)、スキャンチェーンに含まれるフリップフロップの総数と、取得したフリップフロップの数との差分を、スキャンキャプチャ動作後のスキャンシフト回数として決定する(ステップS28)。

(もっと読む)

半導体集積回路のテスト回路及び方法

【課題】ウェハ上の単一チップに形成された貫通ビアの不良の可否をテストすることができ、またパッケージングされた半導体集積回路に形成された貫通ビアの不良の可否をテストすることができる半導体集積回路のテスト回路及び方法を提供する。

【解決手段】半導体集積回路のテスト回路1は貫通ビア100、電圧駆動部200及び判定部300を含む。前記貫通ビア100は入力電圧V1を受信する。前記電圧駆動部200は前記貫通ビア100と連結されて前記入力電圧V1を受信し、テスト制御信号EN_P,EN_Nに応答して前記入力電圧V1のレベルを変化させてテスト電圧VTを生成する。前記判定部300は前記入力電圧V1及び前記テスト電圧VTを比較して結果信号を出力する。

(もっと読む)

マザーボード用デバッグカード

【課題】本発明の目的は、正確に挿し込んでも間違って挿し込んでも全て正常に使用できるマザーボード用デバッグカードを提供することである。

【解決手段】本発明のマザーボード用デバッグカードは、マザーボードの拡張スロットに電気的に接続されるコネクターと、前記マザーボードの故障をテストするテスティング回路と、前記コネクターと前記テスティング回路との間に接続される切り替え回路と、前記コネクター、前記切り替え回路及び前記テスティング回路に接続されて、前記コネクター及び前記拡張スロットによって、前記マザーボードの電圧を前記切り替え回路及び前記テスティング回路に提供して作動電圧とする駆動回路と、を備え、前記コネクターの接地ピンが受ける電圧が低レベルであるか又は高レベルであるかによって、前記コネクターと前記テスティング回路との間の対応するデータ伝送チャンネルを選択する。

(もっと読む)

プリント基板試験装置

【課題】システムバスに接続された複数のプリント基板の試験を確実に行なうことを目的とする。

【解決手段】バウンダリスキャンテストソフトウェアを搭載しているコンピュータと、コンピュータの指示に基づいてJTAG信号を生成するJTAGコントローラと、ボードID判定とI/O制御を行なう第1の制御回路と、第1の制御回路によって制御される第1のI/Oバッファと、第1の制御回路に接続された第1のコネクタと、ボードID判定とI/O制御を行なう第2の制御回路と、第2の制御回路によって制御される第2のI/Oバッファと、第2の制御回路に接続された第2のコネクタと、JTAGバスと、システムバスと、システムバスを流れる信号をスキャンするシステムバススキャン回路と、を備えているプリント基板試験装置。システムバスとJTAGバスとシステムバススキャン回路はバックプレーンに実装されている。

(もっと読む)

電子デバイスをテストするためのシステムの動作周波数を増加させるための装置

【課題】DUTがテストされることができる周波数を増加させる。

【解決手段】テストシステムは、テストされる電子デバイス112の入力端子208,210と接触するプローブ110d,110e内を終端とする、通信チャネル220,222を備える。抵抗が、プローブの近くの通信チャネル220,222と接地の間に接続されている。抵抗は、端子の入力抵抗を減少させ、それによって入力端子208,210の立上がりおよび立下がり時間を減少させる。分路抵抗402,404が、各分岐内に設けられており、このことが、端子の入力抵抗を減少させ、それによって入力端子208,210の立上がりおよび立下がり時間を減少させる。分路抵抗402,404はまた、チャネルを戻る信号反射を減少、最小化、または除去するようにサイズ調整されてもよい。

(もっと読む)

半導体集積回路の故障解析装置及び故障解析方法

【課題】電源電圧や電源電流の変化が微小であり、通常のOBIRCH法では解析が困難な故障を解析する半導体集積回路の故障解析装置、方法を提供する。

【解決手段】半導体集積回路の出力端子の電圧を測定する電圧測定部と、半導体集積回路の内部回路であって出力端子に接続される内部回路の状態を設定するテストパターンを半導体集積回路に与えるテストパターン発生部と、レーザービームを内部回路の所定の領域に対して走査しながら照射し、照射された部分の抵抗値を変化させるレーザー走査部と、レーザー走査部及び電圧測定部と連動し、レーザービームを照射したときに、出力端子の電圧の変化したレーザービームの照射位置を検出して表示する故障位置表示部と、を備える。

(もっと読む)

プロトタイプシステムにおける汎用的な可制御性及び可観測性のための方法及び装置

【課題】プロトタイプの試験を行うための方法及びシステムを提供することである。

【解決手段】この方法は、第1のインタフェース・コンポーネントにおいて、ユーザ設計の少なくとも一部及び関連付けられた検証モジュールを表す構成画像に関連付けられた構成パラメータと、ランタイム制御情報とを受信することを含む。この方法は、さらに、第1のインタフェース・コンポーネントを使用して、構成画像をデバイスへ送信することを含む。第2のインタフェース・コンポーネントは、第1のインタフェース・コンポーネントから受信された構成画像及びランタイム制御情報のうち少なくとも1つに基づいて、タイミング及び制御情報を検証モジュールへ送信するように構成され得る。第2のインタフェース・コンポーネントからタイミング及び制御情報を受信することに応答して、検証モジュールは、デバイスを制御し、且つ/又は、ユーザ設計の少なくとも一部のデバイス状態を監視する。

(もっと読む)

半導体試験装置

【課題】試験時間に大きな影響を与えることなく、校正により半導体試験の精度を向上させる。

【解決手段】試験対象の半導体デバイスにテスト信号を出力するための切替可能な複数の経路と、経路の切替を指示する設定命令ブロックとテスト信号出力を指示する信号出力命令ブロックとを含んだテストユニットを1または複数個備えたテストプログラムを実行する制御部と、テストプログラムのテストユニット実行中において、設定命令ブロックの実行後、信号出力命令ブロックの実行前に、設定命令ブロックで設定された経路における校正データを取得し、取得した校正データを用いて、信号出力命令ブロックに基づいて出力されるテスト信号の補正を行なう校正処理部とを備えた半導体試験装置。

(もっと読む)

半導体パッケージの検査方法及びそれに用いる検査装置

【課題】 被検体内の異なるデバイスを同時に検査可能な半導体パッケージの検査方法を提供する。

【解決手段】 テストプロセッサ112が第1制御信号および第2制御信号をそれぞれテスタ110内の第1パターン発生部114およびテストヘッド120内の第1パターン発生部124に伝送する(ST150)。第1パターン発生部114が第1パターンを第1半導体チップDに入力し(ST152)、第1判定部116が第1半導体チップDの不良可否を判断する(ST154)。一方、第2パターン発生部124が第2パターンを第2半導体チップFに入力し(ST162)、第2判定部126が第2半導体チップFの不良可否を判断する(ST164)。これにより、異なる第1半導体チップと第2半導体チップとを同時に検査できるようになり、異なる半導体チップを有する半導体パッケージを検査する時間を大幅に短縮することができる。

(もっと読む)

半導体装置、試験装置、および製造方法

【課題】電流電圧のパルス特性を向上させて電流電圧のDC特性に近づける。

【解決手段】半導体層と、半導体層上に設けられたゲート絶縁膜と、ゲート絶縁膜上に設けられたゲート電極と、ゲート絶縁膜上に設けられ、ゲート絶縁膜上におけるゲート電極の端部の少なくとも一部においてゲート電極と接するゲート境界膜と、を備え、ゲート境界膜およびゲート絶縁膜は、同種の絶縁材料を含む半導体装置を提供する。ゲート電極およびゲート境界膜上に設けられた絶縁性の保護膜を更に備え、保護膜は、ゲート境界膜およびゲート絶縁膜とは別種の絶縁材料を含んでよい。

(もっと読む)

オンチップジッタデータ取得回路、ジッタ測定装置、及びその方法

【課題】本発明は、高周波プローブを要さずにジッタ測定が可能なオンチップジッタデータ取得回路を提供することを目的とする。

【解決手段】本発明に係るオンチップジッタデータ取得回路1は、クロック信号を、遅延量選択信号で選択可能な複数の遅延量のいずれか1つの遅延量で遅延する可変遅延部10と、クロック信号の位相と、可変遅延部で遅延されたクロック信号の位相とを比較して、位相比較信号を生成する位相比較信号生成部20と、位相比較信号を所定の期間に亘り取得する位相比較信号取得部30と、を有することを特徴とする。

(もっと読む)

試験装置および調整方法

【課題】試験装置を精度良く調整する。

【解決手段】被試験デバイスを試験する試験装置であって、被試験デバイスへ試験信号を供給する供給部と、供給部から出力される信号の直流電圧を測定する測定部と、供給部から予め定められた周期信号を出力させた場合における測定部に測定される周期信号電圧に基づき、立上りエッジを出力する場合の供給部の出力時間と立下りエッジを出力する場合の供給部の出力時間との時間差である出力時間差を算出する第1算出部と、を備える試験装置を提供する。

(もっと読む)

波形発生装置および波形発生装置の配線遅延校正方法

【課題】ピン回路を並列に接続してピンマルチ構成とした場合にも、伝送路間のインピーダンス不整合を生じさせることなくTDR波形を取得し、配線遅延校正を行うことの可能な波形発生装置および波形発生装置の配線遅延校正方法を実現する。

【解決手段】ドライバ21の出力部における信号波形を取得するパーピンTDR手段71と、校正部9を有し、ドライバ21のそれぞれは、校正部9の指令に基づき、第二の伝送路81の一端に同時に到達するように信号を出力し、パーピンTDR手段71は、ドライバのそれぞれの出力端において、信号が出力されてから前記第二の伝送路の他端で反射して戻るまでの波形であるTDR波形を取得し、校正部9は、TDR波形の形状に基づいて第一の伝送路41、42と前記第二の伝送路81の配線遅延の和を求める。

(もっと読む)

複合的に時間測定を行う方法および装置

【課題】被試験デバイスの複数の異なる信号間での時間測定を効率よく行う試験装置を提供する。

【解決手段】自動試験装置は、複数のシステムモジュールを備える。各システムモジュールは、一の時間測定部を備える。時間測定部に備えられたグローバル・タイム・スタンプ・モジュールは、複数のグローバル・タイム・スタンプ・コアを備え、該コアはそれぞれ、少なくとも2つの情報を受信する情報受信部と、コア入力においてイベントを受信するイベント受信部と、コア入力で受信されるイベントから対象イベントを決定するイベント決定部と、対象イベントが決定されると、クロック情報に対応するタイム・スタンプ・カウンタの現在のステータスを記録するようにタイム・スタンプ・メモリに指示する指示部とを備える。グローバル・タイム・スタンプ・モジュールはさらに、複数のグローバル・タイム・スタンプ・コアに共通時間基準を供給する供給部を備える。

(もっと読む)

半導体試験装置

【課題】ユーザの使い勝手を向上することが可能な半導体試験装置を実現する。

【解決手段】異なる速度の低速レート信号と高速レート信号を用いて被試験対象デバイスの試験を行う半導体試験装置において、高速レート信号のレート長が設定されるレート長設定レジスタと、パターンプログラムに設定されている高速レート番号の組み合わせを抽出し、この組み合わせの中の1つの高速レート番号を調整レート番号に置き換え、低速レート信号のレート長の時間分解能に基づいて調整レート番号のレート長を算出して調整レート番号のレート長設定レジスタに設定する演算制御部とを備える。

(もっと読む)

半導体試験装置

【課題】ピンの有効利用形態をとる場合でも、クロストークの少ない良好な試験が可能な、汎用性の高い半導体試験装置を実現する。

【解決手段】被測定デバイス(DUT)への信号印加及び前記DUTから発生される信号の計測を実行するピンエレクトロニクスカードと、前記DUTのピン端子に接触するデバイスボードまたはプローブカードと、前記ピンエレクトロニクスカードの測定ピンを前記DUTの所望のピン端子に対応させるための配線変換部と、この配線変換部と前記デバイスボードまたはプローブカードとをコネクタ接続する勘合部とを具備する半導体試験装置において、

前記ピンエレクトロニクスカードの測定ピンから前記DUTのピン端子との間に、帯域制限回路を挿入した。

(もっと読む)

試験装置

【課題】高速多値信号を試験可能な試験装置を提供する。

【解決手段】試験装置2は、DUT1から出力される被試験信号S1であって、その値に応じて電圧レベルが変化する被試験信号S1を試験する。パターン発生器PGは、I/O端子PIOに入力される被試験信号S1の期待値を示す期待値データEXPを発生する。しきい値電圧発生器10は、期待値データEXPを受け、当該期待値データEXPに応じた電圧レベルを有するしきい値電圧Vthを、被試験信号S1と同期して生成する。比較部12は、被試験信号S1の電圧レベルVDUTをそれと対応するしきい値電圧Vthと比較する。電圧変調器11は、しきい値電圧Vthを、所定の電圧範囲で変化させる。

(もっと読む)

1 - 20 / 84

[ Back to top ]