Fターム[4M104BB00]の内容

半導体の電極 (138,591) | 電極材料 (41,517)

Fターム[4M104BB00]の下位に属するFターム

Si (2,965)

Al (2,955)

遷移金属 (20,763)

遷移金属のシリサイド (5,826)

高融点金属窒化物 (3,639)

高融点金属炭化物 (257)

高融点金属ホウ化物 (40)

上記以外の電極材料 (2,536)

結晶性(上層部を含む) (284)

組成比(上層部を含む) (553)

不純物を含むもの(上層部を含む) (1,693)

Fターム[4M104BB00]に分類される特許

1 - 6 / 6

グラフェンと金属電極との電気的接合デバイス、それを用いた電子デバイス,電子集積回路及び光/電子集積回路

【課題】グラフェンと金属電極との間の接触抵抗を低減する。

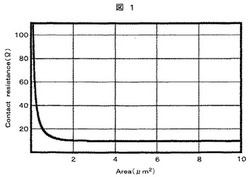

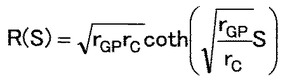

【解決手段】グラフェンの単位面積あたりの電気抵抗をrGP[Ω/μm2]、グラフェンと金属電極との単位面積当たりの界面抵抗をrC[Ωμm2]とすると、接触面積をSとして、接触抵抗は

と計算できる。rGPを10Ω/μm2、rCを10Ωμm2とした場合の計算結果を示し、接触面積を

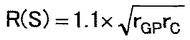

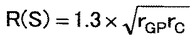

にすることにより、接触抵抗を収束値の10%増し、あるいは30%増しの値にまで、低減することができる。

(もっと読む)

導電性薄膜の形成方法

【課題】 簡単かつ短時間に基材面に金属ナノ粒子からなる安定した導電性薄膜を形成できる導電性薄膜の形成方法を提供する。

【解決手段】 金属ナノ粒子含有インクを基板上に塗布して薄膜を形成する工程と、当該薄膜に還元剤を作用させて還元処理を施す工程とを含むことを特徴とする導電性薄膜の形成方法。前記金属ナノ粒子含有インクは、炭素数10〜20の直鎖または分岐したアルキル基を有する保護剤で被覆された金属ナノ粒子を非水分散媒中に分散させたものを含有するのが好ましい。また、前記還元剤は、濃度0.005〜0.5mol/lの水溶液の状態で用い、還元処理は40〜70℃の温度条件下に行なうのが好ましい。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス型薄膜トランジスタアレイ、及びアクティブマトリクス駆動表示装置

【課題】オン電流が大きな薄膜トランジスタを安価な印刷プロセスにより提供する。

【解決手段】薄膜トランジスタ1は、絶縁基板2、ゲート電極3、ゲート絶縁膜4、下層の半導体層5、ソース電極6、ドレイン電極7、上層の半導体層8からなっている。特に特徴的な構造として、半導体層が2層構成であり、下層の半導体層5とソース電極6及びドレイン電極7と上層の半導体層8が順次積層された構造をしている。

(もっと読む)

半導体装置

【課題】 ソース領域とコンタクトプラグとの接触面積を増大させることのできる半導体装置を提供すること。

【解決手段】 エピタキシャル層3にゲートトレンチ6を形成し、その側方にボディ領域5を形成する。また、エピタキシャル層3において、ゲートトレンチ6と間隔を空けた位置にコンタクトトレンチ11を形成する。エピタキシャル層3において、その表面31およびコンタクトトレンチ11の側面12に沿うソース領域9を形成する。また、表面がコンタクトトレンチ11の底面13の一部を提供するようにボディコンタクト領域10を形成する。ゲートトレンチ6には、ゲート絶縁膜7を介してゲート電極8を埋設する。そして、コンタクトトレンチ11の内面とエピタキシャル層3の表面31とに跨るように、コンタクトプラグ17を形成し、上記各面におけるソース領域9にコンタクトさせる。

(もっと読む)

配線パターンとこれを用いた電子素子、有機半導体素子、積層配線パターンおよび積層配線基板

【課題】導電パターンの角部の盛り上がりが少なく、絶縁層を介して積層配線構造とした場合でも絶縁特性の良好な配線パターンと、これを用いた電子素子等を提供する。

【解決手段】濡れ性変化層2に、エネルギーを付与して高表面エネルギー部3とし、その上に導電性液体により導電パターン5を形成して配線パターン1とする。その際、導電パターンの平面視形状は角部に面取りが施された矩形の配線形状とし、その断面視形状は該角部の盛り上がりが少なく、パターン中央部となだらかに連なり全体が略平坦な形状とする。配線パターン1を用いて積層配線パターン、積層配線基板を構成する。又は濡れ性変化層2の低表面エネルギー部に接して半導体層を設け、電子素子、有機半導体素子を構成する。

(もっと読む)

半導体基板上にて集積回路を形成するための方法

【課題】配線に使われる多結晶シリコン層を形成する際に、アモルファスシリコン層が相変化して基板が変形する。この変形を、相変化時の機械的ストレスの発生を回避することにより軽減する方法を提供する。

【解決手段】基板1上のキャパシタ電極、ゲート電極などの導電層2の上に中間層としてアモルファス状の抗ストレス層3を設け、その上にアモルファスシリコン層4を形成する。この後、シリコン層の結晶化温度に加熱し、アモルファスシリコン層を相変化させ多結晶シリコン層にする。抗ストレス層の存在により結晶化時の機械的ストレスの発生が回避される。抗ストレス層は、別の加熱により相変化させ低抵抗化し、導電層と多結晶シリコン層は電気的に接続される。

(もっと読む)

1 - 6 / 6

[ Back to top ]