Fターム[4M104DD33]の内容

半導体の電極 (138,591) | 製造方法(特徴のあるもの) (30,582) | 電極材料の析出 (10,624) | PVD (4,537)

Fターム[4M104DD33]の下位に属するFターム

Fターム[4M104DD33]に分類される特許

1 - 20 / 227

配線の製造方法、およびこれを用いた立体的な配線を有する回路形成体の製造方法

半導体装置の作製方法

【課題】酸化物半導体を用いた半導体装置に安定した電気的特性を付与し、高信頼性化す

ることを目的の一とする。

【解決手段】第1の絶縁膜を形成し、第1の絶縁膜上に、ソース電極およびドレイン電極

、ならびに、ソース電極およびドレイン電極と電気的に接続する酸化物半導体膜を形成し

、酸化物半導体膜に熱処理を行って、酸化物半導体膜中の水素原子を除去し、水素原子が

除去された酸化物半導体膜に酸素ドープ処理を行って、酸化物半導体膜中に酸素原子を供

給し、酸素原子が供給された酸化物半導体膜上に、第2の絶縁膜を形成し、第2の絶縁膜

上の酸化物半導体膜と重畳する領域にゲート電極を形成する半導体装置の作製方法である

。

(もっと読む)

半導体装置および半導体装置の作製方法

【課題】酸化物半導体膜と金属膜との接触抵抗を低減させ、オン特性の優れた酸化物半導体膜を用いたトランジスタを提供する。

【解決手段】絶縁表面上の一対の電極と、一対の電極と接して設けられる酸化物半導体膜と、酸化物半導体膜上のゲート絶縁膜と、ゲート絶縁膜を介して酸化物半導体膜と重畳するゲート電極と、を有し、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含む半導体装置とする。さらに、一対の電極において、酸化物半導体膜と接する領域にハロゲン元素を含ませる方法として、フッ素を含む雰囲気におけるプラズマ処理を用いることができる。

(もっと読む)

ポリメタルゲート電極を持つ半導体素子の製造方法

【課題】TiN膜及びバッファ層から形成されるバリアー膜を備えるポリメタルゲート電極を持つ半導体素子及びその製造方法を提供する。

【解決手段】半導体基板上に形成されたゲート絶縁膜と、ゲート絶縁膜上に半導体基板側から順に積層された導電性ポリシリコン膜、第1金属シリサイド膜、バリアー膜、及び金属膜から形成されるポリメタルゲート電極と、を備える半導体素子である。バリアー膜は、第1金属シリサイド膜上に形成されるTiN膜と、TiN膜と金属膜との間に介在されるバッファ層と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】個別の工程で形成されることで分離して配置された電極どうしを断線することなく接続できる半導体装置及びその製造方法を提供する。

【解決手段】半導体基板の主面に第1の絶縁膜を介して形成された第1の電極と、半導体基板の主面に第2の絶縁膜を介して形成された第2の電極との間に補償膜を埋設する。第1の電極及び第2の電極上には、第1の電極の上面及び第2の電極の上面と接触する、第1の電極の上面から補償膜の上面を経由して第2の電極の上面まで到達する配線を形成する。

(もっと読む)

炭化珪素半導体装置の製造方法

【課題】配線を形成したときに電極と配線との密着性を向上できる炭化珪素半導体装置の製造方法を提供する。

【解決手段】第1の面と、第1の面と反対の第2の面とを有する炭化珪素半導体層110が準備される。炭化珪素半導体層110の第2の面を部分的に覆う金属層と、炭化珪素半導体層110の第2の面を部分的に覆う熱酸化膜130とが形成される。金属層を熱処理することにより電極150が形成される。金属層を形成する工程は、金属層を熱処理する温度において炭素よりもシリコンとの反応性が高い材料を用いて行われる。電極150を形成する工程において電極150の表面上に炭素が偏析する。電極150の表面および熱酸化膜130の表面の両方において、炭素を除去可能なエッチングが行われる。

(もっと読む)

トップエミット型窒化物系発光素子

【課題】 優れた電気的特性を有するトップエミット型窒化物系発光素子を提供する。

【解決手段】 本発明は、トップエミット型窒化物系発光素子に関し、窒化物系発光素子は、n型クラッド層、活性層及びp型クラッド層が順次に積層されており、p型クラッド層上に形成された導電性ナノ相酸化物粒子と、p型クラッド層及び導電性ナノ相酸化物粒子層上に形成された透明導電性薄膜層と、を備え、透明導電性薄膜層は透明導電性素材で形成され、導電性ナノ相酸化物粒子は界面改質層が熱処理によってナノ相酸化物に分解されることにより形成される。このようなトップエミット型窒化物系発光素子によれば、p型クラッド層とのオーミック接触特性が改善され、発光素子のパッケージングの際に、ワイヤーボンディング効率及び収率を高めることができ、低い非接触抵抗及び優れた電流−電圧特性により素子の発光効率及び素子寿命を向上することができる。

(もっと読む)

窒化物系発光素子及びその製造方法

【課題】窒化物系発光素子及びその製造方法を提供する。

【解決手段】窒素物系発光素子は、基板110、n型クラッド層130、活性層140、

p型クラッド層150、格子セル層160及びオーミック接触層が順次に積層された構造

よりなっている。また格子セル層160は導電性を有する素材で30μm以下の大きさを

有する粒子型セルがオーミック接触層内に埋め込まれて、相互離隔されて形成されている

発光素子である。このような窒素物系発光素子とその製造方法は、p型クラッド層とのオ

ーミック接触特性が改善されているため発光効率及び素子寿命を向上させ、かつウェーハ

成長後の活性化工程を省略できて、製造工程を単純化させうる。

(もっと読む)

半導体装置

【課題】異なる特性の半導体素子を一体に有しつつ、高集積化が実現可能な、新たな構成の半導体装置を提供することを目的の一とする。

【解決手段】第1の半導体材料が用いられた第1のチャネル形成領域と、第1のゲート電極と、を含む第1のトランジスタと、第1のゲート電極と一体に設けられた第2のソース電極および第2のドレイン電極の一方と、第2の半導体材料が用いられ、第2のソース電極および第2のドレイン電極と電気的に接続された第2のチャネル形成領域と、を含む第2のトランジスタと、を備えた半導体装置である。

(もっと読む)

半導体装置及びその製造方法

【課題】higher-k材料であるチタン酸化膜の半導体基板との界面を安定化でき、さらなる微細化に対応できるゲート構造を実現できるようにする。

【解決手段】半導体装置は、半導体基板1の上に形成されたゲート絶縁膜と、該ゲート絶縁膜の上に形成されたゲート電極とを備えている。ゲート絶縁膜は、アナターゼ型酸化チタンを主成分とする高誘電率絶縁膜5であり、ゲート電極は、第1の金属膜6又は第2の金属膜8を含む導電膜から構成されている。

(もっと読む)

電極被覆材料、電極構造体、及び、半導体装置

【課題】低いコンタクト抵抗、高い移動度を達成し得る半導体装置を提供する。

【解決手段】ゲート電極13、ゲート絶縁層14、有機半導体材料層から構成されたチャネル形成領域16、及び、金属から成るソース/ドレイン電極15を有する電界効果型トランジスタから成る半導体装置において、チャネル形成領域16を構成する有機半導体材料層と接するソース/ドレイン電極15の部分は、電極被覆材料21で被覆されており、電極被覆材料21は、金属イオンと結合し得る官能基、及び、金属から成るソース/ドレイン電極15と結合する官能基を有する有機分子から成る。

(もっと読む)

半導体装置

【課題】良好な特性を維持しつつ、微細化を達成した、酸化物半導体を用いた半導体装置を提供することを目的の一とする。

【解決手段】酸化物半導体層と、酸化物半導体層と接するソース電極及びドレイン電極と、酸化物半導体層と重なるゲート電極と、酸化物半導体層とゲート電極との間に設けられたゲート絶縁層と、酸化物半導体層に接して設けられた絶縁層と、を有し、酸化物半導体層は、該酸化物半導体層の端面において、ソース電極またはドレイン電極と接し、且つ該酸化物半導体層の上面において、絶縁層を介して、ソース電極またはドレイン電極と重なる半導体装置である。

(もっと読む)

半導体装置

【課題】新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】直列に接続されたメモリセルと、メモリセルを選択して第2信号線及びワード線を駆動する駆動回路と、書き込み電位のいずれかを選択して第1信号線に出力する駆動回路と、ビット線の電位と参照電位とを比較する読み出し回路と、書き込み電位及び参照電位を生成して駆動回路および読み出し回路に供給する、電位生成回路と、を有し、メモリセルの一は、ビット線及びソース線に接続された第1のトランジスタと、第1、第2の信号線に接続された第2のトランジスタと、ワード線、ビット線及びソース線に接続された第3のトランジスタを有し、第2のトランジスタは酸化物半導体層を含み、第1のトランジスタのゲート電極と、第2のトランジスタのソース電極またはドレイン電極の一方が接続された、多値型の半導体装置。

(もっと読む)

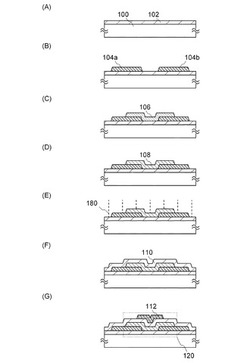

半導体装置の作製方法

【課題】信頼性の高い半導体装置及び、信頼性の高い半導体装置の作製方法を提供する。また、消費電力が低い半導体装置及び消費電力が低い半導体装置の作製方法を提供する。また、量産性の高い半導体装置及び量産性の高い半導体装置の作製方法を提供する。

【解決手段】酸素欠損を生じることなく酸化物半導体層に残留する不純物を除去し、酸化物半導体層を極めて高い純度にまで精製して使用すればよい。具体的には、酸化物半導体層に酸素を添加した後に加熱処理を施し、不純物を除去して使用すればよい。特に酸素の添加方法としては、高エネルギーの酸素をイオン注入法またはイオンドーピング法などを用いて添加する方法が好ましい。

(もっと読む)

半導体装置

【課題】電力が供給されない状況でも記憶内容の保持が可能で、かつ、書き込み回数にも制限が無い、新たな構造の半導体装置を提供することを目的の一とする。

【解決手段】第1のトランジスタ上に設けられた第2のトランジスタと容量素子とを有し、第2のトランジスタの半導体層にはオフセット領域が設けられた半導体装置を提供する。第2のトランジスタを、オフセット領域を有する構造とすることで、第2のトランジスタのオフ電流を低減させることができ、長期に記憶を保持可能な半導体装置を提供することができる。

(もっと読む)

半導体装置とその製造方法

【課題】 単純で容易な実装手段によりMOSFETの閾値電圧を制御することが可能な半導体装置とその製造方法を提供する。

【解決手段】 一実施形態によれば、電界効果トランジスタは、STI(浅いトレンチ分離)を含んでいる半導体基板402と、p−FET401及びn−FET403と、p−FET401が形成される基板の窪み内のシリコン・ゲルマニウム層800と、n−FET部上とシリコン・ゲルマニウム層上に設けられた、ハフニウム化合物とレアアース化合物を含むゲート誘電体414, 432と、ゲート誘電体414, 432上にそれぞれ配置された互いに同じ材料を含むゲート電極416, 434とを具備している。

(もっと読む)

半導体装置の製造方法

【課題】高温化下でも安定な高信頼性を有する配線を容易に精度良く形成する方法を提供する。

【解決手段】本発明の実施形態にかかる半導体装置の製造方法は、半導体基板上方に窒化チタンからなる第1の絶縁層を形成し、第1の絶縁層に複数の溝を形成し、溝の底面及び側壁下部を覆う部分が溝の側壁上部を覆う部分よりも厚くなるように、溝の底面及び側壁を覆うバリアメタルを形成し、溝のバリアメタル上に金属膜を埋め込み、複数の配線を形成し、第1の絶縁層を除去して、隣り合う複数の配線の間に配線に接するような空隙を形成し、複数の配線の上面に、金属又は酸化物からなるキャップ膜を形成し、複数の配線の上面及び側壁を覆うようにシリコンナイトライドカーバイド膜又は窒化ボロン膜からなる拡散防止膜を形成し、複数の配線の上面を覆い、且つ、複数の配線間に空隙が形成されるように、第2の絶縁層を形成する。

(もっと読む)

高有効仕事関数で電極を堆積する方法

【課題】半導体処理の方法が提供される。

【解決手段】いくつかの実施形態によれば、高い有効仕事関数を有する電極が形成される。この電極は、トランジスタのゲート電極であってもよく、導電材料の第1の層を堆積し、第1の層を水素含有ガスに露出し、第1の層に導電材料の第2の層を堆積することにより、high−kゲート誘電体に形成されてもよい。第1の層は、基板がプラズマ又はプラズマ発生ラジカルに露出されないプラズマ無しプロセス(non−plasma process)を用いて堆積される。第1の層が露出される水素含有ガスは、励起された水素種を含んでもよく、これは水素含有プラズマの一つであってもよく、水素含有ラジカルであってもよい。第2の層を堆積する前に、第1の層もまた、酸素に露出されてもよい。ゲートスタックのゲート電極の仕事関数は、いくつかの実施形態において約5eV又はそれ以上であってもよい。

(もっと読む)

半導体装置の製造方法

【課題】電解めっき法によるCu膜の確実に析出させる。

【解決手段】抑制剤と促進剤を添加しためっき液とシリコン基板の相対速度が100m/分以上になる速度でシリコン基板を回転させながら、シリコン基板をめっき槽に浸漬させる。抑制剤の分子がシード層の表面に吸着し、シード溶解が抑制される。導電膜を成長させるときは、シリコン基板とめっき液の相対速度が30m/分以下になる速度でシリコン基板を回転させながら、シリコン基板とアノード電極の間に通電する。ボトムアップ成長が促進され、配線溝内での空孔の形成が防止される。

(もっと読む)

半導体素子および電子機器

【課題】有機半導体層の上面の層の形状不良を抑えることが可能な半導体素子およびこれを備えた電子機器を提供する。

【解決手段】有機半導体層と、有機半導体層の上面に設けられた層とを有し、この層の外形線は、有機半導体層の外形線よりも内側にある半導体素子。この半導体素子を備えた電子機器。

(もっと読む)

1 - 20 / 227

[ Back to top ]