Fターム[4M104HH00]の内容

半導体の電極 (138,591) | 目的 (7,416)

Fターム[4M104HH00]の下位に属するFターム

エレクトロマイグレーション防止 (153)

ストレスマイグレーション防止 (50)

表面ヒロック防止 (133)

基板領域への突き抜け防止 (165)

電極層間の相互拡散防止(突抜け防止を含む) (265)

チャンネリング防止 (4)

基板、又は電極層間の密着性改善 (419)

絶縁膜との密着性改善 (215)

基板内不純物濃度分布の変化防止 (29)

電極下面(絶縁膜を含む)の照射損傷防止 (27)

平坦性の改善 (219)

段差被覆の改善 (385)

微細加工性向上 (783)

オーミック性向上 (948)

電極バルク、シート抵抗の低減 (810)

ショットキーバリアハイトの調整 (49)

周辺効果の緩和 (144)

シールド (17)

その他 (2,580)

Fターム[4M104HH00]に分類される特許

1 - 20 / 21

窒化物半導体素子及びその製造方法

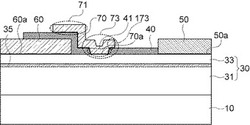

【課題】オン抵抗を低め、高電流で動作する半導体素子及び製造方法を提供する。

【解決手段】基板10上部に配設され、内部に2次元電子ガスチャネルを形成する窒化物半導体層30と、窒化物半導体層30にオーミック接合されたドレイン電極50と、ドレイン電極50と離間して配設され、窒化物半導体層30にショットキー接合されたソース電極60と、ドレイン電極50とソース電極60との間の窒化物半導体層30上及びソース電極60の少なくとも一部上にかけて形成され、ドレイン電極50とソース電極60との間にリセスを形成する誘電層40と、ドレイン電極50と離間して誘電層40上及びリセスに配設され、一部が誘電層40を挟んでソース電極60のドレイン方向へのエッジ部分上部に形成されたゲート電極70とを含む。

(もっと読む)

半導体装置

【課題】半導体装置内に保護ダイオードをレイアウトする。

【解決手段】半導体装置は、電界効果トランジスタ11と、電界効果トランジスタ11の形成領域30に隣接するダイオード形成領域12とを備え、ダイオード形成領域12はトランジスタの形成領域30と半導体基板上で絶縁され、ダイオード形成領域12内において、電界効果トランジスタ11のゲート電極1がバス配線7を介して半導体基板とショットキー接合とオーミック接合のいずれか又は両方の接合をする第1のダイオード電極20と、電界効果トランジスタ11のソース電極2がパッド5を介して半導体基板とオーミック接合とショットキー接合のいずれか又は両方の接合をする第2のダイオード電極21とを備えることによってゲート電極1とソース電極2間にダイオードが形成されたことを特徴とする。

(もっと読む)

半導体装置

【課題】nチャネル型電界効果トランジスタとpチャネル型電界効果トランジスタを有する半導体装置において、nチャネル型電界効果トランジスタ、pチャネル型電界効果トランジスタ共にドレイン電流特性に優れた半導体装置を実現する。

【解決手段】nチャネル型電界効果トランジスタ10と、pチャネル型電界効果トランジスタ30とを有する半導体装置において、nチャネル型電界効果トランジスタ10のゲート電極15を覆う応力制御膜19には、膜応力が引張応力側の膜を用いる。pチャネル型電界効果トランジスタ30のゲート電極35を覆う応力制御膜39には、膜応力が、nチャネル型トランジスタ10の応力制御膜19より、圧縮応力側の膜を用いることにより、nチャネル型、pチャネル型トランジスタの両方のドレイン電流の向上が期待できる。このため、全体としての特性を向上させることができる。

(もっと読む)

薄膜トランジスタ、アクティブマトリクス基板、およびそれらの製造方法

【課題】材料の選択幅が広く、生産性が高いTFT、アクティブマトリクス基板、およびそれらの製造方法を提供すること。

【解決手段】本発明にかかる薄膜トランジスタは、ゲート電極2と、半導体層5と、半導体層5の上に設けられ、半導体層5と電気的に接続されたソース電極7、及びドレイン電極8と、を備えた薄膜トランジスタであって、半導体層5が、透光性半導体膜5aと、透光性半導体膜5a上に配置され、透光性半導体膜5aよりも光透過率の低いオーミック導電膜5bと、を有し、オーミック導電膜5bが、透光性半導体膜5aからはみ出さないように形成され、オーミック導電膜5bが、ソース電極7とドレイン電極8の間のチャネル部9を挟むように分離して形成され、ソース電極7、及びドレイン電極8が、オーミック導電膜bを介して、透光性半導体膜5aに接続されているものである。

(もっと読む)

半導体装置及びその製造方法

【課題】工数を大幅に増加せず且つ高誘電体からなるゲート絶縁膜にダメージを与えることがない、仕事関数変更用金属不純物膜の効果を有する半導体装置を実現できるようにする。

【解決手段】半導体装置は、半導体基板101と、半導体基板101の上部に形成されたp型活性領域110と、p型活性領域110の上に形成されたゲート絶縁膜150と、ゲート絶縁膜150の上に形成されたゲート電極106とを有している。ゲート絶縁膜150は、二酸化シリコンよりも大きい誘電率を有する高誘電体膜103と、高誘電体膜103の上に形成され、炭素を含む炭素含有膜104とを有している。高誘電体膜103及び炭素含有膜104は、第1の金属としてランタン又はマグネシウムを含み、ゲート電極106は、第2の金属を含む。

(もっと読む)

半導体装置及びその製造方法

【課題】低いチャネル抵抗を具現し、電界効果移動度が高くなる効果がある二重ゲートトランジスタを含む半導体装置及びその製造方法を提供する。

【解決手段】本発明による半導体装置は、下部ゲート電極と、前記下部ゲート電極上の上部ゲート電極と、前記下部ゲート電極と前記上部ゲート電極の間に介在され、前記下部ゲート電極と前記上部ゲート電極を連結するコンタクトプラグと、前記上部ゲート電極と同一の高さに前記上部ゲート電極から離隔して形成された機能電極と、を含む。本発明によれば、電界効果移動度が高い二重ゲートトランジスタを半導体装置に適用させることによって、半導体装置の特性を改善することができる。特に、本発明によれば、別途のマスク工程や蒸着工程を追加する必要がないので、工程コストの上昇や収率減少をもたらすことなく、大面積・高画質の半導体装置を大量生産することができる。

(もっと読む)

半導体装置の製造方法、及び半導体装置

【課題】ゲート電極が金属窒化膜により構成されるMOSFETにおいて、電流駆動能力の向上を図る。

【解決手段】基板10に、素子形成領域20を分離する素子分離領域50を設ける。次に素子形成領域20上にゲート絶縁膜100を形成する。その後ゲート絶縁膜100上に金属窒化膜により構成される下部ゲート電極膜200を形成する。さらに下部ゲート電極膜200を熱処理する。そして下部ゲート電極膜200上に上部ゲート電極膜220を形成する。

(もっと読む)

半導体装置の製造装置

【課題】装置の高いスループットを維持しつつ、バリアメタルの酸化工程の追加や異なる種類のシード層の積層、バリア層の積層等を行い配線の信頼性を向上させる。

【解決手段】薄膜の合金シード層を成長させるチャンバー、または、薄膜のバリアメタルを成長させるチャンバーのうち、最も短いタクト時間のチャンバー数を最も少なくして、あるいは、統一して1台の装置で専用に用い、タクト時間の長い工程のチャンバーを2または、3チャンバー以上にすることにより、薄膜工程のチャンバー間バラツキを無くして、装置のスループットを向上させる。

(もっと読む)

集積回路チップ上の電気めっき相互接続構造

【解決課題】集積回路用のサブミクロン相互接続構造を製作する方法を提供する。

【解決手段】添加剤を含み、平坦で光沢があり延性があり低応力のCu金属を付着させるのに通常用いられる浴からCuを電気めっきすることによって、ボイドのないシームレスな導体が得られる。ボイドまたはシームを残すことなくフィーチャを超充填できるこの方法の能力は独特であり、他の付着方法より優れている。この方法で電気めっきされたCuを利用する構造のエレクトロマイグレーションの抵抗は、AlCu構造または電気めっき以外の方法で付着されたCuを用いて製作された構造のエレクトロマイグレーションの抵抗より優れている。

(もっと読む)

半導体装置

【課題】 電極間絶縁膜のリーク電流や絶縁耐圧に関する問題を防止することが可能な半導体装置を提供する。

【解決手段】 素子形成領域11を有する半導体基板10と、素子形成領域上に形成されたトンネル絶縁膜12と、トンネル絶縁膜上に形成された浮遊ゲート電極18と、素子形成領域の側面、トンネル絶縁膜の側面及び浮遊ゲート電極の下部分の側面を覆う素子分離絶縁膜16と、浮遊ゲート電極の上部分の上面及び側面を覆う電極間絶縁膜20と、電極間絶縁膜上に形成された制御ゲート電極とを備え、浮遊ゲート電極の上部分の上面及び側面に平行な方向から見て、浮遊ゲート電極の上コーナー部は丸められている。

(もっと読む)

半導体装置およびその製造方法

【課題】パラジウムシリサイドからなるフルシリサイドゲート電極を有し、ソース/ドレイン領域上にシリサイド層を備えた半導体装置を提供する。

【解決手段】半導体基板と、半導体基板の上に、ゲート絶縁膜を介して設けられたパラジウムシリサイドのゲート電極と、ゲート電極の両側の半導体基板に形成されたソース/ドレイン領域とを含むMOS構造の半導体装置において、ゲート電極にホウ素を不純物としてドープすることにより、ゲート電極の仕事関数を小さくなるようにシフトさせた。

(もっと読む)

基板の製造方法及び基板処理装置

【課題】工程数を増やすことなく、Mo酸化物を除去すると共にMo酸化物の基板への付着を抑制する基板の製造方法を提供する。

【解決手段】本発明に係る基板の製造方法は、基板上にモリブデンを含む層を形成し、前記モリブデンを含む層が露出した状態において、前記基板に対し、少なくとも窒素ガスを用いた大気圧プラズマ処理を行うものである。このような構成により、工程数を増やすことなく、Mo酸化物を除去すると共にMo酸化物の基板への付着を抑制する基板の製造方法を提供する。

(もっと読む)

開口不良の評価方法及び半導体装置の製造方法

【課題】 製品不良の原因となる開口不良を感度よく検出することが可能な、開口不良の評価方法及び半導体装置の製造方法を提供する。

【解決手段】 本発明は、半導体基板1上に設けられた第1の絶縁膜2に形成され、かつ少なくとも1つの接続孔を有する接続孔パターンの開口不良を評価する方法であって、接続孔パターンを半導体基板1に転写する転写工程と、転写工程後に第1の絶縁膜2を除去する除去工程と、転写工程にて接続孔パターンが転写された場合に、開口不良がない正常接続孔3であると判定する一方、接続孔パターンが転写されない場合には、開口不良が生じた不良接続孔4である判定する判定工程とを含む。

(もっと読む)

パターンの形成方法及び液滴吐出ヘッド

【課題】 パターン形成において、低コスト化及び形成時間の短縮化を図るとともに、微細パターンの形成を可能としたパターンの形成方法を提供する。

【解決手段】 本発明のパターン形成方法は、基板18上に第1金属膜28を形成する第1金属膜形成工程と、第1金属膜28上に、パターンを形成しない基板18上の位置に対応する第1金属膜28が露出するようにマスクパターン38を形成するマスクパターン形成工程と、マスクパターン38をマスクとして第1金属膜28上に絶縁膜40を形成する絶縁膜形成工程と、マスクパターン38を除去し、メッキ法により、マスクパターン38を除去した第1金属膜28上に絶縁膜40をマスクとして少なくとも第2金属膜42を形成する第2金属膜形成工程と、を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 チャネル形成領域に異なる応力を発声させる膜を互いに積層形成した半導体装置において、当該膜のエッジ部形状に起因するボイドが形成された場合であっても、隣り合うコンタクトがショートすることがない半導体装置及びその製造方法を提供する。

【解決手段】 コンタクト開口部を形成した後に絶縁材料を堆積して、コンタクト開口部に表出したボイド開口部を塞ぐ。これにより、当該ボイドに導電性材料が侵入することを防止し、隣り合うコンタクトがショートすることを防止する。

(もっと読む)

薄膜トランジスタの製造方法

【課題】 ゲート電極及びソース・ドレイン電極を形成する工程間において、熱の印加による寸法変動を回避し、生産効率を保持したまま、簡易な工程により、安定した特性を有

する薄膜トランジスタの製造方法を提供する。

【解決手段】 本発明の薄膜トランジスタの製造方法は、ゲート絶縁膜としてのフィルムのいずれかの面にゲート電極、それと異なる面にソース・ドレイン電極を、導電性材料が有機溶媒により溶解された溶液または分散体を印刷することにより形成する薄膜トランジスタの製造方法であって、フィルムの一方の面に、いずれか一方の電極のパターン形状を前記溶液または分散体により印刷する工程と、先に印刷された電極のパターン形状の溶液または分散体を真空乾燥し、有機溶媒を揮発させて電極を形成する工程とを有する。

(もっと読む)

半導体装置およびその製造方法

【課題】 優れた特性を有するとともに信頼性が向上し、またSiCウエハを用いることができると。

【解決手段】 SiCチップ9には、複数個のショットキーバリアダイオードのユニット10が形成され、各ユニット10は独立した外部出力電極4を持っている。SiCチップ9に形成されたユニット10のうち良品ユニットの外部出力電極4のみに、バンプ11(直径が数10〜数100μm)が形成され、耐圧がなかったりリーク電流が多かったりする不良品ユニットの外部出力電極4の上にはバンプは形成されていない。不良品ユニットにはバンプが形成されていないので、ショットキーバリア側電極3は外部出力電極4からバンプ11、配線基板12の配線層13、外部リード13aへと外部と並列接続され、良品のユニット10の外部出力電極4のみが並列に接続されている。

(もっと読む)

液晶表示装置

【課題】効率よく放熱することが可能な薄膜トランジスタを備えた液晶表示装置を提供する。

【解決手段】基板上にマトリクス状に配置された複数の画素PXによって構成された表示部と、基板上の表示部の外側領域に設けられ、表示部を駆動するための駆動回路と、を備える液晶表示装置10であって、それぞれに切欠部132aを有した一対の拡散層を備えるポリシリコン半導体層132と、拡散層のそれぞれの上面及び切欠部に沿った端面に接触する第1電極136及び第2電極138と、第1電極136と第2電極138との間の電流をオンオフする電圧が加えられる第3電極134と、を備える薄膜トランジスタを具備した液晶表示装置10。

(もっと読む)

半導体内部配線

【課題】Si基板上に成膜配線して半導体素子を形成することにより銅の利点である耐EM性や耐SM性を十分に生かして高度耐腐食性の微細化配線を持つ半導体素子を製造することができる高純度単結晶銅とその製造方法、更に得られた単結晶銅からなるスパッタリングターゲットおよび同ターゲットを用いて成膜した配線を有する半導体素子を提供すること。

【解決手段】銀と硫黄の合計含有量が0.1ppm以下である純度99.9999wt%以上の高純度銅を出発原料として用い、これを電気炉1内に配置した原料るつぼ5内に入れて溶解し、るつぼ底部の溶解滴下孔4から下方の単結晶鋳型6に溶解銅を滴下する。この間上部、中部、下部ヒーター10、11、12により温度を調節し、石英外筒3内を真空排気装置2により排気する。炉底部には断熱トラップ8がありその外側に冷却水9が貫流する水冷フランジ7が配置されている。この装置の単結晶鋳型内に半導体素子の配線形成用ターゲット材として好適な高純度単結晶銅が得られる。

(もっと読む)

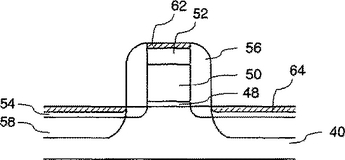

ニッケルゲルマノシリサイド化したゲートを組み込んだMOSFETおよびこれらのMOSFETを形成する方法

MOSFETのゲートまたはMOSFETのソースまたはドレイン領域は、シリコンゲルマニウムまたは多結晶シリコンゲルマニウムを含む。好ましくはニッケルシリサイドのモノシリサイドフェーズを含むニッケルゲルマノシリサイド(62、64)を形成すべく、ニッケルでのシリサイデーションを実行する。

ニッケルモノシリサイドによって呈される優れたシート抵抗を実質的に保持する一方、シリサイド中にゲルマニウムを含むことは、モノシリサイドフェーズが形成され得るより温度領域をより広くする。その結果、ニッケルゲルマノシリサイドは、後続のプロセスの間、ニッケルモノシリサイドよりも、より高い温度に耐えることができる。しかしながら、ニッケルモノシリサイドとほぼ同一のシート抵抗および他の有益な特性を提供する。  (もっと読む)

(もっと読む)

1 - 20 / 21

[ Back to top ]