Fターム[5E338CC06]の内容

Fターム[5E338CC06]に分類される特許

1 - 20 / 1,016

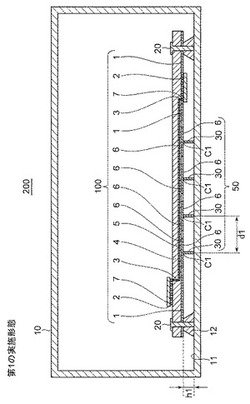

基板取り付け装置、基板取り付け方法及び電子機器

【課題】電子機器の筐体に多層基板を容易かつ安価に取り付けて、電磁バンドギャップ構造体を設ける。

【解決手段】多層基板100は、多層基板100の下面に形成された接地導体1と、配線導体5と、多層基板100の下面の各位置であって配線導体5に対向する各位置に所定の間隔d1で形成された複数のパッチ導体6とを備える。基板取り付け装置50は、パッチ導体6と、各パッチ導体6を電子機器200の筐体10にそれぞれ電気的に接続する複数の導電性の足部30を備える。

(もっと読む)

多層基板

【課題】高性能な高周波伝送特性を実現したうえで、ビルドアップ接続の簡単化を図ることができる。

【解決手段】第1及び第2の誘電体層10,11の層面側の中心位置の周囲に所定位置ずらして放射状に配置した4個のビルドアップ接続部18を設けた接続用導体パターン17を有する高周波線路16を形成して、この第1及び第2の誘電体層10,11間に該第1及び第2の誘電体層10,11のビルドアップ接続部18がビルドアップ接続される4個のビルドアップ接続部18を所定角度ずらせて放射状に配置した接続用導体パターン17を有した第1乃至第3の中間誘電体層12〜14を積層配置してビルドアップ接続するように構成したものである。

(もっと読む)

多層配線基板、AV機器およびテレビジョン受像機

【課題】より確実に静電気から保護されている安価な多層配線基板を提供すること。

【解決手段】本発明の多層配線基板は、スルーホール、導電体層、半田材料の凸部および半田材料の被覆部を用いて静電気対策がなされている。

(もっと読む)

電子回路、電子回路の製造方法、及び、実装部材

【課題】回路の大規模化を抑制しつつ、品質の良いデータ伝送を行う。

【解決手段】半導体チップである、例えば、ミリ波伝送チップには、シングルエンド信号がやりとりされるパッドを有するシングルエンドI/Fが設けられている。一方、例えば、インターポーザやプリント基板等の半導体チップが実装される実装部には、差動信号を伝送する、例えば、コプレーナストリップ線路等の差動伝送路が形成されている。ミリ波伝送チップは、差動伝送路を構成する導体に、シングルエンドI/Fのパッドが、電気的に直接接続されるように、実装部に実装されている。本技術は、例えば、IC等の電子回路に適用できる。

(もっと読む)

フレキシブル光電配線モジュール

【課題】 電磁ノイズ放射の抑制を可能としたフレキシブル光電配線モジュールを提供することである。

【解決手段】 フレキシブル光電配線モジュールあって、光配線路12と電気配線11を有する可撓性のフレキシブル光電配線板10と、フレキシブル光電配線板10の一主面上に搭載され、電気配線11に電気的に接続され、光配線路12に光結合された光半導体素子13と、フレキシブル光電配線板10の一主面と反対側の面に搭載され、電気配線11に電気的に接続され、光半導体素子13を駆動する駆動IC14と、フレキシブル光電配線板10を貫通して設けられ、光半導体素子13と駆動IC14を電気的に接続する貫通配線15とを具備した。

(もっと読む)

回路基板、回路基板の製造方法及び電子装置

【課題】回路基板の信号伝送特性を向上させる。

【解決手段】回路基板10は、絶縁層6内に設けられた配線層2、配線層4、及び貫通ビアホール7を含む。配線層2は、貫通ビアホール7が接続されたランド部2aと、そのランド部2aに接続された配線部2bとを有し、ランド部2aが、配線部2bよりも、上層の配線層4から離れる方向に薄くなっている。ランド部2aを薄くすることで、信号伝送時の、貫通ビアホール7との接続部におけるインピーダンスの低下を抑え、伝送損失を低減する。

(もっと読む)

フレキシブル光電配線モジュール

【課題】電磁ノイズ放射の抑制を可能とする。

【解決手段】実施形態によるフレキシブル光電配線モジュールは、光配線路12と第1の電気配線11iと第2の電気配線11aと第3の電気配線11c,11eとを有する可撓性のフレキシブル光電配線板10と、フレキシブル光電配線板に搭載され、第1の電気配線に電気的に接続され、光配線路に光結合された光半導体素子13aと、フレキシブル光電配線板に搭載され、第1の電気配線と第2の電気配線と第3の電気配線とに電気的に接続され、第1の電気配線を介して光半導体素子を駆動し、第2の電気配線を介して電気信号を入出力し、第3の電気配線を介して電源電位及びグランド電位を供給される駆動IC14aと、第3の電気配線に電気的に接続されたコンデンサ16aと、を具備し、光半導体素子と駆動ICとコンデンサとが搭載された回路領域15aを有する。

(もっと読む)

配線回路基板

【課題】グランド層の第1絶縁層または第2絶縁層に対する密着性を向上させることのできる配線回路基板を提供すること。

【解決手段】回路付サスペンション基板1において、第1ベース絶縁層3には、第1グランド開口部78が形成され、第2ベース絶縁層5には、第1グランド開口部78に対応する第2グランド開口部80が形成されており、第1グランド開口部78は、第2グランド開口部80に囲まれており、グランド層6が、第2グランド開口部80を介して、第1グランド開口部78内に、金属支持層2の上面に接触するように充填されているか、あるいは、第1グランド開口部78は、第2グランド開口部80を囲んでおり、第2ベース絶縁層5は、第1グランド開口部78の周端部に充填され、グランド層6が、第2グランド開口部80内に、金属支持層2の上面に接触するように充填されている。

(もっと読む)

プリント配線基板

【課題】接続端子部のリード端子層の剥がれを防止するのに好適なプリント配線基板を提供することを目的とする。

【解決手段】プリント配線基板は、外部コネクタに挿入嵌合される接続端子部T1を有し、前記接続端子部は、外部コネクタへの挿入方向に直交する一外形線Yに沿う先端面を有する可撓性の絶縁基板1と、前記絶縁基板の一方の面に形成された複数のリード配線層4と、前記複数のリード配線層の各先端部を構成して互いに平行に配置され前記一外形線に沿う先端面2a及び露出された平坦外面2sを有する細条の複数のリード端子層2と、前記リード端子層の背面位置において前記絶縁基板の他方の面に接着され前記一外形線に平行する先端面7aを有する補強体7とを備え、前記一外形線を基準にして前記補強体の先端面7aが前記絶縁基板1の先端面1aからリード配線層側に離間していること。

(もっと読む)

配線基板

【課題】信号線に伝送される高周波信号を低損失で伝送することが可能な配線基板を提供すること。

【解決手段】互いに積層された複数の絶縁層1と、絶縁層1の層間に配設された帯状の信号線2と、信号線2の上下に絶縁層1を挟んで対向配置された対向導体3と、信号線2と同じ絶縁層間に信号線2に対して並設された共面導体4と、を具備して成る配線基板であって、対向導体3と共面導体4との間に、対向導体3および共面導体4に電気的に接続された付加導体5が信号線2に対して並設されている。付加導体5により信号線2の側端部への電界の集中が緩和され、それにより信号線2に伝送される高周波信号を低損失で伝送することが可能となる。

(もっと読む)

プリント配線板

【課題】はんだクラック等の配線不良を防止しつつ、部品実装領域の外側のレイアウトにかかる制限を小さくすることができるプリント配線板の提供。

【解決手段】マトリクス状に配列された複数の電極パッド3と、複数の電極パッド3が配列された部品実装領域5の外側に設けられ熱応力を緩和する孔部7と、を有するプリント配線板1であって、部品実装領域5に実装されると共に、平面視で該部品実装領域5よりも大きな外縁を有するBGAパッケージ2を備え、孔部7は、BGAパッケージ2の外縁に対応する位置に設けられているという構成を採用する。

(もっと読む)

フレキシブルプリント基板

【課題】屈曲性が良好でありつつも安定した特性インピーダンスを実現し、高周波特性に優れる。

【解決手段】フレキシブルプリント基板100は、ベース基材12と、ベース基材12の両面に形成された配線11及びグランドプレーン層とを備える。配線11の一部には、配線11よりも幅広に形成されたパッド10が形成され、グランドプレーン層のパッド10とベース基材12を介して対向する位置には、パッド10と相似形状で且つパッド10の外形から100±50μm外側に拡がった外形となるようにくり抜かれたグランド除去部14が形成されている。

(もっと読む)

高周波信号線路及び電子機器

【課題】容易に曲げることができると共に、信号線の特性インピーダンスが所定の特性インピーダンスからずれることを抑制できる高周波信号線路及び電子機器を提供することである。

【解決手段】誘電体素体12は、保護層14及び誘電体シート18a〜18cが積層されてなり、かつ、表面及び裏面を有する。信号線20は、誘電体素体12に設けられている線状の導体である。グランド導体22は、誘電体素体12に設けられ、かつ、誘電体シート18aを介して信号線20と対向しており、信号線20に沿って連続的に延在している。グランド導体24は、誘電体素体12に設けられ、かつ、信号線20を挟んでグランド導体22と対向しており、複数の開口30が信号線20に沿って並ぶように設けられている。信号線20に関してグランド導体22側に位置する誘電体素体12の表面が、バッテリーパック206に対して接触する

(もっと読む)

高周波モジュール

【課題】リフロー方式の半田付けに対応可能で且つ小型化された高周波モジュールを提供することを目的としている。

【解決手段】略正方形状の多層基板の表層に、RFICが実装されるRFIC領域と、入力インピーダンスの整合を行う入力整合回路が実装される入力整合回路領域と、水晶発振器を含む発振回路が実装される発振回路領域と、前記RFIC、前記入力整合回路、前記発振回路を含む回路の電源管理を行う電源回路領域と、を有し、前記RFIC領域は、前記表層の略中央に配置され、前記入力整合回路領域は、前記RFIC領域の2辺と、前記RFIC領域の2辺とそれぞれ対向する前記多層基板の2辺とに沿った略L字形状である。

(もっと読む)

回路基板

【課題】

高周波信号の伝送損失を低減でき、かつ、クロストークノイズを抑制できる回路基板を提供する

【解決手段】

絶縁基板と、前記絶縁基板の内部又は少なくとも一主面上に形成された配線層とを含む回路基板であって、前記絶縁基板が、25℃で1GHzにおける誘電正接(tanδ)が0.004〜0.01の基板であり、前記配線層が、配線導体幅が40μm以下の部分を有し、かつ、絶縁基板と接する面の表面粗さ(Rz)が、1.5μm以下の層である、回路基板。

(もっと読む)

多層配線基板及びその多層配線基板に実装された高周波回路

【課題】異なる層の高周波伝送線路を接続する接続線路と高周波伝送線路とのインピーダンス不整合を効率的に改善し信号の反射損失を減らす。

【解決手段】多層配線基板1は積層した第1の誘電体基板20aの一方の面で延伸する信号線路10と他方の面上の接地導体40とで構成されるマイクロストリップ線路を備える。第1貫通導体30は、基板面に垂直に基板を貫通し信号線路10の先端と他の信号線路とを接続し、第2貫通導体ビア50は、基板面に垂直に複数個、基板を貫通して第1貫通導体30を円筒状に囲むように形成され、接地導体40を他の接地導体に接続する。接地導体40と第1貫通導体30とは第1の誘電体基板20aで構成される誘電体領域60で隔絶され、その信号線路10側の領域は、基板面上で第1貫通導体30の中心から所定の距離離れた領域確定線90に基づき決定され、信号線路10のない側の領域よりも面積が小さい。

(もっと読む)

半導体装置の実装構造及び実装方法

【課題】半導体パッケージが基板表面に接続された実装構造体の不要な電磁波を抑制する。

【解決手段】本実装構造は、基板1表面上には、複数の第1の電極パッド12と、基板の電源層又はグラウンドに接続された複数の第3の電極パッド13とが形成されており、半導体パッケージ表面上には、複数の第2の電極パッド22と、半導体パッケージの電源層又はグラウンドに接続された複数の第4の電極パッド23とが形成されている。半導体パッケージと基板は、第1及び第2の電極パッドを電気的に接続する第1の導電性接合体31と、第3及び第4の電極パッドを電気的に接続する第2の導電性接合体32とにより接続され、第2の導電性接合体は、その大きさが第1の導電性接合体よりも小さく形成されるとともに、第1の導電性接合体のそれぞれの周囲を取り囲むように分布して配置されている。

(もっと読む)

半導体メモリカード及びその製造方法

【課題】半導体メモリを搭載する基板上においてデータ信号の劣化を防止した半導体メモリカード及びその製造方法を提供する。

【解決手段】実施の形態によれば、半導体メモリと、通常モード及び通常モードよりもデータ転送速度が速い高速モードの両方での半導体メモリへのデータの読み書きを制御するメモリコントローラと、少なくとも一つの内層を有する多層プリント基板に半導体メモリ及びメモリコントローラを表裏に分けて実装した回路基板とを備える。回路基板は、メモリコントローラと外部機器との間での高速モードによるデータ入出力用としてメモリコントローラの実装面に設けられ、金めっき加工が施された高速モード用の金端子と、高速モード用の金端子とメモリコントローラの実装用のボンディングパッドとの間の高速差動信号配線と、高速差動信号配線から分岐し、回路基板の面内において分岐点の近傍で切断された金めっき加工用のめっきリードを有する。

(もっと読む)

配線基板

【課題】信号配線に30GHz以上の超高周波の信号を効率よく伝送させることが可能な配線基板を提供すること。

【解決手段】絶縁層1を貫通する貫通導体3Sと、絶縁層1の表面に貫通導体3Sを覆うランド部Lを有して配設された帯状の信号配線2Sと、絶縁層1の表面に信号配線2Sの周囲を所定の間隔をあけて取り囲むように配設された接地導体2Gまたは電源導体2Pと、を具備して成る配線基板であって、信号配線2Sは、ランド部Lの直径よりも広い幅で接地導体2Gまたは電源導体2Pとの間隔が一定である幅広部Wと、幅広部Wとランド部Lとの間を接続し、ランド部Lの直径よりも狭い幅で且つ信号配線2Sを伝播する信号の波長の4分の1未満の長さの幅狭部Nとを有する配線基板である。

(もっと読む)

電子機器

【課題】表示装置の大型化や厚みの増加を抑制しつつ、フレキシブルプリント配線板のグランドをシャーシに確実に接続する。

【解決手段】液晶パネルユニット9に接続される液晶FPC14は、ジョグダイヤルユニット10とメインシャーシ11との間に配置される。シャーシ11の、液晶FPC14に対向する面にシャーシ凸部22を形成する。突起20は、センターボタン4を保持する保持部材の一部を熱カシメすることで形成される。液晶FPC14のうちシャーシ11に対向する面におけるシャーシ凸部22に対向する位置に、グランドパターン露出部23を形成する。突起20によって液晶FPC14が押圧されることでグランドパターン露出部23がシャーシ凸部22に接触する。

(もっと読む)

1 - 20 / 1,016

[ Back to top ]