Fターム[5E346FF01]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 孔あけによるもの(スルーホール等) (5,634)

Fターム[5E346FF01]の下位に属するFターム

Fターム[5E346FF01]に分類される特許

1 - 20 / 812

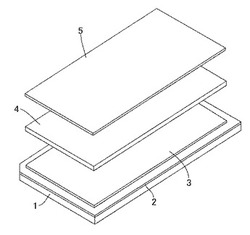

配線板の製造方法

【課題】 薄い銅箔とプリプレグとを積層する作業時の煩雑化や遅延を招くことが少なく、銅箔の位置ずれや皺の発生を防いで製品の信頼性や品質の向上を図ることのできる配線板の製造方法を提供する。

【解決手段】 厚さ18μm以下の銅箔3と厚さ100μm以下のプリプレグ4を使用して配線板を製造する配線板の製造方法であり、サポート基材1の弱粘着性を有する表面に銅箔3の全対向面を着脱自在に粘着し、銅箔3の表面にプリプレグ4と積層用の銅箔5を順次積層してプレスするとともに、積層用の銅箔5に所定の配線パターンをパターニングして積層体6を形成し、サポート基材1から積層体6を剥離した後、積層体6を形成する銅箔3を所定の電極パターンにパターニングする。剛性を有するサポート基材1に薄く扱いにくい銅箔3を粘着して剛性を確保するので、一枚目の銅箔3とプリプレグ4を積層する際、作業の煩雑化や遅延を招くことが少ない。

(もっと読む)

積層回路基板の製造方法、積層回路基板、および電子機器

【課題】ビアの接続不良を抑制可能な積層回路基板およびその製造方法を提供する。

【解決手段】積層回路基板の製造方法は、第1基板と第2基板とが積層された積層回路基板の製造方法であって、第1基板上に、一の面の開口面積が他の面の開口面積よりも大きい複数の異形ビアホールを有する接着樹脂シートを、一の面を第1基板に向けて配置する第1の配置工程と、ビアホールに導電性ペーストを充填する充填工程と、導電性ペーストが充填された後、接着樹脂シートの他の面上に第2基板を配置する第2の配置工程と、加熱下で第1基板と第2基板の積層方向に加圧する熱プレス処理を行う熱プレス工程とを有する。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】本発明は、半導体パッケージ及びその製造方法に関する。

【解決手段】本発明の実施形態による半導体パッケージは、第1側面を有する電気素子と、電気素子が位置するキャビティを有するコア基板と、を含み、コア基板は、コア基板の厚さ方向に対して傾き、キャビティを定義する第2側面を有する。

(もっと読む)

差動伝送線路および多層配線基板

【課題】 外部からのノイズの影響を低減し、高周波信号を効率よく伝送することができる差動伝送線路および該差動伝送線路を備えた多層配線基板を提供することにある。

【解決手段】 絶縁層を挟んで上下に対向する第1配線導体2および第2配線導体3を有する一対の配線導体からなる差動伝送線路において、一方の第1配線導体2aの端部と他方の第1配線導体2bの端部とが絶縁層を貫通して設けられた第1貫通導体4を介して電気的に接続され、一方の第2配線導体3aの端部と他方の第2配線導体3bの端部とが絶縁層を貫通して設けられた第2貫通導体5を介して電気的に接続されており、第1貫通導体4と第2貫通導体5との間に接地貫通導体6が設けられている。外部からのノイズの影響を低減し、高周波信号を効率よく伝送することが可能となる。

(もっと読む)

プリント基板およびそれを用いた電子機器

【課題】

電子機器において、コネクタや電子部品の接続に用いられるプレスフィット接続に関し、プレスフィット端子近傍のプリント基板が損傷し、プリント基板の耐湿性や実装部品の信頼性を低下させる現象を防止し、高密度実装が可能な電子機器を提供する。

【解決手段】

プリント基板を上面から見たときに、多数のスルーホールのうち隣接するスルーホール間でプレスフィット端子を挿入したときに圧縮力が作用するスルーホール間に、ランド又は最上層の基板と最下層の基板とに挟まれた基板に形成されたスルーホールの内壁面に形成された導体膜に接続する導体膜またはスルーホールの内壁面に形成された導体膜に電気的に接続しない導体膜のいずれかがスルーホールの直径と同じかそれよりも広い幅に亘って存在するようにプリント基板を形成した。

(もっと読む)

回路基板およびその製造方法

【課題】キャビティーを有する回路基板を提供する。

【解決手段】回路基板200は第1のコア層210、第2のコア層220、および中央誘電体層230を含む。第1のコア層はコア誘電体層212およびコア回路層214を含み、コア回路層はコア誘電体層の上に配置される。第2のコア層は第1のコア層の上に配置される。中央誘電体層は、第1のコア層と第2のコア層の間に配置される。キャビティーRは第2のコア層および中央誘電体層を貫通し、コア回路層の一部を露出させる。

(もっと読む)

コンデンサ素子及びコンデンサ内蔵基板

【課題】コンデンサ内蔵基板に生じるインダクタンスを小さくすることが可能なコンデンサ素子、及び該コンデンサ素子を具えたコンデンサ内蔵基板を提供する。

【解決手段】本発明に係るコンデンサ素子は、第1電極層11と第2電極層12との間に誘電体層13が介在したコンデンサ素子1であって、第1電極層11は、第2電極層12側の表面111の一部が該第2電極層12によって覆われ、第1電極層11が金属箔により形成される一方、第2電極層12が金属薄膜又は金属箔により形成されている。本発明に係るコンデンサ内蔵基板は、前記コンデンサ素子1と絶縁基板2とを具え、該絶縁基板2内にコンデンサ素子1を埋設することにより絶縁基板2にコンデンサ素子1が内蔵されている。

(もっと読む)

チップインダクタ内蔵配線基板

【課題】チップインダクタ内蔵配線基板において、チップインダクタの漏れ磁束に起因したノイズとしての高周波電流の配線層への影響を低減し、配線基板に実装された他の回路部品や電子部品に対する電位変動や電源供給の変動を抑制して、これら回路部品及び電子部品の動作を良好に保持する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層と、前記第1の配線層及び前記第2の配線層間に配設されてなる絶縁層と、前記絶縁層内に配設されるとともに、前記第1の配線層に実装されてなるチップインダクタとを具え、前記第2の配線層は安定電位を供給する配線層であり、前記第2の配線層の前記チップインダクタと相対向する領域において非連続の複数の開口部が形成され、前記領域が前記非連続の複数の開口部によって画定されるようにして、チップインダクタ内蔵配線基板を構成する。

(もっと読む)

高周波部品及び通信装置

【課題】小型化を図った高周波部品および通信装置を提供する。

【解決手段】複数の誘電体層を積層してなる積層基板に高周波信号処理回路を備えた高周波部品であって、高周波信号の入力、出力端子および高周波信号処理回路の複数の電源端子を含む端子群が積層基板の一方の主面に形成されており、積層基板を構成する誘電体層には、インダクタンス素子用等のパターン電極が構成され、一端がそれぞれ電源端子に接続された複数の電源ラインは、誘電体層1に形成されたビア電極を介して高周波信号処理回路が有する少なくとも一つの半導体素子に接続され、複数の電源ラインのうち少なくとも二つの電源ラインは、それぞれ、隣接する二以上の誘電体層1にわたって積層方向から見て重なるように形成されたビア電極列2を有し、少なくとも二つの電源ラインのビア電極列2は、隣接する誘電体層間において、他の導体パターンを介さずに近接している。

(もっと読む)

部品内蔵配線基板及びその製造方法

【課題】コア基板の収容部内に内蔵部品を収容する際、複雑な加工を行うことなく内蔵部品の正確な位置決めが可能な部品内蔵配線基板を提供する。

【解決手段】部品内蔵配線基板10は、コア基板11と、コア基板11を貫通する収容部21と、収容部21に収容された内蔵部品50と、コア基板11の上下に積層形成した配線積層部12、13とを備えている。収容部21は、平面視で方向が異なる第1及び第2の内壁面を含むコア基板11の内壁面20によって画定され、内蔵部品50は、第1及び第2の内壁面のそれぞれと部分的に接した状態で収容部21に収容され、内壁面20と内蔵部品50との間隙部において内蔵部品50が第1及び第2の内壁面と接していない領域に樹脂充填材Fが充填されている

(もっと読む)

部品内蔵基板およびその製造方法

【課題】ハンダ等の再溶融がなくなり、工程を簡略化可能な部品内蔵基板およびその製造方法を提供する。

【解決手段】第1積層基板11の一方の面11aに第1電子部品T1を載置する第1電極13と、第1積層基板に凹部14を設け、第1積層基板内部の配線回路が凹部内に露呈され、第2電子部品T2の一端T2aと接続する第2電極16とを備える第1配線基板17と、第2積層基板21の一方の面に凹部24を設け、第2積層基板内部の配線回路が凹部内に露呈され、第2電子部品T2の他端T2bと接続する第3電極26とを備える第2配線基板27と、を備えており、第1配線基板と第2配線基板との一方の面はそれぞれの凹部が互いに対向する内面に向いて開口するように配されており、各々の電子部品と各々の電極とは、導電性ペーストPからなる層間導通部により接続される。

(もっと読む)

部品集合体

【課題】高精度に、かつ、容易に主基板に内蔵することのできる部品集合体を提供する。

【解決手段】線膨脹係数αCが小さい複数のコンデンサ52を配列して内蔵する集合体基板の部品内蔵層の線膨脹係数αBが、集合体基板が埋設される部品内蔵基板1の部品内蔵層5の線膨張係数αAより小さく形成されているため、例えばリフローにおける加熱や、雰囲気の温度変動により各部材が膨脹することにより生じる応力を緩和することができ、各部材間における電気的な接続部分に応力が集中することにより各接続部分に不具合が生じることを防止でき、コンデンサ52に対する電気的接続の信頼性の向上を図ることができる。

(もっと読む)

配線基板及びその製造方法、半導体装置

【課題】シリコン層又はガラス層とコア基板とをバンプを介在させないで接続した配線基板及びその製造方法、並びに前記配線基板を有する半導体装置を提供すること。

【解決手段】本配線基板は、絶縁性基材の一方の面から他方の面に貫通する複数の線状導体を備えたコア基板と、前記一方の面側及び前記他方の面側の少なくとも一面側に接合されたシリコン層と、前記シリコン層を貫通する貫通配線と、を有し、前記貫通配線は、バンプを介さずに前記線状導体と電気的に接続されており、1つの前記貫通配線の端部に対して、複数の前記線状導体が電気的に接続されている。

(もっと読む)

回路基板、回路モジュール、及び電子機器

【課題】内包した電子部品へのノイズ遮断機能をもち、薄型・小型対応な回路基板に対し、外部応力への耐性を強めた信頼性の高い回路基板を提供する。

【解決手段】回路基板1は厚さが薄い直方体形状を有するものであって、基材2と、凹部3と、電子部品4と、溝5と、電極6と、絶縁性樹脂7と、導電性樹脂8、とを備えており、導電性樹脂8と電極6Bとの接続を溝5の内部で行っているので、回路基板表面へ外部応力が加わったとしても基材2の内部にある電極6Bと導電性樹脂8との接続面への応力は緩和されるので、外部応力に強い電気接続が得られる。また、溝5の内部に導電性樹脂8が入るので、基材2と導電性樹脂8の接続を強固なものとすることができる。

(もっと読む)

素子内蔵配線基板、及びその製造方法

【課題】少なくとも一対の配線層と、この一対の配線層間に配設された絶縁層とからなる配線基板中に、MEMSやSAWフィルタなどの機能性素子をその機能面の機能を劣化させない状態で埋設してなる新規な構造の素子内蔵配線基板を安価に提供する。

【解決方法】相対向して配置される一対の第1の配線層及び第2の配線層と、前記第1の配線層及び前記第2の配線層間に配設されてなる絶縁層と、前記絶縁層内に配設されるとともに、前記第1の配線層に実装されてなる中空形成部材と、前記中空形成部材内に収容されるとともに、前記第1の配線層に実装されてなる機能性素子と、を具えるようにして、素子内蔵配線基板を構成する。

(もっと読む)

導電性ペーストおよび多層配線基板

【課題】多層配線基板のバンプとして導電性ペーストを用いた際、導電性金属箔への印刷後に樹脂にじみの発生によるランド径周辺の汚染を抑制し、良好なバンプ貫通性を保持できるようなバンプ形状(印刷性)を与えることができる導電性ペーストを提供すること。

【解決手段】

多層基板のバンプ形成に用いられる導電性ペーストであり

(A)25℃において固形であるエポキシ樹脂、(B)硬化剤、(C)導電性フィラー、および(D)有機溶剤を含む導電性ペーストであって、レオメーターを使用して連続的にシェアレートを変えて繰り返し30℃で測定した粘度が、シェアレート10.0sec-1のとき100〜200Pa・sであり、かつ、シェアレート100.0sec-1のとき10〜40Pa・sであることを特徴とする導電性ペースト。

(もっと読む)

部品内蔵基板の製造方法

【課題】樹脂フィルムを熱圧着する際に発生する樹脂流動を抑制し、平坦性に優れ、導体パターンの歪みが抑制された部品内蔵基板を提供する。

【解決手段】本発明の部品内蔵基板20に形成された電子部品9を内蔵するためのキャビティ8は、部品内蔵基板20を積層方向から平面視したとき、電子部品9の面積より大きい貫通孔と、電子部品9の面積より小さい貫通孔によって構成されている。電子部品9をキャビティ8に挿入する際、第2の樹脂フィルム2の舌片部及びが電子部品9の挿入方向に折れ曲がり、キャビティ8と電子部品9の隙間を埋める。その結果、熱圧着時の樹脂流動を抑制し、導体パターン4の歪みや部品内蔵基板20の表面の平坦性の悪化を抑制する。

(もっと読む)

絶縁性基板、金属張積層板、プリント配線板、及び半導体装置

【課題】半導体装置のマイナス反りを充分に軽減又は防止することができる絶縁性基板又は金属張積層板、並びに当該絶縁性基板又は金属張積層板を用いたプリント配線板及び半導体装置を提供する。

【解決手段】1層以上の繊維基材層及び2層以上の樹脂層を含み、両面の最外層が樹脂層である積層体の硬化物からなり、少なくとも1つの繊維基材層が、基準位置、即ち絶縁性基板の全体厚みを繊維基材層数で均等に分割した各領域の厚みをさらに均等に2分割する位置、よりも一面側又は他面側に偏在し、異なる方向に偏在しているものがない絶縁性基板又は当該絶縁性基板を含む金属張積層板をコア基板として用い、プリント配線板を作製する。また、当該プリント配線板に半導体素子を搭載して半導体装置を作製する。

(もっと読む)

薄膜キャパシタ、多層配線基板および半導体装置

【課題】インダクタンスを低減すると共に、有効電極面積の減少を抑えて小型化することが可能な薄膜キャパシタ、多層配線基板、および半導体装置を提供する。

【解決手段】誘電体層の上面に第1極性の電極層、前記誘電体層の下面に第2極性の電極層を有し、特定位置の周りに配置された複数の第1容量素子と、前記誘電体層の上面に前記第2極性の電極層、前記誘電体層の下面に前記第1極性の電極層を有し、前記特定位置の周りに前記複数の第1容量素子と交互に配置された複数の第2容量素子と、前記特定位置に設けられ、前記複数の第1容量素子のすべての第1極性の電極層および前記複数の第2容量素子のすべての第1極性の電極層を接続する単一の共通接続孔と、前記共通接続孔の周りに設けられ、前記複数の第1容量素子の各々の第2極性の電極層を、隣接する前記第2容量素子の第2極性の電極層に接続する複数の個別接続孔とを備えた薄膜キャパシタ。

(もっと読む)

配線基板の製造方法

【課題】複数の絶縁層と該絶縁層の間に形成された配線層とを交互に積層した配線基板において、上記配線層を構成する隣接する配線導体同士の間に絶縁材の樹脂が隙間なく充填され、且つ配線導体の位置ズレやこれに伴う変形や断線などの不具合を皆無とした配線基板の製造方法を提供する。

【解決手段】熱硬化性樹脂からなるベース絶縁層1と、該ベース絶縁層1の表面および裏面に形成された熱可塑性樹脂からなる接着層2a,2bとを含む絶縁層3と、上記ベース絶縁層1の表面側における接着層2aの上に形成され、厚みが5μm超である複数の配線導体4からなり且つ隣接する配線導体4同士の間隔が100μm以下の配線層4と、を交互に積層してなる配線基板の製造方法であって、上記配線層4において隣接する配線導体4同士の隙間6に硬化性樹脂9aを充填する工程と、充填された硬化性樹脂9aを硬化処理する工程と、を含む、配線基板の製造方法。

(もっと読む)

1 - 20 / 812

[ Back to top ]