Fターム[5E346FF45]の内容

多層プリント配線板の製造 (97,916) | 導体層間接続の方法 (9,115) | 部品の実装によるもの (1,788)

Fターム[5E346FF45]に分類される特許

1 - 20 / 1,788

プリント基板組立体の配線設計方法及び製造方法

部品内蔵配線基板、及びその製造方法

配線基板の製造方法

配線基板及びその製造方法、半導体パッケージ

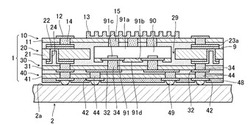

部品内蔵基板及びその製造方法

【課題】製造工程数を増やすことなく放熱用フィンと配線回路を同一面上に備える。

【解決手段】部品内蔵基板1は、第1〜第4プリント配線基材10〜40を熱圧着により一括積層した構造を備える。第1プリント配線基材10の表面には、パターン形成された信号用配線12及び放熱用フィン13が形成され、第1樹脂基材11に形成されたビアホール内に充填された導電ペーストからなる信号用ビア14及びサーマルビア15がこれらに接続されている。信号用配線12及び放熱用フィン13は、例えばサブトラクティブ法により、同一工程にて同時にパターン形成される。第2プリント配線基材20の第2樹脂基材21に形成された開口部29内には、電子部品90の裏面91aがサーマルビア15と接続された状態で内蔵されている。電子部品90の熱は、電子部品90の裏面91aに接するサーマルビア15を介して放熱用フィン13から放熱される。

(もっと読む)

配線基板

【課題】半導体集積回路素子に対して十分な電源供給を行なって半導体集積回路素子を良好に作動させることが可能な配線基板を提供すること。

【解決手段】上面側のビルドアップ配線層3における電源プレーン3Pの中に形成された接地用のビアランド3Lおよびこれに接続されたビア6は、接地用の半導体素子接続パッド7Gの各列における一部のパッドにのみ対応するにように間引かれて形成されているとともに、電源用の半導体素子接続パッド7Pの各列から電源用のスルーホール5Pへの導電路が電源プレーン3Pにおける前記間引かれた部分を通るようにして形成されているとともに、下面側のビルドアップ配線層3におけるビアランド3Lは、複数一組のビア6に対応する分が一つに繋がっている。

(もっと読む)

部品内蔵基板及びその製造方法並びに部品内蔵基板実装体

【課題】電子部品と導熱層との密着性を確保し、放熱特性を向上させる。

【解決手段】部品内蔵基板実装体100は、部品内蔵基板1と、これが実装された実装基板2とからなる。部品内蔵基板1は、第2〜第4プリント配線基材20〜40及びカバーレイフィルム3を熱圧着により一括積層した構造を備える。第2プリント配線基材20の第2樹脂基材21に形成された開口部29内には、電子部品90の裏面91aと導熱層23Aとが密着し、且つ孔部23Bを介して接着層9により固定された状態で内蔵されている。第4プリント配線基材40の実装面2a側にはバンプ49が形成されている。電子部品90の裏面91aに接する導熱層23Aやサーマルビア24を介して、各層のサーマルビア及びサーマル配線を通り、バンプ49から実装基板2に電子部品90の熱が伝わって、実装基板2にて放熱される。

(もっと読む)

半導体モジュール

【課題】本明細書では、基板基材が熱によって劣化することを抑制することができる構造の半導体モジュールを開示する。

【解決手段】半導体モジュール2は、基板基材4内にIGBT10、ダイオード20、プリント配線30〜44、及び、断熱部50が配置されて形成されている。IGBT10とダイオード20は、基板基材4内に並べて配置されている。プリント配線30は、IGBT10及びダイオード20と接続されている。同様に、プリント配線34、36は、IGBT10と接続されている。また、プリント配線38は、ダイオード20と接続されている。プリント配線30〜44の一部は、基板基材4の表面に露出している。断熱部50は、IGBT10と基板基材4との間、ダイオード20と基板基材4との間、及び、プリント配線30、34、36、38と基板基材4との間に配置されている。

(もっと読む)

部品内蔵配線板の製造方法

【課題】複数種の部品が混載で埋設、実装される場合であっても大きな生産性と低コストを実現できる部品内蔵配線板の製造方法を提供すること。

【解決手段】第1の絶縁板上に、端子パッドを有する半導体チップと端子パッドに電気的に接続されたグリッド状配列の表面実装用端子とを備えた半導体素子を実装するための第1のランドと、表面実装用のチップ部品を実装するための第2のランドとを形成し、第1、第2のランド上にクリームはんだを適用し、クリームはんだを介して第1、第2のランド上に半導体素子およびチップ部品をそれぞれ載置し、クリームはんだをリフローすべく加熱して、半導体素子およびチップ部品を第1、第2のランドにそれぞれ接続し、第1の絶縁板とは別の第2の絶縁板中に、第1、第2のランドにそれぞれ接続された半導体素子およびチップ部品を埋め込むように、第1の絶縁板に積層状に第2の絶縁板を一体化する。

(もっと読む)

コンデンサモジュール内蔵配線基板

【課題】製造コストが安く、接続信頼性に優れたコンデンサモジュール内蔵配線基板を提供すること。

【解決手段】コンデンサモジュール内蔵配線基板10は、半導体チップ21を表面実装するための複数の端子パッド44が基板主面51上に設けられるとともに、BGA用パッド48が基板裏面52上に設けられている。ガラス基板102とそのガラス基板102の第2面106上に実装される複数のチップコンデンサ103とによってコンデンサモジュール101が構成される。コンデンサモジュール101は、基板主面51上に設定された半導体チップ搭載領域23の直下にて、チップコンデンサ103を実装していない第1面105側を基板主面51側に向けた状態で内蔵される。

(もっと読む)

半導体パッケージ及びその製造方法

【課題】本発明は、半導体パッケージ及びその製造方法に関する。

【解決手段】本発明の実施形態による半導体パッケージは、第1側面を有する電気素子と、電気素子が位置するキャビティを有するコア基板と、を含み、コア基板は、コア基板の厚さ方向に対して傾き、キャビティを定義する第2側面を有する。

(もっと読む)

半導体装置用多層配線基板

【課題】リードピンへの応力の集中を抑制すると共に、張り合わせ時のボイドの発生を抑制することができる半導体装置用多層配線基板を提供することにある。

【解決手段】導体層104〜109と誘電体層111〜117とが交互に積層され、最上面と最下面が導体層101,102a,102b、109で構成されると共に、最上面の導体層101,102a,102bが、半導体装置が備えるリードピン11,12a,12bを当接接合可能な接合領域121で構成された半導体装置用多層配線基板100であって、前記接合領域121の下部に位置する導体層104〜108は2次元アレイ状に整列配置された複数個の孤立パタンで構成されるようにした。

(もっと読む)

半導体パッケージ、半導体パッケージの製造方法及び半導体装置

【課題】反りを低減することができる半導体パッケージ、半導体パッケージの製造方法及び半導体装置を提供する。

【解決手段】半導体パッケージ1は、半導体チップ2と、半導体チップ2を覆うように形成された第1絶縁層11と、第1絶縁層11上に積層され、半導体チップ2と電気的に接続された第2〜第5配線層20,30,40,50と第2〜第4絶縁層21,31,41とが交互に積層されてなる配線構造と、を有する。第1絶縁層11の面11Aとは反対側の最外層の第4絶縁層41には、その第4絶縁層41を厚さ方向に貫通する溝部41Xが形成されている。

(もっと読む)

半導体装置内蔵基板モジュール及びその製造方法

【課題】特定の機能を備えた半導体装置の高集積化及び小型化を図ることができるとともに、部品実装に係る製造工程の簡略化や効率化を図ることができる半導体装置内蔵基板モジュール、及び、その製造方法を提供する。

【解決手段】半導体装置内蔵基板モジュール10は、コア基板21に、ウエハレベルCSP構造の半導体装置30が内蔵された基板装置部20と、所望の機能を有する機能部であるコイル部50とが、一体的に形成されるとともに、これらが、積層配線を構成する配線層やビア、貫通電極を介して、相互に電気的に接続された構成を有している。

(もっと読む)

多数個取りセラミック基板およびセラミック基板

【課題】 絶縁層が光の反射層となることができ、個片のセラミック基板への分割も容易な多数個取りセラミック基板および個片のセラミック基板を提供することにある。

【解決手段】 複数の基板領域2を有する母基板1と、母基板1の上面に、基板領域2の境界に沿って設けられた分割溝3とを備えており、母基板1が、第1のセラミック焼結体からなる絶縁層1aと、第1のセラミック焼結体よりも結晶化温度が低い第2のセラミック焼結体からなる拘束層1bとが交互に、最上層が絶縁層1aとなるように積層されて形成されているとともに、母基板1の上面に分割溝3に沿って、第2のセラミック焼結体からなる帯状拘束層4が付着している多数個取りセラミック基板9である。帯状拘束層4により、分割溝3が形成された部分における絶縁層1aの収縮を抑制して分割溝3の変形を抑制できる。そのため、分割が容易な多数個取りセラミック基板9を提供できる。

(もっと読む)

部品内蔵配線板、部品内蔵配線板の製造方法

【課題】両方の面上に実装された外付け実装部品のそれぞれとの関係として電気的特性を向上するような部品内蔵を実現すること。

【解決手段】内蔵部品を接続するための第1の接続領域を備えた第1の配線層と、第1の配線層の第1の接続領域に接続された第1の部品と、第1の部品を埋め込むように、第1の配線層上に積層して位置する板状絶縁層と、板状絶縁層が第1の部品を埋め込むため要している該板状絶縁層の空間領域を避けるように、該板状絶縁層の厚み内に内層配線層として設けられた、内蔵部品を接続するための第2の接続領域を備えた第2の配線層と、第2の配線層から見た方向が、第1の配線層から見た第1の部品の方向とは反対になるように、板状絶縁層に埋め込まれて、該第2の配線層の第2の接続領域に接続された第2の部品とを具備する。

(もっと読む)

半導体実装部材及びその製造方法

【課題】 高い信頼性を有する半導体実装部材及びその製造方法を提供する。

【解決手段】 第2基板300が、上方へ突き出る第2接続導体332Pを備える。第1基板500が、上方へ突き出る第1接続導体872Pを備える。例えば半導体実装部材を外部基板に実装する際に生じる応力を、第1接続導体332Pで第1基板側へ逃がすと共に、第2接続導体872Pで第2基板側へ逃がし、靱性が高く脆い半導体素子90へ加わる応力を緩和することができる。

(もっと読む)

電子部品埋込み型印刷回路基板及びその製造方法

【課題】印刷回路基板内に電子部品を直接内蔵し、固定せずに脱着自在に形成することによって、基板の歩留まりに伴う部品損失を減らすことができる、電子部品埋込み型印刷回路基板及びその製造方法を提供する。

【解決手段】本発明の電子部品埋込み型印刷回路基板100は、中空構造の電子部品ケース120が設けられたベース基板110と、電子部品ケース120に挿入される電子部品150と、ベース基板110の上下面に設けられた回路パターン層131、132と、これらの回路パターン層131、132を覆う絶縁層160とを含む。

(もっと読む)

配線基板ならびにその配線基板を備えた電子装置および電子モジュール装置

【課題】 実装信頼性が高い配線基板および電子装置ならびに電子モジュール装置を提供する。

【解決手段】 本発明の配線基板は、中央領域Mおよび周囲領域Sを有する上面を含んでおり、周囲領域Sに設けられておりそれぞれ電子部品Eが収納される複数の凹部3と中央領域Mまたは周囲領域Sに設けられており複数の凹部3を連結する連結部4とを有している絶縁基体2を備えており、同様の高さの部分をたどって中央領域Mから周辺領域Sを介して周辺領域Sの外側へつながる経路を有するように連結部4が配置されている。

(もっと読む)

配線基板及びその製造方法

【課題】半導体チップとの接続信頼性の優れた配線基板を提供すること。

【解決手段】オーガニック配線基板10の基板主面11側には、樹脂絶縁層21〜23と導体層24とを積層した第1ビルドアップ層31が形成されている。第1ビルドアップ層31における最表層の導体層24は、半導体チップをフリップチップ実装するための複数の接続端子部41を含む。複数の接続端子部41は、ソルダーレジスト25の開口部43を介して露出している。各接続端子部41は、半導体チップの接続領域51と、接続領域51から平面方向に延設されかつ接続領域51よりも幅が狭く形成された配線領域52とを有する。配線領域52の表面のはんだ濡れ性は接続領域51の表面のはんだ濡れ性よりも低くなっている。

(もっと読む)

1 - 20 / 1,788

[ Back to top ]