Fターム[5F003BA91]の内容

バイポーラトランジスタ (11,930) | 素子構造 (1,262) | 空乏層制御構造 (403)

Fターム[5F003BA91]の下位に属するFターム

メサ、ベベル (349)

ガードリング、チャンネルストッパー (45)

Fターム[5F003BA91]に分類される特許

1 - 9 / 9

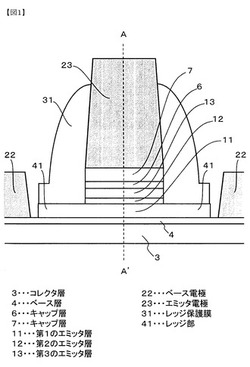

ヘテロ接合バイポーラトランジスタ

【課題】エミッタ電子輸送特性やエミッタ注入効率を劣化させることなく、レッジ部を薄層化することが容易で、微細化に適したヘテロ接合バイポーラトランジスタを提供すること。

【解決手段】エミッタ層は、第1の半導体層11と、第2の半導体層12と、第3の半導体層13との積層構造からなり、第3の半導体層13は、第2の半導体層12に対してウェット・エッチングにより選択的に除去でき、第2の半導体層12は、第1の半導体層11に対してウェット・エッチングにより選択的に除去でき、第1の半導体層11と第3の半導体層13のバンドギャップはベース層4のバンドギャップよりも大きく、第2の半導体層12は不純物添加によって縮退しており、第3の半導体層13は不純物添加によって中性領域を形成しているヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

バイポーラ・トランジスタのコレクタ領域をカウンタ・ドープする方法

【課題】バイポーラ・トランジスタのコレクタウエルを形成する方法を提供する。

【解決手段】本方法は、第1の種類のドーパントでシリコン層をドープすること、および第1の注入工程を実施して第1の種類とは反対の第2の種類のドーパントをシリコン層内に注入することを含む。注入されたドーパントは、シリコン層内で第1のドーパント・プロフィル305を有する。本方法はまた、第2の注入工程を実施して第2の種類の追加のドーパントをシリコン層内に注入することを含む。注入された追加のドーパントは、シリコン層内で第1のドーパント・プロフィル310とは異なる第2のドーパント・プロフィル320を有する。本方法は、シリコン層および第1の種類のドーパントの一部分を消費することによって、シリコン層上に形成された絶縁層を成長させることをさらに含む。

(もっと読む)

炭化珪素バイポーラ型半導体装置

【課題】メサ構造をもつ炭化珪素バイポーラ型半導体装置において、素子の表面付近に存在する欠陥核を起点とした積層欠陥の発生およびその面積拡大を抑制し、これにより順方向電圧の増加を抑制する。

【解決手段】第1導電型炭化珪素単結晶基板、第1導電型炭化珪素ドリフト層、第2導電型炭化珪素電荷注入層および該炭化珪素電荷注入層よりもドーピング密度が高い第2導電型の高ドーピング層が、この順序にて積層してなり、前記炭化珪素ドリフト層から前記高ドーピング層側の素子表面に至るメサ構造を有し、前記高ドーピング層の厚さが15nm〜1.5μmであり、かつ、前記高ドーピング層における最大ドーピング密度が1×1020cm-3〜2×1021cm-3であることを特徴とする炭化珪素バイポーラ型半導体装置。

(もっと読む)

略自然降伏デバイス

【課題】 バイアス電圧が印加されるときに半導体デバイス上に自然降伏状態を作り出すような「略自然降伏状態」を提供する。

【解決手段】 本発明の半導体デバイスは第1半導体領域を含み、第1半導体領域は、強制または非強制略自然降伏領域であり、この領域は、非自然降伏(例えば、ツェナー降伏及び雪崩降伏)の降伏電圧以下の大きさを有する所定電圧がデバイスの両端に印加されるときに完全に空乏化される。

(もっと読む)

ベース領域上に炭化ケイ素保護層を有する炭化ケイ素バイポーラ接合トランジスタとその製造方法

【課題】第1の導電型の炭化ケイ素(SiC)コレクタ層、炭化ケイ素コレクタ層上の第2の導電型のエピタキシャル炭化ケイ素ベース層、およびエピタキシャル炭化ケイ素ベース層上の第1の導電型のエピタキシャル炭化ケイ素エミッタメサを含むバイポーラ接合トランジスタ(BJT)を提供する。

【解決手段】本発明に係るバイポーラ接合トランジスタでは、第1の導電型のエピタキシャル炭化ケイ素保護層が、炭化ケイ素エミッタメサの外側にあるエピタキシャル炭化ケイ素ベース層の少なくとも一部に設けられる。また、エピタキシャル炭化ケイ素保護層が、0デバイスバイアスで完全空乏状態になるように構成される。

(もっと読む)

リサーフ構造を用いた窒化物半導体ヘテロ接合トランジスタ

【課題】リサーフの効果を用いる構造により窒化物系ヘテロ接合トランジスタの高耐圧化を行う。

【解決手段】窒化物半導体により構成されるトランジスタにおいて、GaN層3とAlyGa1−yNバリアー層4のヘテロ接合に形成された二次元キャリアガスの特性を持つn型チャンネルに対して、AlxGa1−xNバリアー層2とGaN層3のヘテロ接合にp型の二次元状キャリアを持つ電界制御チャンネルを平行に形成し、チャンネルと電界制御チャンネルが空乏化したときの空間固定電荷の面密度が実質的に等しくなるトランジスタ構造とすることにより、リサーフ効果を持たせ、これにより、オン耐圧やオフ耐圧の向上を行う。

(もっと読む)

半導体装置及びその製造方法

【課題】素子分離層として拡散層を有する半導体基板の表面に搭載されるNPN型バイポーラトランジスタの信頼性を確保する構造を容易に得ることのできる半導体装置及びその製造方法を提供する。

【解決手段】当該半導体装置は、大きくは、CMOS20とNPN型バイポーラトランジスタ30とをN型のシリコンからなる同一の半導体基板(N−sub)11に備えている。このうち、CMOS20が搭載される領域では、フィールド酸化膜12c、12dの直下の領域に同領域の不純物濃度が高められるかたちで素子分離層としてのN型拡散層15a及びP型拡散層16aが形成されている。こうした半導体基板11の表面に、上記NPN型バイポーラトランジスタ30を形成し、そのベース領域(Pウェル14b)のうち、コレクタ領域と接合する接合部に同領域の不純物濃度を局所的に高く設定するかたちでP型拡散層16bを形成する。

(もっと読む)

半導体集積回路装置およびその製造方法

【課題】縦構造のバイポーラトランジスタを用い、コレクタの電極取り出しを基板の裏面側で行うことで、バイポーラトランジスタのデバイス面積を縮小化するとともに高速動作化を可能とする。

【解決手段】バイポーラトランジスタ100とMOS型トランジスタ200とを同一基板10に搭載した半導体集積回路装置1であって、バイポーラトランジスタ100は、エミッタ層120、ベース層110、コレクタ層130が基板10主面に対して垂直方向に配列されたものからなり、ベース層110に接続されるベース取り出し電極111が基板10の主面側に設けられ、エミッタ層120に接続されるエミッタ取り出し電極121が基板10の主面側に設けられ、コレクタ層130に接続されるコレクタ取り出し電極131が基板10の主面とは反対の裏面側に設けられたものである。

(もっと読む)

バイポーラトランジスタおよびバイポーラトランジスタの製造方法

【課題】ベースオープンUCE0で、高いコレクタ−エミッタ逆電圧UCE0および高いコレクタ−ベース逆電圧UCB0を有するバイポーラトランジスタを提供すること、およびその製造方法を明らかにすること。

【解決手段】本発明はNPNおよびPNPバイポーラトランジスタおよびその製造方法に関し、該トランジスタは特に高いコレクタ−エミッタおよびコレクタ−ベースの遮断電圧を特徴とする。遮断電圧は特殊なドーピングプロファイルによって増加する。NPNバイポーラトランジスタはpドープ基板(1)と、コレクタを形成するトレンチされたnドープ層(3)と、前記トレンチされたnドープ層の上に配置され、ベースから作られたpドープ層(7)と、前記pドープ層の内部に配置されてトランジスタのエミッタを形成するnドープ層とを有する。空間電荷領域(RLZ1)はpドープ層とトレンチされたnドープ層の間に形成され、第2の空間電荷領域(RLZ2)はトレンチされたnドープ層とpドープ基板の間に形成され、トランジスタが電位上昇で動作されるとき、コレクタ上を縦方向に広がる。トレンチされたnドープ層は、トランジスタが電位上昇で動作されるとき、第1および第2の空間電荷領域がコレクタ上に広がり、コレクタとエミッタ間が降伏の臨界電界強度に達する前に、トレンチされたnドープ層の深さ全体を横切るようなドーピングプロファイルを有する。

(もっと読む)

1 - 9 / 9

[ Back to top ]