Fターム[5F003BE04]の内容

バイポーラトランジスタ (11,930) | エミッタ (1,226) | バンドギャップ (158)

Fターム[5F003BE04]に分類される特許

1 - 20 / 158

半導体装置

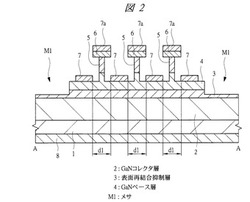

【課題】窒化物半導体を用いたメサ型の半導体装置のp型層の抵抗を低減する。また、窒化物半導体を用いたメサ型の半導体装置に高い値でばらつくオン抵抗が生じることを防ぐ。

【解決手段】窒化物半導体からなり、所定のベース電極間隔を有するヘテロ接合バイポーラトランジスタにおいて、GaNベース層4およびGaNコレクタ層2の間に表面再結合抑制層3を設け、GaNベース層4を貫通して表面再結合抑制層3の途中深さまで開口するメサM1を形成することでGaNベース層4を分離する。

(もっと読む)

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】断線等の問題を抑制しつつ逆メサの段差に配線を設けることができる半導体装置の製造方法を提供する。

【解決手段】エッチングにより半導体基板に逆メサ段差部を形成する。逆メサ段差部の下段における半導体基板の表面に、電極を設ける。逆メサ段差部内を埋めるように当該逆メサ段差部の高さよりも厚い絶縁膜を設ける。逆メサ段差部内に絶縁膜を残すように、絶縁膜積層工程で積層した絶縁膜に対してエッチバックを行う。電極に接続する配線を、逆メサ段差部に残された絶縁膜の上方に設ける。このとき、電極とのコンタクトをとる部分を対象にして、層間絶縁膜に対し開口を形成する。開口形成後、配線を、層間絶縁膜上であって逆メサ段差部の上方の領域に蒸着する。コンタクト開口を介して、配線が電極と接続する。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】成長時間を短縮してスループットを向上することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】基板2上に、電子供給層6,10及びチャネル層8を有する高電子移動度トランジスタ構造層3を形成する工程と、高電子移動度トランジスタ構造層3上に、コレクタ層14、ベース層15、エミッタ層16及びノンアロイ層18を有するヘテロバイポーラトランジスタ構造層4を形成する工程と、を有するトランジスタ用エピタキシャルウェハの製造方法において、ヘテロバイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下で、かつ、一定の成長温度で成長するようにした。

(もっと読む)

半導体装置およびその製造方法

【課題】ヘテロ構造のpn接合において、電子が妨げられることなく注入されるようにする。

【解決手段】Gaを含む窒化物半導体からなるn型の窒化物半導体層101と、窒化物半導体層101に接合して形成されたp型のシリコンからなるp型シリコン層102とを少なくとも備える。窒化物半導体層101とp型シリコン層102とは、接合界面103により接合している。

(もっと読む)

電子装置

【課題】カーボンによるバンドギャップ・エンジニアリングを可能とし、カーボン原子に基づく多彩なエレクトロニクスを達成して、信頼性の高い電子装置を実現する。

【解決手段】電子装置は、単層のグラフェン膜1と、グラフェン膜1上の両端に設けられた一対の電極2,3とを有しており、グラフェン膜1では、電極2,3間の領域において、中央部位のBC間が複数のアンチドット10が形成されてなる第1の領域1aとされており、第1の領域1aの両側におけるAB間及びCD間がアンチドットの形成されていない第2の領域1bとされている。

(もっと読む)

トランジスタ素子

【課題】単体構造のHBTデバイスと同等の信頼性を得る。

【解決手段】化合物半導体からなる、高電子移動度トランジスタ(HEMT)とヘテロバイポーラトランジスタ(HBT)とを、同一基板上に重ねてエピタキシャル成長した多層構造のトランジスタ素子において、エピ層として内在するインジウムガリウムリン層(InGaP)のバンドギャップエネルギを1.91eV以上にすることを特徴とする。

(もっと読む)

トランジスタ素子

【課題】n型不純物としてTeを用いたノンアロイ層を有していても、ベース電流、コレクタ電流のリーク電流が少ないトランジスタ素子を提供する。

【解決手段】基板11と、基板11上に設けられた高電子移動度トランジスタ構造層28と、高電子移動度トランジスタ構造層28上に設けられたヘテロバイポーラトランジスタ構造層29とを備えたトランジスタ素子10において、ヘテロバイポーラトランジスタ構造層29のノンアロイ層26,27は、n型不純物としてTeがドーピングされており、n型不純物濃度が1.0×1019cm-3以上2.0×1019cm-3以下にされているものである。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】コレクタメサ表面で発生するコレクタリーク電流を抑制し、微細なHBTのコレクタ耐圧特性を改善する。

【解決手段】第2サブコレクタ層103は、第1サブコレクタ層102より平面視で小さい面積に形成されている。また、コレクタ層104は、第2サブコレクタ層103を構成している半導体層132より平面視で大きい面積に形成されている。また、ベース層105は、コレクタ層104より平面視で小さい面積に形成されている。また、エミッタ層106は、ベース層105より平面視で小さい面積に形成されている。加えて、第2サブコレクタ層103を構成している半導体層132およびベース層105は、平面視でコレクタ層104の内側の領域に形成されている。

(もっと読む)

半導体装置およびその製造方法

【課題】InP系の微細構造デバイスをより効果的に冷却できるようにする。

【解決手段】主表面を(001)面としたInPからなる基板101の上にInGaAsからなるバッファ層102を形成し、バッファ層102の上に接して配置されたInPの層を含んでバッファ層102の上に形成されたデバイス103を形成し、デバイス103の周囲のバッファ層102を露出させた状態でデバイス103を覆う保護層104を形成し、露出したバッファ層102の上に金を堆積して金層105を形成し、次に、バッファ層102の表面に接触している金層105よりデバイス103の下部のバッファ層102に金を拡散させる。

(もっと読む)

半導体発光素子

【課題】平坦性が向上した半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成されたInGaNからなる多重井戸構造を備える活性層15とを備え、n型積層構造が、GaN層11と、GaN層11上に形成されたドープ層10と、ドープ層10上に設けられた窒化物系III−V族化合物半導体層12と、窒化物系III−V族化合物半導体層12よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】GaAsSb系の化合物半導体のベース層を有するInP系HBTで、大きな電流利得が得られるようにする。

【解決手段】コレクタ層102の上に形成されてGa,As,およびSbから構成された化合物半導体からなるベース層103と、ベース層103の上に接して形成されたスペーサ層104と、スペーサ層104の上に接して形成されてInおよびPから構成された化合物半導体からなるエミッタ層105とを備える。スペーサ層104は、ベース層103の伝導帯端のエネルギー準位よりも低く、エミッタ層105の伝導帯端よりも高い伝導帯端のエネルギー準位を有し、ベース層103の価電子帯端のエネルギー準位よりも低く、エミッタ層105の価電子帯端よりも高い価電子帯端のエネルギー準位を有した状態で、ベース層103およびエミッタ層105に接して形成されている。

(もっと読む)

半導体基板、半導体装置および半導体基板の製造方法

【課題】十分な感度を有したp型キャリアのホール素子の製造に適した半導体基板を提供する。

【解決手段】表面の全部または一部がシリコン結晶面であるベース基板と、前記ベース基板の上に位置し、前記シリコン結晶面に達する開口を有し、結晶の成長を阻害する阻害体と、前記開口の底部の前記シリコン結晶面の上に位置する第1結晶層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第1金属層と、前記第1結晶層の上に位置し、互いに離して配置した一対の第2金属層と、を有し、前記一対の第1金属層のそれぞれを結ぶ第1最短線と、前記一対の第2金属層のそれぞれを結ぶ第2最短線とが、交わる関係、または、ねじれの位置関係にある半導体基板を提供する。

(もっと読む)

バイポーラ半導体素子

【課題】表面欠陥の発生を低減できて積層欠陥の発生を抑制でき、オン電圧ドリフトを抑制できるSiCバイポーラ半導体素子を提供する。

【解決手段】このSiC pinダイオード20は、六方晶構造の炭化珪素半導体で作製され、メサ状の半導体層31が六角柱形状で6つの側面(メサ面)31Aをすべて{0m−m0}面(m,nは整数)とした。これにより、メサ面31Aに対する〈11−20〉方向のバーガーズベクトルBV1,BV2の角度θ1,θ2(図4)が、{11−20}面の素子表面(メサ面)に対するバーガーズベクトルBV101,BV102の角度θ101,θ102(図12)に比べて小さくなると共に表面欠陥が発生するのに必要なバーガーズベクトルBV1,BV2の長さが長くなる。これにより、メサ面31Aに表面欠陥SDが入り難くなり、メサ状の半導体層31の各メサ面31Aでの表面欠陥を低減できて、積層欠陥の発生を抑制できる。

(もっと読む)

トランジスタ用エピタキシャルウェハ

【課題】配管パージ等の作業を行うことなく、電気的特性等に影響を与える残留したTeやSeのエピタキシャル層中への混入を防止できるトランジスタ用エピタキシャルウェハを提供する。

【解決手段】基板100と化合物半導体層200とコンタクト層300とを有し、コンタクト層300は、n型不純物としてTe又はSeがドーピングされたIn組成比xが0.3≦x≦0.6で一定のn型InGaAs層からなり、n型InGaAs層は、n型不純物濃度が1.0×1019cm-3以上5.0×1019cm-3以下で、且つ、炭素濃度が1.0×1016cm-3以上3.0×1018cm-3以下であり、化合物半導体層200は、バッファ層400を備え、バッファ層400は、アンドープAlAs層からなる第1バッファ層401と、Al組成比yが0<y<1のアンドープAlGaAs層からなる第2バッファ層402とからなるものである。

(もっと読む)

トランジスタ用エピタキシャルウェハの製造方法

【課題】HEMTの移動度の低下を抑制することが可能なトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】高電子移動度トランジスタ構造層3を、気相成長法により成長温度600℃以上750℃以下、V/III比150以下の条件で成長し、バイポーラトランジスタ構造層4を、気相成長法により成長温度400℃以上600℃以下、V/III比75以下の条件で成長し、さらにノンアロイ層18を、380℃以上450℃以下の成長温度で成長する。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

ヘテロ接合バイポーラトランジスタ

【課題】電流利得や電流利得遮断周波数などの他の素子性能を劣化させることなく、ヘテロ接合バイポーラトランジスタのオン電圧が効果的に低減できるようにする。

【解決手段】基板101の上に、サブコレクタ層102、コレクタ層103、ベース層104、第1エミッタ層105、第2エミッタ層106、および、キャップ層107が順次積層されており、第2エミッタ層106は、第1エミッタ層105に対してウェットエッチング法により選択的に除去される半導体材料によって形成され、かつ、第2エミッタ層106を構成する半導体が不純物添加によって縮退している。加えて、このHBTの第1エミッタ層105は、ベース層104の側に配置されて不純物が添加された第1半導体層151と、第2エミッタ層106の側に第1半導体層151に接して配置されて不純物が無添加の第2半導体層152とから構成されている。

(もっと読む)

トランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法

【課題】GaAs基板からHBT構造層に伝搬する転位を抑制したトランジスタ素子及びトランジスタ用エピタキシャルウェハの製造方法を提供する。

【解決手段】GaAs基板2上に高電子移動度トランジスタ構造層3が形成され、高電子移動度トランジスタ構造層3上にヘテロバイポーラトランジスタ構造層4が形成されたトランジスタ素子において、GaAs基板2の転位密度が10,000/cm2以上100,000/cm2以下であり、高電子移動度トランジスタ構造層3とヘテロバイポーラトランジスタ構造層4との間に、InGaPからなるエッチングストッパ層12と、エッチングストッパ層12上に設けられたGaAsからなる安定化層21と、を設けたものである。

(もっと読む)

半導体発光素子

【課題】GaN基板上に結晶成長する各半導体層の平坦性向上した半導体基板を実現し、この半導体基板を基礎として、特性の高性能化された半導体発光素子を提供する。

【解決手段】p型電極32と、n型電極31と、p型電極32に接続され、複数のp型窒化物系III−V族化合物半導体からなるp型積層構造(16〜20)と、n型電極31に接続され、複数のn型窒化物系III−V族化合物半導体であるn型積層構造(11〜14)と、p型積層構造(16〜20)とn型積層構造(11〜14)との間に形成された窒化物系III−V族化合物半導体からなる活性層15とを備え、n型積層構造(11〜14)がSiを5x1017cm-3以上2x1019cm-3以下の濃度で含有し、厚さが0.3nm以上200nm以下のドープ層10と、ドープ層10よりも活性層15側に設けられた超格子層13とを含む。

(もっと読む)

1 - 20 / 158

[ Back to top ]