Fターム[5F003BG05]の内容

バイポーラトランジスタ (11,930) | ベース・コレクタ接合 (410) | Jc接合 (217)

Fターム[5F003BG05]の下位に属するFターム

Fターム[5F003BG05]に分類される特許

1 - 9 / 9

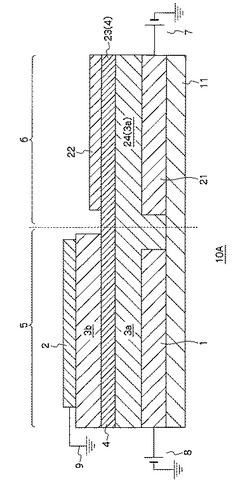

有機トランジスタ、回路素子及びそれらの製造方法

【課題】低電圧で作動するとともに大きなベース電圧を印加した場合でも耐電圧が高く、各種の回路素子への応用が容易で、製造コストを抑えた有機トランジスタ及び回路素子を提供する。

【解決手段】コレクタ電極1とエミッタ電極2と両電極間に設けられた有機半導体層3と有機半導体層3内に設けられたベース電極4とを有する縦型トランジスタ部、及び、ベース電極4とベース電圧電源端子7との間に設けられた抵抗部6、を有する。抵抗部6は、コレクタ電極1と同じ材料からなりベース電圧電源端子7に接続する第1電極21と、エミッタ電極2と同じ材料からなりベース電極4に接続する第2電極22と、有機半導体層3と同じ材料からなり第1電極21及び第2電極22間に挟まれた抵抗層24とを有する。

(もっと読む)

駆動素子アレイ及びその製造方法並びに表示装置

【課題】大電流を含む変調電流で発光素子を低電圧駆動させることができるとともに、製造コストの点でも有利な駆動素子アレイを提供する。

【解決手段】パッシブマトリクス方式で電流駆動する発光素子21と、その発光素子21への電流供給を制御するカラム選択用トランジスタ31A及びライン選択用トランジスタ31Bとを有する駆動素子アレイ10であって、そのカラム選択用トランジスタ31Aとライン選択用トランジスタ31Bを、発光素子21と同一の基板19上に形成された縦型有機トランジスタであるように構成して上記課題を解決した。この縦型有機トランジスタ31A,31Bは、電流変調を容易に行うことができ、特に大面積の表示装置に用いる場合には大電流を発光素子列に供給することができる。さらに、縦型有機トランジスタ31A,31Bには、光吸収層又は光反射層を施す等の遮光処理がなされていることが好ましい。

(もっと読む)

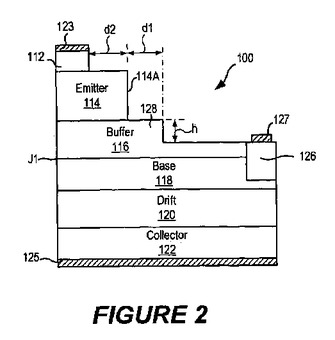

メサ構造とメサ段差を含むバッファ層とを備えた電力半導体デバイス

バイポーラ接合トランジスタが、第1の導電型を有するコレクタと、このコレクタ上の、第1の導電型を有するドリフト層と、このドリフト層上の、第1の導電型と反対の第2の導電型を有するベース層と、このベース層上の、低濃度でドープされ第1の導電型を有しベース層とp−n接合部を形成するバッファ層と、このバッファ層上の第1の導電型を有し側壁を有するエミッタメサとを含む。バッファ層は、エミッタメサの側壁の近傍でそこから横方向に間隔を置いて配置されたメサ段差を含み、エミッタメサの下のバッファ層の第1の厚さは、メサ段差外側のバッファ層の第2の厚さよりも厚い。  (もっと読む)

(もっと読む)

半導体装置とその製造方法

【課題】 複数個の半導体素子を備えている半導体装置において、その半導体装置のサイズを小さくする技術を提供する。

【解決手段】 不純物注入工程では、半導体基板9の表面にn型半導体領域13とp型半導体領域14が隣接して出現する関係に不純物の注入範囲を管理して、不純物を半導体基板9に注入する。熱処理工程では、半導体基板9を加熱して半導体基板9に注入した不純物12、14を活性化する。トレンチ形成工程では、半導体基板9の表面に隣接して出現しているn型半導体領域13とp型半導体領域14の双方を分断して一巡するととともに半導体基板9の表面から半導体基板9の裏面に向けて不純物の注入範囲12、14を貫通する深さにまで伸びているトレンチ15を形成する。絶縁膜形成工程では、トレンチ15内に絶縁膜を形成する。

(もっと読む)

ホットエレクトロントランジスタおよびそれを含む半導体装置

【課題】期待される高周波特性を得ること、ならびに後続の回路で必要とされる駆動電流を得ることが可能なホットエレクトロントランジスタを提供する。

【解決手段】このホットエレクトロントランジスタ100は、コレクタ層3と、ベース層5と、エミッタ層7と、コレクタ層3とベース層5との間に形成されたコレクタバリア層4と、ベース層5とエミッタ層7との間に形成されたエミッタバリア層6とを備えている。そして、エミッタバリア層6とエミッタ層7との間のエネルギー障壁は実質的に存在しないとともに、コレクタバリア層4のエネルギー障壁の高さはエミッタバリア層6のエネルギー障壁の高さよりも低い。

(もっと読む)

略自然降伏デバイス

【課題】 バイアス電圧が印加されるときに半導体デバイス上に自然降伏状態を作り出すような「略自然降伏状態」を提供する。

【解決手段】 本発明の半導体デバイスは第1半導体領域を含み、第1半導体領域は、強制または非強制略自然降伏領域であり、この領域は、非自然降伏(例えば、ツェナー降伏及び雪崩降伏)の降伏電圧以下の大きさを有する所定電圧がデバイスの両端に印加されるときに完全に空乏化される。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、パワー用半導体素子の耐圧特性と制御用半導体素子のデバイスサイズの縮小化とを実現することが難しいという問題があった。

【解決手段】本発明の半導体装置では、P型の単結晶シリコン基板3上にN型のエピタキシャル層4が形成されている。基板3とエピタキシャル層4には、N型の埋込拡散層9がP型の埋込拡散層6上に形成されている。この構造により、P型の埋込拡散層6の這い上がりが抑制され、パワー用半導体素子の耐圧特性を維持しつつ、エピタキシャル層4の厚みを薄くすることができる。そして、制御用半導体素子のデバイスサイズを縮小化することができる。

(もっと読む)

半導体装置及びその製造方法

【課題】 ダブルヘテロバイポーラトランジスタにおいて、高い耐圧を保ったまま伝導帯における障壁の発生を回避し、高電流において高速なトランジスタ動作を可能とする半導体装置及びその製造方法を提供する。

【解決手段】 ベースとコレクタの一部を、半導体基板より禁制帯幅の狭い材料で形成し、ベース内部にはエミッタ側からコレクタ側に向かって階段状又は連続的に禁制帯幅が増大する領域を設け、且つベース−コレクタ界面における禁制帯幅は、ベース中で最小となる禁制帯幅に比べて大きくなるように設計する。エミッタ−ベース近傍でのヘテロ効果を十分に保ったまま、従来よりもコレクタ側のベース層端における禁制帯幅を半導体基板の禁制帯幅に近づけることが出来、コレクタ電流が増大した際に生じるエネルギー障壁の高さを低減し、高電流での良好なトランジスタ動作が可能となる。

(もっと読む)

半導体装置、ドライバ回路及び半導体装置の製造方法

【課題】トランジスタのしきい値電圧の上昇を抑えつつ、その耐圧を向上することが可能な半導体技術を提供する。

【解決手段】SOI基板4におけるn-型の半導体層3にはpチャネル型のMOSトランジスタ20のソース領域5及びドレイン領域6が形成されている。また、半導体層3内にはn型の不純物領域9が形成されている。不純物領域9は、ソース領域5の直下においてその底部の全領域に渡って形成され、ソース領域5とドレイン領域6との間の半導体層3の直下にも形成されている。ソース領域5とドレイン領域6との間の半導体層3における上面の直下では、不純物領域9における不純物濃度のピーク位置9aは、ソース領域5の最下端5aよりも下方に設定されている。

(もっと読む)

1 - 9 / 9

[ Back to top ]