Fターム[5F003BP11]の内容

バイポーラトランジスタ (11,930) | 製法 (1,830) | エッチング (502)

Fターム[5F003BP11]の下位に属するFターム

イオンエッチング、プラズマエッチング (38)

エッチング方法 (1)

異方性エッチング (71)

多工程のエッチング方法 (270)

Fターム[5F003BP11]に分類される特許

1 - 20 / 122

半導体装置の製造方法

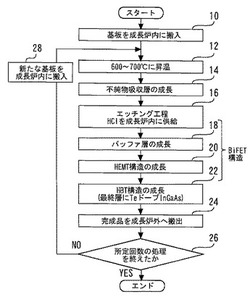

【課題】本発明は、基板に元々付着していた不純物及び成長炉内の不純物を低減することができる半導体装置の製造方法を提供することを目的とする。

【解決手段】本発明に係る半導体装置の製造方法は、基板を成長炉内に搬入する搬入工程と、該基板の上と該成長炉の内壁に、該基板表面と該成長炉内の不純物を吸収する不純物吸収層を形成する吸収層形成工程と、該不純物吸収層と、該基板の一部とをエッチングすることで該基板を薄化基板にするエッチング工程と、該薄化基板の上にバッファ層を形成するバッファ層形成工程と、該バッファ層の上に半導体層を形成する半導体層形成工程と、を備えたことを特徴とする。

(もっと読む)

窒化物半導体素子の製造方法

【課題】ドレインリーク電流を低減することが可能な窒化物半導体素子の製造方法を提供する。

【解決手段】ヘテロ電界効果トランジスタ1の製造方法は、ドリフト層20aを支持基板10上にエピタキシャル成長させる工程と、水素ガスをキャリアガスとして用いて、p型半導体層である電流ブロック層20bをドリフト層20a上に1000℃以上でエピタキシャル成長させる工程と、窒素ガス、アルゴンガス、ヘリウムガス及びネオンガスからなる群より選ばれる少なくとも一種のガスをキャリアガスとして用いて、コンタクト層20cを電流ブロック層20b上にエピタキシャル成長させる工程と、を備える。

(もっと読む)

半導体装置及びその製造方法

【課題】MIMキャパシタの耐圧低下や耐湿劣化を防ぐことができる半導体装置及びその製造方法を得る。

【解決手段】半導体基板1上にベース電極4を形成する。ベース電極4を覆うようにレジスト膜5を形成する。レジスト膜5をマスクとした等方性エッチングにより、ベース電極4の周辺の半導体基板1を掘り込んでベースメサ溝6を形成する。ベース電極4上に絶縁膜7を形成する。絶縁膜7上に配線電極8を形成する。レジスト膜5の外周とベース電極4の外周との最小幅wは、ベースメサ溝6がベース電極4の下に入り込まないような値に設定されている。

(もっと読む)

半導体基板、電子デバイスおよび半導体基板の製造方法

【課題】エピタキシャル成長により形成された結晶膜の成長面内における物性値を均一な値に近づける。

【解決手段】第1化合物半導体および第2化合物半導体を積層した積層半導体を含み、前記第1化合物半導体の所定物性値が第1面内分布を有し、前記第2化合物半導体の前記所定物性値が前記第1面内分布とは異なる第2面内分布を有し、前記積層半導体における前記所定物性値の面内分布の幅が、前記第1面内分布の幅または前記第2面内分布の幅より小さい半導体基板を提供する。

(もっと読む)

増大した直線性および製造可能性を有するFETを含むBiFET

【課題】基板上に位置するBiFETにおいて、HBT性能の低下を引起すことなくFETの製造可能性増大を達成させる。

【解決手段】基板上に位置するBiFET100は、基板の上に位置するエミッタ層部分122を含み、エミッタ層部分は第1のタイプの半導体を含む。HBTはエッチストップ層の第1の部分126をさらに含み、エッチストップ層の第1の部分はInGaPを含む。BiFETは基板の上に位置するFET106をさらに含み、FETはソース領域およびドレイン領域を含み、エッチストップ層の第2の部分146はソース領域およびドレイン領域の下に位置し、エッチストップ層の第2の部分はInGaPを含む。FETはエッチストップ層の第2の部分の下に直接接して位置する第2のタイプの半導体層をさらに含む。エッチストップ層はFETの線形性を増大させ、HBTの電子の流れを低下させない。

(もっと読む)

半導体基板

【課題】AlGaAs/InGaP界面の遷移層の形成を抑制する。

【解決手段】ヒ素化合物からなる第2半導体と、リン化合物からなる第3半導体とを含み、前記第2半導体と前記第3半導体とが接触しており、前記第2半導体が第1原子を第2濃度で含有し、かつ第2原子を含有し、前記第1原子が前記第2半導体に第1伝導型のキャリアを発生させ、前記第2濃度が、前記第2半導体にドープする前記第1原子の量を増加するに従い増加するキャリア数が飽和し始める前記第1原子の濃度以上の濃度であり、前記第2原子が前記第2半導体におけるフェルミ準位と電荷中性準位との差を小さくする半導体基板提供する。

(もっと読む)

ヘテロ接合バイポーラトランジスタおよびその製法

【課題】高い電流増幅率を有し、高周波特性および素子寿命に優れたヘテロ接合バイポーラトランジスタおよびその製法を提供すること。

【解決手段】半絶縁性基板1上に、n型半導体より成る真性エミッタ層16と、p型ドーパントを高濃度でドーピングされ、真性エミッタ層16よりも狭いバンドギャップを有する半導体より成るベース層9と、ベース層9と同じ半導体より成るコレクタ層10とを、この順序で積層して成るへテロ接合バイポーラトランジスタにおいて、真性エミッタ層16の周囲に、高抵抗領域15が設けられ、高抵抗領域15と真性エミッタ層16との間に、真性エミッタ層16の半導体と同じ半導体から成るガードリング領域17が設けられ、真性エミッタ層16とベース層9との接合面が、ガードリング領域17の上面よりも下に位置することを特徴とするヘテロ接合バイポーラトランジスタを構成する。

(もっと読む)

半導体装置及びその製造方法

【課題】III-V族窒化物半導体に設けるオーミック電極のコンタクト抵抗を低減しながらデバイスの特性を向上できるようにする。

【解決手段】半導体装置(HFET)は、SiC基板11上にバッファ層12を介在させて形成された第1の窒化物半導体層13と、該第1の窒化物半導体層13の上に形成され、該第1の窒化物半導体層13の上部に2次元電子ガス層を生成する第2の窒化物半導体層14と、該第2の窒化物半導体層14の上に選択的に形成されたオーム性を持つ電極16、17とを有している。第2の窒化物半導体層14は、底面又は壁面が基板面に対して傾斜した傾斜部を持つ断面凹状のコンタクト部14aを有し、オーム性を持つ電極16、17はコンタクト部14aに形成されている。

(もっと読む)

化合物半導体素子及びその製造方法

【課題】高速動作が可能でかつ、ESD耐性の高い化合物半導体素子及びその製造方法を提供すること。

【解決手段】本発明に係る化合物半導体素子は、電界効果トランジスタ又はヘテロ接合バイポーラトランジスタからなるトランジスタ部と、トランジスタ部と並列に接続されたESD保護部114と、を備え、ESD保護部114は、第1導電型の不純物を含有する第1及び第2の半導体層109、113と、第1及び第2の半導体層109、113の間に形成され、第1及び第2の半導体層109、113の禁制帯幅よりも禁制帯幅が広く、かつ、不純物濃度が1×1017cm−3以下である第3の半導体層111と、を備えるものである。

(もっと読む)

バイポーラトランジスタ及びその製造方法

【課題】バイポーラトランジスタにおいて、耐圧改善のためにコレクタ濃度を低くした際のトランジスタとしての性能低下を抑制する。

【解決手段】バイポーラトランジスタ100は、コレクタ層3上に、エピタキシャル成長されたヘテロ接合の真性ベース層50を有する。真性ベース層50は、分離層4に囲まれたコレクタ層3上に配置され、コレクタ層3の表面部に、N型不純物層30が形成されている。N型不純物層30の不純物濃度は、N型不純物層30の下方におけるコレクタ層3の不純物濃度よりも高い。N型不純物層30と真性ベース層50との間に、N型不純物層30及び真性ベース層50よりも不純物濃度が低いエピタキシャル成長層が形成されている。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、SixGe1−x結晶層(0≦x<1)とをこの順に有する半導体基板であって、SixGe1−x結晶層(0≦x<1)は少なくとも一部の領域がアニールされており、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体を備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられて少なくとも一部の領域がアニールされたSixGe1−x結晶層(0≦x<1)と、少なくとも一部の領域でSixGe1−x結晶層(0≦x<1)に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

半導体基板、電子デバイス、および半導体基板の製造方法

【課題】安価なSi基板に化合物半導体の結晶薄膜を形成する。

【解決手段】ベース基板と、絶縁層と、Si結晶層とをこの順に有する半導体基板であって、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体とを備える半導体基板を提供する。また、サブストレートと、サブストレート上に設けられた絶縁層と、絶縁層上に設けられたSi結晶層と、Si結晶層上に設けられてアニールされたシード結晶と、シード結晶に格子整合または擬格子整合している化合物半導体と、化合物半導体を用いて形成された半導体デバイスとを備える電子デバイスを提供する。

(もっと読む)

ヘテロ接合バイポーラトランジスタ及びその製造方法

【課題】耐破壊性に優れたヘテロ接合バイポーラトランジスタを提供する。

【解決手段】サブコレクタ層と、第1コレクタ層、第2コレクタ層、第3コレクタ層及び第4コレクタ層を有しサブコレクタ層上に形成されたコレクタ層と、コレクタ層上に形成されたベース層と、ベース層上に形成され、ベース層を構成する半導体よりも大きなバンドギャップを有する半導体から構成されるエミッタ層とを備え、第1コレクタ層は、第2コレクタ層、第3コレクタ層及び第4コレクタ層を構成する半導体と異なる半導体から構成されてサブコレクタ層上に形成され、第4コレクタ層は、第2コレクタ層の不純物濃度よりも低い不純物濃度で第1コレクタ層上に形成され、第2コレクタ層は、サブコレクタ層の不純物濃度よりも低く第3コレクタ層の不純物濃度よりも高い不純物濃度で第4コレクタ層上に形成され、第3コレクタ層は、第2コレクタ層とベース層との間に形成される。

(もっと読む)

半導体装置及びその製造方法

【課題】ボンディングパッドの剥がれを防止し、かつボンディングパッド間におけるリーク電流の発生を防止することができる半導体装置及びその製造方法を提供すること。

【解決手段】HBT(ヘテロ構造バイポーラトランジスタ)が構成要素の1つとして集積された半導体装置110は、半絶縁性InP基板11上に、順次、エッチングストップ層12、コレクタコンタクト層13、コレクタ層14、傾斜コレクタ層15、セットバック層16、ベース層17が形成された構成を有し、ベース層17はInGaAsで構成された薄膜であってPを含まず、このベース層17上にSiN23が形成され、SiN23上にボンディングパッド25が形成された構成を有する。

(もっと読む)

バイポーラトランジスタの製造方法

【課題】最終的なコレクタを薄層化しつつ、広い線幅のSiO2細線を例とする絶縁物細線の埋め込みを可能にし、低消費電力での超高速動作が可能なバイポーラトランジスタの製造方法を提供すること。

【解決手段】半絶縁性基板1上にサブコレクタ層2を形成する工程と、サブコレクタ層2上に絶縁物3の細線を形成する工程と、サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程とを有するバイポーラトランジスタの製造方法において、前記サブコレクタ層2および絶縁物3の細線を覆うコレクタ層4を形成する工程は、コレクタ層2の表面をエッチングする工程を含むことを特徴とするバイポーラトランジスタの製造方法を構成する。

(もっと読む)

シリコン基板上に形成されるCMOSデバイスおよびIII−V族デバイスのための電気コンタクト

半導体構造体は、基板(12)と、基板を覆うシード層(13)と、シード層上に配置されるシリコン層(22)と、シリコン層中のトランジスタデバイス(27)と、シード層上に配置されるIII−V族デバイスと、複数の電気コンタクトと、を備え、それぞれの電気コンタクトは、TiNまたはTaNの層(32)と、TaNまたはTiNの層上の銅またはアルミニウムの層(34)と、を備え、電気コンタクトの1つは、トランジスタ(27)に電気的に接続され、電気コンタクトの別の1つは、III−V族デバイスに電気的に接続される。 (もっと読む)

ショットキーバリア量子井戸共振型トンネルトランジスタ

【課題】ショットキーバリア量子井戸のトンネルトランジスタを提供する。

【解決手段】素子構造は、一つ或は複数の導電ベースリージョン33、第一半導体バリアーリージョン、第二半導体バリアーリージョン、導電エミッタリージョン31、導電コレクタリージョン35などを含み、第一半導体バリアーリージョン或は第二半導体バリアーリージョンのサイズは100Åより小く、第一ショットキーバリアの接合を第一半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第二ショットキーバリアの接合を第二半導体バリアーリージョンと導電ベースリージョンのインターフェイスで生じ、第三ショットキーバリアの接合を導電エミッタリージョンと第一半導体バリアーリージョンのインターフェイスで生じ、第四ショットキーバリアの接合を導電コレクタリージョンと第二半導体バリアーリージョンのインターフェイスで生じる。

(もっと読む)

半導体装置及びその製造方法

【課題】本発明は、半導体装置及びその製造方法等に関し、バイポーラトランジスタの面積を縮小してトランジスタの高集積化が可能な半導体装置及びその製造方法等提供する。

【解決手段】本発明に係る半導体装置及びその製造方法は、第1導電型半導体にベース領域6を形成後、第1のシリコン窒化膜8及びシリコン酸化膜9を形成する。シリコン酸化膜に溝を形成し、第2のシリコン窒化膜10を形成する。第1及び第2のシリコン窒化膜をエッチバックすることでカバー膜10aを形成する。溝の底面上及びカバー膜の内側にポリシリコンエミッタを形成し、第3のシリコン窒化膜13を形成する。第3のシリコン窒化膜及びカバー膜をマスクとして自己整合的にシリコン酸化膜をエッチングすることで、カバー膜の周囲に位置し且つ前記ベース領域上に位置する開口部を形成し、ベース領域を露出させ、導電膜17aを形成する工程とを具備することを特徴とする。

(もっと読む)

半導体ウエハのエッチング方法及びそのエッチング装置

【課題】半導体装置の製造方法に関し、特に半導体ウエハの枚葉処理における湿式エッチング装置のクリーンルーム占有床面積の拡大を防止し、生産性の向上を図ること、並びにそれに伴う歩留改善、間接材料の使用量低減可能な作業方法の確立を図る。

【解決手段】本発明の半導体ウエハ1のエッチング方法は、半導体ウエハ1を床面に対して垂直に保持した状態でエッチングするもので、吸着チャック10に垂直に保持された半導体ウエハ1と垂直状態で相対するエッチング機構13の正面部17並びに凸部18の間に、上から下に流れる落ちるエッチング液による薬液層19を形成しつつ、半導体ウエハ1を低速回転させながらエッチングする。

(もっと読む)

1 - 20 / 122

[ Back to top ]