Fターム[5F033MM00]の内容

半導体集積回路装置の内部配線 (234,551) | 配線構造、形状の特徴点 (15,803)

Fターム[5F033MM00]の下位に属するFターム

埋め込み型配線、ダマシン (3,807)

配線の断面構造 (9,197)

配線の断面形状 (637)

配線の平面形状 (698)

表面状態 (80)

膜厚の異なる複数の配線を有するもの (89)

線幅の異なる複数の配線を有するもの (161)

基板内部や裏面に配線が有るもの (1,122)

Fターム[5F033MM00]に分類される特許

1 - 12 / 12

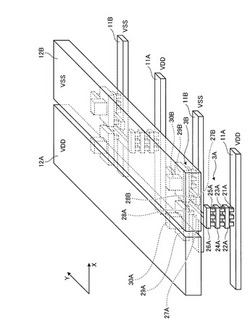

半導体集積回路、半導体集積回路の設計方法、および半導体集積回路の設計装置

【課題】配線層に形成される信号配線をなるべく迂回させずに配線できるように電源スタックビアが配置された半導体集積回路を提供すること。

【解決手段】半導体集積回路は、第1の方向に延伸された第1,第2の下層電源配線11A,11Bと、第2の方向に延伸された第1,第2の上層電源配線12A,12Bと、上層,下層電源配線を接続させる第1,第2接続部3A,3Bと、を備え、第1,第2接続部は、第1,第2の接続用配線26A,26Bと、第1,第2の位置変換用配線27A,27Bと、第1,第2の上側ビア28A,28Bと、を有して構成され、第1,第2の接続用配線は、第2の方向に沿った同一ライン上に配置され、第1,第2の位置変換用配線は、第1,第2の接続用配線を第2の方向に沿って延長した領域内に形成され、第1,第2の上側ビアは、第1の方向に沿った同一ライン上となる位置に配置される。

(もっと読む)

表示装置、電子機器

【課題】アクティブマトリクス型の液晶表示装置の画面の大面積化を可能とするゲート電

極とゲート配線を提供することを第1の課題とする。

【解決手段】同一基板上に表示領域と、表示領域の周辺に設けられた駆動回路と、を有し

、表示領域は、第1の薄膜トランジスタを有し、駆動回路は、第2の薄膜トランジスタを

有し、第1の薄膜トランジスタと第2の薄膜トランジスタは、リンがドープされたシリコ

ンでなるゲート電極を有し、ゲート電極は、チャネル形成領域の外側に設けられた接続部

でアルミニウムまたは銅を主成分とする層とタンタル、タングステン、チタン、モリブデ

ンから選ばれた少なくとも1種を主成分とする層とを有する配線と電気的に接続する。

(もっと読む)

整列したナノ構造物を含む回路基板

【課題】 整列したナノ構造物を含む回路基板を提供する。

【解決手段】 回路基板は、基板と、基板に配置された極性分子層パターンおよび非極性分子層パターンと、基板に配置された第1の電極および第2の電極と、極性分子層パターンに配置され、線状ナノ構造物を含む1つ以上のチャネルとを含む。1つ以上のチャネルは、第1の電極を第2の電極に電気的に結合するのを促す。

(もっと読む)

半導体チップ、光電変換チップおよび半導体チップの製造方法

【課題】衝撃や振動になどに対して強度を向上させることで高い信頼性が得られる半導体チップ、光電変換チップおよび半導体チップの製造方法を提供する。

【解決手段】半導体基板2と、受光部3および制御回路部4とを形成する集積回路と、前記半導体基板2の側面に形成され、半円筒形状に形成された外部端子5と、底面を除く全体を覆う樹脂封止部6とを備えた光電変換チップ1は、プリント配線基板に搭載する場合に、ワイヤによる接続が不要なので、ワイヤボンディング工程が不要である。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗素子として機能する配線を有し、かつ面積の小さな半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、半導体基板SBと、半導体基板SB上に設けられた第2の配線層L2とを備えている。第2の配線層L2は、通常の配線WRと、高抵抗配線REと、通常の配線WRおよび高抵抗配線REを埋め込む絶縁膜8とを含んでいる。通常の配線WRは、第1の銅部10Wと、第1の銅部10Wの底面側および側面側を覆う第1のバリアメタル膜9Wとを有している。高抵抗配線REは、空洞部CVと、空洞部CVの底面側および側面側を覆う第2のバリアメタル膜19Rとを有している。

(もっと読む)

配線、電子装置及び電子装置の製造方法

【課題】抵抗を低減することが可能な配線を提供する。

【解決手段】第1導電膜12と第1導電膜12の上層の第2導電膜26とを電気的に接続する配線24であって、第1導電膜12の上の複数の第1金属粒子16と、複数の第1金属粒子16のそれぞれを介して第1導電膜12の表面に一端を接続する複数の導電部材18と、複数の導電部材18のそれぞれの他端側の側面上の複数の第2金属粒子20と、複数の第2金属粒子20のそれぞれを介して複数の導電部材18のそれぞれの表面に一端を接続し、第2導電膜26にそれぞれ接続する複数の導電部材22とを備える。

(もっと読む)

側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージ

【課題】側面パッドを備えるチップ、その製造方法及びそのチップを利用したパッケージを提供する。

【解決手段】上部表面、下部表面及び上部表面と下部表面とに連結された側部表面を持つ第1チップ100を備える半導体装置であり、第1チップは、チップ基板、チップ基板上の下部導電性パターン、下部導電性パターン上の層間誘電層及び層間誘電層上の上部導電性パターンを備え、下部導電性パターン120bの少なくとも一部及び上部導電性パターンの少なくとも一部は、集合的に側面パッド120を形成するように第1チップの側部表面上に露出される。

(もっと読む)

半導体装置

【課題】半導体装置の保護膜にクラックが入ることを防止した半導体装置を提供すること。

【解決手段】GaAs基板11上にキャパシタを形成予定の場所に対して、約1μmの深さを持つ凹部12を形成する。その上部にキャパシタ下部電極13としてAl配線層を形成する。この下部電極層13は凹部12の側壁に対して接続するように形成し、その上部にキャパシタとして動作させるための誘電体14としてSiNを形成する。その上部に上部電極15を形成してキャパシタが形成できる。GaAs基板11に凹部があるので、昇温降温を行うプロセスにおけるAlスライドによって誘電体14にクラックが生じない。

(もっと読む)

半導体装置およびその製造方法

【課題】抵抗特性が改善され、信頼性が向上する半導体装置およびその製造方法を提供する。

【解決手段】半導体装置は、下部配線110、層間絶縁膜100、200、拡散防止膜120、240、上部配線230を備えている。層間絶縁膜200は、下部配線110上に形成され、下部配線110の上面が露出するビアホール230aを有する。拡散防止膜240は、ビアホール230aの両側壁に形成される。上部配線230は、ビアホール230aを埋め込み、下部配線110と直接接触する。下部配線110内にはビアホール230aの延びる方向に拡散防止膜120の成分を含む不純物領域130が形成される。

(もっと読む)

半導体装置およびその製造方法

【課題】小型化または外部端子数の増加に伴う、電気接続性の劣化が抑制された半導体装置を提供する。

【解決手段】半導体装置は、半導体基板1と、半導体基板1の一方の主面に設けられた素子電極2と、半導体基板1の一方の主面側に配置された絶縁層4と、素子電極2と電気接続され、絶縁層4に接して配置された配線7とを含み、絶縁層4は凸部4aを備え、配線7の一方の端部は素子電極2に接合され、他方の端部は凸部4aの上面4bに配置されてランド部を構成している。

(もっと読む)

配線構造、表示装置および能動素子基板

【課題】 パターニングフリーの能動素子基板の提供。

【解決手段】 能動素子基板は、基板上に形成された能動素子1と、能動素子1上に形成された導電膜2とを有する。導電膜2は、能動素子1から出力された電気信号を有限範囲内に伝達する。

(もっと読む)

高周波用伝送線路およびその製造方法

【課題】 比抵抗の低い半導体基板の上であっても、その上に形成した高周波用伝送線路の伝送損失を抑制できるようにする。

【解決手段】 信号線103およびグランド線104と半導体基板101との間に介在する絶縁膜102と、信号線103の両側の半導体基板101に形成された溝105とを備え、信号線103およびグランド線105は、半導体基板101に接している辺より半導体基板101に垂直な隣辺の方が長い長方形状の断面を有する。

(もっと読む)

1 - 12 / 12

[ Back to top ]