Fターム[5F033WW01]の内容

半導体集積回路装置の内部配線 (234,551) | 数値の特定 (5,273) | 長さ、寸法 (1,572)

Fターム[5F033WW01]の下位に属するFターム

厚さ (759)

Fターム[5F033WW01]に分類される特許

1 - 20 / 813

半導体ウェハ、半導体装置及びその製造方法

半導体ウェハ、半導体装置及びその製造方法

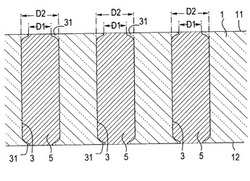

縦導体充填構造

【課題】ウエハ等の基板に設けられた縦孔内に、脱落、抜け等を生じることなく、完全充填された縦導体充填構造を提供すること。

【解決手段】基板1の厚み方向に設けられた縦孔3内に縦導体5を充填した縦導体充填構造であって、孔開口端が内側に突出する凸縁31となっており、凸縁31−31間で見た孔径D1が、孔内壁面3−3間で見た内径D2よりも小さい。

(もっと読む)

配線及び半導体装置

【課題】実施形態は、多層グラフェンの配線及び多層グラフェン配線を有する半導体装置を提供することを目的とする。

【解決手段】実施形態にかかる配線は、基板と、基板上に設けられた金属膜と、記金属膜上に設けられた金属部と、金属部に形成されたグラフェン配線とを有し、前記グラフェン配線は、前記金属膜と電気的に接続し、金属膜と金属部は、異なる金属または合金であることを特徴とする。

(もっと読む)

半導体装置および半導体装置の製造方法

【課題】貫通電極が絶縁膜で被覆されていようがいまいが、貫通電極と配線の接触面積を確保すること。

【解決手段】本実施形態に係る半導体装置は、第1の半導体チップ200と、第1の半導体チップ200上に積層された第2の半導体チップ300と、第1の半導体チップ200と第2の半導体チップ300とを接続する貫通電極120と、を有している。貫通電極120は、第1の貫通電極部122と第2の貫通電極部124を有している。第1の貫通電極部122は、第2の半導体チップ300において、第2の絶縁膜42の上面から第2の配線32の上部まで設けられている。第2の貫通電極部124は、第1の貫通電極部122の下面と繋がっており、かつ第2の配線32と同一層から第2の半導体チップ300の第1の配線30上部まで設けられている。第1の貫通電極部122と第2の貫通電極部124の孔径は、平面視で、第1の貫通電極部122の孔径の方が大きい。

(もっと読む)

パターン形成方法

【課題】微細なパターン、例えば、線幅が50μmよりも小さいパターンであっても高い精度でパターンを形成することができるパターン形成方法を提供する。

【解決手段】微細なパターンのパターン形成方法であって、基板上に形成された、親疎水性変換機能を有する第1の膜において、パターンが形成されるパターン形成領域を親疎水性に変化させる工程と、パターン形成領域に第2の膜を形成し、第2の膜が乾燥してパターンを形成する工程とを有する。第2の膜は、厚さが0.1μmになったときの粘度が3mPa・s以下である。

(もっと読む)

基板貫通バイアを有する半導体構造および製造方法

【課題】基板を貫通するバイアホールを与える。

【解決手段】半導体デバイス構造は、第1の濃度および第1の導電型のバックグラウンドドーピングを有する基板を含んでなる。基板貫通バイアは基板を貫通している。デバイスは基板の第1の面上に第2の導電型の第1のドープ領域を有する。第2のドープ領域が基板貫通バイアの周りにある。第2のドープ領域は、第1の濃度よりも大きい第2の濃度にドーピングされており、第1の導電型を有する。

(もっと読む)

銅及びモリブデンを含む多層膜用エッチング液

【課題】

銅及びモリブデンを含む多層膜用エッチング液、及びこれを用いた銅及びモリブデンを含む多層膜のエッチング方法を提供する。

【解決手段】

(A)分子内にカルボキシル基を二つ以上有し、かつヒドロキシル基を一つ以上有する有機酸イオン供給源、(B)銅イオン供給源、及び(C)アンモニア及び/又はアンモニウムイオン供給源を配合してなり、pHが5〜8であり、(C)アンモニア及び/又はアンモニウムイオン供給源の(B)銅イオン供給源に対する配合比(モル比)が0.1〜20である銅及びモリブデンを含む多層膜用エッチング液、及びこれを用いたエッチング方法である。

(もっと読む)

配線構造及びその製造方法

【課題】配線間の絶縁性に優れ信頼性の高い配線構造及びその製造方法を提供する。

【解決手段】スピンコート法により、ベースポリマーがポリイミド樹脂である非感光性樹脂のワニスを塗布後、ベーク、キュアしてポリイミド樹脂を硬化、膜を形成する。これを第1絶縁膜12とする。次いで、めっきシード層18形成、フォトレジスト溝パターン22形成、めっき、フォトレジスト溝パターン22除去、配線下以外のめっきシード層18除去に依り、第1の絶縁膜上に配線26を形成する。そして、第1絶縁膜の表面上にシリカ粒子30を分散し、散したシリカ粒子30をマスクとして、CF4及びO2を混合したガスで、第1絶縁膜12をドライエッチングすることに依り、段差が100nm以上の凹凸32を形成する。最後に前述と同様にして、スピンコート法により、第2絶縁膜としてのポリイミド樹脂膜34を形成する。

(もっと読む)

半導体装置

【課題】容量素子を有する半導体装置の性能を向上させる。

【解決手段】MISFET形成領域A1の配線M1Aと配線M2Aとの間に位置する層間絶縁膜IL2Aと、キャパシタ形成領域B1の導電膜M1Bと導電膜M2Bとの間に位置する層間絶縁膜IL2Bについて、層間絶縁膜IL2Bを、層間絶縁膜IL2Aより誘電率の大きい膜[ε(IL2A)<ε(IL2B)]とする。また、導電膜M1Bと導電膜M2Bとは、層間絶縁膜IL2Bを介して対向し、導電膜M1Bには第1電位が印加され、導電膜M2Bには第1電位とは異なる第2電位が印加される。このように、縦方向に容量(Cv)を形成することで、耐圧劣化の問題を回避し、容量を構成する導電膜M1BとM2B間に高誘電率の絶縁膜を用いることで、容量を大きくする。

(もっと読む)

電子装置およびその製造方法

【課題】信頼性の高いコンタクト構造を提供する。

【解決手段】電子装置は第1の絶縁膜と、前記第1の絶縁膜の表面に形成された配線溝と、Cuよりなり前記配線溝を充填する配線パタ―ンと、前記配線パタ―ンの表面に形成され、Cuよりも大きな弾性率を有する金属膜と、前記第1の絶縁膜上に形成された第2の絶縁膜と、Cuよりなり、前記第2の絶縁膜中に形成され、前記金属膜とコンタクトするビアプラグと、を備える。

(もっと読む)

半導体基板、電子デバイス及びその製造方法

【課題】シリコン基板、半導体回路素子または絶縁層にクラックが発生することのない高信頼度のTSVを有する半導体基板、電子デバイス及びその製造方法を提供する。

【解決手段】貫通電極を囲む環状の溝に形成された絶縁層3は、シリカ微粒子311と、シリカ微粒子311−311間に生じる隙間に浸透してこれを埋めるナノ結晶またはナノアモルファスのシリカ320とからなるナノコンポジット構造である。

(もっと読む)

半導体装置及び半導体装置の製造方法

【課題】ビア層絶縁膜にビア用の孔を形成する工程において、シールリングのうちビア層絶縁膜に位置する部分に、導体を埋め込むための溝を形成しないで済むようにする。

【解決手段】ビア層絶縁膜40及び第2配線層絶縁膜50にはシール溝121が形成されている。また、エッチングストッパー層30には複数の孔31が形成されている。第2シール導体パターン120は、複数の孔31及びシール溝121に埋め込まれている。そして、エッチングストッパー層30は、シール溝121の底面に位置する部分が薄膜部32となっており、シール溝121が形成されていない部分と比較して薄くなっている。

(もっと読む)

3Dフラッシュ構造用のエッチングプロセス

【課題】プラズマ処理室において、ウェハ上でスタックを形成するシリコン系の複数の二重層の中に高アスペクト比のフィーチャをエッチングするための方法を提供する。

【解決手段】プラズマ処理室に主エッチングガスが流入される。第1の圧力を提供しながら、主エッチングガスがプラズマにされる。20℃未満のウェハ温度が維持される。プラズマにより上記複数のシリコン系二重層のうちの複数の組を貫いてエッチングする間に、第1の圧力よりも低い第2の圧力まで圧力を降下させる。上記複数の二重層のうち第1の複数の組がエッチングされた後に、主エッチングガスの流入を停止させる。

(もっと読む)

半導体装置

【課題】バイアスに依存した抵抗値の変化をさらに低減できるようにした半導体装置を提供する。

【解決手段】N型シリコン層3と、N型シリコン層3上に形成されたP型拡散抵抗7と、P型拡散抵抗7上に形成されたシリコン酸化膜11と、シリコン酸化膜11を貫いてP型拡散抵抗7の一方の端部7aに接続され、一方の端部7aに高電位を印加するための高電位用電極15と、シリコン酸化膜11を貫いてP型拡散抵抗7の他方の端部7bに接続され、他方の端部7bに低電位を印加するための低電位用電極17と、を備える。高電位用電極15及び低電位用電極17はそれぞれシリコン酸化膜11上に延設されると共に、シリコン酸化膜11上において高電位用電極15と低電位用電極17との間にはスリット21が設けられている。このスリット21は、P型拡散抵抗7の一方の端部7aと他方の端部7bとの間の中間位置23よりも一方の端部7aに近い側に位置する。

(もっと読む)

不揮発性半導体記憶装置

【課題】隣接する配線の間におけるリークを抑制することができる不揮発性半導体記憶装置を提供する。

【解決手段】不揮発性半導体記憶装置1は、シリコンを含む基板11と、基板11の上に設けられた複数のメモリセルと、複数のメモリセルの上方に設けられた配線7と、配線7の上に設けられたリーク抑制層8と、前記リーク抑制層8の上方に設けられた層間絶縁膜10と、を備えている。そして、隣接するメモリセルの間、および、隣接する配線7の間には空隙12が形成され、リーク抑制層8の幅寸法は、配線7の幅寸法よりも短いこと、および、隣接するリーク抑制層8の間の寸法は、隣接する配線7の間の寸法よりも長いこと、の少なくともいずれかである。

(もっと読む)

半導体装置及びその製造方法

【課題】プロセス条件の見直しを最小限に抑制しつつ電気的特性を向上させることができる半導体装置及びその製造方法を提供する。

【解決手段】半導体装置1は、半導体構造11の上面領域に形成された島状の絶縁膜20と、絶縁膜20の上面領域に配列された複数の凸状絶縁部23と、これら凸状絶縁部23と絶縁膜20とを被覆する層間絶縁膜26とを備える。

(もっと読む)

半導体装置の製造方法

【課題】アライメント光によるアライメントマークの検出感度を向上させて、低コストで貫通孔の位置合わせを行う。アライメントマークの誤検出を防ぐ。また、アライメントマーク検出時のアライメント光の露光マージンを大きくして、微細化に対応可能な半導体装置の製造方法を提供する。

【解決手段】半導体基板の非有効ショット領域において、半導体基板の主面又は主面よりも上方にアライメントマークを形成する。半導体基板の裏面の方から、アライメントマークが形成された位置に対応する開口を形成する。半導体基板内に形成されている半導体装置の構成パターンと露光用マスクパターンとの位置合わせをして、有効ショット領域の半導体基板内に貫通孔を形成する。

(もっと読む)

有機シリケート材料からの炭素の除去方法

【課題】有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去すること。

【解決手段】本明細書中に記載されているのは、酸化剤等の、しかし酸化剤に限られない薬品を用いてOSG膜を処理する工程、OSG膜紫外線を含むエネルギー源に曝す工程、またはOSG膜を薬品で処理する工程およびOSG膜をエネルギー源に曝す工程により、有機シリケート(OSG)膜内の炭素含有種の少なくとも一部分を除去するための方法である。

(もっと読む)

コバルト薄膜およびその形成方法ならびにナノ接合素子およびその製造方法ならびに配線およびその形成方法

【課題】厚さが35nm以下でも十分に高い保磁力および角型比を有する磁性のコバルト薄膜を得ることができるコバルト薄膜の形成方法およびこの方法により形成したコバルト薄膜を用いたナノ接合素子を提供する。

【解決手段】ポリエチレンナフタレート基板11上に真空蒸着法などによりコバルト薄膜12を35nm以下の厚さに成膜する。こうしてポリエチレンナフタレート基板11上にコバルト薄膜12を成膜した積層体を二つ用い、これらの二つの積層体をそれらのコバルト薄膜12のエッジ同士が、必要に応じて有機分子を挟んで、互いに対向するように交差させて接合することによりナノ接合素子を構成する。このナノ接合素子により不揮発性メモリや磁気抵抗効果素子を構成する。ポリエチレンナフタレート基板11の代わりに、少なくとも一主面がSiO2 からなる基板、例えば石英基板を用いてもよい。

(もっと読む)

1 - 20 / 813

[ Back to top ]