Fターム[5F082DA01]の内容

Fターム[5F082DA01]の下位に属するFターム

Fターム[5F082DA01]に分類される特許

1 - 14 / 14

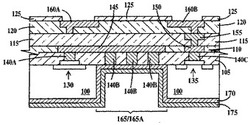

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

半導体装置及びその製造方法

【課題】MOSプロセスへの導入が容易で、エミッタ−ベース間のリーク電流(電界強度)を低減し、ノイズやサージ電圧の影響を受けにくい高性能な半導体装置とその製造方法の提供。

【解決手段】導電膜をマスクとして、2回のイオン注入を行ってエミッタを形成する。第2エミッタ領域111bは、低濃度の不純物イオン注入によって形成し、第1エミッタ領域111aは、高濃度の不純物イオン注入によって形成する。その結果、エミッタの周縁部に低濃度の第2エミッタ領域が形成され、電界が緩和され、リーク電流が低減する。また、導電膜とエミッタ電極116とが接続され、ノイズの影響を受けにくくなる。

(もっと読む)

半導体装置及びその製造方法

【課題】高周波帯域で動作する半導体装置の特性の低下を抑制しつつ、製造コストを低減できる半導体装置及びその製造方法を提供する。

【解決手段】本発明に係る半導体装置100は、電界効果型トランジスタと、ヘテロ接合バイポーラトランジスタと、ヘテロ接合バイポーラトランジスタのGaAsベース層7を用いて形成されたベースエピ抵抗素子28と、電界効果型トランジスタのInGaAsチャネル層4を用いて形成された配線部26と、配線部26とベースエピ抵抗素子28とを絶縁する高抵抗化領域27と、配線部26の水平方向の周囲を囲う絶縁性の素子分離領域24とを含む。また、ベースエピ抵抗素子28は、半絶縁性GaAs基板1の主面に垂直な方向から見て、配線部26と交差しているベースエピ抵抗素子領域29を有する。

(もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストかつ高製造歩留まりで、BiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】シャロートレンチ3、ディープトレンチ6に囲まれた半導体層2の基板領域17に、p型の単結晶半導体からなるエピタキシャル・ベース層24が島状に形成される。当該島状領域を含む半導体層2上の全面に窒化シリコン膜42、酸化シリコン膜43が形成される。島状領域上の異なる位置の窒化シリコン膜42、酸化シリコン膜43には、少なくとも2つの開口部が形成され、開口部が形成された窒化シリコン膜42、酸化シリコン膜43上に半導体膜44が形成される。当該半導体膜44が選択的に除去され、一方の開口部において島状領域に接続するベース電極と、他方の開口部において島状領域に接続するエミッタ電極とが同時に形成される。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置

【課題】制御電極層のない素子のレイアウトサイズを増加させることなく、CMPによる平坦化での過研磨を防ぐことができる半導体装置を提供すること。

【解決手段】半導体基板上に配されるとともに拡散層で構成された拡散層抵抗7と、拡散層抵抗7の外周を囲むように配されるとともに拡散層で構成されたPウェルコンタクト6と、Pウェルコンタクト6の外周を囲むように配されるとともに拡散層で構成されたNウェルコンタクト4と、を備えた抵抗セルを有する半導体装置であって、Pウェルコンタクト6及びNウェルコンタクト4は、それぞれ複数に分断されており、隣り合うPウェルコンタクト6間の領域に制御電極層9bが配されてPウェルコンタクト6と制御電極層9bが交互に配置され、隣り合うNウェルコンタクト4間の領域に制御電極層9aが配されてNウェルコンタクト4と制御電極層9aが交互に配置されている。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板の条件を、所望の静電破壊耐量が得られる比抵抗及び厚みとし、これに低濃度の半導体層を積層した基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

駆動素子アレイ及びその製造方法並びに表示装置

【課題】大電流を含む変調電流で発光素子を低電圧駆動させることができるとともに、製造コストの点でも有利な駆動素子アレイを提供する。

【解決手段】パッシブマトリクス方式で電流駆動する発光素子21と、その発光素子21への電流供給を制御するカラム選択用トランジスタ31A及びライン選択用トランジスタ31Bとを有する駆動素子アレイ10であって、そのカラム選択用トランジスタ31Aとライン選択用トランジスタ31Bを、発光素子21と同一の基板19上に形成された縦型有機トランジスタであるように構成して上記課題を解決した。この縦型有機トランジスタ31A,31Bは、電流変調を容易に行うことができ、特に大面積の表示装置に用いる場合には大電流を発光素子列に供給することができる。さらに、縦型有機トランジスタ31A,31Bには、光吸収層又は光反射層を施す等の遮光処理がなされていることが好ましい。

(もっと読む)

半導体装置の製造方法

【課題】非単結晶Si薄膜と単結晶Si薄膜デバイスとを形成し、高性能なシステムを集積化した半導体装置の製造方法を提供する。

【解決手段】絶縁基板2上に、単結晶Si薄膜トランジスタ16aと非単結晶Si薄膜トランジスタ1aとが形成された半導体装置20の製造方法において、表面に酸化膜、ゲートパターン、不純物イオン注入部が形成された後に平坦化されており、所定の深さに所定の濃度の水素イオンが注入された水素イオン注入部15を備えた単結晶Si基板10aを熱処理によって絶縁基板2上に接合し、さらに水素イオン注入部15において熱処理により劈開剥離した後、非晶質Si薄膜5を形成する。

(もっと読む)

半導体装置

【課題】バイポーラトランジスタ構造を有する静電破壊保護素子のホールド電圧を従来に比して高くするとともに、当該素子のサイズを抑える技術を提供することを目的とする。

【解決手段】エピタキシャル層2の表面にベース領域(P不純物層4)が形成され、P不純物層4の表面にエミッタ領域(N+不純物層5)が形成され、エピタキシャル層2とN+不純物層6とから成るコレクタ領域が構成されている。ベース電極8とベース領域(P不純物層4)の接続部が、ベース領域(P不純物層4)のコレクタ電極10側の端部とエミッタ領域(N+不純物層5)との間に位置する。つまり、コレクタ・ベース・エミッタの順で各電極が構成されている。ベース電極8とエミッタ電極9とは不図示の配線を介して接続されている。また、エピタキシャル層2を複数の島領域に分離するためのP+分離層11が形成されている。

(もっと読む)

横型バイポーラトランジスタ、およびそれを有する半導体装置、ならびにそれらの製造方法

【課題】横型バイポーラトランジスタ、およびそれを有する半導体装置、ならびにそれらの製造方法において、エピタキシャル層表面近傍に潜在しているダメージによって横型バイポーラトランジスタの利得が得られないことを改善する。

【解決手段】ベース領域の上部に設けた不純物を含有する半導体層の前記不純物を熱拡散させてコレクタ拡散層とエミッタ拡散層とを並設してなる横型バイポーラトランジスタ、およびそれを有する半導体装置において、半導体層を横断させて不純物をさらにイオン注入した後に熱処理することによってコレクタ拡散層とエミッタ拡散層とを設ける。半導体層はシリコンゲルマニウム層とし、特に、半導体装置に横型バイポーラトランジスタとともに形成するシリコンゲルマニウムヘテロ接合バイポーラトランジスタの形成に用いるシリコンゲルマニウム層を利用する。

(もっと読む)

半導体装置の製造方法

【課題】 製造工程の短縮が可能なBiCMOS型半導体装置の製造方法を提供する。

【解決手段】 エピタキシャル層12を形成したシリコン基板11表面に、素子分離領域15で分離されたバイポーラ/MOSトランジスタとなる領域を形成し、シリコン基板11表面に絶縁膜41を形成する工程と、エミッタ及びソース/ドレイン用の開口42を形成する工程と、これらのトランジスタ領域にポリシリコン膜を形成し、n型のPを導入する工程と、絶縁膜41の開口42及びその周辺部にあるポリシリコン膜にn型のAsを選択的に導入する工程と、絶縁膜41上のポリシリコン膜を残してエミッタ電極51、開口42のポリシリコン膜を残してソース/ドレイン電極52及びゲート電極53を形成する工程と、半導体基板11を熱処理して、n型不純物をベース領域23及びウェル領域33に拡散させて、エミッタ領域25及びソース/ドレイン領域32を形成する工程とを有する。

(もっと読む)

1 - 14 / 14

[ Back to top ]