Fターム[5F082DA09]の内容

Fターム[5F082DA09]の下位に属するFターム

多結晶 (97)

Fターム[5F082DA09]に分類される特許

1 - 20 / 84

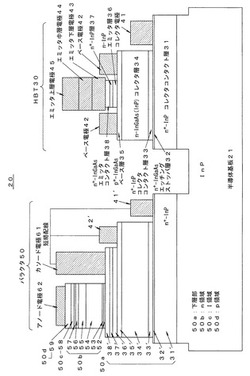

バラクタダイオードおよび半導体集積回路

【課題】狭い範囲の電圧変化に対して容量が線形的に、大きく変化する特性を実現する。

【解決手段】InPの半導体基板21上にエピタキシャル結晶成長させた層に対するエッチング処理により形成されるバラクタダイオード50において、半導体基板21上にエピタキシャル結晶成長させた層には、p型不純物を高濃度にドープさせバンドギャップエネルギーが半導体基板21よりも小さい材料からなるp領域50dと、p領域50dの半導体基板21寄りの面に接し、不純物をドープさせない材料または不純物を低濃度にドープさせた材料からなるI領域50cと、I領域50cの半導体基板21寄りの面に接し、n型不純物を中濃度以上にドープさせバンドギャップエネルギーが半導体基板21よりも大きい材料からなり、I領域50cから半導体基板21側に向かう程不純物濃度が低下する濃度減少部(54〜57)を有するn領域50bが含まれている。

(もっと読む)

低抵抗及び低インダクタンスの裏面貫通ビア及びその製造方法

【課題】裏面コンタクト構造体及びその構造体を製造する方法を提供する。

【解決手段】表面及び対向する裏面を有する基板100の表面上に第1誘電体層105を形成することと、第1誘電体層を貫通して前記基板の表面にまで延びる導電性の第1スタッド・コンタクト140Bを第1誘電体層内に形成することと、基板の裏面から基板を薄くして基板の新しい裏面を形成することと、基板の新しい裏面から前記第1誘電体層まで延びるトレンチ165を基板内に形成して第1スタッド・コンタクトの底面をトレンチ内に露出させることと、基板の新しい裏面、トレンチの側壁、第1誘電体層の露出面、及び第1スタッド・コンタクトの露出面の上に、トレンチを完全に充填するのに十分には厚くない共形導電層170、175を形成することと、を含む前記方法。

(もっと読む)

スイッチ装置

【課題】GaNトランジスタを理想的な還流ダイオードとして動作させ、低損失のスイッチ装置を実現できるようにする。

【解決手段】スイッチ装置は、窒化物半導体素子301と、窒化物半導体素子301を駆動する駆動部302とを備えている。窒化物半導体素子301は、第1のオーミック電極、第2のオーミック電極及び第1のゲート電極を有している。駆動部302は、第1のゲート電極にバイアス電圧を印加するゲート回路311と、第1のゲート電極と第1のオーミック電極との間に接続され、双方向に電流を流すスイッチ素子312とを有している。駆動部302は、第1のオーミック電極から第2のオーミック電極への電流を通電し且つ第2のオーミック電極から第1のオーミック電極への電流を遮断する動作を行う場合には、スイッチ素子312をオン状態とする。

(もっと読む)

半導体装置

【課題】ホールド電圧を変化させずに、トリガー電圧のみを調節することができるようにする。

【解決手段】本実施形態における保護素子10は、低濃度コレクタ層102、シンカー層110、高濃度コレクタ層112、エミッタ層130、高濃度ベース層122、ベース層120、第1導電型層140、及び第2導電型層150を有している。第2導電型層150は低濃度コレクタ層102に形成されており、ベース層120と第1導電型層140の間に位置している。第2導電型層150は低濃度コレクタ層102よりも不純物濃度が高い。

(もっと読む)

抵抗変化型メモリ

【課題】 メモリの動作特性の向上を図る。

【解決手段】実施形態の抵抗変化型メモリは、ビット線BLとワード線WLと、第1エミッタ21と、第1ベース23と、第1コレクタ22とを有する、第1駆動型の第1バイポーラトランジスタ2と、第2エミッタ31と、第2ベース33と、第2コレクタ32とを有する第2駆動型の第2バイポーラトランジスタ3と、第1及び第2端子を有する抵抗変化型メモリ素子1と、を具備し、メモリ素子1の第1端子は第1及び第2エミッタ21,31に接続され、メモリ素子1の第2端子は、ビット線BLに接続され、第1及び第2ベース23,33はワード線WLに接続される。

(もっと読む)

半導体デバイスおよびその製造方法

【課題】CMOS回路側の仕様で不純物領域の深さや濃度が制約を受けるような場合でもhFEの向上を可能とする。

【解決手段】1つのバイポーラトランジスタが、横型の主トランジスタ部と、縦型の補助トランジスタ部とから形成されている。横型の主トランジスタ部は、エミッタ領域31と、ベース領域14Bの表面側部分とコレクタ側部領域13Bとを電流チャネルとして動作する。縦型の補助トランジスタ部は、エミッタ領域31と、その底面に接するベース領域14Bの深部側部と、コレクタ深部領域12Bとを電流チャネルとして動作する。

(もっと読む)

半導体装置およびその製造方法

【課題】低コストで性能向上が可能なBiCMOS型半導体集積回路装置を実現することができる半導体装置およびその製造方法を提供する。

【解決手段】n型の半導体基板1の表面から所定の深さに、コレクタ領域を構成するn型の不純物領域26を備える。当該不純物領域26の上方、かつ半導体基板1に形成されたシャロートレンチ分離14で挟まれた領域18にはp型のベース領域20を備える。ベース領域20には、n型の半導体膜からなるエミッタ電極が接触して設けられている。当該半導体装置は、不純物領域26がベース領域20下からシャロートレンチ分離14下まで延在し、当該シャロートレンチ分離14を貫通して不純物領域26に電気的に接続するコンタクトプラグ52を備える。

(もっと読む)

ヘテロ接合バイポーラ・トランジスタ及びその製造方法

【課題】 ヘテロ接合バイポーラ・トランジスタ及びその製造方法を提供する。

【解決手段】 ヘテロ接合バイポーラ・トランジスタに関連する、半導体構造体及び半導体の製造方法が提供される。この方法は、同じ配線レベルにある金属導線によって接続される2つのデバイスを形成することを含む。2つのデバイスの第1のものの金属導線は、銅配線構造体上に金属キャップ層を選択的に形成することによって形成される。

(もっと読む)

高利得ワイドバンドギャップ・ダーリントン・トランジスタ及び関連する製造方法

パッケージ化電力電子デバイスが、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ・ドライバ・トランジスタ(112)と、ベース、コレクタ、及びエミッタ端子を有するワイドバンドギャップ・バイポーラ出力トランジスタ(116)とを含む。出力トランジスタのコレクタ端子は、ドライバ・トランジスタのコレクタ端子に結合され、出力トランジスタのベース端子は、ドライバ・トランジスタのエミッタ端子に結合され、ダーリントン対をもたらす。平面図における出力トランジスタの面積は、ドライバ・トランジスタの面積より少なくとも3倍大きい。例えば、出力トランジスタのドライバ・トランジスタに対する面積比は、約3:1から約5:1までの間とすることができる。関連するデバイス及び製造方法についても説明される。 (もっと読む)

半導体装置およびその製造方法

【課題】電力増幅モジュールの放熱特性を向上させる。

【解決手段】電力増幅モジュールに用いられる電力増幅回路用のLDMOSFET素子が形成された半導体チップにおいて、LDMOSFET素子用の複数のソース領域、複数のドレイン領域および複数のゲート電極39が形成されたLDMOSFET形成領域上に、ソース用バンプ電極BPSを配置する。ソース用バンプ電極BPSは、アルミニウムを主体とするソース用パッドM3S上に、ソース用パッドM3Sよりも厚くかつ銅を主体とするソース用導体層CNDSを介して形成する。ソース用バンプ電極BPSとソース用導体層CNDSの間には樹脂膜は介在していない。

(もっと読む)

半導体装置及びその製造方法

【課題】従来の半導体装置では、容量素子の誘電体膜の膜厚がフォトレジストの剥離の際に一部除去され、その容量値がばらつき、耐圧特性が劣化するという問題があった。

【解決手段】本発明の半導体装置では、容量素子1の下部電極8上面に誘電体膜としてのシリコン窒化膜12が形成され、シリコン窒化膜12上面に上部電極15が形成される。上部電極15は、シリコン窒化膜12を保護する多結晶シリコン膜13とシリコン膜14の積層構造から成る。この構造により、フォトレジストの剥離の際等にシリコン窒化膜12の一部が除去され、容量素子1の容量値がばらつきや耐圧劣化が防止される。

(もっと読む)

ESD保護素子

【課題】ESD耐量を向上させたESD保護素子を提供する。

【解決手段】本発明によるESD保護素子は、バイポーラトランジスタを用いたESD保護素子である。バイポーラトランジスタは、第1端子(Pad)に接続されるコレクタ拡散層7とエミッタ端子とを備えるバイポーラトランジスタと、第2端子(GND)からエミッタ拡散層4を介してコレクタ拡散層7に至る複数の電流経路上のそれぞれに設けられた電流制御抵抗11とを具備する。

(もっと読む)

非単結晶半導体間隔部分がベース・リンク長を制御するバイポーラ接合トランジスタを有する半導体構成体の構成及び製造

【課題】 半導体構成体がバイポーラトランジスタ(101)及び間隔構成体(265−1又は265−2)を包含している。

【解決手段】 該トランジスタはエミッタ(241)、ベース(243)、コレクタ(245)を有している。該ベースはベースコンタクト部分(243−1)、該エミッタの下側で且つ該コレクタの物質上方に位置されているイントリンシックベース部分(243I−1)、該イントリンシックベース部分とベースコンタクト部分との間に延在しているベースリンク部分(243L−1)を包含している。該間隔構成体は、間隔コンポーネント及び上部半導体表面に沿って延在する分離用誘電体層(267−1又は267−2)を包含している。該間隔コンポーネントは、該ベースリンク部分の上方で該誘電体層上に位置されており、好適には多結晶半導体物質であるほぼ非単結晶の半導体物質の横方向間隔部分(269−1又は269−2)を包含している。該横方向間隔部分の両側の第1及び第2下部端部(305−1及び307−1)は該ベースリンク部分の両側の第1及び第2上部端部(297−1及び299−1)に対して横方向に適合し、その長さを決定し且つそれにより制御する。

(もっと読む)

半導体基板の製造方法、半導体基板、電子デバイスの製造方法、および反応装置

【課題】耐熱性の低い部分を有する基板に加熱処理をして半導体基板を製造する。

【解決手段】単結晶層を有し熱処理される被熱処理部と、熱処理で加えられる熱から保護されるべき被保護部とを備えるベース基板を熱処理して半導体基板を製造する方法であって、被保護部の上方に、ベース基板に照射される電磁波から被保護部を保護する保護層を設ける段階と、ベース基板の全体に電磁波を照射することにより被熱処理部をアニールする段階とを備える半導体基板の製造方法を提供する。

(もっと読む)

トランジスタ素子及びその製造方法並びに発光素子及びディスプレイ

【課題】エミッタ電極−コレクタ電極間において、低電圧で大電流変調を可能とするトランジスタ素子を提供する。また、そうしたトランジスタ素子の製造方法、また、そのトランジスタ素子有する発光素子及びディスプレイを提供する。

【解決手段】エミッタ電極3とコレクタ電極2との間に、半導体層5(5A,5B)とシート状のベース電極4が設けられているトランジスタ素子により、上記課題を解決する。半導体層5は、エミッタ電極3とベース電極4との間及びコレクタ電極2とベース電極4との間に設けられて、それぞれ第2半導体層5B及び第1半導体層5Aを構成し、さらに、ベース電極の厚さが80nm以下であることが好ましい。また、少なくともエミッタ電極とベース電極との間又はコレクタ電極とベース電極との間には、暗電流抑制層が設けられていてもよい。

(もっと読む)

半導体装置およびその製造方法

【課題】外部からの高周波ノイズに対して誤動作しにくい半導体装置およびその製造方法を提供する。

【解決手段】n型コレクタ層11上に配置されたp型ベース層12bと、p型ベース層12b上に配置されたn型エミッタ層13bと、p型ベース層12b上にp型ベース層12bを包囲するように配置されたn型ベースコンタクト層21と、n型コレクタ層11上にp型ベース層12bと離隔して配置されたp型アノード層12cと、n型エミッタ層13bに接続されたエミッタ電極16cと、p型ベース層12bおよびn型ベースコンタクト層21に接続されたベース電極16aと、p型アノード層12cに接続され、かつエミッタ電極16cと共通接続されたアノード電極16bと、エミッタ電極16cとベース電極16a間に接続された第1抵抗R1と、ベース電極16aに接続された第2抵抗R2とを備える。

(もっと読む)

半導体装置の製造方法および半導体装置

【課題】トランジスタを短絡させることなく、シリサイド層を形成することができる半導体装置の提供。

【解決手段】バイポーラトランジスタ形成領域100と、CMOSトランジスタ形成領域200とを分離し、絶縁層52a,52bを形成し、上方に導電層56a,56bを形成し、側壁54a,54bを形成して、バイポーラトランジスタ形成領域100に、短絡防止部50aを形成すると同時に、CMOSトランジスタ形成領域200にゲート50bを形成する。バイポーラトランジスタのエミッタ領域40a、コレクタ領域40bおよびベース領域42aおよびCMOSトランジスタのソース領域40c,42bおよびドレイン領域40d,42cを形成し、各領域の上にシリサイド層60を形成する。短絡防止部50aは、エミッタ領域40a、コレクタ領域40bおよびベース領域42aのうち、いずれか2つの領域の間に位置する半導体基板10の上方に形成される。

(もっと読む)

接合型電界効果トランジスタ

【課題】 基板が低濃度の半導体基板のみからなるJ−FETは、静電破壊耐量は高いが、ノイズ電圧が大きく、ノイズ特性のばらつきも大きい問題があった。一方、ノイズ対策として、高濃度の半導体基板に低濃度の半導体層を積層した基板構造のJ−FETでは、ゲート抵抗の低減によりノイズ電圧を小さくできノイズ特性も安定する反面、静電破壊耐量が劣化する問題があった。

【解決手段】 高濃度半導体基板に低濃度の第1半導体層と、第1半導体層より高濃度の第2半導体層を積層する基板構造とする。これにより静電破壊耐量を劣化させない範囲でノイズ特性のばらつきを抑え、ノイズ電圧を小さくすることができる。また同時にノイズ特性に影響を与えない範囲で静電破壊耐量を向上させることができる。従って、従来構造と比較して市場要求に比較的柔軟に対応できるJ−FETを提供できる。

(もっと読む)

半導体装置の製造方法

【課題】バイポーラトランジスタの特性が劣化するのを抑制することが可能な半導体装置の製造方法を提供する。

【解決手段】この半導体装置100の製造方法は、シリコン基板11の領域A上にプレーナ型のバイポーラトランジスタ1を形成する工程と、プレーナ型バイポーラトランジスタ1が形成される領域を覆うようにシリコン窒化膜からなるカバー膜32aを形成する工程と、その後、プレーナ型のバイポーラトランジスタ1が形成される領域Aがカバー膜32aに覆われた状態で、バイポーラトランジスタ1が形成される領域にイオン注入する工程とを備える。

(もっと読む)

半導体装置の製造方法

【課題】シリサイド化の工程をMOSトランジスタ及びHBTと別けることなく、抵抗値のばらつきが小さいヒューズ素子を形成する半導体装置の製造方法を実現できるようにする。

【解決手段】半導体装置の製造方法は、MOSトランジスタ形成領域11Bにゲート電極22及びソースドレイン領域25を形成する工程と、MOSトランジスタ形成領域11Bを除いて、半導体基板11の上にシリコン及びシリコン以外のIV族元素を含む混晶膜と、シリコン膜とが順次積層された積層膜31A、31Bを形成する工程と、シリコン膜30Bの露出部分、ゲート電極22の上部及びソースドレイン領域25の上部をシリサイド化する工程とを備えている。

(もっと読む)

1 - 20 / 84

[ Back to top ]