Fターム[5J055AX00]の内容

電子的スイッチ (55,123) | 目的、効果 (5,153)

Fターム[5J055AX00]の下位に属するFターム

スイッチの基本性能向上 (933)

性能の向上 (482)

物理量(温度等)変化の補償 (146)

スイッチ状態の表示、マンインターフェイス (2)

スイッチの操作性向上、誤操作の防止 (16)

誤動作防止 (777)

故障対策 (573)

信頼性向上のための変形 (218)

電源電圧変動の対策 (81)

試験、調整 (60)

構造上の改善、配置、配線等 (18)

簡素化、小型化 (492)

特定の規格を考慮しているもの (2)

課題の発生する時、注目している時 (638)

課題の解決手段 (518)

Fターム[5J055AX00]に分類される特許

1 - 20 / 197

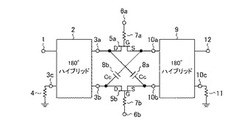

高周波スイッチ

【課題】通過損失を低減するためにオン状態時の抵抗を小さくしても、十分なアイソレーション量を確保する高周波スイッチを得る。

【解決手段】トランジスタ5a,5bのオフ容量Coffと同一の容量Ccを有するクロスカップルキャパシタ8a,8bを設ける。

クロスカップルキャパシタ8a,8bにより、トランジスタ5a,5bのオフ容量Coffをキャンセルすることができるので、アイソレーションを大きく改善することができる。したがって、通過損失を低減するためにトランジスタ5a,5bのオン抵抗Ronを小さくしても、十分なアイソレーション量を確保することができる。

(もっと読む)

ゲート駆動回路

【課題】逆導通IGBTに内蔵されたダイオードで発生するリカバリ電流を低減させる。

【解決手段】逆導通IGBTに内蔵されているダイオードに順方向電流が流れている間に、逆導通IGBTのゲート−エミッタ間にゲート閾値電圧よりも低い電圧を印加することで、逆導通IGBTのドリフト領域への正孔の注入を抑制し、リカバリ電流を低減させる。

(もっと読む)

半導体スイッチ及び無線機器

【課題】高周波特性を改善した半導体スイッチ及び無線機器を提供する。

【解決手段】電源回路と、駆動回路と、スイッチ部と、第1の電位制御回路と、を備えた半導体スイッチが供給される。前記電源回路は、負の第1の電位を生成する第1の電位生成回路と、電源電位を降圧した正の第2の電位を生成する第2の電位生成回路と、を有する。前記駆動回路は、前記第1の電位と第3の電位とが供給され、端子切替信号に基づいて前記第1の電位及び前記第3の電位の少なくとも一方を出力する。前記スイッチ部は、前記駆動回路の出力に応じて複数の高周波端子のいずれか1つに共通端子を接続する。前記第1の電位制御回路は、第1のトランジスタを有する分割回路と、第2のトランジスタを有する増幅回路と、を有する。

(もっと読む)

半導体集積回路及びそれを備えた駆動装置

【課題】絶縁素子を介した信号伝達に誤動作を生じさせ得る異常を検出して制御対象に停止信号をすることが可能な半導体集積回路を提供すること。

【解決手段】本発明にかかる半導体集積回路は、外部から供給される送信データVINに応じた送信信号を生成し出力する送信回路Tx1と、受信信号に基づいて送信データVINを再生する受信回路Rx1と、送信回路Tx1と受信回路Rx1とを絶縁するとともに、送信信号を受信信号として伝達する絶縁素子ISO1と、絶縁素子ISO1を介した信号伝達に誤動作を生じさせ得る異常を検出する異常検出部DT1と、異常検出部DT1により異常が検出された場合には、外部から送信回路Tx1に供給される送信データVINに関わらず停止信号を出力する制御部CT1と、を備える。

(もっと読む)

負荷駆動装置

【課題】負荷電流検出手段により検出された負荷電流を用いてリーク故障を確実に検出する。

【解決手段】駆動回路33a、33bの出力端子Ta2、Tb2から電源線6に至る還流経路内にシャント抵抗9a、9bを接続し、電源線5と給電分岐点Nsとの間に共通のシャント抵抗24を接続する。駆動制御回路32は、MOSFET7a、7bをPWM駆動し、負荷電流検出回路12a、12bから負荷電流Ia、Ibを入力し、総電流検出回路23から総電流Isを入力する。検出負荷電流Ia、Ibに対しそれぞれ対応するPWM駆動信号のオフ駆動期間をマスク処理し、マスク処理した検出負荷電流Iam、Ibmを加算した加算電流Icmと検出総電流Isとを比較する。両者が等しい場合には正常状態と判定し、異なる場合にはショート故障またはリーク故障が生じたと判定する。

(もっと読む)

電流制御用半導体素子およびそれを用いた制御装置

【課題】ゲインa、およびオフセットbの変動を動的に補正することで、1チップのIC内で高精度な電流検出が可能な電流制御用半導体素子、およびそれを用いた制御装置を提供することにある。

【解決手段】

同一半導体チップ上に、トランジスタ4と、電流−電圧変換回路22とADコンバータ23とを有する。参照電流生成回路6,6’は、負荷2の電流に電流パルスIcを重畳して、ADコンバータが出力する電圧デジタル値を変動させる。ゲインオフセット補正部8は、参照電流生成回路6,6’による電圧デジタル値の変動を信号処理して、ADコンバータ23が出力する電圧デジタル値と負荷の電流デジタル値の線形関係式におけるゲインa,a’及びオフセットb,b’を動的に取得する。電流デジタル値演算部12は、ゲインオフセット補正部8により取得されたゲイン及びオフセットを用いて、ADコンバータが出力する電圧値を補正する。

(もっと読む)

アナログスイッチ回路およびマルチプレクサ回路

【課題】 外部端子の雑音の影響を抑制しつつ、リーク電流を低減する。

【解決手段】 アナログスイッチ回路は、第1ノードと第2ノードとの間に配置された第1スイッチと、第2ノードと第3ノードとの間に配置された第2スイッチと、所定の電圧が供給される第4ノードと第2ノードとの間に配置された第3スイッチと、少なくとも2種類の制御信号を受け、第1スイッチおよび第2スイッチをオンし、かつ、第3スイッチをオフする第1制御と、第1スイッチ、第2スイッチおよび第3スイッチをオフする第2制御と、第1スイッチおよび第2スイッチをオフし、かつ、第3スイッチをオンする第3制御とのいずれかを、制御信号の組み合わせに基づいて実施する制御部とを有している。

(もっと読む)

スイッチング回路

【課題】整数倍の信号成分に起因して、負荷回路やスイッチング素子に余分な電流が流れない電力効率を向上したスイッチング回路を提供する。

【解決手段】スイッチング回路1は、第1端子50a及び第2端子50bを有しており、パルス信号により駆動されて第1端子及び第2端子の導通状態をスイッチするスイッチング素子10と、スイッチング素子の第1端子13に電圧を供給する電源部30と、電源部に並列に接続される負荷回路40と、電源部と負荷回路との接続点Pと、スイッチング素子の第1端子との間に接続され、パルス信号のクロック周波数のN倍(Nは1以上の整数)の周波数において、接続点からスイッチング素子へ流れる電流を抑制する受動回路部50と、受動回路部と接続点との間に接続され、N倍の周波数において共振する共振回路部60と、を備える。

(もっと読む)

半導体装置

【課題】InやZnなどを含む酸化物半導体をチャネル領域に用いたトランジスタを、P型トランジスタのように駆動できる半導体装置を提供する。

【解決手段】トランジスタとインバータを有し、インバータの出力はトランジスタのゲートに入力され、トランジスタのチャネル領域はIn、Zn若しくはSnを含む酸化物半導体膜を有し、インバータを構成するトランジスタのチャネル領域はシリコンを有し、インバータにハイ電圧を入力すると、インバータからロー電圧が出力されるとともにトランジスタのゲートにロー電圧が入力されてトランジスタはオフし、インバータにロー電圧を入力すると、インバータからハイ電圧が出力されるとともにトランジスタのゲートにハイ電圧が入力されてトランジスタはオンする半導体装置によって解決する。

(もっと読む)

CMOSインバータを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路

【課題】CMOSインバータのP形MOSトランジスタのボディバイアスを変化させても、入力信号の立ち上がりと立ち下がりの伝搬遅延時間の差を、従来のものより小さく保てるマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路を提供する。

【解決手段】パスゲートM1、M2の出力に初段出力バッファとして低しきい値CMOSインバータINV1を接続したセレクター回路を基本構成とし、それを用いたマルチプレクサ、デマルチプレクサ、ルックアップテーブルおよび集積回路であって、パスゲートはそのボディ端子が可変電位をとるボディバイアス電源VBNに接続し、INV1のP形MOSトランジスタM3のしきい値電圧を可変にできるようにそのボディ端子は可変電位をとるボディバイアス電源VBPに接続し、そのN形MOSトランジスタM4はそのしきい値電圧を固定するためにそのボディ端子が固定電位をとる電源VSSに接続する。

(もっと読む)

駆動装置

【課題】電圧駆動型素子を駆動状態と非駆動状態の間で遷移させるときの遷移期間において、電圧駆動型素子のゲート電圧を柔軟に制御するための技術を提供する。

【解決手段】駆動装置1は、電圧駆動部3と電流駆動部4を備えている。電圧駆動型素子2を駆動状態と非駆動状態の間で遷移させるときの遷移期間のうちの一部の区間では、電圧駆動部3を利用した電圧駆動型素子2のゲート電圧Vgの制御が停止され、電流駆動部4を利用した電圧駆動型素子2のゲート電圧Vgの制御が実行されるように構成されている。

(もっと読む)

電圧検知回路

【課題】高精度で低コストの電圧検知回路を提供する。

【解決手段】パワーオンリセット回路は、分圧回路1、バイポーラトランジスタQ1,Q2、抵抗素子R1,R2、およびベース電流補償回路10を備える。分圧回路1の出力電圧VINがバンドギャップ電圧VBGの場合、バイポーラトランジスタQ1,Q2のコレクタ電流I1,I2が一致する。電圧補償回路10は、電流I1に基いてバイポーラトランジスタQ1,Q2のベース電流の和に相当する電流I6を生成し、その電流I6をバイポーラトランジスタQ1,Q2のベースに供給する。したがって、バイポーラトランジスタQ1,Q2の各々のベース電流が大きい場合でも、高い検出精度が得られる。

(もっと読む)

半導体装置

【課題】充電対象素子へ充電電流を効率的に供給することが可能な半導体装置を提供する。

【解決手段】充電対象素子Cに充電電流を供給する半導体装置1は、第1導電型の半導体層1と、充電対象素子Cの第1電極に結合される第1ノードN1を有し、半導体層1の主表面上に形成される第2導電型の第1の半導体領域2と、電源電圧が供給される電源電位ノードNL1に結合される第2ノードN3および第3ノードN4を有し、第1の半導体領域2の表面において半導体層1と間隔をあけて形成される第1導電型の第2の半導体領域3と、第2ノードN3および第3ノードN4から半導体層1への電荷キャリアの移動を制限する電荷キャリア移動制限部とを備える。

(もっと読む)

ゲートドライブ回路

【課題】簡単な構成で、ワイドバンドギャップ半導体からなるスイッチ素子を駆動するゲートドライブ回路。

【解決手段】ワイドバンドギャップ半導体からなるスイッチ素子Q1であって、ドレインとソースとゲートとを有し、ゲートをドライブする信号とゲートとの間にコンデンサと抵抗の並列接続回路を介して接続され、オフ信号期間は、スイッチ素子Q1のゲート・ソース間を短絡するスイッチSW1とを備えることを特徴とするゲートドライブ回路。

(もっと読む)

パワーオンリセット回路

【課題】パワーオン時における回路電源電圧の変化の緩急に拘らず、非動作電圧から動作電圧へ変化時にリセット信号を確実に出力するパワーオンリセット回路を提供する。

【解決手段】本発明に係るパワーオンリセット回路は、回路電源電圧を受けて充電を行う充電回路と、回路電源電圧を受けて出力電圧を出力する動作電圧設定回路と、前記充電回路の出力する充電電圧、及び、前記動作電圧設定回路の出力する出力電圧を判定して、パワーオンリセット信号を出力する電圧判定回路とを備える。

(もっと読む)

半導体装置

【課題】本発明は、信号線駆動回路におけるトランジスタの特性のばらつきの影響を抑制

する技術に関する。

【解決手段】信号線駆動回路には、各々容量手段と供給手段とを有する第1電流源回路(

437)及び第2電流源回路(438)を設ける。シフトレジスタ(418)から供給さ

れるサンプリングパルスと外部から供給されるラッチパルスに従って、前記容量手段は、

n個のビデオ信号用定電流源(109)の各々から供給される電流を加算した電流を電圧

に変換し、前記供給手段は変換された電圧に応じた電流を供給することで、トランジスタ

の特性によらず、ビデオ信号に応じた電流出力を行うことを特徴とする。前記n個のビデ

オ信号用定電流源から供給される電流値は、20:21:・・・:2nに設定されて、階

調を表現することが可能となる。

(もっと読む)

ホールド回路

【課題】保持電圧の下降または上昇傾きを良好に調整可能なホールド回路を提供すること。

【解決手段】ホールド回路10は、入力端子20、第1出力端子22、基準電圧端子24、オペアンプ30、ダイオード32、コンデンサ36、抵抗R0、電圧発生回路50、を備えている。コンデンサ36は、一端が接続点26に接続され、他端が基準電圧端子24に接続される。抵抗R0は、一端が接続点26に接続される。ダイオード52のアノードが、オペアンプ38を介して接続点26に接続される。抵抗R0の他端と中間接続点58とが接続される。オペアンプ30は、非反転入力端子30bが入力端子20に接続され、反転入力端子30aが接続点26に接続され、出力端子30cがダイオード32に接続される。電圧発生回路50は、ダイオード52に入力される出力電圧V22から変化させたオフセット電圧V23を生成して、中間接続点58から出力する。

(もっと読む)

容量性負荷駆動回路および流体噴射装置

【課題】上限あるいは下限付近のデューティー比でも効率よく容量性負荷を駆動する。

【解決手段】駆動波形信号をパルス変調して変調信号を生成し、電力増幅した後に平滑フ

ィルターを通すことによって生成した駆動信号を容量性負荷に印加する。デジタル電力増

幅器から平滑フィルターに流れる電流の方向が一変調周期内で逆転する条件下では、その

一変調周期内での電流の最大値および最小値の絶対値が所定の閾値以上となるようにキャ

リア周波数を変更する。一変調周期内で平滑フィルターを流れる電流の最大値および最小

値の絶対値が所定の閾値を下回ると、電力増幅時に大きな損失が発生する。従って、所定

の閾値を下回らないようにキャリア周波数を変更してやれば、効率よく電力増幅を行って

容量性負荷を駆動することが可能となる。

(もっと読む)

出力バッファ回路

【課題】出力信号のデューティを保ちつつ消費電流の変化を低減する。

【解決手段】出力バッファ回路は、出力回路(300)と、第1入力回路(210)と、第2入力回路(220)と、第1クランプ回路(110)と、第2クランプ回路(120)とを具備する。出力回路(300)は、第1出力トランジスタ(P301)と第2出力トランジスタ(N301)とを備え、出力信号(VOUT)を出力する。第1クランプ回路(110)および第2クランプ回路(120)のそれぞれは、カスコード接続される第1導電型のトランジスタ(P111/P121)と、第2導電型のトランジスタ(N111/N121)とを備える。第1クランプ回路(110)は、所定の期間第1入力回路(210)の出力電圧(VA1)をクランプする。第2クランプ回路(120)は、所定の期間第2入力回路(220)の出力電圧(VA2)をクランプする。

(もっと読む)

半導体スイッチ及びその測定方法

【課題】端子間の直流オン抵抗を高精度で測定可能な半導体スイッチ及びその測定方法を提供する。

【解決手段】実施形態によれば、第1のスイッチ素子と、第2のスイッチ素子と、制御回路と、を備えた半導体スイッチが提供される。第1のスイッチ素子は、第1の端子及び第2の端子を含む複数の高周波端子のそれぞれと共通端子との間に接続される。第2のスイッチ素子は、前記第1の端子と接地用端子との間に接続される。前記制御回路は、前記第1のスイッチ素子及び前記第2のスイッチ素子をそれぞれオンまたはオフさせる制御信号を出力し、端子切替信号に応じて、前記共通端子を前記複数の高周波端子のいずれか1つに接続する通常動作モードと、前記共通端子を前記第1の端子と前記第2の端子と接地用端子とに接続するテストモードと、を実行することを特徴とする。

(もっと読む)

1 - 20 / 197

[ Back to top ]